# Optimizing Optical Network Terminal Units With Logic

Emrys Maier

## **Functional Block Diagram**

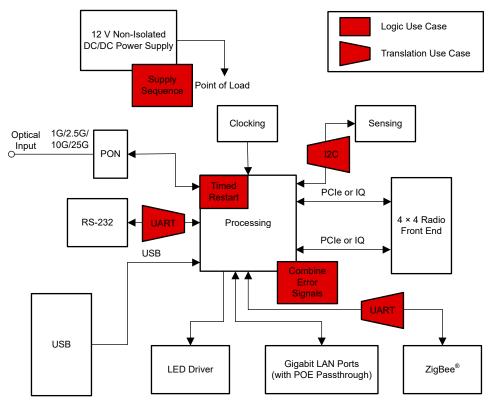

For the purpose of this brief, a simplified Optical Network Terminal unit (ONT) block diagram is used to illustrate the logic and translation use cases, see Simplified Block Diagram for Optical Network Terminal Units. Each red block has an associated use-case document. Links are provided in Table 1 and Table 2. For a more complete block diagram, see the interactive online end equipment reference diagram for Optical Network Terminal units.

Figure 1. Simplified Block Diagram for Optical Network Terminal Units

## **Logic and Translation Use Cases**

Each use case is linked to a separate short document that provides additional details including a block diagram, design tips, and part recommendations. The nearest block and use-case identifiers are listed to match up exactly to the use cases shown in the provided *simplified block diagram*.

| Table 1. Logic Use Cases | Table | 1. L | _ogic | Use | Cases |

|--------------------------|-------|------|-------|-----|-------|

|--------------------------|-------|------|-------|-----|-------|

| <u>-                                      </u> |                       |                                                                |  |  |

|------------------------------------------------|-----------------------|----------------------------------------------------------------|--|--|

| Nearest Block                                  | Use-Case Identifier   | Use Case                                                       |  |  |

| Non-Isolated DC/DC Power Supply                |                       | Power Sequencing With RC<br>Circuits and Schmitt-Trigger Logic |  |  |

| Processing                                     | Timed Restart         | Reset a System for a Short Time                                |  |  |

|                                                | Combine Error Signals | Combine Error Signals                                          |  |  |

#### **Table 2. Translation Use Cases**

| Nearest Block   | Use-Case Identifier | Use Case                    |

|-----------------|---------------------|-----------------------------|

| Sensing         | I2C                 | Translate Voltages for I2C  |

| RS-232, ZigBee® | UART                | Translate Voltages for UART |

### Power Sequencing With RC Circuits and Schmitt-Trigger Logic

Optical Network Terminal units (ONTs) have multiple internal modules that can be operating at different voltages and require specific power-up sequencing to prevent spurious data from being sent during the system start-up. In many cases, simple logic gates and RC delays can be used to provide a power-up sequence.

The RC delays produce signals that are too slow for standard CMOS inputs, so logic parts with Schmitt-trigger inputs are required for this application. Fortunately, TI has the HCS logic family which has Schmitt-trigger architecture on every input, so any required logic function is available for use.

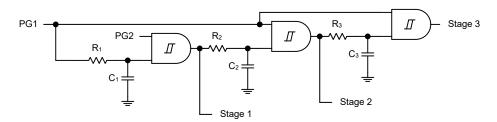

AND gates are the most common gate used for logic sequencing. Figure 2 shows an example circuit with 2 input power good signals and three delayed output stages. When PG1 goes high, there is a short delay ( $t_1 = R_1 \times C_1$ ) after which PG2 can directly enable stage one. When PG2 becomes high, stage 1 immediately is activated and the timer for stage two begins ( $t_2 = 2 \times R_2 \times C_2$ ), which then activates stage 2, and finally, after a short delay ( $t_3 = R_3 \times C_3$ ), stage 3 is activated. The connection of PG1 provides an immediate disable signal to stages two and three, while stage 1 takes a short time ( $t_1$ ) to become disabled. If PG2 becomes low, stage 1 is immediately disabled and stages two and three are disabled after their sequential delays; the same as during the start-up.

Of course, this is just one example. There are infinitely many combinations that can be achieved using discrete logic, and the HCS family enables you to build your own design with reliable operation, low size, and maximum flexibility.

Figure 2. Example Logic Circuit for Sequencing Components

See more about a similar use case in the *Combine Power Good Signals* application report and the *Logic Minute* video *Combining Power Good Signals*.

- Schmitt-trigger input architecture is required for having slow transitioning input signals; a dedicated Schmitttrigger buffer can be added if a logic gate does not include Schmitt-trigger input architecture

- The best practice is to power the start-up sequence logic gates directly from the primary power source or from a dedicated low I<sub>Q</sub> LDO regulator so the logic is powered before all other circuitry

- All HCS logic family devices include positive input clamp diodes, so be sure to add a series resistor to any inputs that can exceed VCC + 0.5 V. Choose resistor values based on the input voltage (V<sub>IN</sub>), forward voltage (V<sub>F</sub>, typically 0.65 V), gate supply voltage (V<sub>CC</sub>) and maximum clamp diode current (I<sub>IK</sub>) per the following equation: R > V<sub>IN</sub> V<sub>CC</sub> V<sub>F</sub> / I<sub>IK</sub>

- Need additional assistance? Ask our engineers a question on the TI E2E™ Logic Support Forum

# **Table 3. Recommended Parts**

| Part Number    | Automotive<br>Qualified | V <sub>CC</sub> Range | Туре                    | Features                                                                                                    |

|----------------|-------------------------|-----------------------|-------------------------|-------------------------------------------------------------------------------------------------------------|

| SN74HCS08-Q1   | ✓                       |                       |                         | Schmitt-trigger inputs                                                                                      |

| SN74HCS08      |                         | 2 V – 6 V             | Quad AND gate           | Positive input clamp diodes on all pins; add series resistors if input voltage exceeds V <sub>CC</sub>      |

| SN74LVC1G17-Q1 | ✓                       |                       |                         | Schmitt-trigger inputs                                                                                      |

| SN74LVC1G17    |                         | 1.65 V – 5.5 V        | Schmitt-trigger buffer  | Inputs are over-voltage tolerant; signals can exceed $V_{\text{CC}}$                                        |

| SN74LVC1G57    |                         |                       |                         | Schmitt-trigger inputs                                                                                      |

| SN74LVC1G58    |                         | 1.65 V – 5.5 V        | Configurable Logic Gate | Between the '1G57 and '1G58, all 2-input logic gate functions can be produced. See data sheets for details. |

| SN74LV14A-Q1   | ✓                       | 2 V – 5.5 V           |                         | Schmitt-trigger inputs                                                                                      |

| SN74LV14A      |                         |                       | Hex inverter            | Overvoltage tolerant inputs Partial power-down support (I <sub>off</sub> ) Improved noise characteristics   |

| SN74LV08A-Q1   | ✓                       |                       |                         | Over-voltage tolerant inputs                                                                                |

| SN74LV08A      |                         | 2 V – 5.5 V           | Quad AND gate           | Partial power-down support (I <sub>off</sub> ) Improved noise characteristics                               |

| SN74AUP1G57    |                         |                       |                         | Schmitt-trigger inputs                                                                                      |

| SN74AUP1G58    |                         | 0.8 V – 3.6 V         | Configurable Logic Gate | Ultra low-power operation (0.6 µA max I <sub>CC</sub> )<br>Overvoltage tolerant inputs                      |

For more devices with Schmitt-trigger input architecture, browse the *online parametric tool* which can be sorted by the desired voltage, output current, and other features.

# **IMPORTANT NOTICE AND DISCLAIMER**

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated