# Application Note **Do's and Don'ts for TXB and TXS Voltage Level-Shifters** with Edge Rate Accelerators

Michael Ikwuyum, Ajith Narayansetty, Sahil Garg

#### ABSTRACT

Auto Directional level shifter families are designed with weaker outputs than devices from other level shifting families, to be easily overdriven by the hosts. This makes Auto Direction devices a requirement for bidirectional interfaces such as I<sup>2</sup>C, MDIO, Quad-SPI, and so on.

The TXS and TXB Auto Directional level shifter families as shown in *Voltage Translators and Level Shifters* are designed with edge rate accelerators (commonly known as one-shots). The one-shots are designed for a set duration of pulse width for optimal signal integrity, impacted by RC components. Therefore, intentional and careful considerations should be made when used with additional external components as majority of one-shot concerns are due to improper use of the devices, false triggering of the one-shots and poor layout design.

## **Table of Contents**

| 1 Introduction                                                         | 2 |

|------------------------------------------------------------------------|---|

| 2 The One-shot's Designed Duration                                     | 3 |

| 2.1 Design Considerations                                              | 3 |

| 2.2 Recommended Parts                                                  |   |

| 3 Design Considerations for Slow Rise and Fall Times                   | 4 |

| 3.1 Design Considerations                                              |   |

| 3.2 Recommended Parts                                                  |   |

| 4 Consider the Impact of External RC Components on Rise and Fall Times | 5 |

| 4.1 Design Considerations                                              |   |

| 4.2 Recommended Parts                                                  | 5 |

| 5 Consider the Lumped Capacitance                                      |   |

| 5.1 Design Considerations                                              | 6 |

| 5.2 Recommended Parts                                                  |   |

| 6 Consider the Effects of Temperature on the Output Impedance          | 7 |

| Design Considerations                                                  |   |

| 7 Summary                                                              | 8 |

| 8 References                                                           |   |

## List of Figures

| Figure 2-1. Example of the one-shot timing out before reaching the designed duration      | . 3 |

|-------------------------------------------------------------------------------------------|-----|

| Figure 3-1. Example of Slow Rise and Fall Times, 2.4 μS/V                                 | 4   |

| Figure 4-1. Example of Rise and Fall Times Increasing with Lumped Capacitance             |     |

| Figure 5-1. Example Voltage Translation showing Lumped Capacitance with a One-Shot Device |     |

| Figure 6-1. Example of Outputs at Varying Temperature                                     |     |

## **List of Tables**

| Table 1-1. Recommended Translator by Interface | 2 |

|------------------------------------------------|---|

| Table 2-1. Recommended Parts                   |   |

| Table 3-1, Recommended Parts                   |   |

| Table 4-1. Recommended Parts                   | 5 |

| Table 5-1. Recommended Parts                   |   |

|                                                |   |

### Trademarks

All trademarks are the property of their respective owners.

1

## **1** Introduction

Texas Instruments' portfolio of level shifter devices contains many different types of level translation functions that collectively is able to address almost any application requirement. TI's level translation portfolio includes Auto Directional, Direction Controlled, Fixed Direction, and Application Specific Level Translators in Industrial and Automotive ratings. For a list of recommended level translation devices for common interface types please see Table 1-1. For more information on all of TI's level translation designs please visit TI's level translation landing page at www.ti.com/translation.

|                         | Translation Level      |                       |  |

|-------------------------|------------------------|-----------------------|--|

| Interface               | Up to 3.6 V            | Up to 5.5 V           |  |

| FET Replacement         | 2N7001T                | SN74LXC1T45 / TXU0101 |  |

| 1 Bit GPIO/Clock Signal | SN74AXC1T45            | SN74LXC1T45 / TXU0101 |  |

| 2 Bit GPIO              | SN74AXC2T245           | SN74LXC2T45 / TXU0102 |  |

| 2-Pin JTAG/UART         | SN74AXC2T45            | SN74LXC2T45 / TXU0202 |  |

| I2C/MDIO/SMBus          | TXS0102 / LSF0102      | TXS0102 / LSF0102     |  |

| IC-USB                  | SN74AVC2T872 / TXS0202 | NA                    |  |

| 4 Bit GPIO              | SN74AXC4T245           | TXB0104 / TXU0104     |  |

| UART                    | SN74AXC4T245           | TXU0204               |  |

| SPI                     | SN74AXC4T774           | TXU0304               |  |

| JTAG                    | SN74AXC4T774           | TXU0304               |  |

| I2S/PCM                 | SN74AXC4T774 / TXB0104 | TXB0104 / TXU0204     |  |

| Quad-SPI                | TXB0106                | TXB0106               |  |

| SDIO/SD/MMC             | TXS0206 / TWL1200      | NA                    |  |

| 8 Bit GPIO/RGMII        | SN74AXC8T245           | SN74LXC8T245          |  |

#### Table 1-1. Recommended Translator by Interface

## 2 The One-shot's Designed Duration

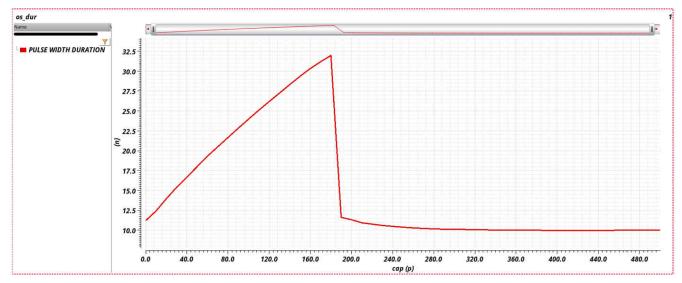

#### Figure 2-1. Example of the one-shot timing out before reaching the designed duration.

#### 2.1 Design Considerations

- Figure 2-1 shows the one-shot expiring at about 200 pF.

- Do not expire or time-out the one-shot prior to reaching the designed duration.

- · Consider short enough traces for round-trip delay reflections within the one-shot duration of 10-30 ns.

- Avoid excessive loading (similar to the datasheets) as the longer the trace length, the more the lumped capacitive loading

- Need additional assistance? Ask our engineers a question on the TI E2E™ Logic Support Forum

#### **2.2 Recommended Parts**

Applications with higher capacitive loading from longer trace lengths, connectors etc, typically do not require Auto Direction. Such applications (SPI for example) require devices with stronger output buffers. See Table 2-1 for more suitable recommendations.

| Part Number     | AEC-Q100 | AEC-Q100 Voltage Translation<br>Range Feat |                                                                                                                |

|-----------------|----------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| TXU0304         |          |                                            | Schmitt-trigger inputs                                                                                         |

| TXU0304-Q1      | 1        | 1.1 V–5.5 V                                | Integrated pull-down resistors $V_{CC}$ Isolation and $V_{CC}$ Disconnect, Glitch-free power supply sequencing |

| SN74AXC4T774    |          |                                            | Direction controlled                                                                                           |

| SN74AXC4T774-Q1 | ✓        | 0.65 V–3.6 V                               | Glitch-free power supply sequencing V <sub>CC</sub> Isolation                                                  |

#### Table 2-1. Recommended Parts

For more devices, browse through the *online parametric tool* where you can sort by desired voltage, channel numbers, and other features.

## **3 Design Considerations for Slow Rise and Fall Times**

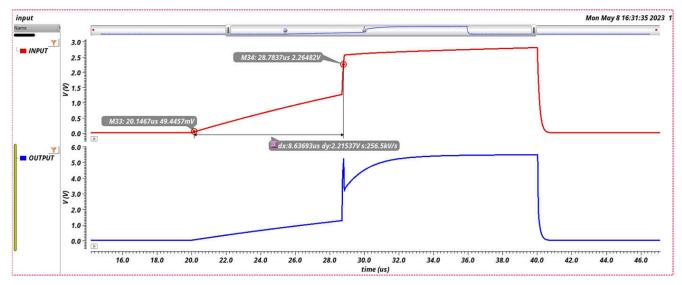

Figure 3-1. Example of Slow Rise and Fall Times, 2.4 µS/V

#### 3.1 Design Considerations

- Figure 3-1 shows the one-shot false triggering due to a slow input rise time outside of the data sheet recommendation.

- Do not use slow input rise or fall transition rates.

- As shown, the one-shots can trigger or expire prior to the designed duration for adverse system-level effects.

- · Consider using fast enough input edges per the data sheet's input transition rate.

- Implications of Slow or Floating CMOS Inputs

- Need additional assistance? Ask our engineers a question on the TI E2E™ Logic Support Forum

#### **3.2 Recommended Parts**

See Table 3-1 for applications that may require the flexibility for slower inputs.

| Device Family | AEC-Q100 | Voltage Translation<br>Range | Features                                                                                                              |

|---------------|----------|------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| TXU and LXC   | √        | 1.1 V–5.5 V                  | Schmitt-trigger inputs<br>Integrated pull-down resistors                                                              |

| AUP           | ✓        | 0.6 V–3.6 V                  | Input hysteresis allows the input to support slew<br>rates as slow as 200 ns/V, improving switching noise<br>immunity |

| LSF           | 1        | 0.65 V–5.5 V                 | No input transition rate requirement.                                                                                 |

#### Table 3-1. Recommended Parts

For more devices, browse through the *online parametric tool* where you can sort by desired voltage, channel numbers, and other features.

4

## 4 Consider the Impact of External RC Components on Rise and Fall Times

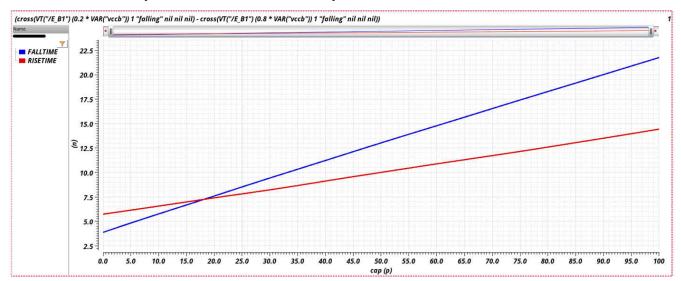

Figure 4-1. Example of Rise and Fall Times Increasing with Lumped Capacitance

#### 4.1 Design Considerations

- Figure 4-1 shows the relationship for rise / fall times being directly proportional to the lumped capacitance.

- Do not exceed the data sheet loading conditions as the rise or fall times will increase, impacting data throughput.

- Consider any tolerances of any additional RC components, similar to the data sheet recommendations.

- Need additional assistance? Ask our engineers a question on the *TI E2E™ Logic Support Forum*.

#### **4.2 Recommended Parts**

The Auto Directional device family with the most flexibility for external resistors per RC components (for applications such as  $I^2C$ ), is the LSF family and then the TXS family. See Table 4-1 for recommendations.

| Part Number | AEC-Q100 Qualified | Voltage Translation<br>Range | Features                                                                 |

|-------------|--------------------|------------------------------|--------------------------------------------------------------------------|

| LSF0102     |                    | 0.65 V – 5.5 V               | Over-voltage tolerant I/O                                                |

| LSF0102-Q1  | $\checkmark$       | 0.05 V - 5.5 V               | Low R <sub>ON</sub> for low output voltage levels                        |

| TXS0102     |                    |                              | Edge-rate acceleration                                                   |

| TXS0102-Q1  | $\checkmark$       | 1.65 V – 5.5 V               | Supports Partial-Power-Down applications<br>Integrated pull-up resistors |

**Table 4-1. Recommended Parts**

For more devices, browse through the *online parametric tool* where you can sort by desired voltage, channel numbers, and other features.

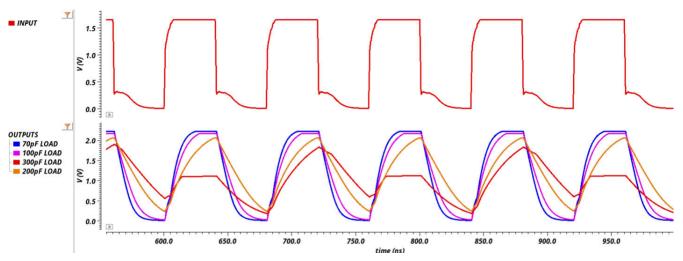

## **5** Consider the Lumped Capacitance

### 5.1 Design Considerations

- Unless otherwise noted in the data sheets, ensure <70 pF lumped capacitance for optimal performance per the data sheet's recommended data rates.

- Additional parasitic capacitance is added from trace length and connectors.

- Additional loading impacts signal integrity at faster data rates.

- Need additional assistance? Ask our engineers a question on the *TI E2E™ Logic Support Forum*

### **5.2 Recommended Parts**

The Fixed and Direction Control families are most suitable for applications for high data throughput. Consider Table 5-1 for applications with connectors or excessive lumped capacitance such as GPIO, instead of TXB.

| Part Number     | AEC-Q100 | Data Rates | Voltage Translation<br>Range | Features                                                                  |

|-----------------|----------|------------|------------------------------|---------------------------------------------------------------------------|

| SN74LXC8T245    |          | Up To 420  |                              | Schmitt-trigger inputs                                                    |

| SN74LXC8T245-Q1 | ✓        | Mbps       | 1.1 V–5.5 V                  | Dynamic pull-downs on I/O $V_{CC}$ Isolation and $V_{CC}$ Disconnect      |

| TXU0104         |          | Up To 200  |                              | Schmitt-trigger inputs                                                    |

| TXU0104-Q1      | 1        | Mbps       | 1.1 V–5.5 V                  | Integrated pull-down resistors $V_{CC}$ Isolation and $V_{CC}$ Disconnect |

| SN74AXC1T45     |          | Up To 500  |                              | Direction controlled                                                      |

| SN74AXC1T45-Q1  | 1        | Mbps       | 0.65 V–3.6 V                 | Glitch-free power supply sequencing $V_{CC}$ Isolation                    |

#### Table 5-1. Recommended Parts

For more devices, browse through the *online parametric tool* where you can choose between the three types of translators.

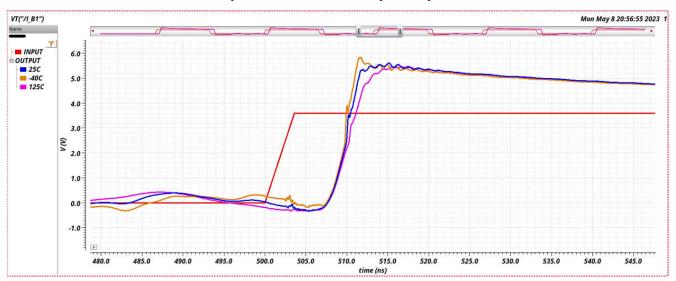

#### 6 Consider the Effects of Temperature on the Output Impedance

Figure 6-1. Example of Outputs at Varying Temperature

#### **Design Considerations**

- Minimize reflections / ringing.

- Consider the impact of temperature on the output impedance, as mismatched impedance with PCB traces yield reflections.

- Reflections or ringing can be amplified by the one-shot as false edge triggers.

- Excessive ringing can cause false triggers observed as oscillating outputs.

- Ringing is also caused by capacitance and inductance of long cables or traces and can be amplified by unstable GND or VCC voltages.

- Use bypass capacitors or stable GND to minimize noise.

- Devices with Schmitt Trigger are most recommended for noisy applications. See Section 3.2 for recommendations.

- Need additional assistance? Ask our engineers a question on the *TI E2E™ Logic Support Forum*

7

## 7 Summary

- Consider short enough traces for round-trip delay reflections within the one-shot duration of 10-30 ns.

- Consider any tolerances of any additional RC components, similar to the data sheet recommendations.

- Consider utilizing fast enough input edges per the input transition rate while avoiding floating inputs as stated in the data sheets.

- Unless otherwise noted in the data sheets, makes sure <70 pF lumped capacitance designed for performance per the data sheet's recommended data rates.

- Avoid timing-out the one-shot duration with additional parasitic capacitance as trace length and connectors yields additional capacitive loading.

- One-shot triggers when they detect rising or falling edges. Reflections and or ringing can cause false triggers. Ringing is also caused by capacitance and inductance of long cables and or traces and can also be amplified by unstable GND or V<sub>CC</sub> voltages.

- Consider the impact on temperature per the output impedance, as mismatched impedance with PCB traces yield reflections that can be amplified by the one-shot as false edge triggers.

## 8 References

- Texas Instruments, *Designing With the SN74LVC1G123 Monostable Multivibrator*, application note.

- Texas Instruments, A Guide to Voltage Translation With TXS-Type Translators, application note.

- Texas Instruments, A Guide to Voltage Translation With TXB-Type Translators, application note.

- Texas Instruments, Effects of Pullup and Pulldown Resistors on TXS and TXB Devices, application note.

- Texas Instruments, Implications of Slow or Floating CMOS Inputs, application note.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated