Application Report SLAA413–July 2009

# Configuring P<sup>2</sup>S to Generate BCLK from TLV320AIC32/33/31/3101/3104/3105/3106/3204/3254/DAC32 Devices and WCLK from McBSP Port

Supriyo Palit and Nitesh Kekre

Audio and Imaging Products / Portable Audio Converters

#### ABSTRACT

This application note describes a method for interfacing the multichannel buffered serial port (McBSP) to the  $I^2S^{TM}$  interface of the TLV320AlC32/33/31, the TLV320AlC3101/3104/3105/3106/3204/3254 and DAC32 devices such that the bit clock (BCLK) is generated by the audio data converter device and the word clock (WCLK) is generated by the McBSP.

This type of interface is useful in applications where the host processor (with a McBSP interface) can synchronize the audio (with video, for example) by controlling the WCLK, whereas the data converter device can generate the BCLK depending on the I<sup>2</sup>S configuration. The McBSP interface is supported in a variety of processors from Texas Instruments, such as the TMS320C5000/C6000<sup>™</sup> digital signal processors (DSPs), the DaVinci<sup>™</sup> digital media processors, and OMAP applications processors.

#### Contents

| 1 | Introduction                              | 2 |

|---|-------------------------------------------|---|

| 2 | Application Setup                         | 2 |

| 3 | Conclusion                                | 9 |

| 4 | References                                | 9 |

|   | List of Tables                            |   |

| 1 | AIC Clock Configuration                   | 3 |

| 2 | AIC Digital Audio Interface Configuration | 5 |

| 3 | 5 ( )                                     |   |

|   |                                           |   |

| 4  | McBSP Serial Port Control Register 2 (SPCR2x)   | 6 |

|----|-------------------------------------------------|---|

| 5  | McBSP Receive Control Register 1 (RCR1x)        | 6 |

| 6  | McBSP Receive Control Register 2 (RCR2x)        | 7 |

| 7  | McBSP Transmit Control Register 1 (XCR1x)       | 7 |

| 8  | McBSP Transmit Control Register 2 (XCR2x)       | 7 |

| 9  | McBSP Sample Rate Generator Register 1 (SRGR1x) | 7 |

| 10 | McBSP Sample Rate Generator Register 2 (SRGR2x) | 7 |

| 11 | McBSP Pin Control Register (PCRx)               | 8 |

TMS320C5000/C6000, DaVinci are trademarks of Texas Instruments. I<sup>2</sup>S is a trademark of NXP Semiconductors. All other trademarks are the property of their respective owners.

1

#### 1 Introduction

The <u>TLV320AIC32/33/31/3101/3104/3105/3106/3204/3254</u> codecs and <u>TLV320DAC32</u> digital-to-analog converter (DAC) from TI provide a glueless interface to applications with McBSPs. The digital audio interface in these devices is programmable to work with popular audio standard protocols (I<sup>2</sup>S, DSP, Left-/Right-Justified, and TDM) and 16-, 20-, 24- and 32- bit data widths. Furthermore, Word-Clock (WCLK) and Bit-Clock (BCLK) can be independently configured in either Master or Slave Mode for flexible connectivity to a wide variety of processors. An on-chip PLL enables generation of audio clocks from a variety of system clocks from 512 kHz to 50 MHz.

The flexibility of the digital audio interface and the on-chip PLL facilitates a host processor with a McBSP interface to provide a single master clock (MCLK) to the audio data converter device in order to generate both the internal audio clock as well as the clock for the digital interface (BCLK). This flexibility eliminates the need to generate BCLK using clock multipliers/dividers within or outside of the host processor.

In addition, because BCLK and WCLK can be configured in either Master or Slave mode independent of each other, the host processor can generate WCLK from BCLK. This feature enables the host processor to control audio streaming by synchronizing audio with other signals, such as video in a multimedia application.

This application report presents the hardware connections and software configurations necessary to enable the digital audio interface as discussed. The host processor under consideration is a TMS320C55x, and the audio data converter device is the TLV320AIC3254. The TLV320AIC3254 is a high-performance audio codec with 16-bit stereo playback and record functionality. The device integrates several analog features such as a microphone interface, input analog mux, low-noise gain stage, headphone drivers, line level drivers, and volume controls.

# 2 Application Setup

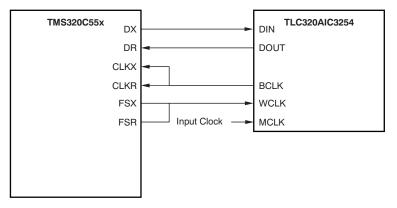

The McBSP on the TMS320C55x is connected to the TLV320AIC3254 through digital audio interface signals, as shown in Figure 1.

Figure 1. McBSP Connection to TLV320AIC3254 Codec

In the application shown, MCLK is provided by a timer output from the TMS320C55x. The TMS320C55x runs from a 200-MHz clock; the timer divides this clock by 16 to provide an MCLK of 12.5 MHz.

# 2.1 AIC Configuration

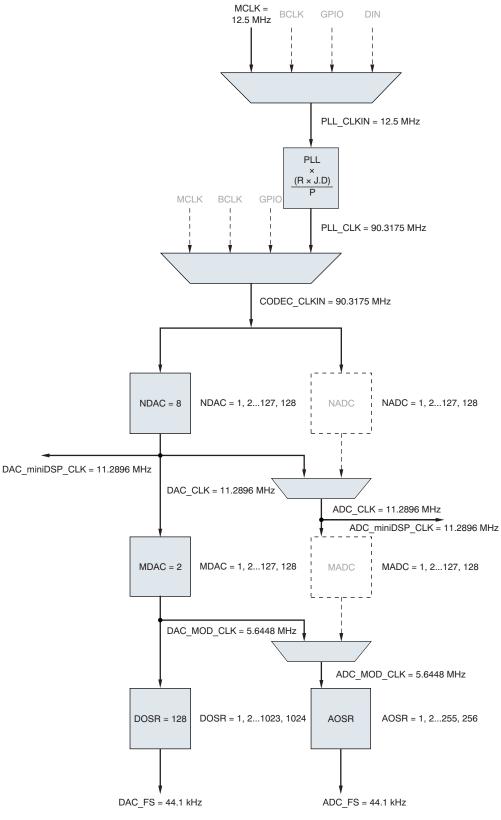

The TLV320AIC3254 uses its internal PLL to run the codec at 44.1 kHz. The codec also generates the BCLK. The TLV320AIC3254 clock configuration is summarized in Table 1.

| Value<br>0 (Default)<br>3<br>1<br>1 | Location<br>Pg 0, Reg 4, D3-D2<br>Pg 0, Reg 4, D1-D0<br>Pg 0, Reg 5, D7 | Description<br>PLL_CLKIN = MCLK<br>CODEC_CLKIN = PLL_CLK                                                             |

|-------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| 3<br>1                              | Pg 0, Reg 4, D1-D0                                                      |                                                                                                                      |

| 1                                   | 0, 0,                                                                   | CODEC_CLKIN = PLL_CLK                                                                                                |

|                                     | Pa 0 Rea 5 D7                                                           |                                                                                                                      |

| 1                                   | 1 g 0, neg 3, D1                                                        | PLL is powered up                                                                                                    |

| 1                                   | Pg 0, Reg 5, D6-D4                                                      | PLL Divider P                                                                                                        |

| 1                                   | Pg 0, Reg 5, D3-D0                                                      | PLL Multiplier R                                                                                                     |

| 7                                   | Pg 0, Reg 6, D5-D0                                                      | PLL Multiplier J                                                                                                     |

| 8                                   | Pg 0, Reg 7, D5-D0                                                      | PLL Fractional Multiplier D(13:8)                                                                                    |

| 206                                 | Pg 0, Reg 8, D7-D0                                                      | PLL Fractional Multiplier (D7–D0)<br>D = $8 \times 256 + 206 = 2254$                                                 |

|                                     |                                                                         | PLL_CLK = PLL_CLKIN x (R x<br>J.D) / P<br>= 12.5 x 1 x 7.2254 / 1<br>= 90.3175 MHz                                   |

| 1                                   | Pg 0, Reg 11, D7                                                        | NDAC Divider is powered up                                                                                           |

| 8                                   | Pg 0, Reg 11, D6-D0                                                     | NDAC-Val = 8<br>DAC_CLK = PLL_CLK/NDAC<br>= 11.2896 MHz                                                              |

| 1                                   | Pg 0, Reg 12, D7                                                        | MDAC Divider is powered up                                                                                           |

| 2                                   | Pg 0, Reg 12, D6-D0                                                     | MDAC-Val = 2<br>DAC_MOD_CLK =<br>DAC_CLK/MDAC<br>= 5.6448 MHz<br>DAC_Fs = DAC_MOD_CLK/DOSF<br>(= 128, default value) |

|                                     | 8<br>206<br>1<br>8<br>1                                                 | 8 Pg 0, Reg 7, D5-D0   206 Pg 0, Reg 8, D7-D0   1 Pg 0, Reg 11, D7   8 Pg 0, Reg 11, D6-D0   1 Pg 0, Reg 12, D7      |

#### Table 1. AIC Clock Configuration

TEXAS INSTRUMENTS

www.ti.com

The TLV320AIC3254 digital audio interface configuration is given in Table 2.

| Name                           | Value       | Location               | Description                                                                                                                                                         |  |  |  |

|--------------------------------|-------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Codec Interface                | 0 (Default) | Pg 0, Reg 27,<br>D7-D6 | Codec Interface = $I^2S$                                                                                                                                            |  |  |  |

| Codec Interface Word<br>Length |             |                        | Codec Interface Word<br>Length = 16 bits                                                                                                                            |  |  |  |

| BCLK Direction                 | 1           | Pg 0, Reg 27, D3       | BCLK is output                                                                                                                                                      |  |  |  |

| WCLK Direction                 | 0           | Pg 0, Reg 27, D2       | WCLK is input                                                                                                                                                       |  |  |  |

| BDIV_CLKIN                     | 1           | Pg 0, Reg 29,<br>D1-D0 | BDIV_CLKIN =<br>DAC_MOD_CLK                                                                                                                                         |  |  |  |

| BCLK Power Up                  | 1           | Pg 0, Reg 30, D7       | BCLK Divider is powered up                                                                                                                                          |  |  |  |

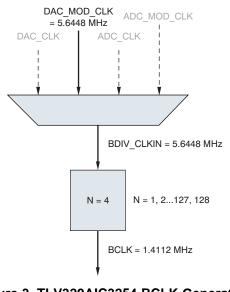

| BCLK-N-Val                     | 4           | Pg 0, Reg 30,<br>D6-D0 | BCLK-N-Val = 4<br>BCLK = DAC_MOD_CLK /<br>BCLK-N<br>= 1.4112 MHz (32 clocks in<br>a 44.1-kHz. frame, 16 clocks<br>for Left Channel, 16 clocks<br>for Right Channel) |  |  |  |

## Table 2. AIC Digital Audio Interface Configuration

The BCLK generation diagram is shown in Figure 3.

**Note:** The configurations presented in this section are not the only configurations required for normal operation of the TLV321AIC3254 codec. Other blocks such as analog routing, digital processor, and so forth must also be configured and powered up for the codec to function properly.

# 2.2 McBSP Configuration

The McBSP must be configured for I<sup>2</sup>S mode to accept the BCLK as an input for CLKX/CLKR and to generate the WCLK through FSX/FSR. The detailed configurations of the McBSP registers are listed in Table 3 to Table 11.

| Name     | Value | Bit   | Description                                                               |

|----------|-------|-------|---------------------------------------------------------------------------|

| DLB      | 0     | 15    | Digital Loop Back mode disabled                                           |

| RJUST    | 01b   | 14-13 | Right-justify the data and sign-extend the data into the MSBs             |

| CLKSTP   | 00b   | 12-11 | Normal clocking for non-SPI mode                                          |

| Reserved | XXX   | 10-8  | Reserved                                                                  |

| DXENA    | 0     | 7     | DX Enabler is off                                                         |

| Reserved | x     | 6     | Reserved (write 0)                                                        |

| RINTM    | 10b   | 5-4   | McBSP sends RINT request to CPU when receive frame-sync pulse is detected |

| RSYNCERR | 0     | 3     | No synchronization error                                                  |

| RFULL    | x     | 2     | Read-only                                                                 |

| RRDY     | x     | 1     | Read-only                                                                 |

| RRST     | 0     | 0     | Serial port receiver is disabled                                          |

#### Table 3. McBSP Serial Port Control Register 1 (SPCR1x)

#### Table 4. McBSP Serial Port Control Register 2 (SPCR2x)

| Name     | Value  | Bit   | Description                                                                |

|----------|--------|-------|----------------------------------------------------------------------------|

| Reserved | хххххх | 15-10 | Reserved                                                                   |

| FREE     | 1      | 9     | Free running                                                               |

| SOFT     | x      | 8     | Don't care when FREE is 1                                                  |

| FRST     | 0      | 7     | Frame Sync Logic is Reset                                                  |

| GRST     | 0      | 6     | Sample Rate Generator is Reset                                             |

| XINTM    | 10b    | 5-4   | McBSP sends XINT request to CPU when transmit frame-sync pulse is detected |

| XSYNCERR | 0      | 3     | No synchronization error                                                   |

| XEMPTY   | x      | 2     | Read-only                                                                  |

| XRDY     | x      | 1     | Read-only                                                                  |

| XRST     | 0      | 0     | Serial port transmitter is disabled                                        |

| Name     | Value   | Bit  | Description                        |

|----------|---------|------|------------------------------------|

| Reserved | х       | 15   | Reserved                           |

| RFRLEN1  | 000001b | 14-8 | Two words per frame <sup>(1)</sup> |

| RWDLEN1  | 010b    | 7-5  | 16 bits per word <sup>(1)</sup>    |

| Reserved | XXXXX   | 4-0  | Reserved                           |

<sup>(1)</sup> Configurations specific to  $I^2S$ .

| Table 0. MCDOF Receive Control Register 2 (RCR2X) |        |      |                                   |  |  |

|---------------------------------------------------|--------|------|-----------------------------------|--|--|

| Name                                              | Value  | Bit  | Description                       |  |  |

| RPHASE                                            | 0      | 15   | Single phase frame                |  |  |

| RFRLEN2                                           | XXXXXX | 14-8 | Don't care for single phase frame |  |  |

| RWDLEN2                                           | XXX    | 7-5  | Don't care for single phase frame |  |  |

| RCOMPAND                                          | 00b    | 4-3  | No companding, MSB received first |  |  |

| RFIG                                              | 0      | 2    | Frame sync detect                 |  |  |

| RDATDLY                                           | 01b    | 1-0  | 1-bit data delay                  |  |  |

#### Table 6 McBSP Receive Control Register 2 (RCR2x)

## Table 7. McBSP Transmit Control Register 1 (XCR1x)

| Name     | Value   | Bit  | Description                        |

|----------|---------|------|------------------------------------|

| Reserved | х       | 15   | Reserved                           |

| XFRLEN1  | 000001b | 14-8 | Two words per frame <sup>(1)</sup> |

| XWDLEN1  | 010b    | 7-5  | 16 bits per word <sup>(1)</sup>    |

| Reserved | XXXXX   | 4-0  | Reserved                           |

(1) Configurations specific to I<sup>2</sup>S.

## Table 8. McBSP Transmit Control Register 2 (XCR2x)

| Name     | Value  | Bit  | Description                          |

|----------|--------|------|--------------------------------------|

| XPHASE   | 0      | 15   | Single phase frame                   |

| XFRLEN2  | XXXXXX | 14-8 | Don't care for single phase frame    |

| XWDLEN2  | XXX    | 7-5  | Don't care for single phase frame    |

| XCOMPAND | 00b    | 4-3  | No companding, MSB transmitted first |

| XFIG     | 0      | 2    | Frame sync detect                    |

| XDATDLY  | 01b    | 1-0  | 1-bit data delay                     |

#### Table 9. McBSP Sample Rate Generator Register 1 (SRGR1x)

| Name   | Value     | Bit  | Description                                            |

|--------|-----------|------|--------------------------------------------------------|

| FWID   | 00001111b | 15-8 | Frame Sync Pulse Width = 16 CLKG cycles <sup>(1)</sup> |

| CLKGDV | 0000000b  | 7-0  | CLKG frequency = Input clock frequency <sup>(2)</sup>  |

(1) Configurations specific to  $I^2S$ .

(2) Configurations specific to receive BCLK for CLKX/CLKR and generate WCLK through FSX/FSR.

| Name  | Value         | Bit  | Description                                                            |  |

|-------|---------------|------|------------------------------------------------------------------------|--|

| GSYNC | 0             | 15   | No clock synchronization                                               |  |

| CLKSP | x             | 14   | Don't care because CLKS is not used as input clock                     |  |

| CLKSM | 1             | 13   | Input for CLKG on CLKX pin (SCLKME = 1) <sup>(1)</sup>                 |  |

| FSGM  | 1             | 12   | Frame sync pulse generated by the sample rate generator <sup>(1)</sup> |  |

| FPER  | 000000011111b | 11-0 | Frame Sync Period = 32 CLKG cycles <sup>(2)</sup>                      |  |

Configurations specific to receive BCLK for CLKX/CLKR and generate WCLK through FSX/FSR. Configurations specific to I<sup>2</sup>S. (1)

(2)

| Name     | Value | Bit | Description                                                 |  |

|----------|-------|-----|-------------------------------------------------------------|--|

| Reserved | X     | 15  | Reserved                                                    |  |

| IDLEEN   | 0     | 14  | McBSP active when PERIPH domain is idle                     |  |

| XIOEN    | 0     | 13  | DX, FSX, CLKX are not GPIO pins                             |  |

| RIOEN    | 0     | 12  | DR, FSR, CLKR are not GPIO pins                             |  |

| FSXM     | 1     | 11  | Internal transmit frame sync signal <sup>(1)</sup>          |  |

| FSRM     | 1     | 10  | Internal receive frame sync signal <sup>(1)</sup>           |  |

| CLKXM    | 0     | 9   | External transmit clock signal <sup>(1)</sup>               |  |

| CLKRM    | 0     | 8   | External receive clock signal (1)                           |  |

| SCLKME   | 1     | 7   | Input for CLKG on CLKX pin (CLKSM = 1) <sup>(1)</sup>       |  |

| CLKSSTAT | X     | 6   | Read-only                                                   |  |

| DXSTAT   | X     | 5   | Read-only                                                   |  |

| DRSTAT   | X     | 4   | Read-only                                                   |  |

| FSXP     | 1     | 3   | Transmit frame sync is active low <sup>(2)</sup>            |  |

| FSRP     | 1     | 2   | Receive frame sync is active low <sup>(2)</sup>             |  |

| CLKXP    | 1     | 1   | Transmit data driven on falling edge of CLKX <sup>(2)</sup> |  |

| CLKRP    | 1     | 0   | Receive data sampled on rising edge of CLKR <sup>(2)</sup>  |  |

Table 11. McBSP Pin Control Register (PCRx)

<sup>(1)</sup> Configurations specific to receive BCLK for CLKX/CLKR and generate WCLK through FSX/FSR.

<sup>(2)</sup> Configurations specific to  $I^2S$ .

# 2.3 McBSP Startup Sequence

The McBSP configuration described in Section 2.2 is during initialization of the McBSP interface. Apart from initialization, a timing sequence must be followed for proper startup of the McBSP interface:

- First, initialize the McBSP registers as shown in Section 2.2. This configuration resets the Sample Rate Generator and the Frame Sync Logic, and keeps the Transmitter and the Receiver in a disabled state. It also configures the McBSP interrupt generator to send an interrupt to the CPU when a frame sync pulse is detected

- Then, enable the Sample Rate Generator and Frame Sync Logic (GRST = FRST = 1 in SPCR2x). This register can be enabled when the host is ready to send/receive audio that is synchronized with other events (for example, video in a multimedia application). The Sample Rate generator will receive the BCLK through CLKX and will generate the WCLK through the internal Frame Sync Logic.

- The first frame sync pulse generated internally interrupts the CPU. The interrupt service routine enables the Transmitter and Receiver, and audio transfer is initiated with the TLV320AIC3254 (RRST = 1 in SPCR1x, XRST = 1 in SPCR2x). Also, the CPU interrupt for a frame sync pulse is disabled because synchronization of the McBSP relative to the frame sync pulse has been achieved.

- Typically, the McBSP Transmitter and the Receiver are connected to a pair of direct memory access (DMA) controllers for block transfers to/from memory. The McBSP Transmitter signals the Transmitter DMA to send the next set of stereo data and the McBSP Receiver signals the Receiver DMA to receive the next set of stereo data. The Transmitter DMA copies stereo samples from memory to the McBSP registers, while the Receiver DMA copies stereo samples from the McBSP registers to memory. After a block of audio samples is sent/received through the McBSP interface, the respective DMA controllers interrupt the CPU for further action.

- The McBSP operation can be stopped by disabling the Transmitter and the Receiver (RRST = 0 in SPCR1x, XRST = 0 in SPCR2x).

# 3 Conclusion

This report discusses a digital audio interface scheme that enables BCLK to be generated by the audio data converter device and WCLK to be generated by the McBSP interface of a host processor. This recommended scheme provides flexibility to the host processor in two ways:

- 1. It allows the user to provide a single MCLK to the audio converter device in order to generate BCLK (through the internal PLL of the audio data converter device), and thereby avoids multipliers/dividers to generate BCLK from the system clock; and

- 2. It enables the user to have control of audio transmission and reception through the WCLK, thus having the ability to synchronize audio with other events (such as video in a multimedia application).

# 4 References

The following documents are available for download at the Texas Instruments web site (www.ti.com).

- 1. TLV320AIC3254 Data Manual (SLAS549)

- TMS320VC5501/5502/5503/5507/5509/5510 DSP Multichannel Buffered Serial Port (McBSP) Reference Guide (<u>SPRU592</u>)

Submit Documentation Feedback

Conclusion

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications       |                           |

|-----------------------------|------------------------|--------------------|---------------------------|

| Amplifiers                  | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters             | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DLP® Products               | www.dlp.com            | Broadband          | www.ti.com/broadband      |

| DSP                         | dsp.ti.com             | Digital Control    | www.ti.com/digitalcontrol |

| Clocks and Timers           | www.ti.com/clocks      | Medical            | www.ti.com/medical        |

| Interface                   | interface.ti.com       | Military           | www.ti.com/military       |

| Logic                       | logic.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Power Mgmt                  | power.ti.com           | Security           | www.ti.com/security       |

| Microcontrollers            | microcontroller.ti.com | Telephony          | www.ti.com/telephony      |

| RFID                        | www.ti-rfid.com        | Video & Imaging    | www.ti.com/video          |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2009, Texas Instruments Incorporated