# Multi-Device Configuration for TPA32xx Amplifiers

Dan Kisling

# ABSTRACT

The TPA32xx family of parts (TPA3244, TPA3245, TPA3250, TPA3251, TPA3255, and TPA3221) comes equipped with functionality to simplify systems with multiple Class-D amplifiers. Class-D amplifiers use pulse-width modulation (PWM) switching (450 kHz – 600 kHz), which are discrete packets of energy, to deliver large amounts of output power at a very high efficiency. However, issues can arise if multiple Class-D amplifiers switch simultaneously, but are not synchronized and managed. Issues include:

- *Power Supply Overloading* resulting from all amplifiers switching on the same edge, causing the supply to droop or sag below the regulated voltage.

- Beat Interference or Beat Tones are audible tones that occur when slightly misaligned switching frequencies interact to create another frequency.

The oscillator sync pins allow multiple devices to share a common clock and draw power on different phases to improve performance. Different phases reduce power supply loading during the switch cycles. Sharing a clock improves performance by preventing beat tones.

The Clip/OTW and FAULT signal lines are configured so multiple lines can be tied together to simplify circuitry. While not required, these functionalities have several benefits that can reduce complexity and improve the performance of your audio system.

#### Contents

| 1 | Oscillator Sync Pins                | 2 |

|---|-------------------------------------|---|

| 2 | Multi Device Clip/OTW and FAULT Pin | 4 |

#### List of Figures

| 1 | Oscillator Sync Pins Timing Diagram                                            | 2 |

|---|--------------------------------------------------------------------------------|---|

| 2 | Master and Slave Configuration for a 5-Device System                           | 4 |

| 3 | Configuration 1: All Clip/OTW Pins Tied Together, all FAULT Pins Tied Together | 5 |

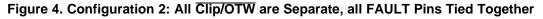

| 4 | Configuration 2: All Clip/OTW are Separate, all FAULT Pins Tied Together       | 5 |

| 5 | Configuration 3: All Clip/OTW are Tied Together, all FAULT Pins are Separate   | 6 |

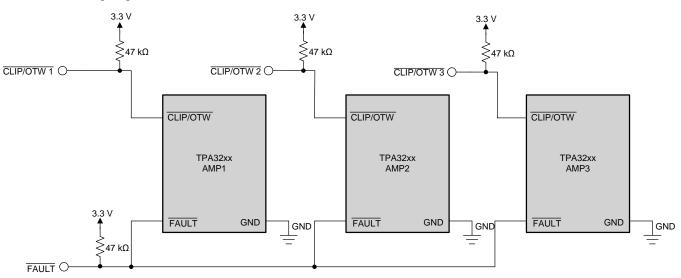

| 6 | Configuration 4: All Clip/OTW are Separate, all FAULT are Separate             | 6 |

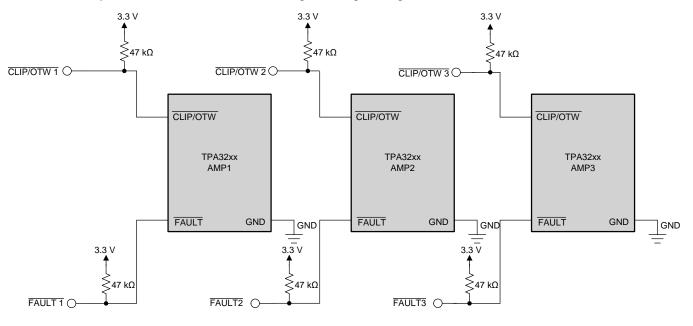

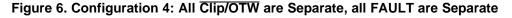

|   |                                                                                |   |

#### List of Tables

| 1 | Frequency Adjust Resistor Value for TPA3245, TPA3251, and TPA3255        | 3 |

|---|--------------------------------------------------------------------------|---|

| 2 | Master and Slave Inter-Channel Delay Settings                            | 3 |

| 3 | Number of Master, Slave 1, and Slave 2 Devices for a Multi-Device System | 3 |

# Trademarks

All trademarks are the property of their respective owners.

Oscillator Sync Pins

# 1 Oscillator Sync Pins

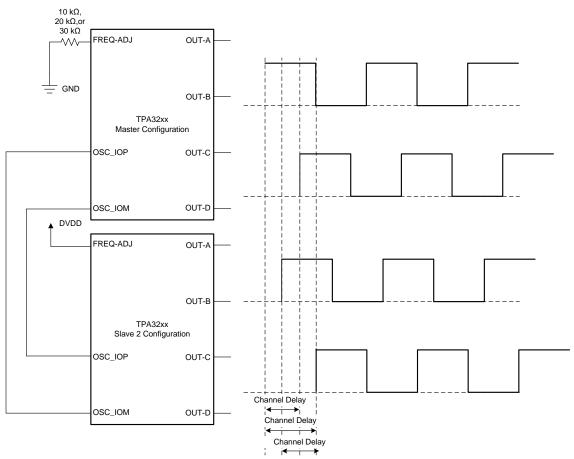

The TPA32xx family has OSC\_IOM and OSC\_IOP pins dedicated to synchronize multiple devices on a common clock. In this setup, one device acts as a master and the rest of the devices act as slaves. In addition, a delay is applied to the positive edge of the slave device PWM.

Copyright © 2017, Texas Instruments Incorporated

Figure 1. Oscillator Sync Pins Timing Diagram

#### **Benefits:**

2

By using the master and slave feature, inter-channel delay is automatically set up between the switching of the audio devices, which can be illustrated by no idle channels switching at the same time. While having no direct influence on the audio output, it will influence the switch timing to minimize noise coupling between the audio channels through the power supply. This will improve operating conditions for the power supply which, in turn, improves audio performance.

In summary: a master and slave system set up inter-channel delay between the audio channels which minimizes channels pulling power from the supply at the same time. This improves power supply performance, in turn, improving audio performance.

#### www.ti.com

## Implementation:

One master device is a requirement. For the master device, connect a resistor from FREQ\_ADJ to GND. The values for the resistor are found in the *Recommended Operating Conditions* of the TPA32xx data sheet. As an example, Table 1 shows the values for the frequency adjust resistor for the TPA3245, TPA3251, and TPA3255.

|                         |                                     |                      | MIN  | TYP | MAX  | Unit |

|-------------------------|-------------------------------------|----------------------|------|-----|------|------|

|                         | PWM frame rate programming register | Nominal; Master Mode | 9.9  | 10  | 10.1 |      |

| R <sub>(FREQ_ADJ)</sub> |                                     | AM1; Master Mode     | 19.8 | 20  | 20.2 | kΩ   |

|                         |                                     | AM2; Master Mode     | 29.7 | 30  | 30.3 |      |

For all slave devices, turn off the oscillator by pulling the FREQ\_ADJ pin to DVDD. All slave devices will have the same PWM frame rate as the master.

The inter-channel delay will be set up for a slave device depending on the polarity of the OSC\_I/O connections as follows:

- Slave 1 mode has normal polarity (master + to slave + and master to slave -)

- Slave 2 mode has reverse polarity (master + to slave and master to slave +)

|         |       | M1 = 0, M2 = 0,<br>2 × BTL Mode | M1 = 1, M2 = 0,<br>1 × BTL + 2 × SE Mode | M1 = 0, M2 = 1,<br>1 × PBTL Mode | M1 = 1, M2 = 1,<br>4 × SE Mode |

|---------|-------|---------------------------------|------------------------------------------|----------------------------------|--------------------------------|

|         | OUT_A | 0°                              | 0°                                       | 0°                               | 0°                             |

| Master  | OUT_B | 180°                            | 180°                                     | 180°                             | 60°                            |

| master  | OUT_C | 60°                             | 60°                                      | 0°                               | 0°                             |

|         | OUT_D | 240°                            | 120°                                     | 180°                             | 60°                            |

|         | OUT_A | 60°                             | 60°                                      | 60°                              | 60°                            |

| Slave 1 | OUT_B | 240°                            | 240°                                     | 240°                             | 120°                           |

| Slave   | OUT_C | 120°                            | 120°                                     | 60°                              | 60°                            |

|         | OUT_D | 300°                            | 180°                                     | 240°                             | 120°                           |

|         | OUT_A | 30°                             | 30°                                      | 30°                              | 30°                            |

| Slave 2 | OUT_B | 210°                            | 210°                                     | 210°                             | 90°                            |

| Slave Z | OUT_C | 90°                             | 90°                                      | 30°                              | 30°                            |

|         | OUT_D | 270°                            | 150°                                     | 210°                             | 90°                            |

Table 2. Master and Slave Inter-Channel Delay Settings

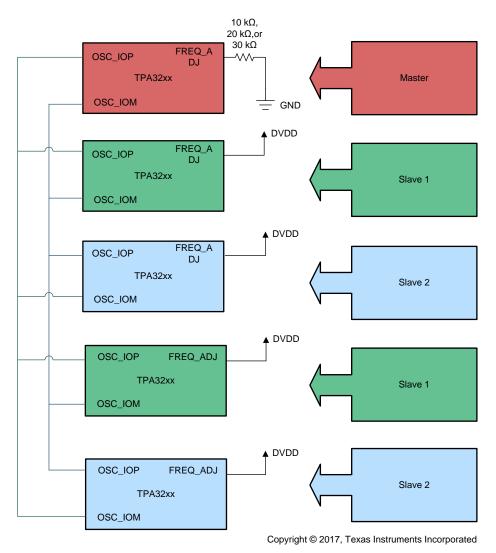

For best performance, use Table 3 to select how many devices should be in Slave 1 and Slave 2. In general, try to split the devices evenly into Slave 1 and Slave 2.

For example, if you have 5 devices, put one in master (FREQ\_ADJ through resistor to GND), two devices in Slave 1 (normal polarity, FREQ\_ADJ to DVDD) and two devices in Slave 2 (reverse polarity, FREQ\_ADJ to DVDD).

| Total Number of Devices | Number of Master Devices | Number of Slave 1 Devices | Number of Slave 2 Devices |

|-------------------------|--------------------------|---------------------------|---------------------------|

| 1                       | 1                        | -                         | -                         |

| 2                       | 1                        | 1                         | -                         |

| 3                       | 1                        | 1                         | 1                         |

| 4                       | 1                        | 2                         | 1                         |

| 5                       | 1                        | 2                         | 2                         |

| 6                       | 1                        | 3                         | 2                         |

| 7                       | 1                        | 3                         | 3                         |

www.ti.com

## Multi Device Clip/OTW and FAULT Pin

Figure 2. Master and Slave Configuration for a 5-Device System

# 2 Multi Device Clip/OTW and FAULT Pin

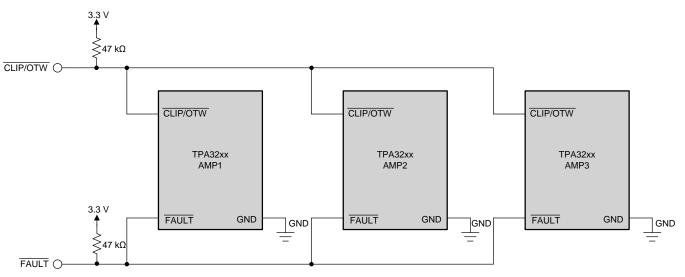

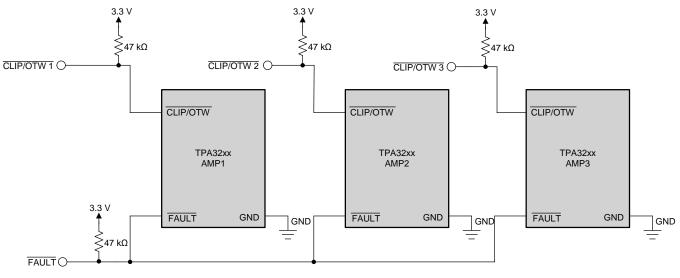

TPA32xx devices have Clip/OTW and FAULT pins to allow a system to know warning and errors occurring at the amplifier. When using multiple devices in a system, it may not be necessary to have separate Clip/OTW or FAULT signals for each device. The TPA32xx gives the option to tie these pins together across devices in order to simplify circuitry.

# Benefits:

When multiple are used in a system, the engineer has the option of tying the warning and error signal lines together in order to simplify the system. This can simplify a circuit by reducing the number of pins to monitor or the number of GPIOs needed on a microcontroller or processor as well as reduce the number of pullup resistors. This comes at the cost of making debug potentially harder. The ability to monitor each device and determine which device is faulting or entering Clip/OTW will be lost. Tying these signals together is equivalent to using an OR gate. For example, one could tie all of the Clip/OTW pins together and if just one device reached clipping, the Clip/OTW signal would go LOW (it is an active HIGH signal). If multiple devices went into clipping, the Clip/OTW signal also goes LOW. Up to 30 devices can have the Clip/OTW or FAULT pins tied together according the TPA32xx datasheet.

#### www.ti.com

# Implementation:

To keep signals to a minimum, all of the Clip/OTW pins could be tied together as well as all of the FAULT pins.

Copyright © 2017, Texas Instruments Incorporated

The Clip/OTW pins can be separated so one can diagnose which device is going into clipping or having an overtemperature warning. The FAULT pins can be tied together because you do not need to know when a particular device is going into FAULT.

Copyright © 2017, Texas Instruments Incorporated

## Multi Device Clip/OTW and FAULT Pin

www.ti.com

The Clip/OTW pins can be tied together because you do not need to distinguish when a particular device is going into clipping or has an OTW warning. The FAULT pins are separated so one can determine which device is going into FAULT.

Copyright © 2017, Texas Instruments Incorporated

One can also use separate Clip/OTW and FAULT for each device. This slightly complicates the circuit, but it allows you to see which device is causing each signal to go LOW.

Copyright © 2017, Texas Instruments Incorporated

There is no requirement that all signals be tied together or separated. Any combination is possible. It is up to the engineer to determine what the best way to configure the system is.

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated