# TMDS181 Schematic Checklist

#### **ABSTRACT**

This schematic checklist provides a brief explanation of each TMDS181 device pin and the recommended configuration of TMDS181 device pins for default operation. The TMDS181 is a digital video interface (DVI) or high-definition multimedia interface (HDMI) retimer. The TMDS181 supports four TMDS channels, audio return channel (SPDIF\_IN/ARC\_OUT), and digital display control (DDC) interfaces. The TMDS181 has the ability to be configured via pin strap or I2C. Use this information to check the connectivity for each TMDS181 device on a system schematic.

This document is intended to aid design at the system level for general applications but must not be the only resource used. In addition to this list, use the information from the TMDS181x 6 Gbps TMDS Retimer Data Sheet, TMDS181RGZ Evaluation Module User's Guide, and associated documents to gain a full understanding of device functionality.

|   | Contents                                              |   |

|---|-------------------------------------------------------|---|

| 1 | TMDS181 Schematic Checklist                           |   |

| 2 | References                                            | 5 |

|   | List of Figures                                       |   |

| 1 | External Termination Network for AC-coupled Interface | 5 |

| 2 | Audio Channel Implementation                          | 5 |

|   | List of Tables                                        |   |

| 1 | TMDS181 Schematic Checklist for Default Operation     | 1 |

| 2 | Enable (OE) Pin Timing Based on Capacitance           | 4 |

#### **Trademarks**

All trademarks are the property of their respective owners.

### 1 TMDS181 Schematic Checklist

Table 1. TMDS181 Schematic Checklist for Default Operation

| PIN NAME             | PIN NUMBER(S)    | PIN DESCRIPTION                       | RECOMMENDATION                                  | ADDITIONAL<br>COMMENT |

|----------------------|------------------|---------------------------------------|-------------------------------------------------|-----------------------|

| MAIN LINK INPUT PINS |                  |                                       |                                                 |                       |

| IN_D[0:2]p/n         | 8, 9, 5, 6, 2, 3 | Main link differential input          | Direct connection from connector/GPU to TMDS181 |                       |

| IN_CLKp/n            | 11, 12           | Main link clock<br>differential input | Direct connection from connector/GPU to TMDS181 |                       |

# Table 1. TMDS181 Schematic Checklist for Default Operation (continued)

| PIN NAME             | PIN NUMBER(S)          | PIN DESCRIPTION                                     | RECOMMENDATION                                                                                                                                                                                                                                                                          | ADDITIONAL<br>COMMENT                                                                                                                                                      |

|----------------------|------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAIN LINK OUTPUT PII | NS                     |                                                     |                                                                                                                                                                                                                                                                                         |                                                                                                                                                                            |

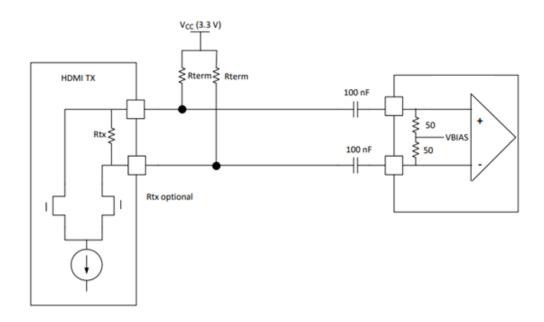

| OUT_D[0:2]p/n        | 28, 29, 31, 32, 34, 35 | TMDS data differential output                       | Direct connection from TMDS181 to connector/receiver                                                                                                                                                                                                                                    | Output can be AC-coupled, but require external termination network, see Figure 1. TMDS181 output amplitude needs to be increased to compensate for the double termination. |

| OUT_CLKp/n           | 26, 25                 | TMDS clock differential output                      | Direct connection from<br>TMDS181 to<br>connector/receiver                                                                                                                                                                                                                              | Output can be AC-coupled, but require external termination network, see Figure 1. TMDS181 output amplitude needs to be increased to compensate for the double termination. |

| DDC PINS             |                        |                                                     |                                                                                                                                                                                                                                                                                         |                                                                                                                                                                            |

| SDA_SRC              | 47                     | Source side TMDS bidirectional DDC data line        | Snoop mode, tie it to GND                                                                                                                                                                                                                                                               |                                                                                                                                                                            |

| SCL_SRC              | 46                     | Source side TMDS<br>bidirectional DDC clock<br>line | Snoop mode, tie it to GND                                                                                                                                                                                                                                                               |                                                                                                                                                                            |

| SDA_SNK              | 39                     | Sink side TMDS<br>bidirectional DDC data<br>line    | SDA/SCL from the source is connected directly to the SDA/SCL sink. The TMDS181 will need its SDA_SNK and SCL_SNK pins connected to this link in order to correctly configure the TMDS_CLOCK_RATIO_STATUS bit.Sink application: 47k pull-ups to 5V Source application: 2k pull-ups to 5V | Consider adding an external I2C buffer for DDC capacitance isolation                                                                                                       |

| SCL_SNK              | 38                     | Sink side TMDS<br>bidirectional DDC clock<br>line   | SDA/SCL from the source is connected directly to the SDA/SCL sink. The TMDS181 will need its SDA_SNK and SCL_SNK pins connected to this link in order to correctly configure the TMDS_CLOCK_RATIO_STATUS bit.Sink application: 47k pull-ups to 5V Source application: 2k pull-ups to 5V | Consider adding an external I2C buffer for DDC capacitance isolation                                                                                                       |

Table 1. TMDS181 Schematic Checklist for Default Operation (continued)

| PIN NAME        | PIN NUMBER(S) | PIN DESCRIPTION                               | RECOMMENDATION                                                                                                                                                                                       | ADDITIONAL<br>COMMENT                                                                                  |

|-----------------|---------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| HOT PLUG DETECT | PINS          |                                               |                                                                                                                                                                                                      |                                                                                                        |

| HPD_SNK         | 33            | Hot plug detect input from sink side          | Connect to HPD output for the display and connector. For snoop mode: Connect directly to Sink's/GPU's(Check GPU supported voltage) directly connected HPD line HPD_SNK has internal 190 k pull-down. | Consider adding an external switch to isolate potential leakage voltage from sink HPD when sink is off |

| HPD_SRC         | 4             | Hot plug detect output to source side         | If HPD_SRC goes to the source connector a level shifter from 3.3 V to 5 V is needed. If HPD_SRC goes to GPU, check supported GPU voltages. If HPD snoop mode is implemented, leave HPD_SRC floated.  |                                                                                                        |

| AUDIO RETURN CH | ANNEL PINS    |                                               |                                                                                                                                                                                                      |                                                                                                        |

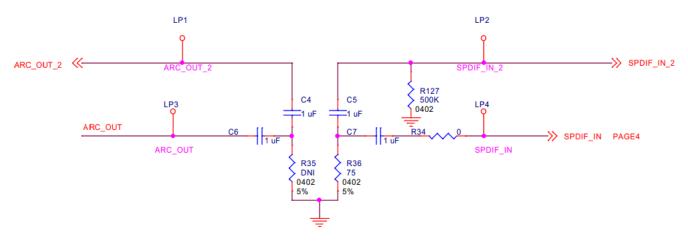

| SPDIF_IN        | 45            | SPDIF signal input                            | If not needed: 500 k<br>pull-down.<br>Implementation<br>dependent, see Figure 2<br>SPDIF_IN -> HDMI sink<br>SPDIF_IN_2 -><br>TMDS181                                                                 |                                                                                                        |

| ARC_OUT         | 44            | Audio return channel output                   | if not needed: NC<br>Implementation<br>dependent,see Figure 2                                                                                                                                        |                                                                                                        |

| CONTROL PINS    |               |                                               | +                                                                                                                                                                                                    | +                                                                                                      |

| OE              | 42            | Enable/reset pin                              | Start with 0.2uF, tune<br>depending on the RC<br>time constant delay (Tr)<br>requirement in regard to<br>power ramp up time                                                                          | See Table 2 for different timing values based on capacitance.                                          |

| Vsadj           | 22            | TMDS-compliant voltage swing control resistor | Start with 7.06 k resistor<br>to ground, resistor value<br>tuning depends on<br>compliance result                                                                                                    |                                                                                                        |

| SCL_CTL         | 15            | I2C clock signal                              | 2 k pull-ups to 3.3 V or value required by I2C master                                                                                                                                                |                                                                                                        |

| SDA_CTL         | 16            | I2C data signal                               | 2 k pull-ups to 3.3 V or value required by I2C maste                                                                                                                                                 |                                                                                                        |

| I2C_EN/PIN      | 10            | I2C control mode                              | 65 k pull-down for pin<br>strap mode<br>65 k pull-up for I2C<br>mode                                                                                                                                 |                                                                                                        |

| EQ_SEL/A0       | 21            | Input receive equalization                    | NC for adaptive EQ in pin strap mode                                                                                                                                                                 | 65 k pull-up or pull-down in I2C mode                                                                  |

| A1              | 27            | Input receive equalization                    | NC in pin strap mode                                                                                                                                                                                 | 65 k pull-up or pull-down in I2C mode                                                                  |

| SIG_EN          | 17            | High address I2C bit for I2C programming      | 65 k pull-down or pullup<br>to enable/disable signal<br>detector                                                                                                                                     | Recommend 65 k pull-<br>down to disable signal<br>detect circuit                                       |

## Table 1. TMDS181 Schematic Checklist for Default Operation (continued)

| PIN NAME    | PIN NUMBER(S)      | PIN DESCRIPTION                      | RECOMMENDATION                                                                                      | ADDITIONAL<br>COMMENT                                         |

|-------------|--------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| PRE_SEL     | 20                 | Signal detector circuit enable       | PRE_SEL = L: -2dB<br>PRE_SEL = NC: 0dB<br>PRE_SEL = H:<br>Reserved                                  | Leave it floating when I2C_EN/PIN = high, control through I2C |

| TX_TERM_CTL | 36                 | Transmit termination control         | NC for automatic Tx termination                                                                     |                                                               |

| SWAP/POL    | 1                  | Input lane SWAP and polarity control | Default NC, 65 k pull-up or pull-down if needed                                                     |                                                               |

| POWER PINS  |                    |                                      |                                                                                                     |                                                               |

| vcc         | 13, 43             | 3.3 V power supply                   | One 100 nF cap on each power pin. 4.7 pF and 10 pF on each power node. One bulky cap per power node |                                                               |

| VDD         | 12, 23, 24, 37, 48 | 1.1 V power supply                   | One 100nF cap on each power pin. 4.7pF and 10pF on each power node. One bulky cap per power node    |                                                               |

|             | 7, 19 ,41, 30      | Ground                               | Connect to board ground                                                                             |                                                               |

| Thermal Pad | 49                 | Ground                               | Connect to board ground                                                                             |                                                               |

## Table 2. Enable (OE) Pin Timing Based on Capacitance

| RISE TIME (T <sub>r</sub> ) (ms) | CAPACITOR VALUE (μF) |  |

|----------------------------------|----------------------|--|

| 25                               | 0.1                  |  |

| 50                               | 0.2                  |  |

| 100                              | 0.4                  |  |

| 200                              | 0.8                  |  |

| 500                              | 2                    |  |

www.ti.com References

Figure 1. External Termination Network for AC-coupled Interface

Figure 2. Audio Channel Implementation

## 2 References

- TMDS181x 6 Gbps TMDS Retimer Data Sheet

- TMDS181RGZ Evaluation Module User's Guide

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated