# Application Report **A System Evaluation of CAN Transceivers**

#### Sam Broyles

#### ABSTRACT

This application note presents the results of an examination of a two-node controller area network using the SN65HVD230 3.3-V CAN transceiver and the TMS320F243, 16-bit, 5 V fixed point DSP with integrated CAN controller. ISO-11898 (CAN) compliance testing is performed with an analysis of network errors under various experimental conditions, such as bus length, signaling rate, network loading, and common-mode voltage.

## **Table of Contents**

| 1 Irademarks                 |   |

|------------------------------|---|

| 2 Introduction               | 1 |

| 3 CAN Basics                 |   |

| 4 The CAN Tranceivers        |   |

| 5 CAN Network Errors         | 4 |

| 6 Analysis of Network Errors | 4 |

| 7 Method                     | 5 |

| 8 Results                    |   |

| 9 Summary                    |   |

| 9 Summary<br>10 References   |   |

| 11 Revision History          |   |

|                              |   |

## 1 Trademarks

All trademarks are the property of their respective owners.

#### 2 Introduction

A controller area network (CAN) is constructed to test transceivers in a real CAN system to better understand and develop CAN devices. This study further investigates the electrical-layer performance of the bus and the resulting system limitations of the network.

1

# **3 CAN Basics**

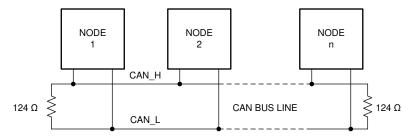

ISO11898 describes the physical-layer implementation of CAN. This specification describes a twisted-wire pair bus with 120- $\Omega$  line impedance, and differential signaling at a rate up to 1 Mbps on a 40-meter bus with multipoint topology. Longer bus lengths are expected to have slower maximum signaling rates. A network with multipoint topology is constructed with multiple transceivers on the same bus lines, as shown in Figure 3-1.

Figure 3-1. Multipoint Topology of a CAN Bus

CAN messages may be transmitted on-demand by any node whenever the bus is free. Each message is received by all nodes on the network, including the node that sent the message. This broadcasting of data allows multiple nodes to use the transmitted data. It also allows the sending node to monitor the bus for errors. If two or more nodes attempt to transmit simultaneously, the lower priority message is overwritten in the collision and this lower priority node will halt transmission upon sensing overwritten bits in its message identifier. The message is then re-transmitted when the bus is again free. This non-destructive process is called bit-wise arbitration.

Every node on the network reads the identifier of a message, and each node independently determines if the message is to be ignored or processed. Since the identifier is specific to the contents of the message rather than the identity of the originating node, new nodes may be added to the network, even while the network is functioning, without modifying the program of any existing node on the network.

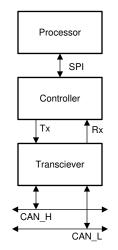

A CAN node is comprised of three basic parts: a processor, a network controller, and a transceiver, as shown in Figure 3-2. The processor may be in the form of a general-purpose microprocessor or a digital signal processor (DSP) and may have the CAN controller incorporated into the same chip.

Figure 3-2. Structure of a CAN Node

CAN protocol is negotiated within the controller, decreasing the load on the processor and simplifying the controller-processor interface to a set of mailboxes and interrupts. Integrating the CAN controller into the processor reduces the read/write time from the processor to the controller, further decreasing the load on the processor and increasing overall system performance. Integrating the CAN controller into the processor also saves board space, simplifies board layout, and reduces total chip cost.

## 4 The CAN Tranceivers

The role of the transceiver is simply to drive and detect data to and from the bus. It converts the single-ended logic used by the controller to the differential signal transmitted over the bus. It also determines the bus logic state from the differential voltage, rejects the common-mode noise, and outputs a single-ended logic signal to the controller. Additionally, many transceivers provide features to isolate the controller from bus conditions such as electrostatic discharge (ESD) or electrical over-stress (EOS) damage, so that a node would be protected if an extreme bus condition were to destroy the transceiver.

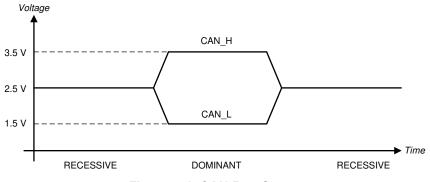

The transceiver distinguishes between two bus logic states, dominant and recessive. A recessive bit is defined as CAN\_H being less than CAN\_L+.5V. A dominant bit is defined as CAN\_H being more than CAN\_L+.9V. Figure 4-1 illustrates the nominal case. Since dominant bits overwrite recessive bits, CAN manages message collision through the process of bit-wise arbitration as described earlier.

Voltage that is common to both lines is referred to as common-mode voltage. It may appear as a time-varying voltage, such as coupled noise from an electric motor, or as a steady-state voltage from an offset ground condition between equipment. The use of twisted-pair cable and differential data transmission causes external noise from neighboring signal lines or noise sources to be coupled onto both lines (common-mode) and rejected by the differential receiver. Differential data transmission also radiates less electromagnetic noise energy than single-ended signals due to the cancellation between the complementary bus signals. (See Reference 1)

## **5 CAN Network Errors**

CAN protocol specifies five different types of network errors: bit errors, stuff errors, CRC errors, form errors, and ACK errors. A bit error is detected when a transmitting node monitors a bit value different than what it is transmitting. A stuff error occurs when the bit-stuffing rule is violated – a bit of opposite value must be inserted immediately following any series of five consecutive bits of the same value in a message. A cyclic redundancy check (CRC) error occurs when a receiving node receives a different CRC sequence than anticipated. (Note that all nodes independently calculate the CRC sequence from the data field). A form error occurs when a field contains an illegal bit value. Finally, an acknowledgment (ACK) error occurs when the transmitter does not monitor a dominant bit in the ACK slot to signify that the message has been received properly by another node. (See Reference 2)

When a node detects a bus error, it transmits an error frame consisting of six dominant bits followed by eight recessive bits. Multiple nodes transmitting an error frame do not cause a problem because the first recessive bits are overwritten. The result remains as six dominant bits followed by eight recessive bits, and causes the bus to be safely reset before normal communications recommence.

The CAN protocol provides a means of fault confinement by requiring each node to maintain separate receive and transmit error counters. Either counter is incremented by 1 or 8, depending on the type of error and conditions surrounding the error. The receive error counter is incremented for errors during message reception, and the transmit error counter is incremented for errors during message transmission (for further details, see **Reference 2**). When either counter exceeds 127, the node is declared error-passive, which limits it from sending any further dominant error frames. When the transmitted error count exceeds 255, the node is declared bus-off, which restricts the node from sending any further transmissions. The receive and transmit error counters are also decremented by one each time a message is received or transmitted without error, respectively. This allows a node to return from error-passive mode to error-active mode (normal transmission mode) when both counters are less than 128. The node may also return to error-active mode from bus-off mode after having received 128 occurrences of 11 consecutive recessive bits. Overall, a network maintains constant transmit and receive error counters if it averages eight properly transmitted or received messages for each error that occurs during transmission or reception, respectively.

## 6 Analysis of Network Errors

A Tektronix 784D oscilloscope with Tektronix P6243 1 GHz single-ended probe is used for network analysis. With careful choice of message identifiers and data fields, messages can be visually associated with the transmitting node, and current bus status may be determined visually. This assures, by observation, that each node is participating during an experiment. Additionally, the transmission lines from the controllers to the transceivers are useful for monitoring the participation of each node during arbitration and acknowledgment bits.

A more detailed record of bus activity may be found in the status and control registers of the processors that are reviewed after each experiment. Though the error counters are incremented and decremented through a complex series of rules, it is sufficient to note error status and types of errors that occur, to assess bus performance under a set of experimental conditions.

In a two-node experiment, if one node enters the bus-off state, the bus would become silent, or the other node would continue to retransmit until the reception of a proper ACK bit. Either case represents experimental conditions, causing a heavily disturbed bus that is not recommended for use in a final application.

## 7 Method

The basic methodology adapted for testing a 2-node CAN network is to send a million messages from node A to node B, then from node B to node A, or until one node goes to bus-off condition. In either case, the error registers of the node are analyzed as a means of measuring bus performance of a transceiver. Excessive errors are indicative of an experimental condition that is not recommended for application.

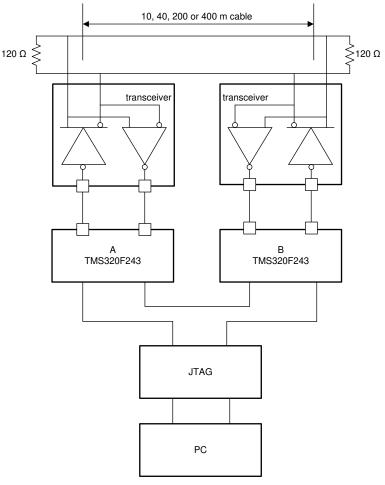

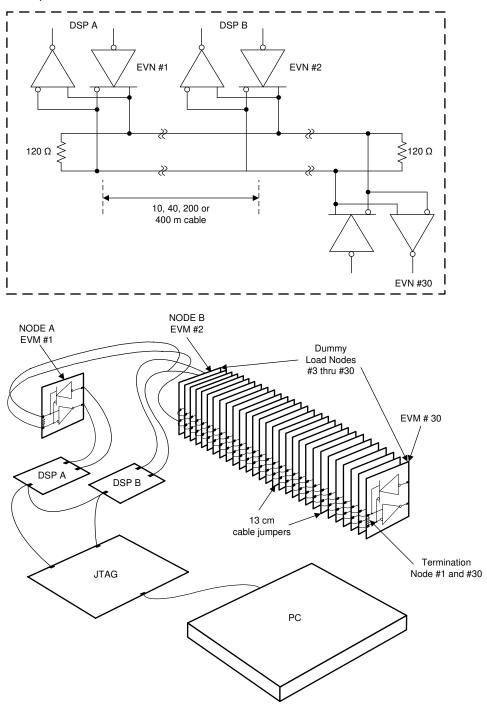

Three different networks are tested to study device performance; each network is tested with Texas Instruments SN65HVD230 3.3-V transceivers. Each network is tested with 10-m, 40-m, 200-m, and 400-m of inexpensive 120- $\Omega$  impedance twisted-pair AWG 24 cable with grounded shielding and 120- $\Omega$  terminating resistors on either end. Each network is tested at speeds of 62.5, 125, 250, 500, 625, 800, 1000, 1250, and 2000 kbps, or until the network has a fatal error failure. The first network is comprised of 2 nodes (Figure 7-1).

Figure 7-1. Experimental 2-Node CAN Bus

Method

The second network adds 28 additional dummy nodes between node B and the second terminating resistor (see Figure 7-2). These nodes are powered and remain in a recessive state to load the network without participating in CAN communication. (Note that the dummy nodes are each separated by 13-cm cables that add to the total length of the network.)

Figure 7-2. Experimental 30-Node CAN Bus

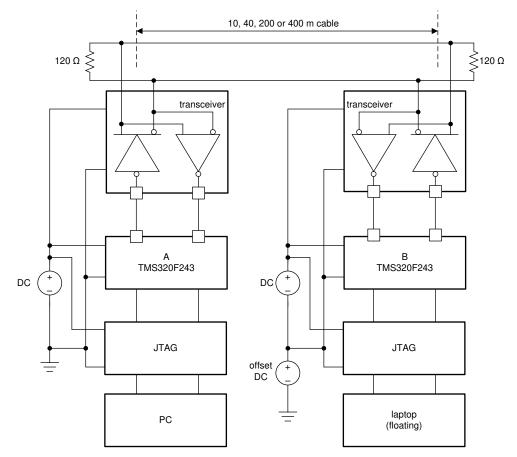

The third network adds a steady-state common-mode offset voltage between two nodes, as seen in Figure 7-3. This simulates an offset ground condition across a CAN network. Two different PCs are required to communicate with the processors due to ground line of the JTAG connection. The offset ground power supply is set to 7 Vdc.

Figure 7-3. Experimental 2-Node CAN Bus With Offset Grounds

7

Method

#### Results

## 8 Results

With a 10-meter cable, the first network (Figure 7-1) performs flawlessly at 1250 kbps, but at 2000 kbps, ACK and form errors cause a fatal bus condition. This pattern continues on this network for 40-m, 200-m, and 400-m bus lengths (see Table 8-1).

| Cable Length | Max Bit Rate | Fatal Bit Rate | Error Types Observed |  |

|--------------|--------------|----------------|----------------------|--|

| 10 m         | 1250 kbps    | 2000 kbps      | ACK, Form            |  |

| 40 m         | 800 kbps     | 1000 kbps      | ACK, Form            |  |

| 200 m        | 125 kbps     | 250 kbps       | ACK, Form            |  |

| 400 m        | 62.5 kbps    | 1250 kbps      | ACK, Form            |  |

#### Table 8-1. Results of First Network

The second network (Figure 7-2) with additional dummy nodes appears to perform the same as the first network (see Table 8-2). However with a 200-meters bus, the network performs error-free at 62.5 kbps and at 125 kbps. Stuff-bit errors and bit errors are observed, but it is not until the 250 kbps rate that missing ACK bits and form errors become frequent enough to cause a bus-off condition. Likewise, at 400-meters, the network encounters missing ACK bits and bad CRC values at 62.5 kbps. But, it is not until 125 kbps that missing ACK bits and form errors become frequent enough to cause a bus-off condition.

| Cable Length | Max Bit Rate | Fatal Bit Rate | Error Types Observed |  |

|--------------|--------------|----------------|----------------------|--|

| 10 m         | 1250 kbps    | 2000 kbps      | ACK, Form            |  |

| 40 m         | 800 kbps     | 1000 kbps      | ACK, Form            |  |

| 200 m        | 125 kbps     | 250 kbps       | ACK, Form            |  |

| 400 m        | 62.5 kbps    | 1250 kbps      | ACK, Form            |  |

#### Table 8-2. Results of Second Network

With a 10-meter cable, the third network (Figure 7-3) performs flawlessly at 800 kbps, but at 1000 kbps, Bit and form errors cause a fatal bus condition (see Table 8-3). With a 40-meter cable, the network performs flawlessly at 500 kbps, but at 625 kbps, Bit and form errors cause a fatal bus condition. With a 200-meter cable, it performs flawlessly at 125 kbps, but at 250 kbps, ACK and form errors cause a fatal bus condition. Similarly, on a 400-meter cable, the network performs flawlessly at 62.5 kbps, but crashes at 125 kbps, due to ACK and form errors.

#### Table 8-3. Results of Third Network

| Cable Length | Max Bit Rate | Fatal Bit Rate | Error Types Observed |

|--------------|--------------|----------------|----------------------|

| 10 m         | 800 kbps     | 1000 kbps      | Form, Bit            |

| 40 m         | 500 kbps     | 625 kbps       | ACK, Bit             |

| 200 m        | 125 kbps     | 250 kbps       | ACK, Form            |

| 400 m        | 62.5 kbps    | 1250 kbps      | ACK, Form            |

## 9 Summary

The method of transceiver evaluation described begins with the construction of a CAN network. Networks are constructed with various system parameters in mind, including cable length, network loading of other transceivers, and offset ground conditions between CAN nodes. Each network is tested at successively higher speeds until errors are observed to cause the network to halt communication.

As seen in the results, it is possible to observe network errors that do not cause a system shut down. CAN network protocol specifies a system of rules to increment or decrement the receive and transmit error counters. To summarize, the single occurrence of an error is quickly forgotten, but a momentary loss of communication quickly shuts down the problem node. An analysis of the results suggests that a nonfatal error is more likely to occur as a network nears its maximum speed.

This study also demonstrates that maximum speed is much more sensitive to increasing cable length than increasing the network load or offsetting the ground of different network nodes.

Note

The choice of CAN transceiver can also influence the achievable range. Newer, higher-speed transceivers like TCAN332 or TCAN1042 would be likely to achieve longer distances compared to SN65HVD230.

Click here to view the entire CAN transceiver portfolio, including new products and technical resources.

#### 10 References

- 1. Application report: *Reducing Electromagnetic Interference with Low Voltage Differential Signaling* (Literature Number SLLA030)

- 2. ISO-11898 CAN Specification 2.0

- 3. Application report: Comparing Bus Solutions (Literature Number SLLA067)

- 4. Controller Area Network, Basic Protocols, Chips and Applications; Dr. Konrad Etschberger, ISBN 3-00-007376-0

- 5. CAN Systems Engineering, From Theory to Practical Applications; Wolfhard Lawrenz, ISBN 0-387-94939-9

#### **11 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| С | Changes from Revision * (March 2002) to Revision A (July 2018) |   |  |

|---|----------------------------------------------------------------|---|--|

| • | Added NOTE and new sentence to the end of Section 9            | 9 |  |

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated