# Isolated RS-485 to RS-485

Mitesh Patel

## ABSTRACT

This application note presents the idea of achieving all-port isolation in an existing non-isolated RS-485-to-RS-485 communication link without delving into the details of the protocol between the nodes.

#### Contents

|   | Introduction             |   |

|---|--------------------------|---|

|   | Need of Isolation        |   |

| 3 | System Block Diagram     | 2 |

| 4 | Circuit Functionality    | 3 |

| 5 | Software (C-Source Code) | 3 |

| 6 | Applications             | 5 |

| 7 | References               | 5 |

|   |                          |   |

#### Trademarks

All trademarks are the property of their respective owners.

## 1 Introduction

The RS-485 is one of the most widely used physical-layer bus designs for most industrial communication. Some of the key features include:

- Long distance links up to 4000 feet

- · Bidirectional communication possible over a single pair of twisted cables

- Differential transmission increases noise immunity and decreases noise emissions

- Multiple drivers and receivers can be connected on the same bus

- · Wide common-mode range allows for differences in ground potential between drivers and receivers

In some cases, RS-485 is used for peer-to-peer communication because of its ability to work differentially and its capability of better noise rejection.

In spite of utmost care in RS-485 designs, a system may fail for the following reasons:

- · Excessive potential difference between interconnecting systems

- Electrostatic discharge (ESD)

- Electrical overstress

- Short-circuit event

- Lighting

- Electrical surges

Some failures may not be the potential failures but system-level failures because of ground-loop interference, high noise levels, or common-mode potential.

#### 2 Need of Isolation

To avoid the previously listed issues, designers use an isolated-bus architecture. Reasons for using an isolated-bus architecture include:

- To avoid ground-loop interference

- To protect one system from another system; these systems may be working at different potentials

- To avoid any potential hazards because of wrong wiring or excessive potential difference

- To avoid noise from one system to another system or to protect the system from electrical noise, electrical surges, ESD, and other causes of system failure

The purpose of this application note is to discuss the implementation of isolation on a half-duplex RS-485 to RS-485 system. This application note shows how to design peer-to-peer half-duplex or multinode isolated RS-485 communication. Because half-duplex RS-485 communication chips require the data-transmit enable and data-receive enable signals for data transmission and reception, isolation is not simple to achieve. This application note discusses how to achieve this functionality using a low-cost design that features a microcontroller (MSP430G2231), isolated RS-485 (ISO3088), isolated DC-DC converter (DCP022405P), and low-dropout (LDO) regulator (TLV70033).

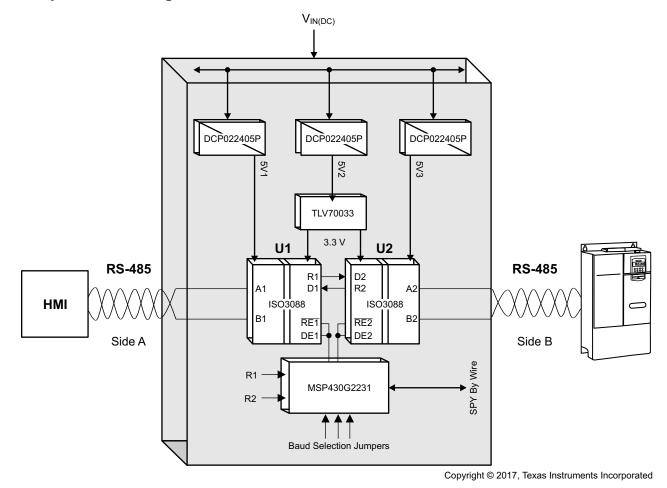

#### 3 System Block Diagram

Figure 1. System Block Diagram

As shown in Figure 1, isolation at the system level offers all port isolation which includes:

- Dual isolation between RS-485 side A to RS-485 side B

- Isolation between input supply to RS-485 side A

2

Isolation between input supply to RS-485 side B

The typical system shown in Figure 1 is a peer-to-peer system but can also be used for master-slave applications. In Figure 1, communication can be initiated from either side, so both of the ISO3088 devices must be in a receiving state when idle. In this diagram, the MSP430G2231 device is vital for data-direction control with precise timing. This timing can be varied depending on the baud rate selection. Two GPIOs of the microcontroller are configured as external GPIO interrupts and two GPIOs are configured in output mode as data-direction control.

The configuration is as follows:

- Signal R1 is connected to PORT1.0 (interrupt is from high to low).

- Signal R2 is connected to PORT1.1 (interrupt is from high to low).

- Output PORT1.2 is connected to the DEx and REx signal of U1.

- Output PORT1.3 is connected to the DEx and REx signal of U2.

- Three GPIOs are used as baud rate selection (optional).

# 4 Circuit Functionality

Data received from side A generates the interrupt on PORT1.0 and software logic puts PORT1.3 in logichigh mode, which puts U2 in transmission mode. Therefore data communication occurs from side A to side B. When either of the configured interrupt pins receives an interrupt (high to low) as a start-up bit, the microcontroller puts the other device in transmission mode for a period of more than 1 byte (11 bits: 1 start + 8 data + 2 stop) time. For each high-to-low transition, transmission mode will be extended by one byte time.

As long as the chain of data continues or a bulk transfer from one side to the other side occurs, the direction control pin of the other side remains in transmission mode for the entire length of time. After the transmission from one side to another side, the direction control pin switches from high to low and both sides are ready to receive a signal.

Because any device (microcontroller or microprocessor) requires some time to respond to a received query, the delay in response is typically more than the 1 byte time in most communication systems. The block diagram (Figure 1) was tested up to 187.5 kBd for peer-to-peer communication without any data loss.

# 5 Software (C-Source Code)

The c-source code is:

```

/* Iolated RS-485 to RS-485 with All port isolation

* Tested with Seimens HMI & AC drive for Baud rate of 187.5K in peer to peer configuration

* Schematic is based on MSP430G2231 but software is tested with MSP430F2013

*/

#include <msp430F2013.h>

#include <stdint.h>

#define CRYSTAL

16000000UL

((CRYSTAL * (TRANSMIT_BIT) / BAUD_RATE))

((CRYSTAL * (TRANSMIT_BIT - 1) / BAUD_RATE))

BYTE_TIME_N_MINUS_1)/2 )+ BYTE_TIME_N_MINUS_1)

#define RECEIVE_1_ENABLE

P10UT &=~0x08

#define RECEIVE_2_ENABLE

P10UT &=~0x04

#define TRANSMIT 1 ENABLE

P10UT |= 0x08

```

www.ti.com

```

Software (C-Source Code)

```

```

#define TRANSMIT_2_ENABLE

Plour = 0x04

unsigned char int_flag_1 = 0;

unsigned char receive_enable_flag = 0;

void main(void)

{

unsigned int i = 200;

WDTCTL = WDTPW + WDTHOLD;

// Stop WDT

// Enable WDT

interrupt

//======Port initialisation========

// Set P1.0 to as ADC channel

P1DIR = 0xFC;

P1OUT = 0 \times 0F;

P1REN = 0x03;

Plie | = 0x03;

// P1.4 interrupt enabled

Plies = 0x03;

// P1.4 Hi/lo edge

P1IFG &= ~0x03;

// P1.4 IFG cleared

while(i > 0)

// Power On delay for supply to stabilize

{

__delay_cycles(5000);

i--;

}

DCOCTL = CALDCO_16MHZ;

BCSCTL1 = CALBC1_16MHZ;

TACCR0 = 940;

//BYTE_TIME;

TACCTLO = CCIE;

Plour &=\sim 0 \times 0 C;

_BIS_SR(GIE + LPM1_bits);

// Enter LPM4 w/interrupt

}

// Port 1 interrupt service routine

#pragma vector=PORT1_VECTOR

__interrupt void Port_1(void)

{

P1IFG = 0;

if((P1IN & 0x01)==0)

{

TRANSMIT_1_ENABLE;

}

if((P1IN & 0x02)==0)

{

TRANSMIT_2_ENABLE;

}

TAR = 0;

TACTL = TASSEL_2 + MC_1;

}

#pragma vector=TIMERA0_VECTOR

__interrupt void TIMERA0(void)

{

TACTL = 0;

RECEIVE_1_ENABLE;

RECEIVE_2_ENABLE;

}

```

4

#### www.ti.com

**NOTE:** The user can modify the program for a multibaud rate design. Add the look-up table for the timer counter which counts depending on the baud rate. The counts for the TACCR0 register must be changed.

The user might want to consider a multioutput flybuck or flyback topology for isolated power supply.

A biasing network can be added to keep the RS-485 bus in a known state when all the drivers are in receiving mode, or when the biasing network is changing roles.

# 6 Applications

Many industrial systems require isolation between various end equipments which may not have isolated RS-485 ports. The solution present in this application note can be good option to achieve the required isolation.

This solution can also work as an RS-485 link extension or buffer for long distance communication with isolation.

# 7 References

For related documentation see the following:

- Texas Instruments, ISO308x Isolated 5-V Full- and Half-Duplex RS-485 Transceivers data sheet

- Texas Instruments, DCP02x 2-W, Isolated, Unregulated DC/DC Converter Modules data sheet

- Texas Instruments, MSP430G2x31, MSP430G2x21 Mixed Signal Microcontroller data sheet

- Wikibooks, Open books for an open world, "RS-485 Technical Manual, Serial Programming/RS-485," https://en.wikibooks.org/wiki/Serial\_Programming/RS-485#RS-485

5

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated