# **TUSB2XX** Implementation Guide

Michael Walker

### ABSTRACT

This document is for platform designers implementing the TUSB2XX family of USB 2.0 redrivers. The Family consists of the TUSB211, TUSB212, TUSB213, TUSB214, and TUSB215. Detailed information for each device can be found in each devices separate datasheet.

This document gives the differences and similarities between the TUSB2XX devices. This document provides board design recommendations for the various devices and features for designing with the TUSB2XX devices. This document is intended for developers familiar with high-speed PCB design and layout. Knowledge of the USB 2.0 protocol is recommended as well. The following layout recommendations should not be considered the sole method of implementation, but rather as a guide. The preferences of the individual developer, requirements of the design, number of components in the circuit, as well as many other factors can influence each individual layout.

### Contents

| 1 | Introduction                    | 2  |

|---|---------------------------------|----|

| 2 | Differences Between Devices     | 2  |

| 3 | General Implantation Guidelines | 4  |

|   | Layout Differences and Examples |    |

| 5 | Testing                         | 7  |

| 6 | Frequently Asked Questions      | 10 |

| 7 | References                      | 12 |

### List of Figures

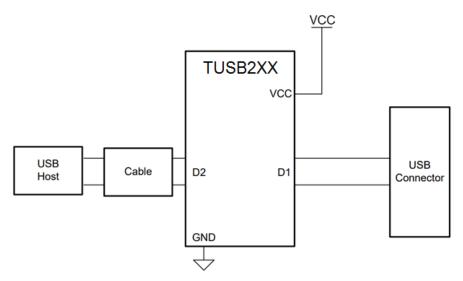

| 1  | Simplified Schematic                                                                       | 2  |

|----|--------------------------------------------------------------------------------------------|----|

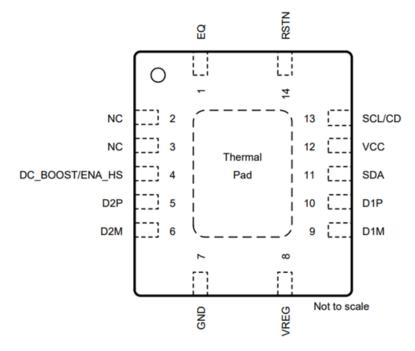

| 2  | RGY Package 14 Pin (VQFN) Top view (TUSB213, TUSB215)                                      | 3  |

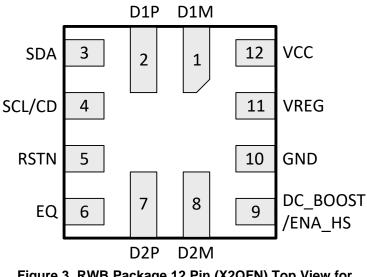

| 3  | RWB Package 12 Pin (X2QFN) Top View for TUSB211, TUSB212, TUSB214 (no DC_BOOST on TUSB211) | 3  |

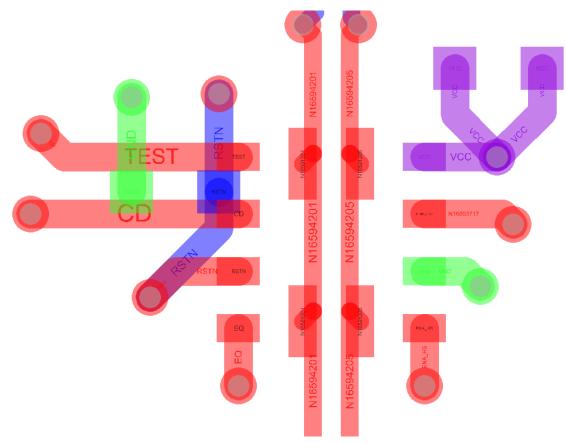

| 4  | TUSB211, TUSB212 and TUSB214 Layout Example                                                | 5  |

| 5  | TUSB213 and TUSB215 Layout Example                                                         | 6  |

| 6  | USB 2.0 High Speed Test Upstream Signal Quality Testing                                    | 8  |

| 7  | USB-IF HS Electrical Test Tool                                                             | 8  |

| 8  | USB 2.0 Device High-Speed Test Fixture with Embedded Host                                  | 9  |

| 9  | Pre-Channel and Post-Channel                                                               | 10 |

| 10 | Falling Edge Eye Diagram                                                                   | 11 |

| 11 | Leading and Trailing Edge                                                                  | 12 |

#### List of Tables

| 1 | TUSB2XX EQ and Boost settings | 1 |

|---|-------------------------------|---|

|   |                               |   |

|   |                               |   |

### Trademarks

All trademarks are the property of their respective owners.

### 1 Introduction

The TUSB2XX family of devices is USB High-Speed (HS) signal conditioners, designed to compensate for ISI signal loss in a transmission channel.

TUSB2XX devices have a patented design which is agnostic to USB Low Speed (LS) and Full Speed (FS) signals. LS and FS signal characteristics are unaffected by the TUSB2XXs while HS signals are compensated.

Programmable signal AC boost permits fine tuning device performance to optimize High Speed signals at the connector. This helps to pass USB High Speed electrical compliance tests.

In addition, The TUSB2XXs are compatible with the USB On-The-Go (OTG) and Battery Charging (BC) protocols.

### 1.1 Typical System Implementation

Figure 1. Simplified Schematic

### 2 Differences Between Devices

### 2.1 DC Boost

All the devices in the TUSB2XX family AC boost. This compensates for ISI loss. The TUSB212, TUSB213, TUSB214 and TUSB215 all offer DC boost which helps to improve the signal quality for USB compliance.

### 2.2 Power Supply Differences

The TUSB211, TUSB212 and TUSB214 require a VCC of 3.3 V. The TUSB213 and TUSB215 require a VCC of 5 V.

### 2.3 Package Differences

The TUSB2XX devices come in two different packages the TUSB213 and TUB215 come in a VQFN package, the TUSB211, TUSB212, TUSB214 come in a X2QFN package.

Figure 2. RGY Package 14 Pin (VQFN) Top view (TUSB213, TUSB215)

Figure 3. RWB Package 12 Pin (X2QFN) Top View for TUSB211, TUSB212, TUSB214 (no DC\_BOOST on TUSB211)

# 2.4 Charging Downstream Port

All of the TUSB2XX devices are compatible with the USB On-The-Go (OTG) and Battery Charging (BC) protocols. Only the TUSB214 and TUSB215 act as Charging Downstream Port(CDP) Controllers.

### **3 General Implantation Guidelines**

### 3.1 Selecting Equalization and Boost Level for the TUSB2XX

The primary purpose of the TUSB2XXs is to restore the signal integrity of a USB high-speed channel up to the USB connector. The platform goal is to pass the USB Near-End or Far-End Eye Mask with the TUSB2XX in the best location.

Typically, place the TUSB2XX close to the USB connector on a host platform in order to pass Near-End Eye Mask testing. This includes systems where the USB connector may be placed at the far-end of an internal cable.

Typical EQ and Boost recommendations for the TUSB211, TUSB212, TUSB213, TUSB214 and TUSB215.

| Device               | EQ Settings     | DC Boost Settings | Approximate<br>Gain(dB) | Max Pre-Channel<br>loss to pass (near<br>end eye mask) | Max Post-Channel<br>Loss to Pass (near<br>end eye mask) |

|----------------------|-----------------|-------------------|-------------------------|--------------------------------------------------------|---------------------------------------------------------|

|                      | 0               | N/A               | 1                       | 12 inches FR4                                          | 6 inches FR4                                            |

| TUSB211              | 1               |                   | 2                       | 1 meter 28 AWG                                         | 0.5 meter 28 AWG                                        |

| 1036211              | 2               |                   | 3                       | 1.7 meter 28 AWG                                       | 1 meter 28 AWG                                          |

|                      | 3(lowest gain)  |                   | 0.4                     | 6 inches FR4                                           | 3 inches FR4                                            |

| TUSB212.             | 0               | LOW               | 2                       | 1 meter 28 AWG                                         | 0.5 meter 28 AWG                                        |

| TUSB212,<br>TUSB213, | 1               | MID               | 3                       | 2 meter 28 AWG                                         | 1 meter 28 AWG                                          |

| TUSB214,             | 2               | MID               | 5                       | 3 meter 28 AWG                                         | 2 meter 28 AWG                                          |

| TUSB215              | 3(highest gain) | HIGH              | 9                       | 5 meter 28 AWG                                         | 3 meter 28 AWG                                          |

Table 1. TUSB2XX EQ and Boost settings

### 3.2 Power Supply Recommendations

On power up, the interaction of the RSTN pin and power on ramp could result in digital circuits not being set correctly. The device should not be enabled until the power on ramp has settled to VCC or higher to ensure a correct power on reset of the digital circuitry. If RSTN cannot be held low by microcontroller or other circuitry until the power on ramp has settled, then an external capacitor from the RSTN pin to GND is required to hold the device in the low power reset state.

The RC time constant should be larger than five times of the power on ramp time (0 to VCC). With a typical internal pull up resistance of 500 k $\Omega$ , the recommended minimum external capacitance is calculated as:

$CRSTN = [Ramp Time \times 5] \div [500 k\Omega]$

(1)

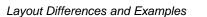

# 4 Layout Differences and Examples

### 4.1 Layout Differences

The TUSB211, TUSB212 and TUSB214 all share the same X2QFN package which require connecting the D1P pin to the D2P pin and the D1M pin to the D2M pin below the device. The TUSB213 and TUSB215 use the VQFN package and do not have their P pins and M pins connected.

# 4.2 Example Layouts

Figure 4. TUSB211, TUSB212 and TUSB214 Layout Example

Figure 5. TUSB213 and TUSB215 Layout Example

# 4.3 High Speed layout guidelines

Refer to the following application Report for general layout guidelines (High Speed Layout Guidelines).

### 5 Testing

# 5.1 USB 2.0 High Speed Downstream Signal Quality Testing

When performing USB 2.0 compliance eye-diagram testing with a host or the downstream port of a HUB with the TUSB2XX, a scenario can occur where the TUSB2XX signal boosting is not enabled. This can occur when the test packets are being transmitted before the USB test fixture is connected to the TUSB2XX. This scenario does not occur during device compliance eye-diagram testing as the USB test fixture must always be connected while testing a device. This scenario only occurs during the compliance testing with the USB test fixtures and does not affect normal operation with a host, HUB, or device.

To avoid this scenario, follow the test procedures provided by the scope equipment vendor and USB-IF (links provided in Section 5.2). Specifically, the USB HS test fixture should be connected prior to executing the TEST PACKETS command using the HSETT test tool. Alternatively, if the test fixture is hot-plugged to the host or downstream HUB port after the command to send test packets has already been entered using the HSETT tool, it is necessary to select TEST PACKETS and click "Execute" again after the test fixture is connected to ensure the TUSB2XX detects a compliance test set-up.

The following generic procedure can be used to take the USB 2.0 compliance eye-diagrams (refer to Section 5.4 for details):

- 1. Connect the USB test fixture to the host, downstream HUB (+ TUSB2XX) port or device under test.

- 2. Configure the host, or HUB, or device using xHSETT or HSETT to send test packets using the procedure detailed in the HSETT documentation.

- 3. Start sending test packets

- 4. Capture test packet on scope to display eye (running compliance software on the scope)

USB 2.0 compliance eye-diagrams can be taken on host, device, and HUB platform ports configured with the TUSB2XX using the EHCI and xHCI High-speed Electrical Test Tool Setup Instruction document provided by the USB Implementers Forum.

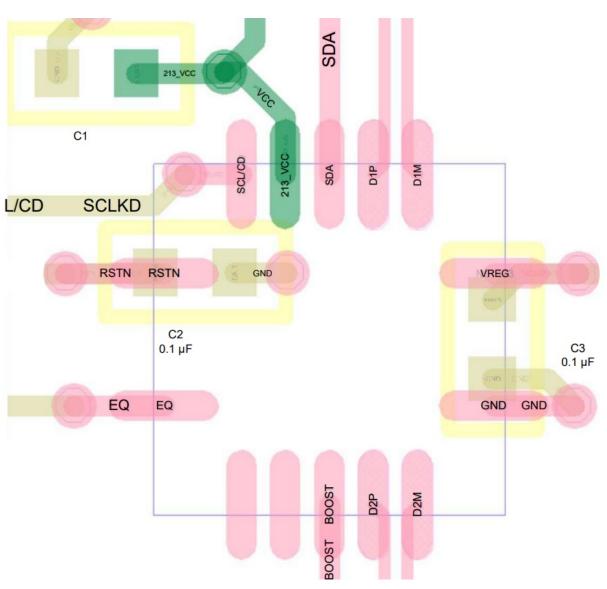

# 5.2 USB 2.0 Upstream Signal Quality Testing

When performing USB 2.0 Compliance Eye Diagram testing on an USB device, a mechanism is required to place the device in the proper test mode. Then output the USB Test Packets. This is normally accomplished by using the xHSETT or HSETT to send a TEST\_PACKET command to the device. Once in test mode, the device controller repeatedly sends the Test Packets on the Port under Test until the device is reset or power cycled. The TUSB2XX is placed between the device controller and USB port in the system and must remain powered on with no reset being asserted to the TUSB2XX. Once the device is sending the High-Speed Test Packets, the TUSB2XX is active and remains active as long as the Host is sending packets, power has not been removed and no reset has been asserted. If power is removed or the TUSB2XX is reset after the device is in test mode sending Test Packets, the device is inactive, and no longer condition the signal.

The following generic procedure can be used to take the USB 2.0 compliance eye-diagrams (refer to Section 5.4 for details):

1. Use the USB-IF (Or Scope Vendor's) USB 2.0 Device High-Speed Test Fixture (See Figure 6). Connect the USB Test Fixture to the USB device to be tested.

Testing

# Figure 6. USB 2.0 High Speed Test Upstream Signal Quality Testing

- 2. Connect the PC to the USB 2.0 Device High-Speed Test Fixture

- 3. Invoke the High-speed Electrical Test Tool software on the PC. The main menu appears and shows the USB2.0 host controller.

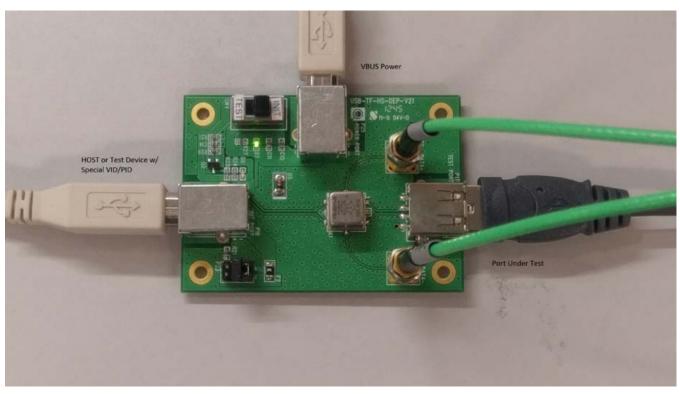

| USB-IF HS Electrical Test Tool |                                           |  |  |  |

|--------------------------------|-------------------------------------------|--|--|--|

| Select Type Of Test            | Select Host Controller For Use In Testing |  |  |  |

| Device                         | PCI bus 5, device 0, function 2 2 Ports   |  |  |  |

| C Hub                          |                                           |  |  |  |

| C Host Controller/System       |                                           |  |  |  |

| []                             | Exit                                      |  |  |  |

Figure 7. USB-IF HS Electrical Test Tool

- 4. Select Device and click TEST to enter the HS Electrical Test Tool Device Test menu. The device under test should be enumerated with the device's VID shown together with the root port in which it is connected.

- 5. Select TEST\_PACKET from the Device Command dropdown menu and click EXECUTE. This forces the device under test to continuously transmit test packets.

- 6. Switch Test Fixture from "INIT" to "TEST" to Capture Test Packet on scope to display eye (Running Compliance software on the scope)

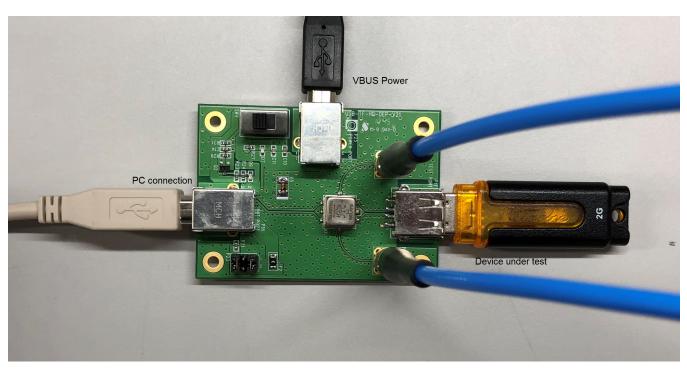

# 5.3 USB 2.0 High Speed Embedded Host Signal Quality Testing

When performing USB 2.0 Compliance Eye Diagram testing on an embedded USB Host, a mechanism is needed to place the Controller in the Head unit in the proper test mode. Then output the USB Test Packets. This is accomplished with the use of a USB device with a specific VID/PID which places the Controller into a test mode. Once in test mode, the embedded Host repeatedly sends the Test Packets on the Port under Test until the Host is reset or power cycled. The TUSB2XX is placed between the Host and USB port in the system and must remain powered on with no reset being asserted to the TUSB2XX. Once the Host is sending the High-Speed Test Packets, the TUSB2XX is active and remains active as long as the Host is sending packets. Power has not been removed and no reset has been asserted. If power is removed or the TUSB2XX is reset after the Host is in test mode sending Test Packets, the device is inactive and no longer condition the signal.

The following generic procedure can be used to take the USB 2.0 compliance eye-diagrams (refer to Section 5.4 for details):

1. Use the USB-IF (Or Scope Vendor's) USB 2.0 Device High-Speed Test Fixture (See Figure 8). Connect the USB Test Fixture to the Head Unit USB Port to be tested.

Figure 8. USB 2.0 Device High-Speed Test Fixture with Embedded Host

- 2. Connect the special test device with test VID/PID info to the Test fixture (Where the USB Host would normally connect).

- 3. Use any specific steps or commands to enable the Host to send Test Packets (This step may be specific to each platform).

- 4. Start sending Test Packets

- 5. Switch Test Fixture from "INIT" to "TEST" to Capture Test Packet on scope to display eye (Running Compliance software on the scope)

# 5.4 Test Procedure Document Links

Details for setting up and running the application are contained in the EHCI and xHCI High-speed Electrical Test Tool Setup Instruction document provided by the USB-IF at the following link: http://www.usb.org/developers/tools/HSETT Instruction 0 4 1.pdf

Copyright © 2018, Texas Instruments Incorporated

Testing

#### Frequently Asked Questions

xHCI (USB 3.0 Host) – XHSETT test application: http://www.usb.org/developers/tools/ EHCI (USB 2.0 Host) – EHSETT test application: http://www.usb.org/developers/tools/usb20\_tools/ Vendor-Specific Test Procedures: http://www.usb.org/developers/compliance/electrical\_tests/ USBET: http://www.usb.org/developers/tools/usb20\_tools/#USBET20

# 6 Frequently Asked Questions

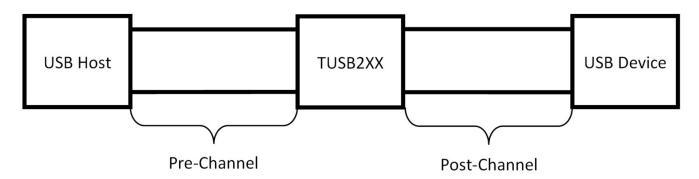

### 6.1 What is Pre-Channel and Post-Channel?

The pre-channel is the path the signal takes from the host to the TUSB2XX device. The post-channel is the path the signal takes from the TUSB2XX device to the USB device.

Figure 9. Pre-Channel and Post-Channel

# 6.2 Can D1 and D2 be swapped?

It does not matter whether D1 or D2 is connected to the host or the device. It does matter that the DP is connected to the data plus and that DM is connected to data minus.

# 6.3 Does the Thermal Pad need to be connected to GND?

No, the Thermal Pad on the TUS213 and TUSB215 are not connected to anything and do not need to be connected to GND.

# 6.4 What are the near end and far end eye masks?

Near end eye masks are used to test the electrical compliance to the USB protocol for USB receptacles while far end eye masks are used to test the electrical compliance of a USB plug.

# 6.5 Where to place the TUSB2XX in an active cable?

The TUSB2XX should be placed on the device side of an active cable. For USB 2.0 cables, this is the type B side of the cable. This is because the TUSB2XX can over boost the Hosts USB 2.0 signal and trigger a disconnect in the host device.

# 6.6 Why is the TUSB2XX is stuck in High speed mode upon startup?

Due to the lack of HS negotiation and subsequent enumeration during HOST downstream eye diagram test the TUSB2XX detect the HOST downstream eye diagram test by detecting high speed test fixture to get into high speed electrical compliance mode.

Some host or hub downstream port has been observed to pull down DP/DM low during power up or when it is in the process of initialization. During this time period, while DP/DM is being pulled down by the host, if TUSB2XX is powered on TUSB2XX could detect this low bus condition on DP/DM as a test fixture and get into high speed electrical compliance mode.

While in this mode, ENA\_HS remains high even if the device is disconnected or suspend. If ENA\_HS is high, low speed or full speed device could fail to enumerate. RSTN must be low to reset the device and exit compliance mode.

The recommendation at power up is to hold TUSB2XX in reset by holding RSTN low until the host initialization is completed.

# 6.7 is the DC Boost boosting both DP and DM lines and why is it needed?

Yes, the DC Boost boosts both the DP and DM lines. DC Boost is needed to compensate for the DC loss that occurs in the transmission channel (Longer cables have more DC loss which can result in eyediagram mask hits).

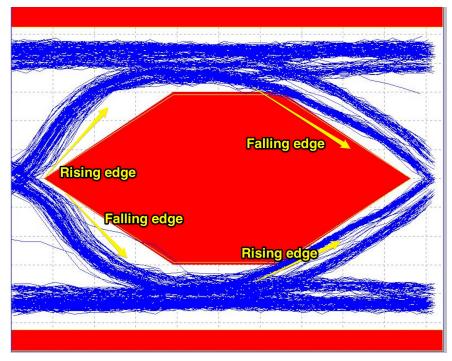

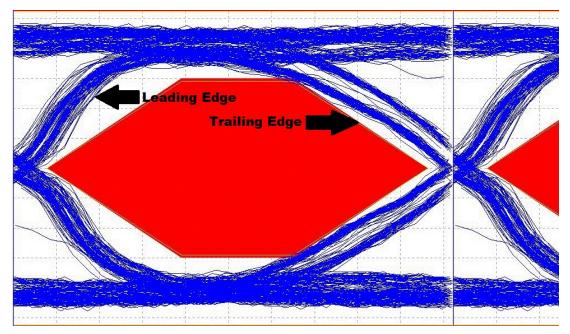

# 6.8 Why does the TUSB2XX not boost the falling edge?

Figure 10. Falling Edge Eye Diagram

The eye diagram has two Edges. It has the leading edge and the trailing edge not rising edge and falling edge. This is because every falling edge is also a raising edge and every raising is also a falling edge (see Figure 11).

Figure 11. Leading and Trailing Edge

The way to improve the trailing edge to pass electrical compliance is to reduce the capacitance on the data lines. One way to decrease capacitance on lines is to use layout techniques that reduce capacitance. the user can also reduce capacitance by changing the thickness of the PCB and changing the material of the PCB to reduce the capacitance on the data lines. Another way to reduce capacitance is to use lower capacitance ESD devices on the data lines.

# 7 References

- TUSB211 Datasheet (SLLSEO0)

- TUSB211 Schematic Checklist (SLLA389)

- TUSB211 to TUSB212 Changes (SLLA376)

- TUSB212 Datasheet (SLLSEX5)

- TUSB212 Schematic Checklist (SLLA391)

- TUSB213 Datasheet (SLLSEX6)

- TUSB213 Schematic Checklist (SLLA393)

- TUSB214 Datasheet (SLLSEX7)

- TUSB214 Schematic Checklist (SLLA394)

- TUSB215 Datasheet (SLLSEX8)

- TUSB215 Schematic Checklist (SLLA395)

- High-Speed Layout Guidelines (SCAA082)

### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated