## Application Brief How Do Integrated GPIO Channels Improve Isolated I2C?

TEXAS INSTRUMENTS

## Miguel Solis, Tony Calabria

Reliable and cost-effective integrated circuit (IC) solutions used for isolation are a critical part of board to board communication within industrial and automotive designs. There are several isolated intraboard interfaces to choose from, each with their own benefits. A standard I2C interface consists of a twowire interface, with a bi-directional serial data (SDA) line and an, either bidirectional or unidirectional, serial clock line (SCL). The Inter-Integrated Circuit (I2C) standard allows for a multi-device shared communication method between controllers and ICs such as data converters or sensors using only two lines. The I2C protocol typically runs at a slower speed, commonly 100kHz or 400kHz and up to 1MHz, allowing time for handshaking between the devices in a communication network. Adding isolation to I2C, such as in ISO1640 and ISO1641 devices, can break long distance ground loops, provide protection to human operators, and prevent damage to high voltage systems. Although I2C is a dependable communication standard, due to the aforementioned speed limitations, it is not the protocol of choice for time sensitive interrupts in some use cases and systems.

Opposed to I2C, Serial Peripheral Interphase (SPI) uses 4-channels to communicate between devices and runs at much faster speeds. SPI does not utilize bidirectional lines or an address scheme to talk to multiple devices in a network. Instead, individual Chip Select (/CS) lines are used to note which device is being communicated to on the bus. With this architecture, SPI can run at much higher speeds, in some cases reach well over 40Mbps. As more devices are added to the communication bus, Individual Chip Select (/CS) lines are added. Since individual /CS lines are needed for devices added to the bus. I2C buses have the benefit of communicating with a large number of devices in a single communication bus without having to increase the number of lines used. In an isolated system, this would require increasing isolation channels needed for each /CS line. Because both SPI and I2C have their own benefits, many system designs incorporate both a SPI and I2C bus in the same module. This allows for systems to both minimize the number of

isolated lines used with I2C and have an isolated solution for time sensitive signals with SPI.

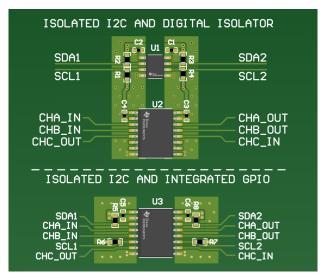

To accommodate both faster signal communication and slower bidirectional I2C communication in an isolated system, a multiple-chip solution has historically been used. Texas Instruments latest digital isolator family, ISO67xx, offers 2, 3, 4, and 6 unidirectional channel options for isolating UART, SPI, and GPIO. To have these devices used in an I2C interface, the design would require multiple discrete components (How to Isolate Signal and Power for I2C). To simplify the use of SPI and I2C in the same device and package, Texas Instruments released the ISO1642, ISO1643, and ISO1644 to help decrease board surface area while providing quality isolation protection. Our new ISO164x family offers two bidirectional I2C channels, and up to three unidirectional options with varying directions in a single package. This allows designs to get smaller without sacrificing features and the design flexibility of having multiple isolated communication buses. Figure 1 shows the difference in board area savings going from a multiple chip solution solving I2C and SPI to a single ISO1644.

1

The ISO1642/3/4 devices also make an excellent solution when only an isolated I2C bus is present in a system. Because, I2C runs at lower speeds, some designs may have time sensitive signals, such as a reset or power down signal, that cannot wait for a device to decode an I2C command to perform a function. GPIO lines are used parallel to the I2C bus to handle these signals and need to be isolated. The historical solution has been to add a separate digital isolator or optocoupler isolator to pass the additional lines across the barrier. The release of the new ISO1642/3/4 allows a design to address 2 or 3 GPIO lines, in parallel with the I2C device, without adding to the IC count or increasing the circuit board size. This one chip solution will not only decrease the surface area by 50% on you board, but will provide a cost-efficient solution depending on the amount of GPIO channels you need for your system.

There are multiple solutions that can accomplish intraboard communication, and the appropriate choice between interfaces is sometimes dependent on speed, size, or time sensitive signal reliability. Using a combination of Isolated SPI and Isolated I2C buses yields the most space reduction while also providing fast and reliable data. TI has designed an Isolated I2C family with GPIO integration to meet this need. These new generation of Isolated I2Cs found in the ISO164x family, allow for a wider array of use cases, and provide a fast, reliable, and size conscious solution to these needs.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated