# The UC3902 Load Share Controller and Its Performance in Distributed Power Systems

Laszlo Balogh

System Power

#### ABSTRACT

Users of distributed power systems are seeking reliable and economic solutions to supply their loads. A modular approach, where stand alone power supplies are utilized for local power conversion, is widely accepted in these applications. The power rating of the individual converters are usually limited by the available height, board space and by the limitation on volumetric heat dissipation. High current loads are supplied by several parallel connected power supplies. In addition to higher currents, the parallel modules can also offer redundancy, an important factor to achieve reliable, uninterrupted operation and extended life expectancy in these systems.

#### Contents

| 1 | UC3902 Applications                 | 1    |

|---|-------------------------------------|------|

| 2 | UC3902 Block Diagram                | 2    |

| 3 | UC3902 Load Share Controller Design | 4    |

| 4 | Design Example                      | 8    |

| 5 | Parts List                          | . 11 |

| 6 | Experimental Results                | . 12 |

| 7 | References                          | . 12 |

## 1 UC3902 Applications

The current demanded by large electronic systems continuously rises due to higher performance and increased functionality. At the same time, supply voltages, especially in digital circuits, are falling to previously unprecedented low levels. The combination of higher load currents and low supply voltages impose difficult requirements on the power distribution and in most cases, forces a higher voltage distribution bus with local voltage conversion.

Parallel connected power supplies require a dedicated control mechanism, (load share circuitry) to assure full utilization of the system. The purpose of a load share controller, like the UC3902, is to provide for equal distribution of the load current among the parallel connected power supplies. By equalizing the output currents, uniform thermal stress of the individual modules is also ensured which has the utmost importance for long term reliability of electronic components.

Trademarks are the property of their respective owners.

For the UC3902 to work properly, the modular power system has to consist of power supplies which possess their own feedback circuits. Furthermore, the stand alone modules have to be equipped with true remote sense capability or with an output voltage adjustment terminal. Each module must have its own load share controller. The operating principle of a load share mechanism is to measure the output current of each individual module and to be able to modify the output voltage of the units until all participating power supplies deliver equal output currents. It is accomplished by the UC3902 integrated circuits which are connected to the common load share bus and adjust the positive sense voltage (or the voltage of the output voltage adjust pin) of their respective modules to provide equal load current sharing.

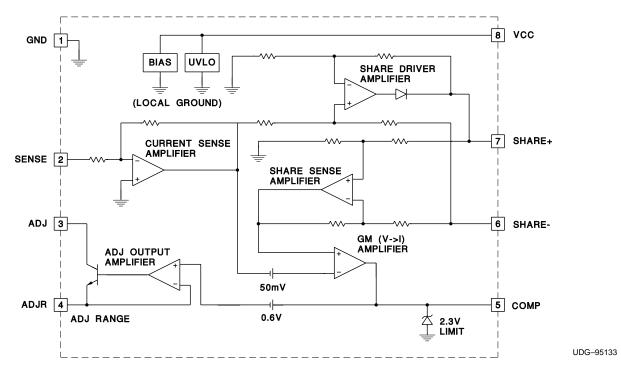

### 2 UC3902 Block Diagram

The UC3902 is an 8-pin integrated circuit. Its sole purpose is to provide the load sharing function for existing power supplies. The device incorporates only the building blocks required for load sharing. Tight regulation of the converters' output voltage is not anticipated with this circuit. In fact, the UC3902 performs just the opposite task by finely adjusting the regulated output voltage of the converters to match all output currents evenly.

A unique advantage of the UC3902 is its differential load share bus. This architecture greatly enhances the noise immunity of the system. Figure 1 shows the block diagram of the load share controller.

This device consists of a current sense amplifier, a share bus driver and sense amplifier pair, an error amplifier, a buffer stage called adjust amplifier, and housekeeping circuit which provides internal bias and the on-chip reference for the circuit.

The UC3902 has an inverting current sense amplifier with the a gain of 40. The output of the current sense amplifier is proportional to the output current of the power supply it is connected to. It provides the input signals to the load share bus driver amplifier and to the inverting input of the error amplifier. Because the share driver amplifier is configured for unity gain, the voltage on the output of the share driver amplifier also equals the output voltage of the current sense amplifier. When this voltage is the highest potential among the parallel connected load share controllers, i.e. the unit delivers the highest output current, the module acts as the master unit. The output of the share driver amplifier of the master also determines the voltage on the share bus. In the case where this voltage is lower then the share bus voltage, i.e. the module supplies less current than any one of the other units in the system, the share controller behaves as a slave. The output of the share driver amplifier of the slave controllers is disconnected from the share bus by the diodes in series with their respective outputs.

The share sense amplifier measures the voltage on the differential share bus and provides the signal for the noninverting input of the error amplifier. Similar to the share driver amplifier, this circuit has a gain of 1 which is fixed internally. Consequently, the output voltage of the share sense amplifier always corresponds to the highest output current level, delivered by the master unit in the system.

A transconductance amplifier is utilized for the error amplifier function in the UC3902. If a feedback network were connected between the output and the inverting input of the error amplifier, the output current representation would be inaccurate. The transconductance amplifier allows the feedback network to be connected from the amplifier output to the ground which preserves the authenticity of the current signal at the inverting input of the error amplifier. Also note that this type of amplifier requires a voltage difference between its inverting and noninverting inputs. Furthermore, the transconductance amplifier has high input and output impedances. Instead of the usual low impedance voltage source output of operational amplifiers, this circuit has a high impedance current source output. Accordingly, the gain is defined as transconductance (A/V) but it can be converted back to the general V/V gain term by multiplying the transconductance of the amplifier ( $g_M$ ) with the impedance of the compensation network (X<sub>COMP</sub>).

The steady-state output voltage of the error amplifier is the function of the voltage difference between the outputs of the current sense and the share sense amplifiers. When a particular controller works as the master in the system this voltage difference is zero. To guarantee the correct state of the error amplifier, a 50-mV offset is inserted in series with the inverting input. This artificial offset ensures zero volts at the output of the error amplifier when the unit is the master module. All slave controllers develop a non-zero error voltage at the output of the transconductance amplifier which is proportional to the difference between the output current of the respective power supply and the output current value of the master module represented on the share bus.

The output voltage of the error amplifier is used to adjust the output voltage of the power converter to balance the load current among the parallel connected modules. This is done by the adjust amplifier and its companion NPN transistor. The adjust amplifier provides signal conditioning for the error signal and its output drives an NPN transistor which is configured as a programmable current source. A resistor from its emitter to ground and the error voltage defines the current, I<sub>ADJ</sub>, which flows through a resistor connected between the ADJ pin of the load–share controller and the positive output terminal. The I<sub>ADJ</sub> current causes a voltage drop across the resistor which requires the power supply to increase its output voltage. The resulting higher power supply output voltage increases the output current of that particular module until the output current levels equal out among the units. At that point load sharing has been established.

## 3 UC3902 Load Share Controller Design

The UC3902 load share controller requires only a few external components. Before the values of these components can be calculated, the DC/DC converter module parameters must be reviewed and some application specific limits have to be determined. There are three parameters which must be known;  $V_{O(nom)}$  is the nominal output voltage of the converter,  $I_{O(max)}$  is the maximum current delivered by the unit and  $\Delta V_{O(max)}$  is the maximum adjustment range of the output voltage. The output voltage adjustment can be accomplished by using either the positive sense terminal or the adjust pin of the DC/DC converters and it is usually limited by the design of the modules. Depending on the output current level, the allocated voltage drop and the allowed power dissipation, the current sense resistor can be selected. Since the UC3902 is operational from 2.7 V to 20 V, in most cases the device is powered directly from the output voltage of the system. If that is not possible because of an inappropriate value of the output voltage, the supply voltage, VCC, has to be determined as well.

### 3.1 Setting Up The DC Operating Point

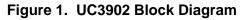

Figure 2 shows a typical application of the UC3902 load share controller. This circuit must be repeated for each power supply sharing the current for a common load in the system. The design process starts with calculating the component values for setting up the basic operating conditions for the device.

Figure 2. Typical Application

In order to precisely share the load current among parallel connected modules, the output current of each individual power supply has to be measured. A current sense resistor,  $R_{SENSE}$ , is placed in the negative return path of the units. Choosing  $R_{SENSE}$  is based on two factors: the maximum power dissipation and the maximum voltage drop across the sense resistor. While the power dissipation is only limited by practical considerations like efficiency and component ratings, the maximum voltage drop has to comply with internal signal level limits of the integrated circuit. Most important is to prevent the output of the current sense amplifier from saturation. The highest voltage of the amplifier output,  $V_{CSAO}$  is a function of VCC. It equals either 10 V or VCC – 1.5V, whichever is lower. Consequently,

$$V_{\text{SENSE(max)}} = \frac{V_{\text{CSAO}}}{A_{\text{CSA}}} \tag{1}$$

where:

- V<sub>SENSE(max)</sub> is the maximum voltage drop across the current sense resistor,

- V<sub>CSAO</sub> is the maximum voltage of the current sense amplifier output and

- A<sub>CSA</sub> is 40, the gain of the current sense amplifier

Once  $V_{\text{SENSE}(max)}$  is determined, the current sense resistor value can be calculated by the following formula:

$$R_{SENSE} = \frac{V_{SENSE(max)}}{I_{O(max)}}$$

(2)

$I_{ADJ(max)}$ , the maximum current of the adjust amplifier is 10 mA as specified in the datasheet. This current is determined by the highest possible voltage on the ADJR pin which is 1.8 V and by the resistor,  $R_G$ , between the ADJR pin and ground. Thus the resistor value can be calculated as:

$$R_{G} = \frac{1.8 \text{ V}}{I_{\text{ADJ(max)}}}$$

(3)

$R_{ADJ}$  is the impedance inserted in the positive sense line of the power supply. Its value is the function of the maximum adjustment range of the output voltage,  $\Delta V_{O(max)}$  and the previously selected  $I_{ADJ(max)}$  current value. Since the voltage drop across the current sense resistor reduces the range available for output voltage adjustment, that factor has to be accounted for as shown in the equation for  $R_{ADJ}$  below:

$$R_{ADJ} = \frac{\Delta V_{O(max)} - I_{O(max)} \times R_{SENSE}}{I_{ADJ(max)}}$$

(4)

**NOTE:** This relationship points out an important design constraint for the system. The sum of the voltage drops across the wiring impedances and the voltage drop across the current sense resistor must be significantly lower than  $V_{O(max)}$  or the load share mechanism has no headroom to adjust the output voltage of the modules to achieve proper distribution of the load current.

#### 3.2 Closing The Share Loop

Balanced distribution of the load currents among the parallel connected units is accomplished by an additional control loop provided only for the load share function. Similarly to other control loops inside the power supplies, the current share loop is based on negative feedback. Such control loops must obey certain stability criteria in order to work properly. Although this application note does not cover the theoretical background of loop stability, some of the most critical conditions for successfully closing the load share loop are pointed out.

**NOTE:** Since the load share loop is added to existing power supplies, interaction between the existing voltage control loop and the share loop must be avoided. For that reason the crossover frequencies of the two loops must be well separated.

The voltage loop crossover frequency,  $f_{0,V}$  is greatly dictated by the required transient response of the converter. In order to maintain the stability of the voltage control loop, the share loop has to be set up not to cause any excess phase shift at  $f_{0,V}$ . This is usually achieved by placing the crossover frequency of the share loop ( $f_{0,S}$ ) at least one, but preferably two decades lower than the crossover frequency of the voltage loop. Also a zero should be placed in the transfer function at  $f_{0,S}$ . This way, the effect of the share loop is minimized at the crossover frequency of the voltage loop.

Closing the load share loop at a low crossover frequency is acceptable, if the purpose of load sharing is clarified. The primary concern for load sharing is to extend the life expectancy of the system and to increase reliability. It is achieved in the system by paralleling several modules and assuring that their thermal stresses are balanced during the life of the product. Another advantage in such systems is the possibility for redundancy. These goals can be completely fulfilled by slow acting corrective measures which allow  $f_{0.S}$  to be significantly lower than  $f_{0.V}$ .

The first step is to determine the transfer functions of the individual building blocks for the frequency range from 0.1 Hz to approximately 1 kHz. The unity gain crossover frequency of the load share control loop is expected to be within these frequency limits. If off-the-shelf power supplies are being used, then a network analyzer should be used to measure the transfer function. This is also a good practice to confirm actual versus calculated performance as well.

The valid transfer functions for the range of interest are described in Table 1.

| FUNCTION                         | DESCRIPTION                                                                                                                                                                                                              |  |  |  |  |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| A <sub>PWR</sub> (s)             | Transfer function of the power supply, measured by injecting an AC signal between $V_{SENSE+}$ and $V_{OUT+}$ terminals.                                                                                                 |  |  |  |  |

| A <sub>VO</sub> →V <sub>IS</sub> | This gain term describes the relationship between the output voltage and the voltage across the current sense resistor. It varies with the load impedance according to equation (5).                                     |  |  |  |  |

| A <sub>CSA</sub>                 | The gain of the current sense amplifier. This term is a constant and equals 40.                                                                                                                                          |  |  |  |  |

| A <sub>SHA</sub>                 | Both amplifiers driving and sensing the signal on the differential share bus are configured for unity gain. $(A_{SHA} = 1)$ .                                                                                            |  |  |  |  |

| A <sub>EA</sub> (s)              | The gain of the error amplifier defined in equation (6) where $g_M$ is the transconductance of the error amplifier and $X_{COMP(s)}$ is the impedance of the compensation components as a function of complex frequency. |  |  |  |  |

| A <sub>ADJ</sub>                 | The adjust circuit gain depends only on the $R_G$ and $R_{ADJ}$ resistors because the adjust amplifier is configured as a unity gain buffer stage. And consequencly $A_{ADJ}$ can be described in equation (7).          |  |  |  |  |

Table 1. Valid Transfer Functions

$$A_{\vec{VoVis}} = \frac{R_{SENSE}}{R_{LOAD}}$$

(5)

$$A_{EA}(s) = g_{M} \times X_{COMP}(s)$$

(6)

$$A_{ADJ} = \frac{R_{ADJ}}{R_{G}}$$

(7)

The overall share loop characteristic is established by multiplying the gain terms of the individual blocks and is described in equation (8).

$$A_{SHARE\_LOOP}(s) = A_{PWR}(s) \times A_{\vec{VoVis}} \times A_{CS} \times A_{SHA} \times A_{EA}(s) \times A_{ADJ}$$

(8)

### 4 Design Example

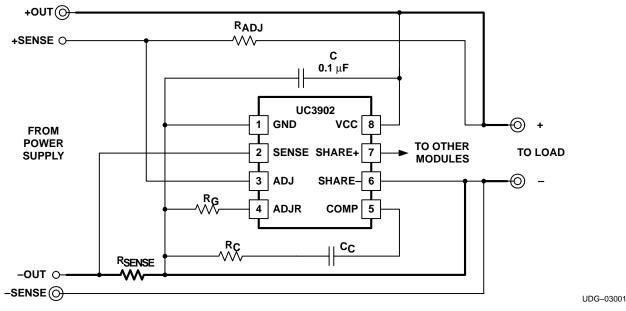

Users experimenting with the UC3902 load share controller can utilize a demonstration board featured in Figure 3. This circuit provides a solution for paralleling three power supply modules. The performance of the system was measured using three off-the-shelf DC/DC converter modules, each rated for 100 W delivering 8.4 A to the load at 12-V nominal output voltage.

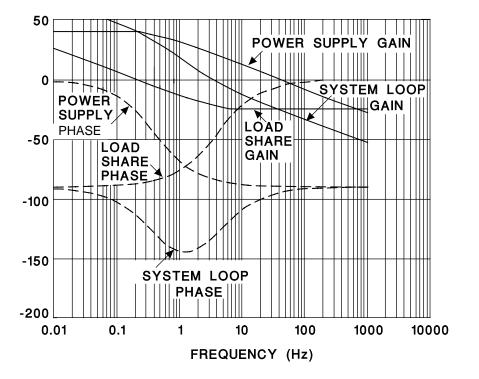

The design process starts by measuring the transfer function of the power supplies between their positive voltage sense and power output terminals. The resulting Bode plot shown in Figure 4 reveals a 40-Hz crossover frequency which requires a crossover frequency of 4 Hz for the load share loop. The power stage has a 20-dB gain at this frequency.

In the demonstration board, the UC3902 is powered from the output voltage of the system. Note the 0.1- $\mu$ F local bypass capacitor connected to the VCC pin of the device. Using 12 V as VCC, the maximum output voltage of the internal amplifiers are approximately 10 V. This voltage denotes the highest possible full scale voltage between SHARE+ and SHARE-, but the actual voltage on the load share bus at full load is determined by the designer. Noise sensitivity, accuracy, and the number of units in parallel have to be taken into consideration when choosing the full scale bus voltage. The load share bus is driven by the master controller only and each slave module represents a 10-k $\Omega$  load on the bus. This means that every unit increases the supply current of the master module by 100  $\mu$ A/V on the load share bus.

The power supply's 8.4-A output current rating allows the use of a higher shunt resistor value in favor of better load share accuracy with only a slight decrease in overall efficiency. The full scale bus voltage,  $V_{CSAO}$  is selected to be 6 V.

Accordingly,

$$R_{SENSE} = \frac{6 V}{8.4 A \times 40} = 0.0178\Omega$$

and a 20 m $\Omega$  standard value had been selected.

(9)

UDG-96246

#### Figure 3. Demonstration Board Schematic

The R<sub>G</sub> resistor value depends on the current flowing through the NPN buffer transistor of the adjust amplifier and in the R<sub>ADJ</sub> resistor placed in the positive sense line of the converter. This current is selected by the designer but its value shall be smaller than 10 mA according to the datasheet. For this application, 3.5 mA is chosen. Smaller values tend to increase the noise sensitivity of the solution while larger current values represent unnecessary power dissipation for the device. Although this current does not show up in the I<sub>CC</sub> current requirements, the power dissipation of the buffer transistor can be a significant part of the total power loss inside the integrated circuit. For instance, in this application, the voltage across the collector emitter terminals equals VCC – 1.8 V, approximately 10 V. The power dissipated in this part of the circuit is  $10 \text{ V} \times 3.5 \text{ mA} = 35 \text{ mW}$ . Once the maximum current for this part of the circuit is selected the value of R<sub>G</sub> can be calculated as:

$$R_{\rm G} = \frac{1.8 \,\rm V}{3.5 \,\rm mA} = 514\Omega \tag{10}$$

The nearest standard value of 510  $\Omega$  is used.

The R<sub>ADJ</sub> resistor value is defined by the maximum adjustment range of the output voltage, the highest load current, the current sense resistor value, and I<sub>ADJ</sub> value. In this application,  $\Delta V_{O(max)}$  is 470 mV while the other parameters have been previously calculated. Thus,

$$R_{ADJ} = \frac{470 \text{ mV} - 8.4 \text{ A} \times 20 \text{ m}\Omega}{3.5 \text{ mA}} = 86.3\Omega$$

(11)

Instead, an 82  $\Omega$  standard value is chosen.

At this point, the steady-state operating conditions of the system are defined. The compensation components  $C_C$  and  $R_C$  can be calculated from the loop gain equation.

$$A_{SHARE\_LOOP}(s) =$$

$$A_{PWR}(s) \times \frac{R_{SENSE}}{R_{LOAD}} \times A_{CSA} \times g_{M} \times \left(\frac{1}{C_{C} \times s} + R_{C}\right) \times \frac{R_{ADJ}}{R_{G}}$$

$$A_{PWR}(s) = 20 \text{ dB} = 10 \text{ V/V}$$

(12)

Substituting the power stage gain of 10 at the load share loop crossover frequency and solving the equation for  $C_C$ , the compensation capacitor value can be calculated as:

$$C_{C} = A_{PWR}(s) \times \frac{R_{SENSE}}{R_{LOAD}} \times A_{CSA} \times g_{M} \times \left(\frac{1}{\pi \times f_{O,S}}\right) \times \frac{R_{ADJ}}{R_{G}}$$

(13)

which gives

$$C_{C} = 10 \times \left(\frac{20 \text{ m}\Omega}{1.43 \Omega}\right) \times 40 \times 4.5 \text{ mS} \times \left(\frac{1}{\pi \times 4 \text{ Hz}}\right) \times \left(\frac{82 \Omega}{510 \Omega}\right) = 322 \,\mu\text{F}$$

(14)

A 330- $\mu$ F capacitor is used. Note that the reason for the large capacitor value is the extremely low crossover frequency dictated by the transfer function characteristic of the DC/DC converter.

The value of  $R_C$  is determined by the selected crossover frequency and compensation capacitor value according to:

$$R_{\rm C} = \frac{1}{2\pi \times f_{\rm O,S} \times C_{\rm C}}$$

(15)

UDG-96247

Using the previously calculated capacitor value results in a R<sub>C</sub> value of 270  $\Omega$ .

The resulting Bode plot of the load share control loop is displayed in Figure 4. The phase margin of the loop can be increased by separating the two crossover frequencies,  $f_{0,V}$  and  $f_{0,S}$  even further. In this particular design, moving  $f_{0,S}$  to a lower frequency would have resulted in a very large capacitor value, thus this idea was not considered.

Figure 4. DC/DC Converter and Load Share Loop Bode Plots

### 5 Parts List

Table 2 lists the board components and their values, which can be modified to meet the application requirements.

| REFEREN            | ICE DESIGNATOR | QTY | VALUE    |

|--------------------|----------------|-----|----------|

| с                  | C10, C20, C30  | 3   | 0.1 μF   |

|                    | C11, C21, C31  | 3   | 0.01 μF  |

|                    | C12, C22, C32  | 3   | not used |

|                    | C13. C23. C33  | 3   | not used |

| CC                 | C14, C24, C34  | 2   | 330 μF   |

| R <sub>ADJ</sub>   | R10, R20. R30  | 3   | 82 Ω     |

| R <sub>SENSE</sub> | R11, R21, R31  | 3   | 20 mΩ    |

| R <sub>G</sub>     | R12, R22, R32  | 3   | 510 Ω    |

| R <sub>C</sub>     | R13, R23, R33  | 3   | 270 Ω    |

Table 2. Part List

### 6 Experimental Results

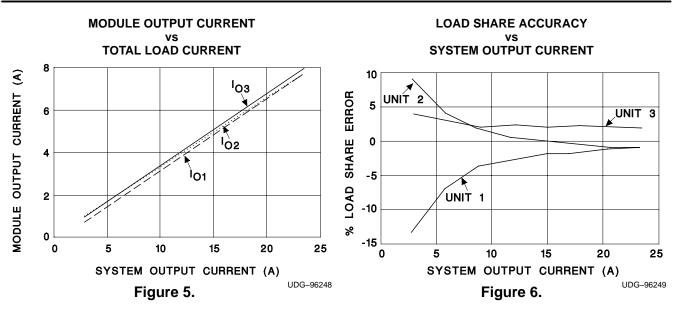

The performance of the demonstration circuit was measured using the calculated component values and running three DC/DC converters in parallel. Figure 5 shows the output currents of the individual modules as a function of the total load current.

In Figure 6, the percentage of deviation from the calculated average module current is depicted. The current distribution error is the largest at light load, as expected, because of the effects of internal offset voltages and the small current measurement signal level. At full load, where load sharing has the most impact, the three modules shared the load current evenly, within 1% of the ideal load current values.

Results similar to this can be obtained in other applications with the formulas contained within this application note.

### 7 References

- 1. UC3902 Load Share Controller, Datasheet, TI Literature No. SLUS232

- 2. M. Jordan, Application Note, UC3907 Load Share IC Simplifies Parallel Power Supply Design, TI Literature No SLUA147. (AKA U–129).

- 3. J. Rajagopalan, et al, *Modeling and Dynamic Analysis of Paralleled DC/DC Converters* with Master–Slave Current Sharing Control, APEC '96 Proceedings, pp. 678–684

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third–party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2003, Texas Instruments Incorporated