# Application Note **Multiple FETs with the BQ769x2 Battery Monitors**

# TEXAS INSTRUMENTS

#### Willy Massoth

#### ABSTRACT

The typical schematics for the BQ769x2 family of battery monitors (which includes the BQ76952, BQ76942, and BQ769142) show single high-side series FETs. Many designers need to parallel FETs in their designs for current capability or heat dissipation. This document discusses and shows results of switching multiple FETs using BQ76952 devices and provides an example for designers implementing multiple FETs with this or other devices in the BQ769x2 family.

#### **Table of Contents**

| 1 Introduction                       | 3  |

|--------------------------------------|----|

| 2 Reverse Charge Circuit             | 4  |

| 3 Reverse Charge Component Selection |    |

| 4 Charge Pump (and FET Turn On)      |    |

| 5 Parallel FET Test Circuits         |    |

| 6 CHG Driver                         |    |

| 7 CHG Driver Current Paths           | 14 |

| 8 DSG Driver                         |    |

| 9 DSG Driver Current Paths           |    |

| 10 Conclusion                        |    |

| 11 References                        |    |

| 12 Revision History                  |    |

#### List of Figures

| Figure 1-1. Typical 7S Series FET Schematic                    | 3              |

|----------------------------------------------------------------|----------------|

| Figure 2-1. Negative PACK+ Without Reverse Charge Circuit      | 4              |

| Figure 2-2. Negative PACK+ With Reverse Charge Circuit         | 4              |

| Figure 3-1. Reverse Charge Current Paths                       | <mark>5</mark> |

| Figure 4-1. Charge Pump and FET Turn On, Low Voltage, 470 nF   | <mark>6</mark> |

| Figure 4-2. Charge Pump Start, Low Voltage, 470 nF             | 6              |

| Figure 4-3. Charge Pump Start, Normal, 470 nF                  |                |

| Figure 4-4. Charge Pump Start and FET Turn On, 2 µF CP1 Cap    | <mark>6</mark> |

| Figure 4-5. CP1 drop, 24 FETs, C <sub>CP1</sub> 470 nF         |                |

| Figure 4-6. CP1 drop, 24 FETs, C <sub>CP1</sub> 2 μF           | <b>7</b>       |

| Figure 5-1. Multiple FET Test Circuit                          |                |

| Figure 5-2. Multiple FET Test Circuit With Local Current Loops | 9              |

| Figure 6-1. CHG On, Single FET, 5.1 kΩ, 470 nF                 |                |

| Figure 6-2. CHG Off, Single FET, 5.1 kΩ                        |                |

| Figure 6-3. CHG On, 2 FETs, 5.1 kΩ, 470 nF                     |                |

| Figure 6-4. CHG Off, 2 FETs, 5.1 kΩ                            |                |

| Figure 6-5. CHG On, Single FET, 1 kΩ, 470 nF                   |                |

| Figure 6-6. CHG Off, Single FET, 1 kΩ                          | 11             |

| Figure 6-7. CHG On, Single FET, 100 Ω, 470 nF                  |                |

| Figure 6-8. CHG Off, Single FET, 100 $\Omega$                  |                |

| Figure 6-9. CHG Off, 4 FETs, 100 Ω                             | <b>11</b>      |

| Figure 6-10. CHG Off, 4 FETs, 100 Ω, PNP                       |                |

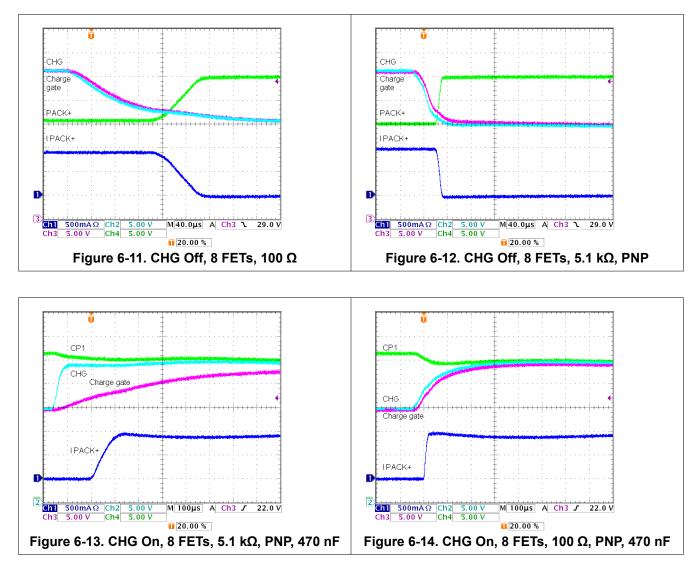

| Figure 6-11. CHG Off, 8 FETs, 100 Ω                            |                |

| Figure 6-12. CHG Off, 8 FETs, 5.1 kΩ, PNP                      |                |

| Figure 6-13. CHG On, 8 FETs, 5.1 kΩ, PNP, 470 nF               |                |

| Figure 6-14. CHG On, 8 FETs, 100 Ω, PNP, 470 nF                | 12             |

1

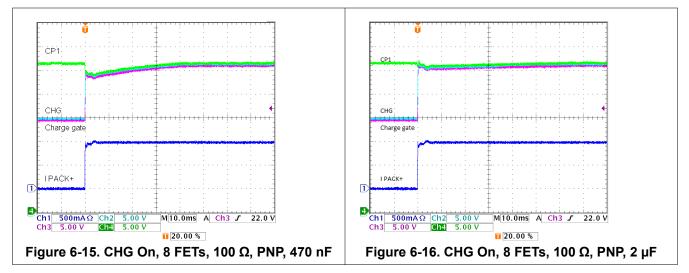

| Figure 6-16. CHG On, 8 FETs, 100 Ω, PNP, 2 μF.   13     Figure 6-17. CHG On, 12 FETs, 100 Ω, PNP, 2 μF.   13     Figure 6-18. CHG Off, 12 FETs, 100 Ω, PNP.   μF.     Figure 7-1. CHG Driver Tum-On Current Path.   14     Figure 7-2. CHG Loaded With 36-V Battery.   15     Figure 7-4. CHG Off, 4 FETs, 100 Ohm, No Current.   15     Figure 7-4. CHG Off, 4 FETs, 100 Ohm, No Current.   16     Figure 8-1. DSG On, Single FET, 10 kΩ, 470 nF.   17     Figure 8-4. DSG Off, Single FET, R41 100 Ω.   17     Figure 8-5. DSG Off, Single FET, R41 1 kΩ.   18     Figure 8-4. DSG On, Single FET, R41 1 kΩ.   18     Figure 8-5. DSG Off, 2 FETs, R41 1 kΩ.   19     Figure 8-6. DSG On, 2 FETs, 10 kΩ, 470 nF.   19     Figure 8-1. DSG Off, 4 FETs, R41 1 kΩ.   19     Figure 8-1. DSG Off, 4 FETs, R41 1 kΩ.   19     Figure 8-1. DSG Off, 8 FETs, R41 1 kΩ.   19     Figure 8-1. DSG Off, 8 FETs, R41 1 kΩ.   19     Figure 8-1. DSG Off, 8 FETs, R41 1 kΩ.   19     Figure 8-1. DSG Off, 8 FETs, R41 1 kΩ.   19     Figure 8-1. DSG Off, 8 FETs, R41 1 kΩ.   19     Figure 8-1. DSG Off, 12 FETs, 10 kΩ, 470 nF. </th <th>Figure 6-15. CHG On, 8 FETs, 100 Ω, PNP, 470 nF</th> <th>13</th>                                                                                                                                                                                           | Figure 6-15. CHG On, 8 FETs, 100 Ω, PNP, 470 nF  | 13 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----|

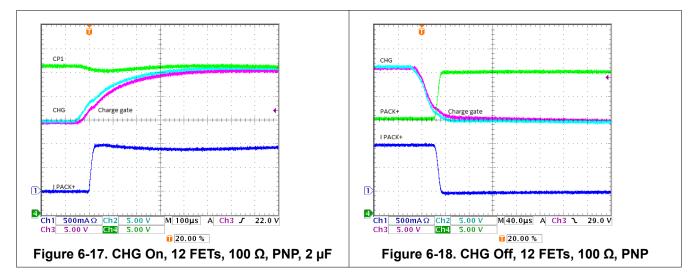

| Figure 6-17. CHG On, 12 FETs, 100 Ω, PNP, 2 μF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                  |    |

| Figure 6-18. CHG Off, 12 FETs, 100 Ω, PNP. 13   Figure 7-1. CHG Driver Turn-On Current Path. 14   Figure 7-2. CHG Loaded With 36-V Battery. 15   Figure 7-3. CHG Driver Turn-Off Current Path. 15   Figure 7-3. CHG Driver Turn-Off Current Path. 15   Figure 8-1. DSG Off, Single FET, 100 Chm, No Current. 16   Figure 8-1. DSG Off, Single FET, R41 100 Ω. 17   Figure 8-3. Battery Transient With Single FET, R41 100 Ω. 18   Figure 8-4. DSG On, Single FET, R41 100 Ω. 18   Figure 8-5. DSG Off, Single FET, R41 1 KΩ. 18   Figure 8-6. DSG On, 2 FETs, 10 kΩ, 470 nF. 19   Figure 8-7. DSG Off, 2 FETs, R41 1 kΩ. 19   Figure 8-8. DSG On, 4 FETs, 10 kΩ, 470 nF. 19   Figure 8-10. DSG Off, 8 FETs, R41 1 kΩ. 19   Figure 8-10. DSG Off, 8 FETs, R41 1 kΩ. 19   Figure 8-10. DSG Off, 8 FETs, R41 1 kΩ. 19   Figure 8-10. DSG Off, 8 FETs, R41 1 kΩ. 19   Figure 8-12. DSG Off, 8 FETs, R41 1 kΩ. 19   Figure 8-12. DSG Off, 8 FETs, R41 1 kΩ. 19   Figure 8-12. DSG Off, 8 FETs, R41 1 kΩ. 19   Figure 8-12. DSG Off, 12 FETs, R41 1 kΩ. 19   Figure 8-12.                                                                                                                                                                                                                                                                                                                          |                                                  |    |

| Figure 7-1. CHG Driver Turn-On Current Path. 14   Figure 7-2. CHG Loaded With 36-V Battery. 15   Figure 7-4. CHG Off, 4 FETs, 100 Ohm, No Current. 16   Figure 8-1. DSG On, Single FET, 10 kQ, 470 nF. 17   Figure 8-2. DSG Off, Single FET, R41 100 Q. 17   Figure 8-3. Battery Transient With Single FET, R41 100 Q. 17   Figure 8-4. DSG On, Single FET, R41 100 Q. 17   Figure 8-5. DSG Off, Single FET, R41 1 KQ. 18   Figure 8-6. DSG On, 2 FETs, 10 kQ, 470 nF. 18   Figure 8-7. DSG Off, 2 FETs, R41 1 kQ. 19   Figure 8-8. DSG On, 4 FETs, 10 kQ, 470 nF. 19   Figure 8-10. DSG On, 8 FETs, 10 kQ, 470 nF. 19   Figure 8-10. DSG On, 8 FETs, 10 kQ, 470 nF. 19   Figure 8-10. DSG On, 8 FETs, 10 kQ, 470 nF. 19   Figure 8-11. DSG Off, 8 FETs, R41 1 kQ. 19   Figure 8-12. DSG On, 8 FETs, 10 kQ, 470 nF. 20   Figure 8-13. DSG Off, 12 FETs, R41 100 Q. 20   Figure 8-13. DSG Off, 12 FETs, R41 100 Q. 20   Figure 8-13. DSG Off, 12 FETs, 10 kQ, 470 nF. 20   Figure 8-14. DSG On, 12 FETS, 10 kQ, 470 nF. 20   Figure 8-15. DSG Off, 12 FETS, R41 100 Q. 20                                                                                                                                                                                                                                                                                                                     |                                                  |    |

| Figure 7-2. CHG Loaded With 36-V Battery.15Figure 7-3. CHG Driver Turn-Off Current Path.15Figure 7-4. CHG Off, 4 FETs, 100 Ohm, No Current.16Figure 8-1. DSG On, Single FET, 10 kQ, 470 nF.17Figure 8-2. DSG Off, Single FET, R41 100 Q.17Figure 8-3. Battery Transient With Single FET, R41 100 Q.18Figure 8-4. DSG On, Single FET, R41 10 kQ, 470 nF.18Figure 8-5. DSG Off, Single FET, R41 1 kQ.18Figure 8-6. DSG On, 2 FETs, 10 kQ, 470 nF.19Figure 8-7. DSG Off, 2 FETs, R41 1 kQ.19Figure 8-8. DSG On, 4 FETs, 10 kQ, 470 nF.19Figure 8-9. DSG Off, 4 FETs, R41 1 kQ.19Figure 8-10. DSG Onf, 8 FETs, R41 1 kQ.19Figure 8-10. DSG Onf, 8 FETs, R41 1 kQ.19Figure 8-10. DSG Onf, 8 FETs, 10 kQ, 470 nF.19Figure 8-11. DSG Off, 8 FETs, R41 1 kQ.19Figure 8-12. DSG On, 8 FETs, 10 kQ, 470 nF.20Figure 8-13. DSG Off, 8 FETs, R41 100 Q.20Figure 8-14. DSG On, 12 FETs, R41 100 Q.20Figure 8-15. DSG Off, 12 FETs, R41 100 Q.20Figure 8-16. DSG On, 12 FETs, R41 100 Q.20Figure 8-17. DSG Off, 12 FETs, R41 100 Q.20Figure 8-16. DSG On, 12 FETs, R41 100 Q.20Figure 8-17. DSG Off, 12 FETs, R41 100 Q.20Figure 8-16. DSG On, 12 FETs, R41 100 Q.20Figure 8-17. DSG Off, 12 FETs, R41 100 Q.20Figure 8-16. DSG Off, 12 FETs, R41 100 Q.20Figure 8-20. DSG Off, 12 FETs, R41 100 Q.20Figure 8-20. DSG Off, 12 FETs, R4                                                                     | <b>o</b>                                         |    |

| Figure 7-3. CHG Driver Turn-Off Current Path. 15   Figure 7-4. CHG Off, 4 FETs, 100 Ohm, No Current. 16   Figure 8-1. DSG On, Single FET, 10 kΩ, 470 nF. 17   Figure 8-2. DSG Off, Single FET, R41 100 Ω. 17   Figure 8-3. Battery Transient With Single FET, R41 100 Ω. 18   Figure 8-4. DSG On, Single FET, 10 kΩ, 470 nF. 18   Figure 8-5. DSG Off, Single FET, R41 1 kΩ. 18   Figure 8-6. DSG On, 2 FETs, 10 kΩ, 470 nF. 19   Figure 8-7. DSG Off, 4 FETs, R41 1 kΩ. 19   Figure 8-8. DSG On, 4 FETs, 10 kΩ, 470 nF. 19   Figure 8-9. DSG Off, 4 FETs, R41 1 kΩ. 19   Figure 8-10. DSG On, 8 FETs, 10 kΩ, 470 nF. 19   Figure 8-10. DSG On, 8 FETs, 10 kΩ, 470 nF. 19   Figure 8-11. DSG Off, 8 FETs, R41 1 kΩ. 19   Figure 8-12. DSG Off, 8 FETs, 10 kΩ, 470 nF. 20   Figure 8-13. DSG Off, 12 FETs, 10 kΩ, 470 nF. 20   Figure 8-13. DSG Off, 12 FETs, 10 kΩ, 470 nF. 20   Figure 8-15. DSG Off, 12 FETs, R41 100 Ω. 20   Figure 8-15. DSG Off, 12 FETs, R41 100 Ω. 20   Figure 8-15. DSG Off, 12 FETs, R41 100 Ω. 20   Figure 8-15. DSG Off, 12 FETs, R41 100 Ω. 20                                                                                                                                                                                                                                                                                                                   |                                                  |    |

| Figure 7-4. CHG Off, 4 FETs, 100 Ohm, No Current. 16   Figure 8-1. DSG On, Single FET, 10 kΩ, 470 nF. 17   Figure 8-2. DSG Off, Single FET, R41 100 Ω. 17   Figure 8-3. Battery Transient With Single FET, R41 100 Ω. 18   Figure 8-3. DSG Off, Single FET, R41 1kΩ. 18   Figure 8-5. DSG Off, Single FET, R41 1 kΩ. 18   Figure 8-6. DSG On, 2 FETs, 10 kΩ, 470 nF. 19   Figure 8-7. DSG Off, 2 FETs, R41 1 kΩ. 19   Figure 8-8. DSG On, 4 FETs, 10 kΩ, 470 nF. 19   Figure 8-9. DSG Off, 4 FETs, R41 1 kΩ. 19   Figure 8-10. DSG Off, 8 FETs, R41 1 kΩ. 19   Figure 8-10. DSG Off, 8 FETs, R41 1 kΩ. 19   Figure 8-11. DSG Off, 8 FETs, R41 1 kΩ. 19   Figure 8-12. DSG Off, 8 FETs, R41 1 kΩ. 19   Figure 8-13. DSG Off, 12 FETs, 10 kQ, 470 nF. 20   Figure 8-14. DSG On, 12 FETs, 10 kQ, 470 nF. 20   Figure 8-15. DSG Off, 12 FETs, R41 100 Ω. 20   Figure 8-16. DSG On, 12 FETs, 10 kQ, PNP.470 nF. 21   Figure 8-15. DSG Off, 12 FETs, R41 100 Ω. 20   Figure 8-16. DSG On, 12 FETs, 100 Ω, No Reverse Charge Circuit. 21   Figure 8-17. DSG Off, 12 FETs, R41 1 kΩ, PNP. 21                                                                                                                                                                                                                                                                                                         |                                                  |    |

| Figure 8-1. DSG On, Single FET, 10 kΩ, 470 nF. 17   Figure 8-2. DSG Off, Single FET, R41 100 Ω 17   Figure 8-3. Battery Transient With Single FET, R41 100 Ω 18   Figure 8-4. DSG On, Single FET, 10 kΩ, 470 nF. 18   Figure 8-5. DSG Off, Single FET, R41 1 kΩ. 18   Figure 8-6. DSG On, 2 FETs, 10 kΩ, 470 nF. 19   Figure 8-7. DSG Off, 2 FETs, R41 1 kΩ. 19   Figure 8-8. DSG On, 4 FETs, 10 kΩ, 470 nF. 19   Figure 8-9. DSG Off, 4 FETs, R41 1 kΩ. 19   Figure 8-10. DSG Off, 8 FETs, R41 1 kΩ. 19   Figure 8-10. DSG Off, 8 FETs, R41 1 kΩ. 19   Figure 8-10. DSG Off, 8 FETs, N0 kΩ, 470 nF. 19   Figure 8-11. DSG Off, 8 FETs, R41 1 kΩ. 19   Figure 8-12. DSG On, 8 FETs, 10 kΩ, 470 nF. 20   Figure 8-13. DSG Off, 8 FETs, R41 100 Ω. 20   Figure 8-14. DSG On, 12 FETs, 10 kΩ, 470 nF. 20   Figure 8-15. DSG Off, 12 FETs, R41 100 Ω. 20   Figure 8-16. DSG Off, 12 FETs, R41 100 Ω. 20   Figure 8-17. DSG Off, 12 FETs, R41 100 Ω. 20   Figure 8-18. DSG Off, 12 FETs, R41 100 Ω. 20   Figure 8-19. DSG Off, 12 FETs, R41 1 KQ. PNP. 21   Figure 8-19.                                                                                                                                                                                                                                                                                                                          | Figure 7-4, CHG Off, 4 FETs, 100 Ohm, No Current |    |

| Figure 8-2. DSG Off, Single FET, R41 100 Ω.17Figure 8-3. Battery Transient With Single FET, R41 100 Ω.18Figure 8-4. DSG On, Single FET, 10 kΩ, 470 nF.18Figure 8-5. DSG Off, Single FET, R41 1 kΩ.19Figure 8-6. DSG On, 2 FETs, 10 kΩ, 470 nF.19Figure 8-7. DSG Off, 2 FETs, R41 1 kΩ.19Figure 8-8. DSG On, 4 FETs, 10 kΩ, 470 nF.19Figure 8-9. DSG Off, 4 FETs, R41 1 kΩ.19Figure 8-10. DSG On, 8 FETs, 10 kΩ, 470 nF.19Figure 8-11. DSG Off, 8 FETs, R41 1 kΩ.19Figure 8-12. DSG Off, 8 FETs, R41 1 kΩ.19Figure 8-13. DSG Off, 8 FETs, R41 1 kΩ.19Figure 8-14. DSG Off, 8 FETs, R41 1 kΩ.19Figure 8-15. DSG Off, 8 FETs, R41 1 kΩ.19Figure 8-10. DSG On, 8 FETs, 10 kΩ, 470 nF.20Figure 8-13. DSG Off, 12 FETs, R41 1 kΩ.20Figure 8-14. DSG On, 12 FETs, 10 kΩ, 470 nF.20Figure 8-15. DSG Off, 12 FETs, R41 1 00 Ω.20Figure 8-15. DSG Off, 12 FETs, R41 1 kΩ, PNP.21Figure 8-17. DSG Off, 12 FETs, R41 1 kΩ, PNP.21Figure 8-17. DSG Off, 12 FETs, R41 1 kΩ, PNP.21Figure 8-18. DSG On, 12 FETs, 10 kΩ, PNP, 470 nF.22Figure 8-19. DSG Off, 12 FETs, 10 0Ω, No Reverse Charge Circuit, 470 nF.22Figure 8-20. DSG Off, 12 FETs, 100 Ω, No Reverse Charge Circuit, 470 nF.22Figure 8-21. P-ch DSG Turn On Circuit.23Figure 8-22. DSG On, 12 FETs, P-ch With 1k Turn On Path, 470 nF.24Figure 8-23. DSG Off, 12 FETs, P-ch With 1k Turn On Path, 470 nF.24 <tr< td=""><td></td><td></td></tr<> |                                                  |    |

| Figure 8-3. Battery Transient With Single FET, R41 100 Ω.18Figure 8-4. DSG On, Single FET, 10 kΩ, 470 nF.18Figure 8-5. DSG Off, Single FET, R41 1 kΩ.19Figure 8-6. DSG On, 2 FETs, 10 kΩ, 470 nF.19Figure 8-7. DSG Off, 2 FETs, R41 1 kΩ.19Figure 8-8. DSG On, 4 FETs, 10 kΩ, 470 nF.19Figure 8-9. DSG Off, 4 FETs, R41 1 kΩ.19Figure 8-9. DSG Off, 4 FETs, R41 1 kΩ.19Figure 8-10. DSG On, 8 FETs, 10 kΩ, 470 nF.19Figure 8-11. DSG Off, 8 FETs, R41 1 kΩ.19Figure 8-12. DSG On, 8 FETs, 10 kΩ, 470 nF.19Figure 8-13. DSG Off, 8 FETs, R41 1 kΩ.19Figure 8-14. DSG On, 12 FETs, 10 kΩ, 470 nF.20Figure 8-15. DSG Off, 12 FETs, R41 100 Ω.20Figure 8-14. DSG Off, 12 FETs, 10 kΩ, 470 nF.20Figure 8-15. DSG Off, 12 FETs, R41 100 Ω.20Figure 8-16. DSG On, 12 FETs, 10 kΩ, PNP, 470 nF.21Figure 8-17. DSG Off, 12 FETs, R41 100 Ω.20Figure 8-18. DSG Off, 12 FETs, R41 1 kΩ, PNP.21Figure 8-19. DSG Off, 12 FETs, 100 Ω, No Reverse Charge Circuit, 470 nF.22Figure 8-20. DSG Off, 12 FETs, 100 Ω, No Reverse Charge Circuit, 470 nF.22Figure 8-20. DSG Off, 12 FETs, P-ch With 1k Turn On Path, 470 nF.23Figure 8-21. P-ch DSG Turn On Circuit.23Figure 8-22. DSG Off, 12 FETs, P-ch With 1k Turn On Path, 470 nF.24Figure 8-23. DSG Off, 12 FETs, P-ch With 1k Turn On Path, 470 nF.24Figure 8-24. Short Circuit Example.24Figure 8-24. Short Circuit Example.25 <td></td> <td></td>       |                                                  |    |

| Figure 8-4. DSG On, Single FET, 10 kΩ, 470 nF. 18   Figure 8-5. DSG Off, Single FET, R41 1 kΩ. 18   Figure 8-6. DSG On, 2 FETs, 10 kΩ, 470 nF. 19   Figure 8-7. DSG Off, 2 FETs, R41 1 kΩ. 19   Figure 8-8. DSG On, 4 FETs, 10 kΩ, 470 nF. 19   Figure 8-9. DSG Off, 4 FETs, R41 1 kΩ. 19   Figure 8-9. DSG Off, 4 FETs, R41 1 kΩ. 19   Figure 8-10. DSG On, 8 FETs, 10 kΩ, 470 nF. 19   Figure 8-11. DSG Off, 8 FETs, R41 1 kΩ. 19   Figure 8-12. DSG On, 8 FETs, 10 kΩ, 470 nF. 20   Figure 8-13. DSG Off, 8 FETs, R41 100 Ω. 20   Figure 8-14. DSG Off, 12 FETs, R41 100 Ω. 20   Figure 8-15. DSG Off, 12 FETs, R41 100 Ω. 20   Figure 8-16. DSG On, 12 FETs, 10 kΩ, 470 nF. 20   Figure 8-17. DSG Off, 12 FETs, R41 100 Ω. 20   Figure 8-17. DSG Off, 12 FETs, R41 100 Ω. 20   Figure 8-19. DSG On, 12 FETs, 10 kΩ, PNP, 470 nF. 21   Figure 8-19. DSG On, 12 FETs, N0 N, APVerse Charge Protection Circuit. 22   Figure 8-19. DSG On, 12 FETs, 100 Ω, No Reverse Charge Circuit, 470 nF. 22   Figure 8-20. DSG Off, 12 FETs, 100 Ω, No Reverse Charge Circuit. 22   Figure 8-21. P-ch DSG Turn On Circuit. <td></td> <td></td>                                                                                                                                                                                                                                                          |                                                  |    |

| Figure 8-6. DSG On, 2 FETs, 10 kΩ, 470 nF. 19   Figure 8-7. DSG Off, 2 FETs, R41 1 kΩ. 19   Figure 8-8. DSG On, 4 FETs, 10 kΩ, 470 nF. 19   Figure 8-9. DSG Off, 4 FETs, R41 1 kΩ. 19   Figure 8-10. DSG On, 8 FETs, 10 kΩ, 470 nF. 19   Figure 8-11. DSG Off, 8 FETs, R41 1 kΩ. 19   Figure 8-11. DSG Off, 8 FETs, R41 1 kΩ. 19   Figure 8-12. DSG On, 8 FETs, 10 kΩ, 470 nF. 20   Figure 8-13. DSG Off, 8 FETs, R41 100 Ω. 20   Figure 8-14. DSG On, 12 FETs, 10 kΩ, 470 nF. 20   Figure 8-15. DSG Off, 12 FETs, R41 100 Ω. 20   Figure 8-16. DSG On, 12 FETs, 10 kΩ, 470 nF. 20   Figure 8-15. DSG Off, 12 FETs, R41 100 Ω. 20   Figure 8-16. DSG On, 12 FETs, 10 kΩ, PNP, 470 nF. 20   Figure 8-17. DSG Off, 12 FETs, R41 1 kΩ, PNP. 21   Figure 8-18. DSG Drive Without Reverse Charge Protection Circuit. 22   Figure 8-19. DSG On, 12 FETs, 100 Ω, No Reverse Charge Circuit, 470 nF. 22   Figure 8-20. DSG Off, 12 FETs, 100 Ω, No Reverse Charge Circuit. 22   Figure 8-21. P-ch DSG Turn On Circuit. 23   Figure 8-22. DSG On, 12 FETs, P-ch With 1k Turn On Path, 470 nF. 24   Figure 8-24. Short Circu                                                                                                                                                                                                                                                                           |                                                  |    |

| Figure 8-7. DSG Off, 2 FETs, R41 1 kΩ.19Figure 8-8. DSG On, 4 FETs, 10 kΩ, 470 nF.19Figure 8-9. DSG Off, 4 FETs, R41 1 kΩ.19Figure 8-10. DSG On, 8 FETs, 10 kΩ, 470 nF.19Figure 8-11. DSG Off, 8 FETs, R41 1 kΩ.19Figure 8-12. DSG On, 8 FETs, 10 kΩ, 470 nF.20Figure 8-13. DSG Off, 8 FETs, R41 10 Ω.20Figure 8-14. DSG On, 12 FETs, 10 kΩ, 470 nF.20Figure 8-15. DSG Off, 12 FETs, 10 kΩ, 470 nF.20Figure 8-15. DSG Off, 12 FETs, 10 kΩ, 470 nF.20Figure 8-15. DSG Off, 12 FETs, 10 kΩ, 470 nF.20Figure 8-15. DSG Off, 12 FETs, 10 kΩ, PNP, 470 nF.21Figure 8-16. DSG On, 12 FETs, 10 kΩ, PNP, 470 nF.21Figure 8-17. DSG Off, 12 FETs, R41 1 kΩ, PNP.21Figure 8-18. DSG Drive Without Reverse Charge Protection Circuit.22Figure 8-19. DSG On, 12 FETs, 100 Ω, No Reverse Charge Circuit, 470 nF.22Figure 8-20. DSG Off, 12 FETs, 100 Ω, No Reverse Charge Circuit.22Figure 8-21. P-ch DSG Turn On Circuit.23Figure 8-22. DSG On, 12 FETs, P-ch With 1k Turn On Path, 470 nF.24Figure 8-23. DSG Off, 12 FETs, P-ch With 1k Turn On Path, 100 Ω.24Figure 8-24. Short Circuit Example.24Figure 8-24. Short Circuit Example.24Figure 9-2. DSG Loaded With 36-V Battery.26                                                                                                                                                                                                                     | Figure 8-5. DSG Off, Single FET, R41 1 kΩ        | 18 |

| Figure 8-8. DSG On, 4 FETs, 10 kΩ, 470 nF.19Figure 8-9. DSG Off, 4 FETs, R41 1 kΩ.19Figure 8-10. DSG On, 8 FETs, 10 kΩ, 470 nF.19Figure 8-11. DSG Off, 8 FETs, R41 1 kΩ.19Figure 8-12. DSG On, 8 FETs, R41 1 kΩ.19Figure 8-13. DSG Off, 8 FETs, R41 1 kΩ.20Figure 8-14. DSG On, 12 FETs, R41 1 kΩ.20Figure 8-15. DSG Off, 8 FETs, R41 100 Ω.20Figure 8-15. DSG Off, 12 FETs, R41 100 Ω.20Figure 8-15. DSG Off, 12 FETs, R41 100 Ω.20Figure 8-16. DSG On, 12 FETs, 10 kΩ, PNP, 470 nF.21Figure 8-17. DSG Off, 12 FETs, R41 1 kΩ, PNP.21Figure 8-18. DSG Drive Without Reverse Charge Protection Circuit.22Figure 8-19. DSG Off, 12 FETs, 100 Ω, No Reverse Charge Circuit, 470 nF.22Figure 8-20. DSG Off, 12 FETs, 100 Ω, No Reverse Charge Circuit.22Figure 8-21. P-ch DSG Turn On Circuit.23Figure 8-22. DSG Off, 12 FETs, P-ch With 1k Turn On Path, 470 nF.24Figure 8-23. DSG Off, 12 FETs, P-ch With 1k Turn On Path, 100 Ω.24Figure 8-24. Short Circuit Example.24Figure 9-1. DSG Turn On Current Path.25Figure 9-2. DSG Loaded With 36-V Battery.26                                                                                                                                                                                                                                                                                                                                    | Figure 8-6. DSG On, 2 FETs, 10 kΩ, 470 nF        | 19 |

| Figure 8-9. DSG Off, 4 FETs, R41 1 kΩ.19Figure 8-10. DSG On, 8 FETs, 10 kΩ, 470 nF.19Figure 8-11. DSG Off, 8 FETs, R41 1 kΩ.19Figure 8-12. DSG On, 8 FETs, 10 kΩ, 470 nF.20Figure 8-13. DSG Off, 8 FETs, R41 100 Ω.20Figure 8-14. DSG On, 12 FETs, 10 kΩ, 470 nF.20Figure 8-15. DSG Off, 12 FETs, R41 100 Ω.20Figure 8-16. DSG On, 12 FETs, 10 kΩ, 470 nF.20Figure 8-17. DSG Off, 12 FETs, R41 100 Ω.20Figure 8-16. DSG On, 12 FETs, 10 kΩ, PNP, 470 nF.21Figure 8-17. DSG Off, 12 FETs, R41 1 kΩ, PNP.21Figure 8-18. DSG Drive Without Reverse Charge Protection Circuit.22Figure 8-19. DSG Off, 12 FETs, 100 Ω, No Reverse Charge Circuit, 470 nF.22Figure 8-20. DSG Off, 12 FETs, 100 Ω, No Reverse Charge Circuit, 470 nF.22Figure 8-21. P-ch DSG Turn On Circuit.23Figure 8-22. DSG Off, 12 FETs, P-ch With 1k Turn On Path, 470 nF.24Figure 8-23. DSG Off, 12 FETs, P-ch With 1k Turn On Path, 100 Ω.24Figure 8-24. Short Circuit Example.24Figure 9-1. DSG Turn On Current Path.25Figure 9-2. DSG Loaded With 36-V Battery.26                                                                                                                                                                                                                                                                                                                                                         | Figure 8-7. DSG Off, 2 FETs, R41 1 kΩ            | 19 |

| Figure 8-10. DSG On, 8 FETs, 10 kΩ, 470 nF.19Figure 8-11. DSG Off, 8 FETs, R41 1 kΩ.19Figure 8-12. DSG On, 8 FETs, 10 kΩ, 470 nF.20Figure 8-13. DSG Off, 8 FETs, R41 100 Ω.20Figure 8-14. DSG On, 12 FETs, 10 kΩ, 470 nF.20Figure 8-15. DSG Off, 12 FETs, R41 100 Ω.20Figure 8-16. DSG On, 12 FETs, 10 kΩ, PNP, 470 nF.20Figure 8-17. DSG Off, 12 FETs, R41 1 kΩ, PNP.21Figure 8-18. DSG Drive Without Reverse Charge Protection Circuit.22Figure 8-19. DSG Off, 12 FETs, 100 Ω, No Reverse Charge Circuit, 470 nF.22Figure 8-20. DSG Off, 12 FETs, 100 Ω, No Reverse Charge Circuit.22Figure 8-21. P-ch DSG Turn On Circuit.22Figure 8-23. DSG Off, 12 FETs, P-ch With 1k Turn On Path, 470 nF.24Figure 8-23. DSG Off, 12 FETs, P-ch With 1k Turn On Path, 100 Ω.24Figure 8-24. Short Circuit Example.24Figure 9-1. DSG Turn On Current Path.25Figure 9-2. DSG Loaded With 36-V Battery.26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                  |    |

| Figure 8-11. DSG Off, 8 FETs, R41 1 kΩ.19Figure 8-12. DSG On, 8 FETs, 10 kΩ, 470 nF.20Figure 8-13. DSG Off, 8 FETs, R41 100 Ω.20Figure 8-14. DSG On, 12 FETs, 10 kΩ, 470 nF.20Figure 8-15. DSG Off, 12 FETs, R41 100 Ω.20Figure 8-16. DSG On, 12 FETs, 10 kΩ, PNP, 470 nF.20Figure 8-17. DSG Off, 12 FETs, R41 1 kΩ, PNP.21Figure 8-18. DSG Drive Without Reverse Charge Protection Circuit.22Figure 8-19. DSG On, 12 FETs, 10 kΩ, No Reverse Charge Circuit, 470 nF.22Figure 8-20. DSG Off, 12 FETs, 100 Ω, No Reverse Charge Circuit.22Figure 8-20. DSG Off, 12 FETs, 100 Ω, No Reverse Charge Circuit.22Figure 8-21. P-ch DSG Turn On Circuit.23Figure 8-22. DSG On, 12 FETs, P-ch With 1k Turn On Path, 470 nF.24Figure 8-23. DSG Off, 12 FETs, P-ch With 1k Turn On Path, 100 Ω.24Figure 8-24. Short Circuit Example.24Figure 9-1. DSG Turn On Current Path.25Figure 9-2. DSG Loaded With 36-V Battery.26                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Figure 8-9. DSG Off, 4 FETs, R41 1 kΩ            | 19 |

| Figure 8-12. DSG On, 8 FETs, 10 kΩ, 470 nF.20Figure 8-13. DSG Off, 8 FETs, R41 100 Ω.20Figure 8-14. DSG On, 12 FETs, 10 kΩ, 470 nF.20Figure 8-15. DSG Off, 12 FETs, R41 100 Ω.20Figure 8-16. DSG On, 12 FETs, R41 100 Ω.20Figure 8-17. DSG Off, 12 FETs, R41 1 kΩ, PNP.21Figure 8-18. DSG Drive Without Reverse Charge Protection Circuit.22Figure 8-19. DSG On, 12 FETs, 100 Ω, No Reverse Charge Circuit, 470 nF.22Figure 8-20. DSG Off, 12 FETs, 100 Ω, No Reverse Charge Circuit.22Figure 8-21. P-ch DSG Turn On Circuit.23Figure 8-22. DSG On, 12 FETs, P-ch With 1k Turn On Path, 470 nF.24Figure 8-23. DSG Off, 12 FETs, P-ch With 1k Turn On Path, 100 Ω.24Figure 8-24. Short Circuit Example.24Figure 9-1. DSG Turn On Current Path.25Figure 9-2. DSG Loaded With 36-V Battery.26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                  |    |

| Figure 8-13. DSG Off, 8 FETs, R41 100 Ω                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Figure 8-11. DSG Off, 8 FETs, R41 1 kΩ           | 19 |

| Figure 8-14. DSG On, 12 FETs, 10 k $\Omega$ , 470 nF.20Figure 8-15. DSG Off, 12 FETs, R41 100 $\Omega$ .20Figure 8-16. DSG On, 12 FETs, 10 k $\Omega$ , PNP, 470 nF.21Figure 8-17. DSG Off, 12 FETs, R41 1 k $\Omega$ , PNP.21Figure 8-18. DSG Drive Without Reverse Charge Protection Circuit.22Figure 8-19. DSG On, 12 FETs, 100 $\Omega$ , No Reverse Charge Circuit, 470 nF.22Figure 8-20. DSG Off, 12 FETs, 100 $\Omega$ , No Reverse Charge Circuit.22Figure 8-21. P-ch DSG Turn On Circuit.23Figure 8-22. DSG On, 12 FETs, P-ch With 1k Turn On Path, 470 nF.24Figure 8-23. DSG Off, 12 FETs, P-ch With 1k Turn On Path, 100 $\Omega$ .24Figure 8-24. Short Circuit Example.24Figure 9-1. DSG Turn On Current Path.25Figure 9-2. DSG Loaded With 36-V Battery.26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                  |    |

| Figure 8-15. DSG Off, 12 FETs, R41 100 $\Omega$ .20Figure 8-16. DSG On, 12 FETs, 10 k $\Omega$ , PNP, 470 nF.21Figure 8-17. DSG Off, 12 FETs, R41 1 k $\Omega$ , PNP.21Figure 8-18. DSG Drive Without Reverse Charge Protection Circuit.22Figure 8-19. DSG On, 12 FETs, 100 $\Omega$ , No Reverse Charge Circuit, 470 nF.22Figure 8-20. DSG Off, 12 FETs, 100 $\Omega$ , No Reverse Charge Circuit.22Figure 8-21. P-ch DSG Turn On Circuit.23Figure 8-22. DSG On, 12 FETs, P-ch With 1k Turn On Path, 470 nF.24Figure 8-23. DSG Off, 12 FETs, P-ch With 1k Turn On Path, 100 $\Omega$ .24Figure 8-24. Short Circuit Example.24Figure 9-1. DSG Turn On Current Path.25Figure 9-2. DSG Loaded With 36-V Battery.26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                  |    |

| Figure 8-16. DSG On, 12 FETs, 10 k $\Omega$ , PNP, 470 nF.21Figure 8-17. DSG Off, 12 FETs, R41 1 k $\Omega$ , PNP.21Figure 8-18. DSG Drive Without Reverse Charge Protection Circuit.22Figure 8-19. DSG On, 12 FETs, 100 $\Omega$ , No Reverse Charge Circuit, 470 nF.22Figure 8-20. DSG Off, 12 FETs, 100 $\Omega$ , No Reverse Charge Circuit.22Figure 8-21. P-ch DSG Turn On Circuit.23Figure 8-22. DSG On, 12 FETs, P-ch With 1k Turn On Path, 470 nF.24Figure 8-23. DSG Off, 12 FETs, P-ch With 1k Turn On Path, 100 $\Omega$ .24Figure 8-24. Short Circuit Example.24Figure 9-1. DSG Turn On Current Path.25Figure 9-2. DSG Loaded With 36-V Battery.26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                  |    |

| Figure 8-17. DSG Off, 12 FETs, R41 1 k $\Omega$ , PNP.21Figure 8-18. DSG Drive Without Reverse Charge Protection Circuit.22Figure 8-19. DSG On, 12 FETs, 100 $\Omega$ , No Reverse Charge Circuit, 470 nF.22Figure 8-20. DSG Off, 12 FETs, 100 $\Omega$ , No Reverse Charge Circuit.22Figure 8-21. P-ch DSG Turn On Circuit.23Figure 8-22. DSG On, 12 FETs, P-ch With 1k Turn On Path, 470 nF.24Figure 8-23. DSG Off, 12 FETs, P-ch With 1k Turn On Path, 100 $\Omega$ .24Figure 8-24. Short Circuit Example.24Figure 9-1. DSG Turn On Current Path.25Figure 9-2. DSG Loaded With 36-V Battery.26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                  |    |

| Figure 8-18. DSG Drive Without Reverse Charge Protection Circuit.22Figure 8-19. DSG On, 12 FETs, 100 $\Omega$ , No Reverse Charge Circuit, 470 nF.22Figure 8-20. DSG Off, 12 FETs, 100 $\Omega$ , No Reverse Charge Circuit.22Figure 8-21. P-ch DSG Turn On Circuit.23Figure 8-22. DSG On, 12 FETs, P-ch With 1k Turn On Path, 470 nF.24Figure 8-23. DSG Off, 12 FETs, P-ch With 1k Turn On Path, 100 $\Omega$ .24Figure 8-24. Short Circuit Example.24Figure 9-1. DSG Turn On Current Path.25Figure 9-2. DSG Loaded With 36-V Battery.26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                  |    |

| Figure 8-19. DSG On, 12 FETs, 100 $\Omega$ , No Reverse Charge Circuit, 470 nF.22Figure 8-20. DSG Off, 12 FETs, 100 $\Omega$ , No Reverse Charge Circuit.22Figure 8-21. P-ch DSG Turn On Circuit.23Figure 8-22. DSG On, 12 FETs, P-ch With 1k Turn On Path, 470 nF.24Figure 8-23. DSG Off, 12 FETs, P-ch With 1k Turn On Path, 100 $\Omega$ .24Figure 8-24. Short Circuit Example.24Figure 9-1. DSG Turn On Current Path.25Figure 9-2. DSG Loaded With 36-V Battery.26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                  |    |

| Figure 8-20. DSG Off, 12 FETs, 100 Ω, No Reverse Charge Circuit. 22   Figure 8-21. P-ch DSG Turn On Circuit. 23   Figure 8-22. DSG On, 12 FETs, P-ch With 1k Turn On Path, 470 nF. 24   Figure 8-23. DSG Off, 12 FETs, P-ch With 1k Turn On Path, 100 Ω. 24   Figure 8-24. Short Circuit Example. 24   Figure 9-1. DSG Turn On Current Path. 25   Figure 9-2. DSG Loaded With 36-V Battery. 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                  |    |

| Figure 8-21. P-ch DSG Turn On Circuit.23Figure 8-22. DSG On, 12 FETs, P-ch With 1k Turn On Path, 470 nF.24Figure 8-23. DSG Off, 12 FETs, P-ch With 1k Turn On Path, 100 Ω.24Figure 8-24. Short Circuit Example.24Figure 9-1. DSG Turn On Current Path.25Figure 9-2. DSG Loaded With 36-V Battery.26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                  |    |

| Figure 8-22. DSG On, 12 FETs, P-ch With 1k Turn On Path, 470 nF. 24   Figure 8-23. DSG Off, 12 FETs, P-ch With 1k Turn On Path, 100 Ω. 24   Figure 8-24. Short Circuit Example. 24   Figure 9-1. DSG Turn On Current Path. 25   Figure 9-2. DSG Loaded With 36-V Battery. 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                  |    |

| Figure 8-23. DSG Off, 12 FETs, P-ch With 1k Turn On Path, 100 Ω.24Figure 8-24. Short Circuit Example.24Figure 9-1. DSG Turn On Current Path.25Figure 9-2. DSG Loaded With 36-V Battery.26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                  |    |

| Figure 8-24. Short Circuit Example. 24   Figure 9-1. DSG Turn On Current Path. 25   Figure 9-2. DSG Loaded With 36-V Battery. 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                  |    |

| Figure 9-1. DSG Turn On Current Path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                  |    |

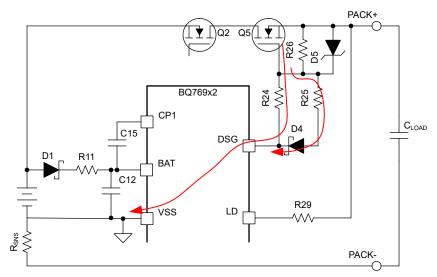

| Figure 9-2. DSG Loaded With 36-V Battery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                  |    |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>v</b>                                         |    |

| Figure 9-3. DSG Turn-Off Current Path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | •                                                |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Figure 9-3. DSG Turn-Off Current Path            | 26 |

#### List of Tables

# Trademarks

All trademarks are the property of their respective owners.

#### **1** Introduction

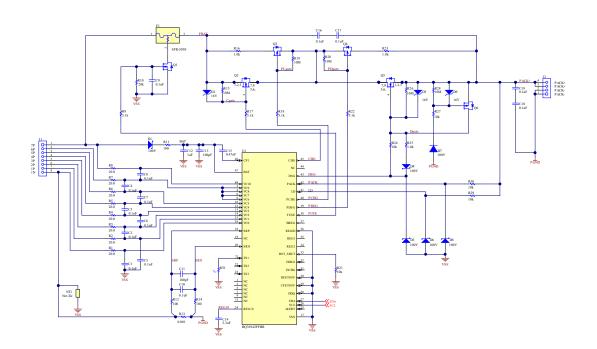

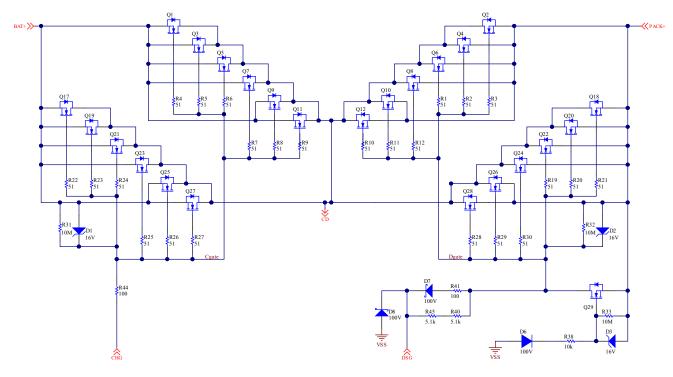

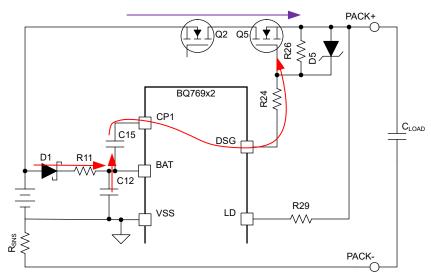

A typical battery has one set of terminals for both charge and discharge. Current passes through charge and discharge FETs arranged in series. Since the current flows through both FETs, the size and quantity used for charge and discharge are the same. The BQ76952 family of battery monitors consisting of the BQ76942 and BQ76952 support high-side series FETs. References to the BQ76952 in this document will generally apply to all family members unless specifically indicated. A typical schematic with the BQ76942 and series FETs is shown in Figure 1-1. The schematic is for a 7-cell implementation and includes pre-charge and pre-discharge FETs. The pre-charge path is used to limit current into the battery from a fixed voltage charger when the battery is deeply discharged. The pre-discharge path is used to charge high capacitive loads without a high current spike. With the series FETs, there is the possibility of charging through a disabled discharge FET or discharging through a disabled charge FET. The current through the body diode of the disabled FET can produce significant heat, so the BQ76952 devices use a body diode protection feature to enable the FET when current is flowing in the non-protected direction.

The cell count and circuit configuration around the and low voltage pins of the device will vary with the implementation and will typically not be shown in further schematics in this application report. Like the main power FETs, the pre-charge and pre-discharge FETs must be selected for the application. The pre-charge and pre-discharge circuits are relatively low current to avoid high power in the battery pack and are not a focus of this application report.

# 2 Reverse Charge Circuit

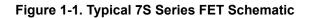

The schematic includes a reverse charge circuit consisting of Q6 and the components surrounding its gate. The purpose of the circuit is to hold the gate of the discharge power FET at the source potential to keep it off when the PACK+ terminal is pulled below VSS. This circuit can be an important feature when a system uses a common connector such as a coaxial power connector for the charger. Since adapters with both polarities are available in the market, the incorrect charger could be attached resulting in both the battery and charger pushing current in the same direction. A discharge fault will occur and the PACK+ terminal could be pulled below VSS and the battery-. Since DSG does not go below VSS of the IC, without Q6 the gate of Q5 will be held near VSS while the source (PACK+) is pulled down by the charger. Current continues to flow from the battery as Q5 operates as a source follower, see Figure 2-1.

With the Q6 reverse charge circuit, when PACK+ is pulled below VSS the source of Q6 is pulled below its gate which is held up by D7 and R27. When Q6 turns on it pulls the Q5 gate to its source keeping the discharge FET off. Since DSG of U1 can not go below VSS, voltage is dropped across R24 which must be sized to dissipate the power required for the applied voltage. D4 blocks current through the smaller R25 which is selected for the turn off speed of Q5. DSG is not intended to provide power, D3 will carry the current rather than the IC pin. Similarly LD and PACK pins on U1 are not intended to provide power, D6 and D8 provide a current path when PACK+ is forced below VSS. If PACK+ is sufficiently below VSS, D9 will conduct keeping a safe VGS voltage on the Q6 gate with the additional voltage across R27. R28 keeps Q6 off when PACK+ is in a normal range. Figure 2-2 shows an example of the reverse charge circuit operation.

#### **3 Reverse Charge Component Selection**

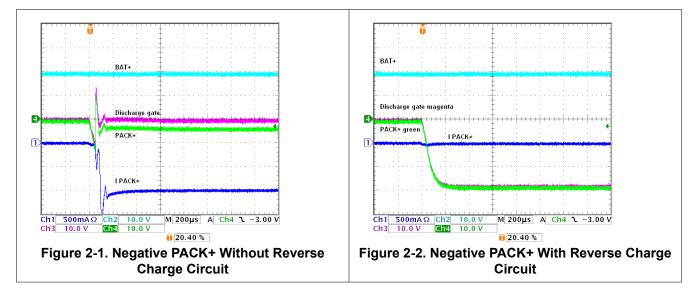

Component values used in the test are shown in the schematic Figure 1-1. Understanding the circuit operation is easier when the circuit is redrawn to clearly show the current paths as in Figure 3-1.

Figure 3-1. Reverse Charge Current Paths

With the reversed charger attached the PACK+ terminal will have a significant negative voltage. The main battery current path must not be conducting and the discharge FET Q5 must be able to withstand the battery voltage plus the reversed charger voltage. In most cases this will be at least twice the maximum battery voltage. Any component placed across the discharge FET should have a similar rating.

The LD pin resistor R29 should be the value recommended in the data sheet. When resistors with low power rating are used select a series or parallel combination of resistors to achieve the desired resistance and a suitable power dissipation when PACK+ is at its lowest value. D6 avoids current and ABS MAX violation for the BQ769x2 LD pin.

The Q6 transistor clamps the Q5 discharge FET gate to its source to keep the discharge FET off during the reverse charger application. D3 carries current to avoid violating the ABS MAX limit of the DSG pin. R24 must have a value large enough and have a power rating to support the reversed charger voltage.  $R_{CLAMP}$  is not shown in Figure 1-1 but included in Figure 3-1 since it is sometimes used to slow turn off of the Q5 FET when PACK+ goes below PACK- due to inductance in the load during turn off. When  $R_{CLAMP}$  is used it forms a voltage divider with R24 and the value must be small enough to keep Q5 off during the reversed charger voltage application.

The Q6 transistor is turned on by the voltage divider formed by R27 and R28. Generally R27 is small and R28 is large so that the gate voltage will come on quickly as PACK+ goes negative with the Q6 gate voltage limited by D9. R27 should be large enough to withstand the power dissipation while the reversed charger is applied. D7 biases R27 during the reversed charger application but blocks drain of the pack through R27 during normal positive voltage on PACK+. The capacitance of D7 also provides a capacitive divider with D9 and the Ciss of Q6 which could allow enough gate voltage for Q6 to conduct during dynamic movement of PACK+. If this is a concern in a design use a low capacitance diode for D7 or add capacitance to the Q6 gate.

# 4 Charge Pump (and FET Turn On)

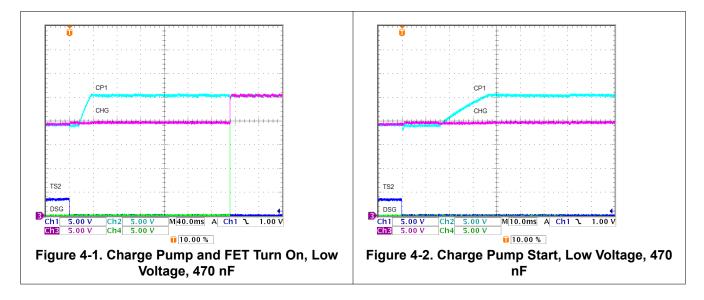

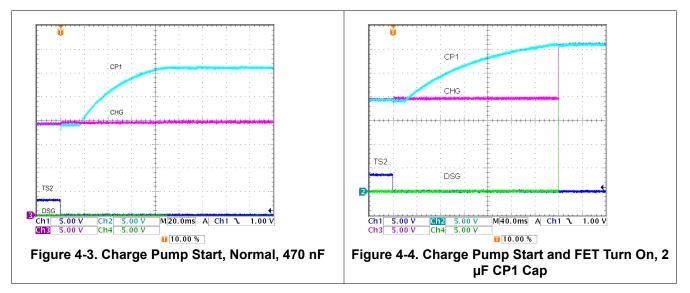

The BQ76952 uses a charge pump to provide a voltage above the battery+ to turn on the high-side N-channel MOSFETs used in the system. The flying capacitor for the charge pump is internal, charge is stored in the CP1 capacitor external to the device. CP1 is the supply for the CHG and DSG drivers. In figures Figure 4-1 to Figure 4-4 the BQ76952 has been set to SHUTDOWN mode and is awakened by the TS2 signal. When the charge pump is at voltage it will turn off until its voltage drops and it runs again. It is common to see a ripple on the CP1 voltage, a slow drop followed by a rapid rise. In Figure 4-1 notice the slow cycling before the FETs turn on and the faster ripple once the FETs are on with the added load of the  $R_{GS}$  resistors and the load of the additional scope probes. Figure 4-2 shows more detail of the charge pump ramp at low voltage. Rise time is longer at the normal voltage shown in Figure 4-3. Using a larger CP1 capacitor also increases the rise time as in Figure 4-4. Notice the charge pump is still transitioning as the FETs turn on. Using a CP1 capacitor larger than 2.2  $\mu$ F is not recommended with the BQ769x2 family devices.

The rounded shape of the CP1 signal at startup indicates the charge pump can produce more current at a lower voltage. CP1 is the power supply for the high side FET drivers. When CHG or DSG turn on the current for the CHG and DSG to turn on the FETs comes from the CP1 capacitor. As an approximation with ideal switching charge is not lost and the charge on the CP1 capacitor before turn on is distributed between CP1 and the FET gate capacitance after turn on.

Charge Pump (and FET Turn On)

(1)

(2)

$Q = V1 \times C_{CP1} = V2 \times (C_{CP1} + (N \times Ciss))$

So the voltage after turn on will be a ratio of the initial voltage.

$$V2 = V1 \times C_{CP1} / (C_{CP1} + (N \times Ciss))$$

where

- V1 is the charge pump voltage before switching on the FETs

- V2 is the charge pump and FET gate voltage after switching on the FETs

- C<sub>CP1</sub> is the charge pump capacitor

- N is the number of FETs switching

- Ciss is the gate capacitance of the FET used

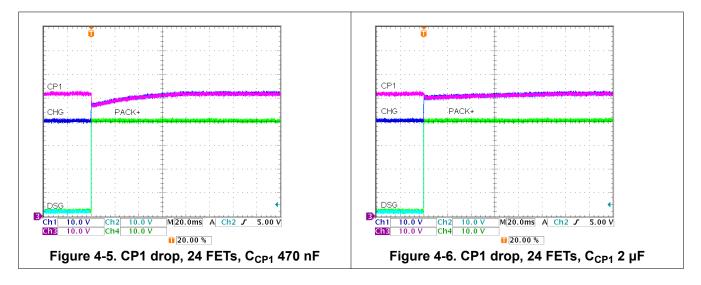

The charge pump will take time to replenish the charge transferred to the gates and bring the voltage back to the regulated CP1 voltage range. Figure 4-5 shows the drop in charge pump voltage turning on 24 CSD19536KCS FETs when using a 470 nF for C<sub>CP1</sub>. Figure 4-6 shows the smaller drop when turning on the same 24 FETs when using 2  $\mu$ F for C<sub>CP1</sub>.

7

# **5 Parallel FET Test Circuits**

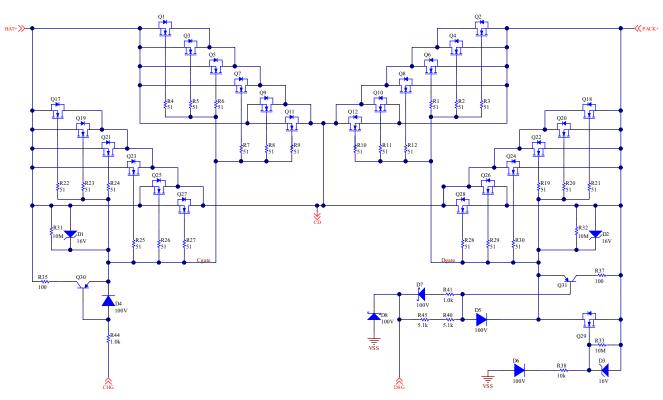

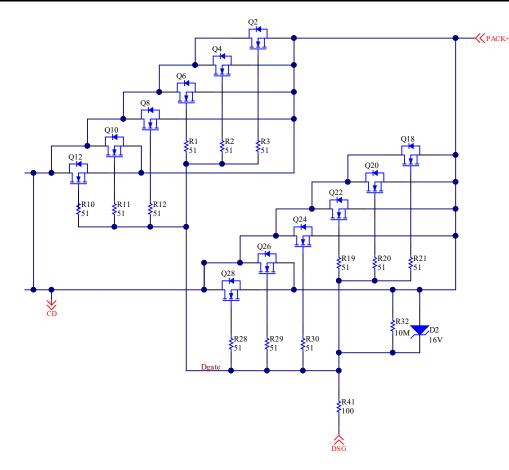

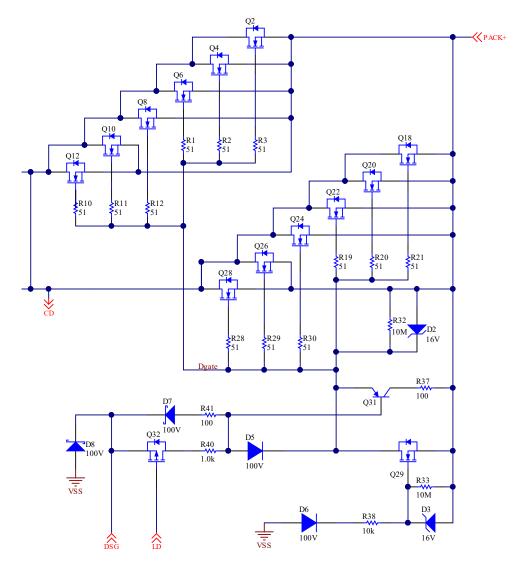

When FETs are operated in parallel they can oscillate when switching. A small resistance or ferrite bead is often used in the individual gate path to avoid the oscillation. Figure 5-1 shows a test circuit with multiple FETs.  $51-\Omega$  resistors are used in the test circuits of this application report to isolate the individual gates from the common Cgate and Dgate signals. Cgate and Dgate are commonly used in the figures in this document rather than an individual gate voltage unless noted. When a single FET is used the  $51-\Omega$  resistor remains. FETs are populated as needed, the remainder of the BQ769x2 schematic remains the same. The CSD19536KCS FETs used in this application note have a typical Ciss of 9.25 nF. R41 and R44 are adjusted for the number of FETs. The reverse charge circuit is retained in the parallel FET test circuits, Q29 is the clamping FET.

Figure 5-1. Multiple FET Test Circuit

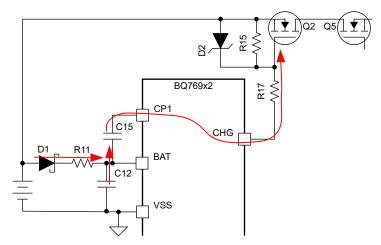

The BQ769x2 has internal driver resistances, so for larger loads, a local turn off circuit may be used. Figure 5-2 shows a circuit where PNP transistors are used to provide a local current loop for turn off of the FETs. The allows turn off with a smaller current loop through the transistor and external resistance. During charge FET turn off CHG draws base current from Q30 through R44 while the collector current discharges the charge FET gates through R35. Similarly DSG draws base current for Q31 through the combination of R40, R45, R41 and D7. The collector current discharges the FET gates through R37. Turn on is still from the charge pump capacitor through D4 for CHG and D5 for DSG. When the diode drop across D4 and D5 is a concern a Schottky type diode could be used or a large value parallel resistor may be added to bring the gates to full voltage after the initial current surge.

Figure 5-2. Multiple FET Test Circuit With Local Current Loops

#### 6 CHG Driver

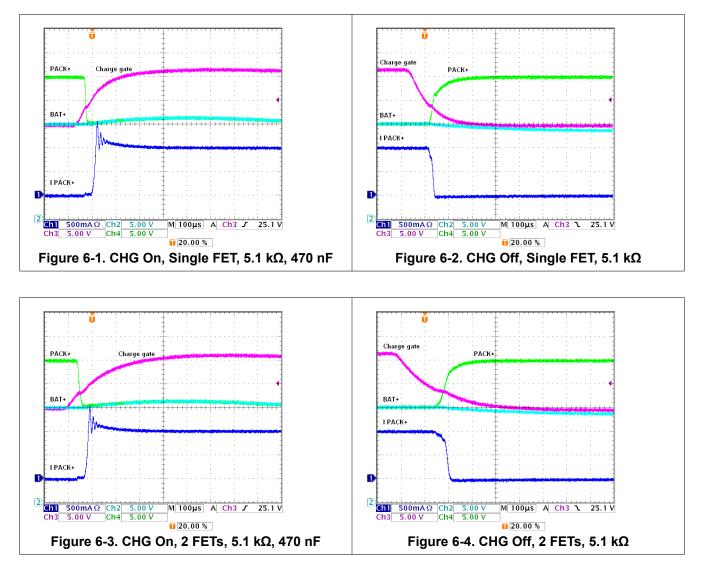

The charge driver operates between the BAT pin level and the CP1 voltage. Figure 6-1 to Figure 6-18 show examples for the charge driver switching different FET counts with different circuit connections. In many of the waveforms the current and some voltages show ripple where the connected equipment settled into regulation with the new load. Charge waveform examples are at 20-V and 1-A charge current.

Figure 6-1 to Figure 6-4 show turn on and off of one and 2 FETs with R44 = 5.1 k $\Omega$ . The added capacitance of the second gate slows the turn on and off.

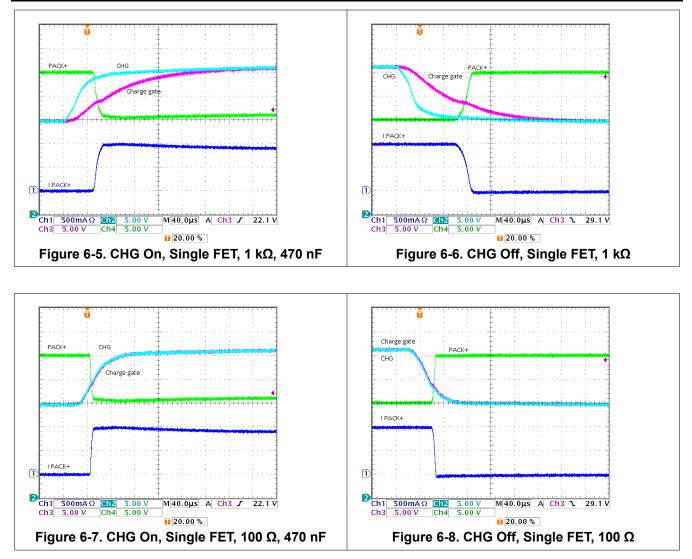

Figure 6-5 to Figure 6-8 show turn on and off with R44 replaced with 1 k $\Omega$  then 100  $\Omega$ . The difference between the CHG pin and common charge gate (Cgate) net can be observed. The smaller resistor drives the gate faster and the larger gate load slows the pin transition.

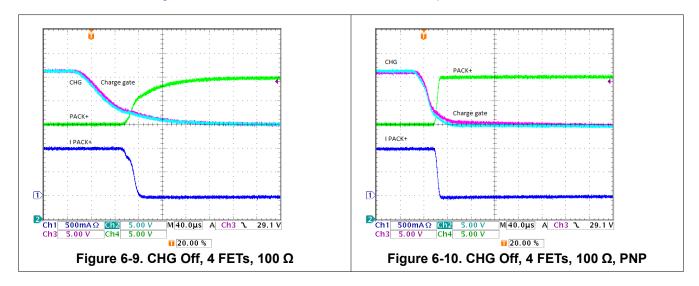

With more FETs switching is slowed as the resistance acts on the gate capacitance. Figure 6-9 shows turn off of 4 FETs using R44 at 100  $\Omega$ . For faster switching the local current loop created by a PNP transistor controlled by the BQ769x2 CHG pin shown in Figure 5-2 allows the gate to discharge through a lower resistance for a faster transition as shown in Figure 6-10. R44 remains at 100  $\Omega$  for this example.

Switching 8 FETs with R44 at 100  $\Omega$  and without the PNP is shown in Figure 6-11. The slow transition would indicate most of the resistance is internal to the CHG driver. Figure 6-12 shows that even with R44 at 5.1 k $\Omega$  the turn off time is must faster as the CHG pin only sinks the base current for the PNP. The 5.1-k $\Omega$  R44 does slow turn on as shown in Figure 6-13, using 100- $\Omega$  R44 in Figure 6-14 increases turn on speed although the 100  $\Omega$  was not needed for turn off.

In a wider time scale Figure 6-15 and Figure 6-16 show the effect of the charge pump capacitor size on switching 8 FETs.

With 2  $\mu$ F of CP1 capacitance, Figure 6-17 and Figure 6-18 show turn on and off of 12 FETs with R44 100  $\Omega$  and the PNP circuit. Adjusting the turn off speed using the R35 value is not shown in this report.

# 7 CHG Driver Current Paths

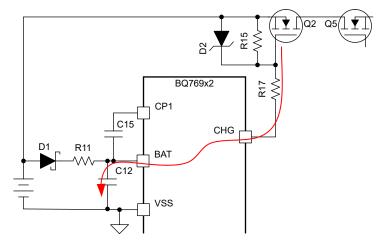

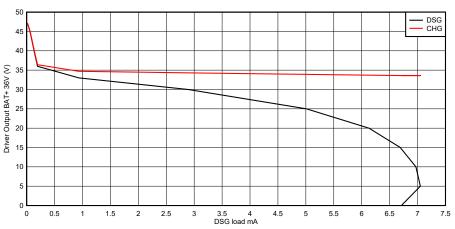

The drive strength of the CHG driver is a common question, but it does not have a simple answer. The driver was designed to provided a controlled turn on and turn off of FETs with the load capacitance. It is not rated in amps as some general purpose gate drivers or by resistance, but characterized for the rise and fall times shown in the data sheet. At CHG turn-on current flows from the CP1 capacitor out the CHG pin to the FET gates as shown in Figure 7-1. Measuring at low current may show an internal resistance of 1 to 2 k $\Omega$  but the switch is not linear and will limit current. The charge pump provides limited current so the current to charge the FET gates comes from the CP1 capacitor C15 and distributes the charge from the CP1 capacitor to the capacitor and gate capacitances. A larger CP1 capacitor will allow less droop during turn on as previously shown in Figure 6-15 and Figure 6-16. Current from the CP1 capacitor C15 is held up by C12 and made up by current flow through D1 and R11. The CHG pin resistor R<sub>GATE</sub> (R17) is not recommended below 100  $\Omega$  to provide some isolation for the pin from the current path.

Figure 7-1. CHG Driver Turn-On Current Path

When the BQ769x2 is in SHUTDOWN mode the CHG pin is allowed to fall to VSS. In the normal circuit however the charge FET gate-source Zener D2 and resistor R15 will hold the CHG pin voltage at the battery voltage level.

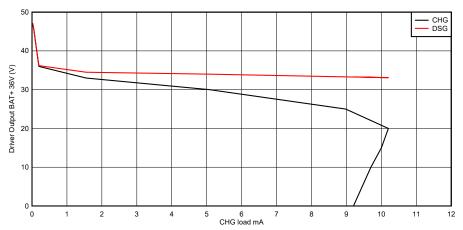

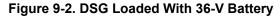

The typical recommended gate-source resistor (R15) is 10 M $\Omega$  providing about 1.1-µA load when the charge pump is operated at the V<sub>(FETON\_HI)</sub> level. While any load will cause the charge pump voltage to drop some, the charge pump can typically maintan 10 V with up to about 40-µA load on the drivers. The charge pump is shared with the DSG driver so its load must also be considered. As the CHG driver is loaded its voltage will drop and also cause the DSG pin voltage to drop if DSG is also on. An example is shown in Figure 7-2. The charge pump can provide approximately 200 µA into a shorted gate-source resistor. There is a supply current gain of about 6 to provide that short circuit current, so the BAT pin current will increase approximately 1200 µA to provide that 200 µA to CHG. When the CHG driver is pulled down more it will go below the BAT pin voltage, current is limited. If implementing a circuit to override the CHG output, provide some margin above the charge pump capability to be sure the charge FET is off. Also be aware of the pull down of DSG, the reduced voltage will leave the discharge FET operating as a source follower. It may be beneficial to signal turn off of the DSG FET output with the DFETOFF input to the BQ769x2 when available.

Figure 7-2. CHG Loaded With 36-V Battery

When the CHG driver turns off, CHG is pulled to the BAT pin and the Ciss of the charge FETs discharges to the BAT pin capacitance C12 as shown in Figure 7-3. The pulldown will look like about 1 k $\Omega$ , but will vary with the voltage. This can temporarily raise the BAT pin voltage until the supply current load of the BQ769x2 reduces the voltage of BAT to the normal level. An example rise of the BAT pin with turn-off with 4 FETs is shown in Figure 7-4. C12 should not be made smaller than the typical 1  $\mu$ F to avoid voltage rise of BAT. Using the local current loop circuit will reduce the current sent to C12 and the resulting voltage rise in addition to speeding up the turn off of the charge FETs as shown in the difference between Figure 6-9 and Figure 6-10.

Figure 7-3. CHG Driver Turn-Off Current Path

Figure 7-4. CHG Off, 4 FETs, 100 Ohm, No Current

#### 8 DSG Driver

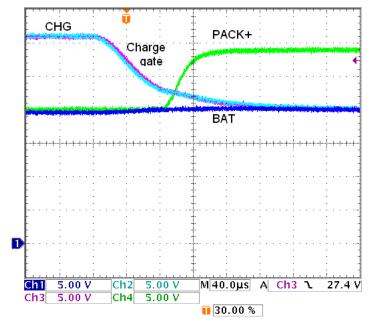

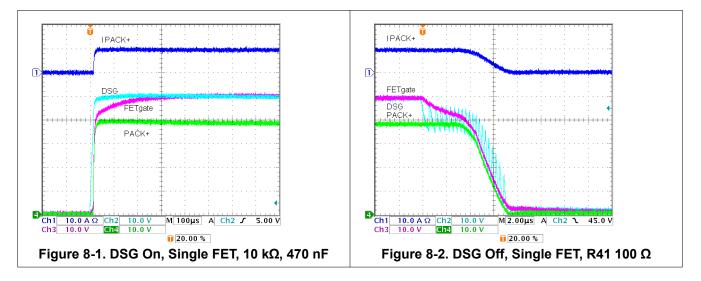

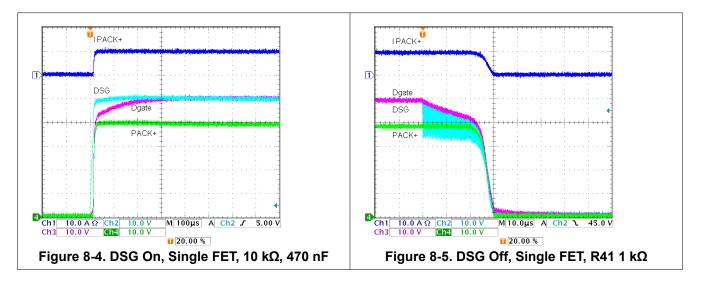

The discharge driver operates between VSS and the CP1 voltage. When the driver turns on, DSG rises toward the CP1 voltage as current flows through R45 and R40 of Figure 5-1. R45 and R40 provide a 10-k $\Omega$  turn-on resistance. An example of a single FET turn on is shown in Figure 8-1. As the FET turns on PACK+ rises and current flows in the discharge FET. The gate voltage will lag the DSG voltage with the filter effect of the turn on resistance and the gate capacitance.

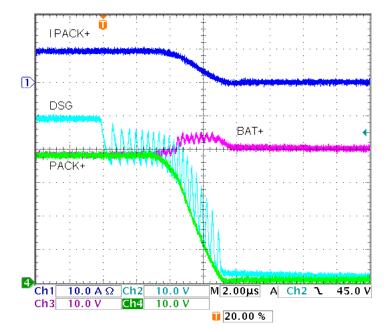

When the DSG driver is triggered to turn off, the device will initially begin discharging the DSG pin toward VSS. However, since the PACK+ terminal may not fall to a voltage near VSS quickly, the DSG FET gate should not be driven significantly below PACK+, otherwise the DSG FET may be damaged due to excessive negative gate-source voltage or the DSG pin attempts to discharge PACK+ through the gate-source resistor or Zener diode. Thus, the device monitors the voltage on the LD pin (which is connected to PACK+ through an external series resistor) and will stop the discharge when the DSG pin voltage drops below the LD pin voltage. When the discharge has stopped, the pin voltage may relax back above the LD pin voltage, at which point the device will again discharge the DSG pin toward VSS, until the DSG gate voltage again falls below the LD pin. This pulsing continues for approximately 200 µs, after which the driver remains in a high impedance state if below the voltage of the LD pin plus approximately 500 mV. The external resistor between the DSG gate and source then discharges the remaining voltage so the FET remains off.

An example turn off is shown in Figure 8-2. DSG pulling low draws current from the gate of the FET through the Schottky diode D7 and R41. Additional current will flow through R40 and R45. Current into the DSG pin is sent to the VSS pin, not out the LD pin. Figure 8-1 and Figure 8-2 show the single FET's gate voltage rather than the common gate net voltage since there is only 1 FET.

Inspecting the battery voltage in Figure 8-3 the pulsing acts to avoid a rapid turn off with and the resulting large inductive spike. The designer must select a turn off speed suitable for the battery inductance. With this test current the battery voltage has risen 4 V, a larger R41 value will be used for low FET count comparisons.

Figure 8-3. Battery Transient With Single FET, R41 100  $\boldsymbol{\Omega}$

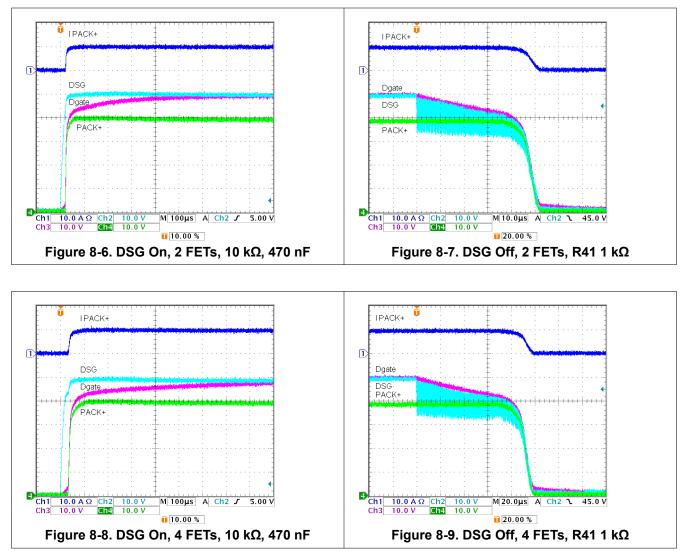

Figure 8-4 to Figure 8-9 show example turn on and off with the reverse charge circuit, R41 as 1 k $\Omega$ , and 1 to 4 FETs. Turn on for a single FET is similar to the case with R41 100  $\Omega$  since the Schottky diode blocks current in R41 during turn on. In Figure 8-4 the common gate net is monitored rather than the single FET gate.

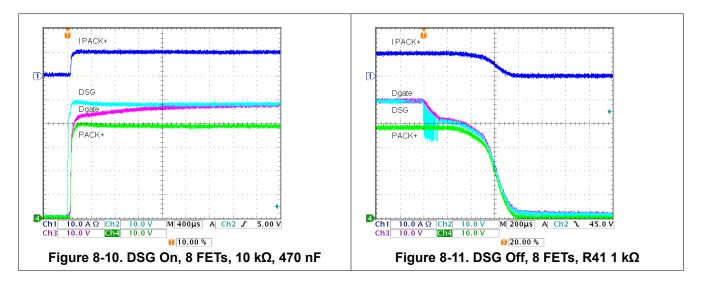

With 8 FETs gate capacitance has increased the separation of the DSG and Dgate net at turn on and slowed the rise as shown in Figure 8-10. In Figure 8-11 the FETs do not turn off during the pulsing time of the DSG output but later from the weak pull down of DSG. The time to turn off is extended significantly and turn off is slow. This condition should be avoided in a design.

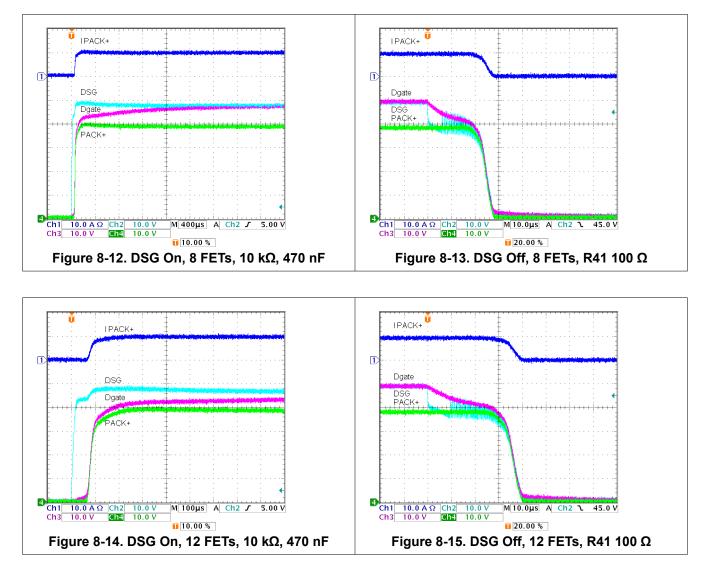

A smaller pull down resistor for DSG which may have been inappropriate for a smaller number of FETs will increase the turn off time for the larger FET count. In Figure 8-12 and Figure 8-13 R41 is changed back to 100  $\Omega$ . Turn on is not changed but turn off is faster. Switching 12 FETs with this configuration is shown in Figure 8-14 and Figure 8-15.

With a given gate pull down resistance, adding FETs increases the capacitance and slows the transition of the DSG pin initial drop due to its internal resistance and the transition of the gate. The effect can be hard to identify with the transition of PACK+. The followng table shows typical values collected for various FET quantities with PACK+ connected to BAT+ using R41 100  $\Omega$ . Fall times are 90% to 10%, an example FET gate was measured rather than the Dgate net.

| Number of FETs | Sum of Ciss, nF | DSG Initial Fall Time, us | Example FET Gate Fall Time,<br>us |  |  |

|----------------|-----------------|---------------------------|-----------------------------------|--|--|

| 1              | 9.25            | 0.50                      | 6.4                               |  |  |

| 2              | 18.5            | 1.0                       | 9.6                               |  |  |

| 4              | 37              | 1.4                       | 16                                |  |  |

| 6              | 55.5            | 2.3                       | 21                                |  |  |

| 8              | 74              | 5.0                       | 27                                |  |  |

| 10             | 92.5            | 6.7                       | 33                                |  |  |

#### Table 8-1. Fall Times With Various FETs, 100 $\boldsymbol{\Omega}$

| Table 8-1. Fall Times With Various FETs, 100 $\Omega$ (continued) |     |                           |                                   |  |

|-------------------------------------------------------------------|-----|---------------------------|-----------------------------------|--|

| Number of FETs Sum of Ciss, nF                                    |     | DSG Initial Fall Time, us | Example FET Gate Fall Time,<br>us |  |

| 12                                                                | 111 | 7.2                       | 39                                |  |

. . . . . . . . . . . . . . . . . . .....

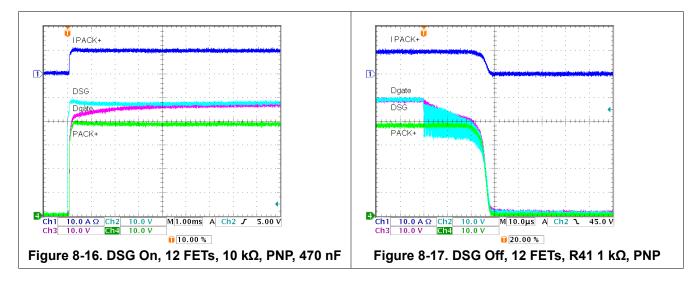

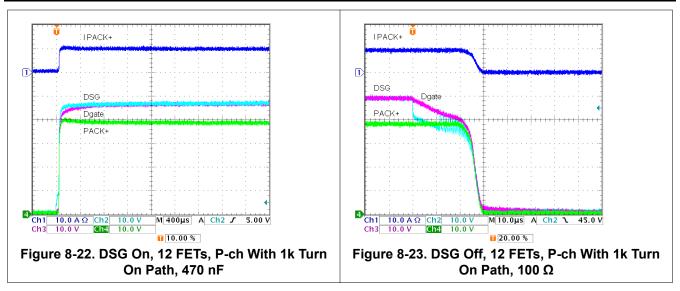

In the above images, the DSG pin discharges the gate capacitance directly. A PNP transistor can be used to discharge the gate capacitance with control by the DSG pin as shown in Figure 5-2. Figure 8-16 and Figure 8-17 show the turn on and turn off with 12 discharge FETs and this circuit.

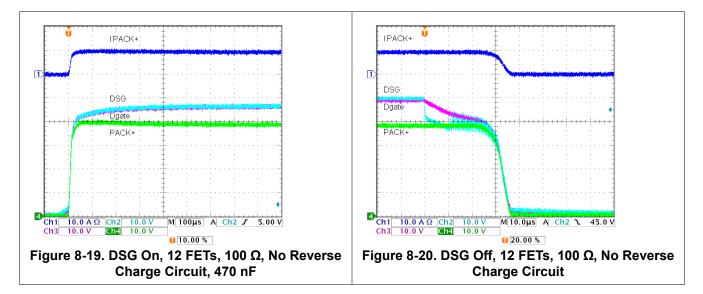

The reader has observed that the turn on takes increasing time as the FET count increases. This is because of the 10-k $\Omega$  resistance (R40, R45) to keep the power in the resistors at a reasonable level during the reverse charge condition. If the reverse charge circuit is not needed, DSG can be connected to the common gate point with a single resistor replacing the connection network of Figure 5-1. The Schottky diodes, R40 and R45, the reverse charge clamp transistor and related components are omitted. See Figure 8-18. Switching is shown in Figure 8-19 and Figure 8-20.

Figure 8-18. DSG Drive Without Reverse Charge Protection Circuit

If the reverse charge circuit is needed, a P-ch FET may be inserted in place of R45 with the gate referenced to the LD pin as shown in Figure 8-21. The FET will be on when DSG rises, as DSG falls to LD the FET will be on and R40 will help drain the discharge FET gate capacitance, but will turn off allowing the gate pull down resistor R41 to complete turn off. In Figure 8-22 and Figure 8-23 R40 is 1 k $\Omega$ . With DSG off the P-ch FET Q32 is off and a reverse charge voltage will drop the Dgate net without current flow in R40. At turn on R40 will act with the gate capacitance and can be adjusted for Dgate to better approach the DSG pin. Remember that the turn on current comes from the CP1 capacitor, the drop in the DSG will depend on the internal resistance and

the charge transfer from the CP1 capacitor to the FET gates. This example uses the 470 nF CP1 capacitor and the low voltage after turn on can be observed. At turn off R40 is in parallel with the R41 and Schottky path until voltage is low enough for the P-ch FET to turn off. The user should note that the BQ769x2 does not limit the voltage between DSG and LD at turn on. The intent of the P-ch circuit is to allow using a small R40 so that the FET gates, PACK+ and LD come up quickly with DSG. If a large R40 is used or the discharge FET turn on is slow, a zener on the source-gate connection and large resistor from the Q32 gate to LD connection are desired to protect the Q32 gate.

Figure 8-21. P-ch DSG Turn On Circuit