# Compensating the Current-Mode-Controlled Boost Converter

Jeff Falin, Tahar Allag, Ben Hopf

PMP - DCDC Low-Power Converters

#### ABSTRACT

This application report summarizes one method for compensating a current-mode-controlled boost. A detailed description of both the power stage and the feedback network is provided. The design procedures are explained step by step. A design example using TPS61175 is provided. Similar design steps are used for the TPS61199 as well.

#### Contents

| 1      | Simplif | ied Small Signal Model     | 2 |

|--------|---------|----------------------------|---|

|        |         | Steps                      |   |

|        | -       | Example using the TPS61175 |   |

| Append | dix A   | Additional Data            | 9 |

|        |         |                            |   |

#### List of Figures

| 1 | Simplified Diagram of a Current-Mode Boost Converter with $g_M$ Amplifier                                         | 2 |

|---|-------------------------------------------------------------------------------------------------------------------|---|

| 2 | TPS61175 Design Example Schematic                                                                                 | 5 |

| 3 | Simulated Bode Plot of Power Stage Gain and Phase                                                                 | 6 |

| 4 | Simulated Bode Plot of the Type II Compensation (Including Feedback Network) for a g <sub>m</sub> Error Amplifier | 7 |

| 5 | Modeled Bode Plot of the Total Open Loop                                                                          | 7 |

| 6 | Loop Gain and Phase                                                                                               | 8 |

| 7 | Full Model Diagram                                                                                                | 9 |

# 1 Simplified Small Signal Model

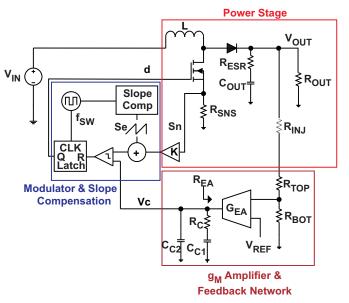

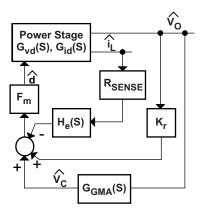

Figure 1 shows a simplified block diagram of a current-mode boost converter with a transconductance amplifier providing the feedback.

Figure 1. Simplified Diagram of a Current-Mode Boost Converter with g<sub>M</sub> Amplifier

With inductor current information fed back by  $R_{SNS}$  (and possibly gained by factor K) as well as output voltage feedback, this boost converter's inductor and switches effectively combine into a current source driving an RC load. By removing the inductor, the small-signal, control-loop model of the power stage reduces from a two-pole system, created by L and  $C_{OUT}$ , to a single-pole ( $f_P$ ) system, created by  $R_{OUT}$  and  $C_{OUT}$ . The single-pole system is easily used with Type-II compensation.

The single-pole system only holds true if the slope of the external compensation signal, Se, is not too large in relation to the ramp sensed across  $R_{SENSE}$ , Sn or the natural slope. If the Se slope dominates Sn, for example, when the inductance is oversized in order to give ripple current much smaller than the recommended 0.2-0.4 times the average input current, then the converter begins behaving more like a voltage-mode converter and the full model, included in Appendix A, must be used.

Regardless of which model is used, the right-half-plane zero ( $f_{RHPZ}$ ), created by lack of continuous current flow to the output, is still present.

Including the slope compensation, the new power stage small-signal model is presented mathematically as follows:

$$G_{PS}(S) = \frac{R_{OUT} * (1-D)}{2 * R_{SENSE}} * \frac{(1 + \frac{S}{2\pi * f_{ESR}})(1 - \frac{S}{2\pi * f_{RHPZ}})}{1 + \frac{S^2}{2\pi * f_P}} * He(s)$$

Where D is the duty cycle and the single pole is:

$$f_P = \frac{2}{2\pi * R_{OUT} * C_{out}} \tag{2}$$

The zero created by the ESR of the output capacitor is:

$$f_{ESR} = \frac{1}{2\pi * R_{ESR} * C_{out}}$$

(3)

Compensating the Current-Mode-Controlled Boost Converter

(1)

For a boost converter having multiple, identical output capacitors in parallel, simply combine the capacitors and ESR in parallel and use the result in Equation 2 and Equation 3. For boost converters with ceramic capacitor(s) in parallel with a much larger, high-ESR capacitor, use the total capacitance in parallel for  $C_{OUT}$  in Equation 2 but only use the high-ESR capacitor's capacitance and ESR for Equation 3.

The right-hand plane zero is:

$$f_{RHPZ} = \frac{R_{out}}{2\pi * L} * \left(\frac{V_{IN}}{V_{out}}\right)^2 \tag{4}$$

He(s) models the inductor current sampling effect as well as the slope compensation effect on the small-signal response.

$$He(s) = \frac{1}{1 + \frac{s*[(1 + \frac{Se}{Sn})*(1 - D) - 0.5]}{f_{SW}} + \frac{s^2}{(\pi * f_{SW})^2}}$$

(5)

The equation for Se is unique to each IC and is found in the IC's datasheet. Equation 6 gives the typical equation for Sn regarding a peak current mode converter.

$$S_n = \frac{V_{IN}}{L} * R_{SNS} \tag{6}$$

The natural slope may change for other types of current mode converters.

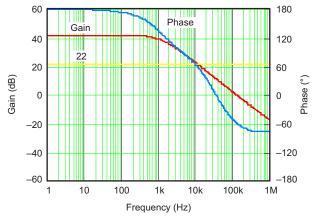

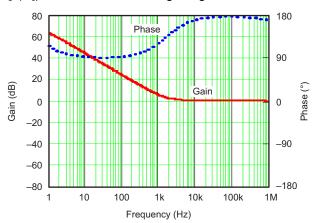

Figure 3 in the design example section shows a bode plot of a typical CCM boost converter power stage, assuming the ESR pole is at a very high frequency.

Equation 7 shows the equation for feedback resistor network and the error amplifier.

$$H_{EA} = G_{EA} * R_{EA} * \frac{R_{BOT}}{R_{BOT} + R_{TOP}} * \frac{1 + \frac{S}{2\pi * f_z}}{(1 + \frac{S}{2\pi * f_{P1}}) * (1 + \frac{S}{2\pi * f_{P2}})}$$

(7)

Where  $G_{\mbox{\tiny EA}}$  and  $R_{\mbox{\tiny EA}}$  are the error amplifier's transconductance and output resistance.

$$f_{P1} = \frac{1}{2\pi * R_{EA} * C_{C1}}$$

(8)

$$f_{P2} = \frac{1}{2\pi * R_C * C_{C2}}$$

(Optional) (9)

C<sub>C2</sub> is optional and is modeled as 10-pF stray capacitance.

and

$$f_Z = \frac{1}{2\pi * R_C * C_{C1}}$$

(10)

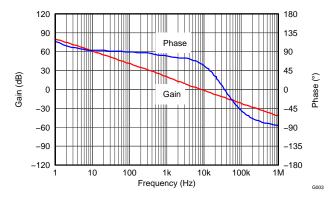

Figure 4 in the design example shows a typical shape of a bode plot for transfer function  $H_{EA}(s)$  with Type-II compensation components.

#### 2 Design Steps

The steps to compensate the loop are as follows:

1. Choose the desired loop crossover frequency, fc

The higher in frequency that the loop gain stays above zero before crossing over, the faster the loop response is and, therefore, the lower the output voltage droops during a step load. It is generally recommended that the loop-gain crossover point is no higher than the lower of either 1/5 of the switching frequency,  $f_{SW}$ , or 1/3 of the RHPZ frequency,  $f_{RHPZ}$ . It is also recommended to cross over at a frequency where the power stage gain is decreasing at approximately a -20 dB/decade slope (after the dominant pole and well before the effects of an RHPZ).

The size of the output capacitor plays a significant role in how wide the loop bandwidth is. Once the minimum capacitance is met, meeting the output ripple specification, Equation 11 is used to estimate the capacitance needed to meet the application's load transient requirement for the maximum voltage dip ( $V_{TRAN}$ ) after a given load step ( $\Delta I_{TRAN}$ ).

$$C_{out} = \frac{\Delta I_{TRAN}}{2\pi * f_C * V_{TRAN}}$$

(11)

2. Properly size the compensation resistor, Rc

By placing  $f_z$  below  $f_c$ , for frequencies above  $f_c$ , Rc|  $|R_{REA} \sim = R_c$  and so  $R_c \times G_{EA}$  sets the compensation gain. Setting the compensation gain,  $K_{COMP-dB}$ , at  $f_c$ , results in the total loop gain,  $T(s) = G_{PS}(s) \times H_{EA}(s) \times He(s)$  being zero at  $f_c$ . Therefore, to approximate a single-pole roll-off up to  $f_{P2}$ , rearrange Equation 12 to solve for  $R_c$  so that the compensation gain,  $K_{COMP-dB}$ , at  $f_c$  is the negative of the gain,  $K_{PW-dB}$ , read at frequency  $f_c$  for the power stage bode plot or more simply

$$K_{COMP-dB}(f_c) = 20 * \log(G_{EA} * R_c * \frac{R_{BOT}}{R_{BOT} + R_{TOP}}) = -K_{PW-dB}(f_c)$$

(12)

3. Properly size the compensation capacitor, C<sub>C1</sub>

Compensation capacitor  $C_{C1}$  is sized so that  $f_Z \approx f_C/10$  and optional  $f_{P2} > f_C \times 10$

4. Optionally, size the compensation capacitor,  $C_{C2}$ .

Equation 9 is for a pole produced by RC and  $C_{C2}$ . This pole may be necessary to ensure that the gain continues to roll off after the crossover frequency. Alternatively, for boost circuits with high ESR output capacitors, and therefore a low-frequency ESR zero per Equation 3, this pole is useful for canceling unhelpful effects of the ESR zero.

The preceding steps lead to a loop with a phase margin near 45 degrees. Lowering  $R_c$ , while keeping fz  $\approx f_{BW}/10$ , increases the phase margin without significantly changing the gain and therefore increases the time it takes for the output voltage to settle following a step load.

Copyright © 2012, Texas Instruments Incorporated

RUMENTS

**FEXAS**

## 3 Design Example using the TPS61175

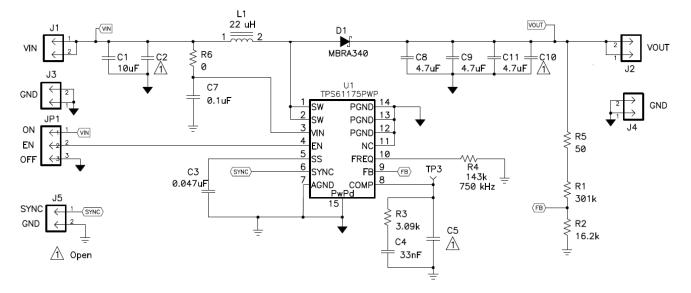

Figure 2 shows the EVM schematic and Table 1 gives the specifications for the design example. In order to meet the transient requirement, the output capacitance value may need to changed.

Figure 2. TPS61175 Design Example Schematic

|                            | PARAMETER                 | CONDITIONS | MIN | NOM  | MAX | UNIT |  |

|----------------------------|---------------------------|------------|-----|------|-----|------|--|

| INPUT CHARACTERISTICS      |                           |            |     |      |     |      |  |

| V <sub>IN</sub>            | Input Voltage             |            |     | 12   |     | V    |  |

| f <sub>sw</sub>            | Switching Frequency       |            |     | 750  |     | kHz  |  |

| OUTPUT CHARACTERISTICS     |                           |            |     |      |     |      |  |

| Vo                         | Output Voltage            |            | 23  | 24   | 25  | V    |  |

| I <sub>o</sub>             | Output Current            |            | 1   |      | 1.2 | А    |  |

| TRANSIENT RESPONSE         |                           |            |     |      |     |      |  |

| $\Delta I_{\text{tran}}$   | Load Step                 |            |     | 0.35 |     | А    |  |

| $\Delta_{\rm IO}/\Delta T$ | Load slew rate            |            |     | 9    |     | A/µs |  |

| $\Delta V_{\text{tran}}$   | V <sub>o</sub> undershoot |            |     | 500  |     | mV   |  |

| t <sub>s</sub>             | Settling time             |            |     | 300  |     | μs   |  |

| Table 1. TPS61175EVM-326 Performance S | Specification Summary for $V_{IN} = 12.0 V$ |

|----------------------------------------|---------------------------------------------|

|----------------------------------------|---------------------------------------------|

Equation 13 and Equation 14 give Sn and Se for the TPS61175.

$$S_{n} = \frac{V_{IN}}{L} * R_{SNS} = \frac{12V}{22\mu H} * 40m\Omega$$

$$S_{e} = \frac{\frac{0.32V}{R_{4}}}{16*(1-D)*6pF} + \frac{0.5uA}{6pF}$$

(13)

(13)

(13)

Where  $R_4$  is the frequency setting resistor.

1. Choose the desired loop crossover frequency, fc.

One fifth of the switching frequency is

Texas Instruments

www.ti.com

Design Example using the TPS61175

$$\frac{f_{SW}}{5} = \frac{750kHz}{5} = 150kHz \tag{15}$$

$f_{\text{RHPZ}}$  is calculated using Equation 4

Where:

$$R_{OUT} = \frac{V_{OUT}}{I_{OUT}} = \frac{24V}{1.2A} = 20\Omega$$

(16)

From Equation 4

$$f_{RHPZ} = \frac{20}{2\pi * 22uH} * (\frac{12V}{24V})^2 = 36.2kHz$$

(17)

one-third of f<sub>RHPZ</sub> is

$$\frac{f_{RHPZ}}{3} = \frac{36.2kHz}{3} = 12.1kHz \tag{18}$$

thus, try  $f_c = 10$  kHz.

2. Find the output cap value using Equation 11

$$C_{out} = \frac{\Delta I_{TRAN}}{2\pi * f_C * V_{TRAN}} = \frac{350mA}{2\pi * 10kHz * 500mV} = 11.14\mu F$$

(19)

Three 4.7  $\mu$ F capacitors in parallel yield a total of 14.7  $\mu$ F for the output capacitance (C8, C9, and C11 in Figure 2)

3. Properly size the compensation resistor, R<sub>c</sub> (R3 in Figure 2). Using MathCAD, plot the power stage,  $G_{PS}(s)$ , with  $R_{SENSE} = 40 \text{ m}\Omega$  (given in the datasheet)

from Equation 2

6

$$f_P = \frac{2}{2\pi * R_{OUT} * C_{out}} = \frac{2}{2\pi * 20\Omega * 3 * 4.7 uF} = 1.1 kHz$$

(20)

From Equation 4,  $f_{RHPZ}$  is 36.2 kHz. Neglecting the ESR zero produced by the ceramic output capacitors gives the plot found in Figure 3.

Copyright © 2012, Texas Instruments Incorporated

The crossover frequency,  $f_c$ , was chosen as 10 kHz and from Figure 3,  $K_{PW}$  (10 kHz) = 22 dB. With  $R_{TOP}$  = 301 k $\Omega$ ,  $R_{BOT}$  = 16.2 k $\Omega$  (R1 and R2 respectively in Figure 2), and  $G_{EA(TYP)}$  = 340 µmho, solving Equation 12 for  $R_c$  gives:

$$K_{COMP-dB}(f_c) = 20 * \log(G_{EA} * R_c * \frac{R_{BOT}}{R_{BOT} + R_{TOP}}) = -K_{PW-dB}(f_c) \Longrightarrow$$

$$R_{C} = \frac{10^{\frac{K_{COMP-dB(fc)}}{20dB}}}{G_{EA} * \frac{R_{BOT}}{R_{BOT} + R_{TOP}}} = \frac{10^{\frac{-22}{20}}}{340 umho * \frac{16.2k\Omega}{16.2k\Omega + 301k\Omega}} = 4.57k\Omega$$

(22)

4. Properly size the compensation capacitor, C<sub>C1</sub> (C4 in Figure 2).

Solving Equation 10 for

$$C_{C1}$$

and setting  $f_z = f_c/10 = 1$  kHz gives

$$C_{C1} = \frac{1}{2\pi * R_C * f_z} = \frac{1}{2\pi * 4.57k\Omega * 1kHz} = 34.82nF \Longrightarrow 33nF$$

(23)

5. Optionally, size the compensation capacitor,  $C_{C2}$  (C5 in Figure 2)

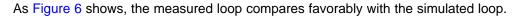

A stray capacitance of 10 pF is assumed for C5. Figure 4 displays the plot for the Type II compensated amplifier and Figure 5 shows T(s) =  $G_{PS}(s) \times H_{EA}(s) \times He(s)$  with  $R_c$  ( $R_3$ ) reduced to 3.09 k $\Omega$ , getting closer to the desired 60 degree phase margin.

Figure 4. Simulated Bode Plot of the Type II Compensation (Including Feedback Network) for a  $g_m$  Error Amplifier

Figure 5. Modeled Bode Plot of the Total Open Loop

## Design Example using the TPS61175

www.ti.com

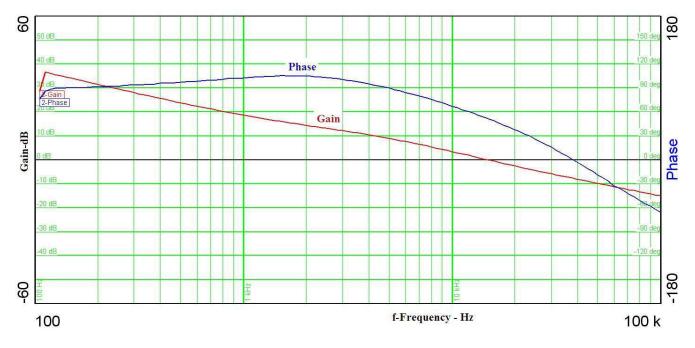

Figure 6. Loop Gain and Phase

# Appendix A Additional Data

Figure 7. Full Model Diagram

$$G_{id}(s) = \frac{\frac{2V_0^3}{V_{IN}^2} (1 + \frac{R_0C_0}{2}s)}{1 + \frac{V_0^2L}{V_{IN}^2R_{OUT}}s + \frac{V_0^2LC_0}{V_{IN}^2}s^2}$$

(24)

Where:

$$G_{PS}(s) = \frac{V_{o}}{V_{c}} = \frac{F_{m}G_{vd}(s)}{1 + F_{m}R_{SENSE}H_{e}(s)G_{id}(s) - F_{m}K_{r}G_{vd}(s)}$$

(25)

$$F_{m} = \frac{1}{(S_{e} + S_{n})T_{s}}$$

(26)

$$G_{vd}(s) = \frac{\frac{V_{O}}{V_{IN}} (1 - \frac{V_{O}L}{V_{IN}^{2}R_{O}}s)(1 + R_{ESR}C_{O}s)}{1 + \frac{V_{O}^{2}L}{V_{IN}^{2}R_{O}}s + \frac{V_{O}^{2}LC_{O}}{V_{IN}^{2}}s^{2}}$$

$$He(s) = 1 - \frac{T_{S}}{2}s + \frac{T_{S}}{\pi^{2}}s^{2}$$

(27)

A.1 References

He, Dake, and R. M. Nelms, "Peak Current-Mode for a Boost Converter Using an 8-bit Microcontroller," IEEE 34th Annual Power Electronics Specialist Conference 2, June 2003 Record, pp. 938–943.

Ridley, R. D., "Current-Mode Control Modeling," Switching Power Magazine, 2006, pp. 1–12.

(28)

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46C and to discontinue any product or service per JESD48B. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components which meet ISO/TS16949 requirements, mainly for automotive use. Components which have not been so designated are neither designed nor intended for automotive use; and TI will not be responsible for any failure of such components to meet such requirements.

| Products               |                                 | Applications                  |                                   |

|------------------------|---------------------------------|-------------------------------|-----------------------------------|

| Audio                  | www.ti.com/audio                | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers             | amplifier.ti.com                | Communications and Telecom    | www.ti.com/communications         |

| Data Converters        | dataconverter.ti.com            | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products          | www.dlp.com                     | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                    | dsp.ti.com                      | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers      | www.ti.com/clocks               | Industrial                    | www.ti.com/industrial             |

| Interface              | interface.ti.com                | Medical                       | www.ti.com/medical                |

| Logic                  | logic.ti.com                    | Security                      | www.ti.com/security               |

| Power Mgmt             | power.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers       | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

| RFID                   | www.ti-rfid.com                 |                               |                                   |

| OMAP Mobile Processors | www.ti.com/omap                 | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity  | www.ti.com/wirelessconnectivity |                               |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2012, Texas Instruments Incorporated