## Power Supply Design for NXP i.MX 7 Using the TPS65023

Wenchau Albert Lo

#### ABSTRACT

This document details the design considerations of a power management unit solution for the NXP i.MX 7 processor using the TPS65023 power management IC (PMIC).

The TPS65023 has an input range from 2.5 to 6 V. The device has three low-dropout (LDO) regulators and three step-down converters that provide the 1-, 1.35-,1.8-, 3-, and 3.3-V rail signals in the appropriate power-on and power-off sequence that is required by the i.MX 7. For an i.MX 6 power solution please refer to the VVDN design on RadiumBoards website.

| 1  | Introduction            | 2  |

|----|-------------------------|----|

| 2  | Power Requirements      | 2  |

| 3  | Schematic               | 5  |

| 4  | Bill of Materials (BOM) | 7  |

| 5  | Waveforms               | 8  |

|    | Transient Response      |    |

|    | Efficiency Curve        |    |

|    | Layout                  |    |

| 9  | Conclusion              | 14 |

| 10 | References              | 14 |

#### List of Figures

| 1  | TPS65023 Power Solution Block Diagram                                                                    | 2  |

|----|----------------------------------------------------------------------------------------------------------|----|

| 2  | External Resistor Divider                                                                                | 5  |

| 3  | TPS65023 Power and Sequencing Circuit for i.MX 7 Powering Requirements                                   | 6  |

| 4  | Power-On Sequence for DCDC1 and DCDC2                                                                    | 8  |

| 5  | Power-On Sequence for DCDC2, LDO Regulators, and DCDC3                                                   | 9  |

| 6  | Power-Off Sequence for DCDC 1, DCDC2, and DCDC3. DCDC3 has Output Load of 300 $\Omega$                   | 9  |

| 7  | Power-Off Sequence for DCDC2, LDO Regulators, and DCDC3. DCDC3 and LDOs Have Output Load of 300 $\Omega$ | 10 |

| 8  | Transient Response for DCDC1                                                                             | 11 |

| 9  | Transient Response for DCDC2                                                                             | 11 |

| 10 | Transient Response for DCDC3                                                                             | 12 |

| 11 | DCDC1 Efficiency                                                                                         | 12 |

| 12 | DCDC2 Efficiency                                                                                         | 13 |

| 13 | DCDC3 Efficiency                                                                                         |    |

| 14 | Layout Example of a DC-DC Converter                                                                      | 14 |

#### List of Tables

| 1 | i.MX 7 Power Requirements          | 3  |

|---|------------------------------------|----|

| 2 | Bill of Materials                  | 7  |

| 3 | Transient Requirements and Results | 10 |

#### Trademarks

All trademarks are the property of their respective owners.

#### 1 Introduction

This reference design applies to the NXP i.MX 7 Solo and Dual family of applications processors. This report provides all the required external components necessary to achieve the required output and sequence to power on and off the i.MX 7 processor. This reference design provides a solution for Vin being 5 V, DDR3L requiring 1.35 V, and NVCC power domain requiring 1.8 V. However if DDR3, LPDDR2, or LPDDR3 is desired, the necessary output can be achieved through a resistor divider, which is detailed in this document.

### 2 **Power Requirements**

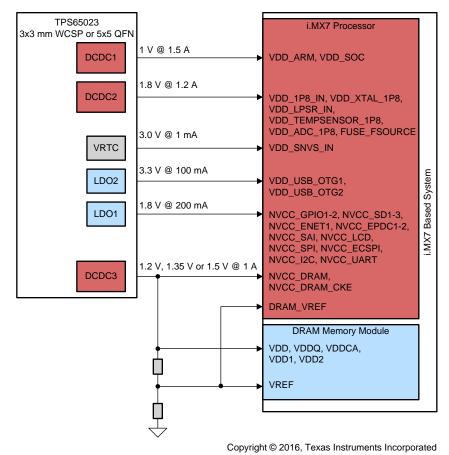

Figure 1 shows a block diagram of the TPS65023 and i.MX 7 processor interfaces. A circuit schematic detailing the TPS65023 and the sequencing circuit is shown in Figure 3.

Figure 1. TPS65023 Power Solution Block Diagram

The i.MX 7 power requirements are listed on Table 1 provided by the i.MX 7 Dual Family of Applications Processors Data Sheet and the i.MX 7 Solo Family of Applications Processors Data Sheet.

|                      | -                          | FPS65023        |              | i.MX 7                   |                                                                                                                                     |                                                 |                        |

|----------------------|----------------------------|-----------------|--------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------------------|

| POWER-UP<br>SEQUENCE | POWER-<br>DOWN<br>SEQUENCE | POWER<br>SUPPLY | lout<br>[mA] | OUTPUT<br>VOLTAGE<br>[V] | POWER SUPPLY                                                                                                                        | NOMINAL<br>RATING [V]                           | MAX<br>CURRENT<br>[mA] |

| 2                    | 2                          | DCDC1           | 1500         | 1.0                      | VDD_ARM, VDD_SOC                                                                                                                    | Minimum: 0.95<br>Typ: 1<br>Maximum:<br>1.155    | 1500                   |

| 2                    | 2                          | DCDC2           | 1200         | 1.8                      | VDD_1P8_IN,<br>VDD_XTAL_1P8,<br>VDD_LPSR_IN,<br>VDD_TEMPSENSOR_1P8,<br>VDD_ADC_1P8,<br>FUSE_FSOURCE                                 | 1.8 V ± 5%                                      | 600                    |

| 3                    | 1                          | DCDC3           | 1000         | 1.35                     | NVCC_DRAM,<br>NVCC_DRAM_CKE                                                                                                         | Minimum:<br>1.283<br>Typ: 1.35<br>Maximum: 1.45 | 1000                   |

| 3                    | 1                          | LDO1            | 200          | 1.8                      | NVCC_GPIO1-2,<br>NVCC_SD1-3,<br>NVCC_ENET1,<br>NVCC_EPDC1-2, NVCC_SAI,<br>NVCC_LCD, NVCC_SPI,<br>NVCC_LCSPI, NVCC_I2C,<br>NVCC_UART | 1.8 V ± 8.33%                                   | 100 <sup>(1)</sup>     |

| 3                    | 1                          | LDO2            | 100          | 3.3                      | VDD_USB_OTG1,<br>VDD_USB_OTG2                                                                                                       | 3.3 V ± 9.09%                                   | 100                    |

| 1                    | 3                          | VRTC            | 1            | 3.0                      | VDD_SNVS_IN                                                                                                                         | 3.0 V ± 20%                                     | 1                      |

#### Table 1. i.MX 7 Power Requirements

<sup>(1)</sup> NVCC rail requirements are estimated to be well below 100 mA. LDO1 can provide up to 100 mA and is reflected in the table, which depends on the processor requirements.

The TPS65023 fulfills all the power requirements with three step-down converters and three LDO regulators. In order to meet the power sequence requirements, a simple sequencing circuit is used, which is detailed in Figure 3.

Even though all the rail requirements are met, combining VDD\_ARM and VDD\_SOC limits the processor speed to 800 MHz. This combination also limits low-power mode by maintaining VDD\_ARM on during low power mode. Because the i.MX 7Solo family runs at an 800-MHz frequency, the i.MX 7Dual family will also have to run at 800-MHz frequency with this design.

TEXAS INSTRUMENTS

Power Requirements

www.ti.com

#### 2.1 Power-On Sequence

The required power-on sequence specified by the i.MX 7 datasheet is as followed.

- 1. VDD\_SNVS\_IN supplied by VRTC

- 2. VDD\_SOC and VDD\_ARM supplied by DCDC1

- 3. NVCC\_DRAM and NVCC\_DRAM\_CKE supplied by DCDC3

The first step is turning on VDD\_SNVS\_IN with VRTC. In the TPS65023 one of the three LDO regulators is designated as VRTC with an output of 3 V. VRTC defaults to turning on when the TPS65023 powers on, which means VDD\_SNVS\_IN will always be the first rail on.

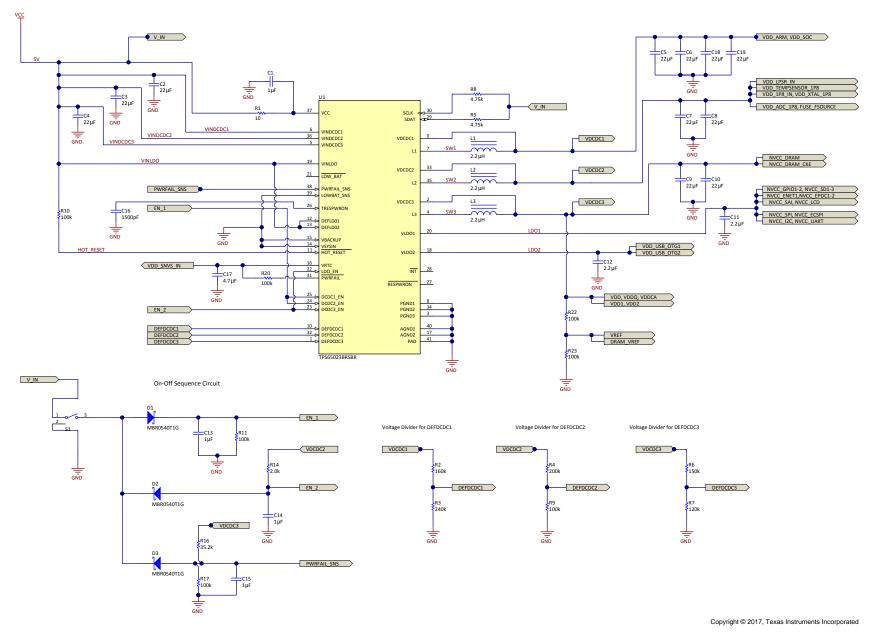

The second step comes in the sequencing circuit. A slider switch is used in the schematic; however, the switch can be replaced with an outside enable signal going HIGH. By setting the signal HIGH it will set diode D1 to be forward bias, whereas, diodes D2 and D3 are reverse bias. With diode D1 in forward bias, EN\_1 signal goes HIGH and turns on DCDC1 and DCDC2. DCDC2 turns on at this time because there are no sequence requirements necessary for what DCDC2 powers. The threshold voltage for the enable input is 1.3 V. With DCDC1 at 1 V, DCDC1 is unable to set the enable pin high, which is why DCDC2, at 1.8 V, is used to turn on the remaining enable pins.

When DCDC2 reaches 1.8 V, DCDC2 output goes through an RC (R14 and C14) delay before enabling DCDC3 and the remaining two LDO regulators. Once reaching operating level, DCDC3 goes through a resistor divider and RC delay before going to the PWRFAIL\_SNS pin, which will set the internal comparator for the PWRFAIL signal.

The power-on sequence is complete. The proper connections for the power-on sequence are detailed in the schematic shown in Figure 3.

#### 2.2 Power-Off Sequence

From the i.MX 7 datasheet, the processor must be powered off in the reverse order of the power-on sequence.

- 1. NVCC\_DRAM and NVCC\_DRAM\_CKE supplied by DCDC3

- 2. VDD\_SOC and VDD\_ARM supplied by DCDC1

- 3. VDD\_SNVS\_IN supplied by VRTC

To begin the turn off sequence, the switch is turned off or the enable signal is set to LOW making diodes D2 and D3 forward biased. PWRFAIL\_SNS becomes LOW pulling PWRFAIL LOW. EN\_2 becomes LOW and causes the output of DCDC3 and the LDOs to ramp down.

In the meantime D1 is now reverse bias, allowing for C13 to discharge into R11, which creates a delay longer than the ramp down of DCDC3 and the LDO regulators. At this point steps DCDC3 and DCDC1 are shut off in the correct order. VRTC is tied to Vin and, therefore, will power down when Vin starts ramping down. This power down sequence ensures that VRTC is the last rail on fulfilling all the requirements for the power-off sequence.

The proper connections for the power off sequence are shown in Figure 3.

## 2.3 Adjusting the Step-Down Output

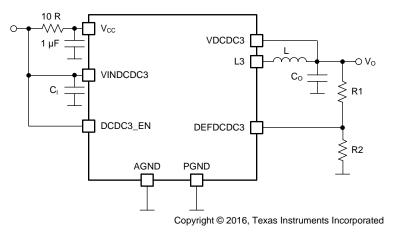

Figure 2. External Resistor Divider

The DEFDCDC1, DEFDCDC2, and DEFDCDC3 pins are used to set the output voltage for each stepdown converter. By using an external resistor divider, the output voltage can be set from 0.6-V up to the input voltage  $V_{(bat)}$ . The total resistance (R1 + R2) of the voltage divider must be kept in the 1-M $\Omega$  range to maintain a high efficiency at light loads.

$$V_{(DEFDCDCx)} = 0.6 V$$

$$V_{OUT} = V_{DEFDCDCx} \times \frac{R1 + R2}{R2}$$

$$R1 = R2 \times \left(\frac{V_{OUT}}{V_{DEFDCDCx}}\right) - R2$$

(3)

## 2.4 Adjusting the Sequencing Circuit

In the schematic shown in Figure 3, the sequence circuit is designed with a DCDC3 output of 1.35 V. If DDR3, LPDDR2, or LPDDR3 is desired over DDR3L then the resistor divider (R16 and R17) needs to be changed accordingly to provide 1 V to PWRFAIL\_SNS.

## 3 Schematic

Figure 3 shows the circuit schematic as well as detailing the external components necessary for the TPS65023 to achieve the 1-, 1.35-, and 1.8-V power rails required by the i.MX 7. The sequencing circuit is also detailed to achieve the proper power-on and power-off sequence. A slider switch is depicted in the schematic; however, any switching mechanism can be used, for example, an external enable signal.

## 4 Bill of Materials (BOM)

The BOM is displayed in Table 2.

| COUNT | REFDES                        | VALUE   | DESCRIPTION                                          | SIZE     | PART NUMBER         | MFR      |

|-------|-------------------------------|---------|------------------------------------------------------|----------|---------------------|----------|

| 4     | C1, C13-C15                   | 1 µF    | Capacitor, ceramic, 16 V,<br>X5R, 20%                | 0603     | 885012106017        | Wurth    |

| 11    | C2-C10, C18, C19              | 22 µF   | Capacitor, ceramic, 10 V,<br>X5R, 20%                | 0603     | C1608X5R1A226M080AC | TDK      |

| 2     | C11, C12                      | 2.2 µF  | Capacitor, ceramic, 10 V,<br>X5R, 20%                | 0603     | C0603C225M8PACTU    | Kemet    |

| 1     | C16                           | 1500 pF | Capacitor, ceramic, 10 V,<br>X5R, 10%                | 0201     | GRM033R61A152KA01D  | Murata   |

| 1     | C17                           | 4.7 µF  | Capacitor, ceramic,10 V,<br>X5R, 20%                 | 0402     | GRM155R61A475M      | Murata   |

| 3     | D1-D3                         |         | Diode, Schottky, 40 V,<br>0.5 A                      | SOD-123  | MBR0540T1G          | MCC Semi |

| 3     | L1-L3                         | 2.2 µH  | Inductor, shielded, ferrite, 1.72 A, 0.059 ohm, SMD  | VLCF4020 | VLCF4020T-2R2N1R7   | TDK      |

| 1     | R1                            | 10      | RES, chip, 5%, 0.063 W                               | 0402     | CRCW040210R0JNE     | Vishay   |

| 1     | R2                            | 160 K   | RES, chip, 1%, 0.063 W                               | 0402     | CRCW0402160KFKED    | Vishay   |

| 1     | R3                            | 240 K   | RES, chip, 1%, 0.063 W                               | 0402     | CRCW0402240KFKED    | Vishay   |

| 1     | R4                            | 200 K   | RES, chip, 1%, 0.063 W                               | 0402     | CRCW0402200KFKED    | Vishay   |

| 2     | R5,R8                         | 4.75 K  | RES, chip, 1%, 0.063 W                               | 0402     | CRCW04024K75FKED    | Vishay   |

| 1     | R6                            | 150 K   | RES, chip, 1%, 0.063 W                               | 0402     | CRCW0402150KFKED    | Vishay   |

| 1     | R7                            | 120 K   | RES, chip, 1%, 0.063 W                               | 0402     | CRCW0402120KFKED    | Vishay   |

| 7     | R9-R11, R17, R20, R22,<br>R23 | 100 K   | RES, chip, 1%, 0.063 W                               | 0402     | CRCW0402100KFKED    | Vishay   |

| 1     | R14                           | 2 K     | RES, chip, 5%, 0.063 W                               | 0402     | CRCW04022K00JNED    | Vishay   |

| 1     | R16                           | 35.2 K  | RES, chip, 0.1%, 0.1 W                               | 0603     | RT0603BRD0735K2L    | Yageo    |

| 1     | U1                            |         | Power Management IC<br>for Li-Ion Powered<br>Systems | RSB0040B | TPS65023BRSBR       | TI       |

#### Table 2. Bill of Materials

Waveforms

8

## 5 Waveforms

The following waveforms demonstrate the power-on and power-off sequence of the TPS65023 as required by the i.MX 7.

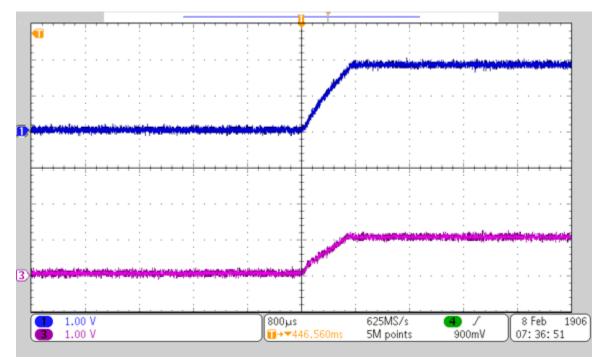

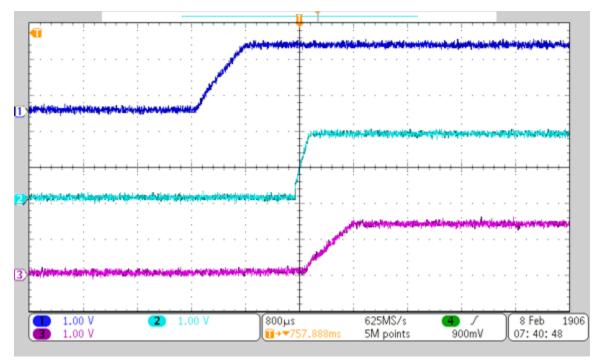

Figure 4 shows the power-on sequence where DCDC1 and DCDC2 turn on at the same time.

Figure 4. Power-On Sequence for DCDC1 and DCDC2

9

Figure 5 shows the start of the power-on sequence where DCDC2 turns on first, then the LDO regulators, and finally DCDC3. Only one of the LDO regulators is captured; however, both LDO regulators share the same enable pin.

Figure 5. Power-On Sequence for DCDC2, LDO Regulators, and DCDC3

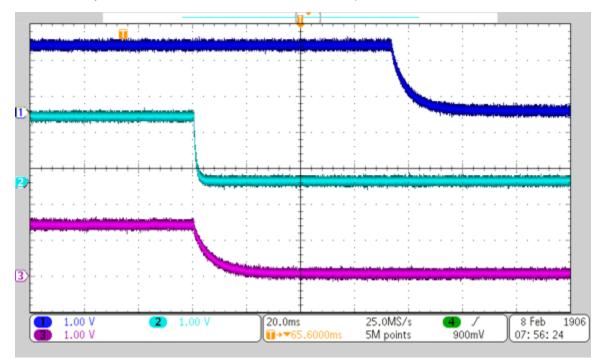

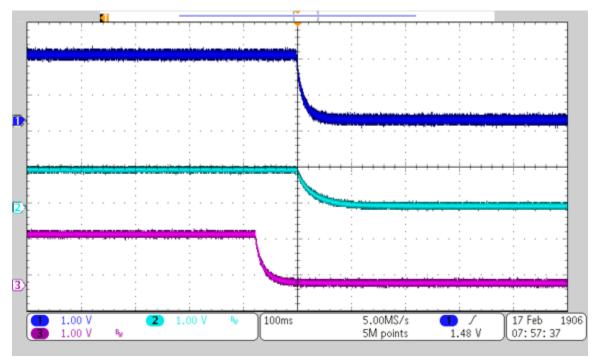

Figure 6 shows the power-off sequence for each output showing that DCDC1 and DCDC2 turn off at the same time, only after DCDC3 turns off. DCDC3 has an output load of 300  $\Omega$ .

Figure 6. Power-Off Sequence for DCDC 1, DCDC2, and DCDC3. DCDC3 has Output Load of 300  $\Omega$

Transient Response

www.ti.com

Figure 7 shows the power-off sequence where DCDC3 and the LDO registers turn off at the same time and then DCDC2 turns off. DCDC3 and LDO have an output load of 300  $\Omega$ .

# Figure 7. Power-Off Sequence for DCDC2, LDO Regulators, and DCDC3. DCDC3 and LDOs Have Output Load of 300 $\Omega$

## 6 Transient Response

Table 3 provides the transient requirements and results for each step down. Transient requirements are provided by the i.MX 7 Dual Family of Applications Processors Data Sheet and the i.MX 7 Solo Family of Applications Processors Data Sheet.

| DCDC1 TYP. VOLTAGE: 1.0-V                  |            |               |                    |  |  |  |

|--------------------------------------------|------------|---------------|--------------------|--|--|--|

| DCDC1 (mV) DCDC1 RESULTS i.MX7 REQUIRE     |            |               |                    |  |  |  |

| Minimum                                    | 50         | 5%            | 5%                 |  |  |  |

| Maximum                                    | 54.4       | 5.44%         | 15.55%             |  |  |  |

| DCDC2 TYP. VOLTAGE: 1.8-V                  |            |               |                    |  |  |  |

| DCDC2 (mV) DCDC2 RESULTS i.MX7 REQUIREMENT |            |               |                    |  |  |  |

| Minimum                                    | 52         | 2.89%         | 5%                 |  |  |  |

| Maximum 54.4                               |            | 3.02%         | 5%                 |  |  |  |

| DCDC3 TYP. VOLTAGE: 1.35-V                 |            |               |                    |  |  |  |

|                                            | DCDC3 (mV) | DCDC3 RESULTS | i.MX7 REQUIREMENTS |  |  |  |

| Minimum                                    | 62         | 4.59%         | 4.96%              |  |  |  |

| Maximum                                    | 61.2       | 4.53%         | 7.41%              |  |  |  |

#### Table 3. Transient Requirements and Results

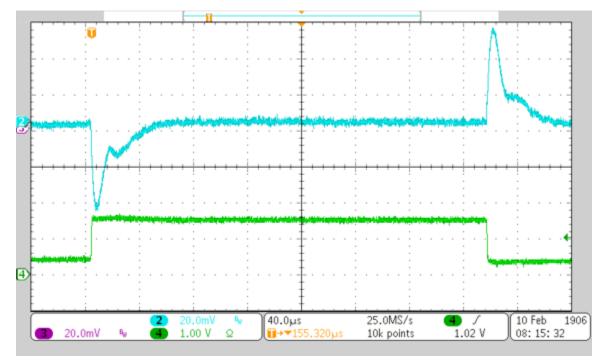

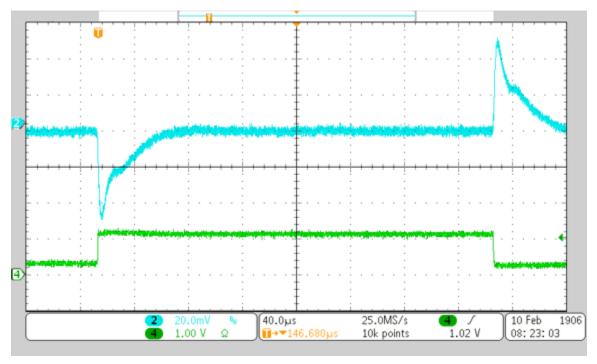

Figure 8 shows the transient response of DCDC1 with a load going from 450 to 1500 mA in 1  $\mu$ s. The transient response shows that DCDC1 fits within the necessary range of 1 V ± 5%.

Figure 8. Transient Response for DCDC1

Figure 9 shows the transient response of DCDC2 with a load going from 360 to 1200 mA in 1  $\mu$ s. The transient response shows that DCDC2 fits within the necessary range of 1.8 V ± 5%.

Figure 9. Transient Response for DCDC2

#### Efficiency Curve

www.ti.com

Figure 10 shows the transient response of DCDC3 with a load going from 300 to 1000 mA in 1  $\mu$ s. The transient response shows that DCDC3 fits within the necessary range of 1.283  $\leq$  1.35  $\leq$  1.45.

Figure 10. Transient Response for DCDC3

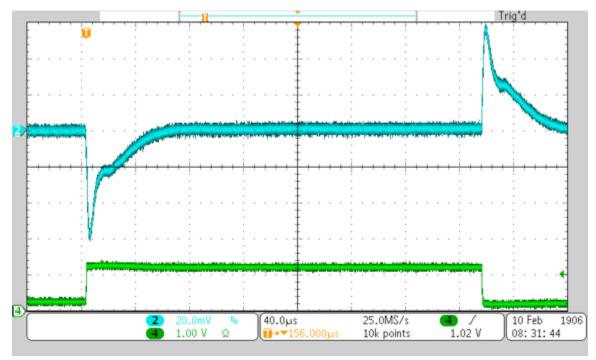

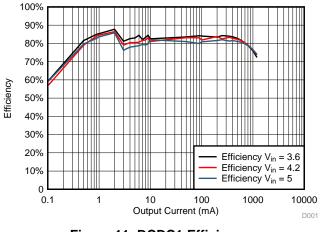

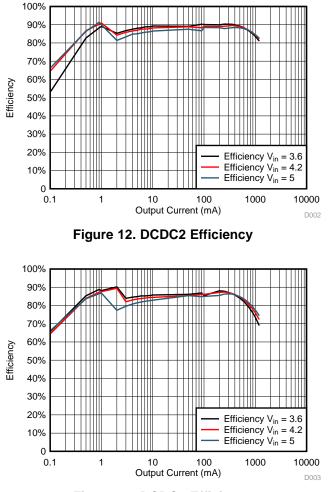

## 7 Efficiency Curve

The following efficiency curves show the efficiency for each of the converters over the possible range of output currents.

Figure 11. DCDC1 Efficiency

Figure 13. DCDC3 Efficiency

## 8 Layout

#### 8.1 Layout Guidelines

As for all switching power supplies, the layout is an important step in the design. Proper function of the device demands careful attention to PCB layout. If the layout is not carefully done, the regulators may show poor line, load regulation, or both along with stability issues and electromagnetic interference (EMI) problems. It is critical to provide a low-impedance ground path. Therefore, use wide and short traces for the main current paths. The input capacitors must be placed as close as possible to the IC pins as well as the inductor and output capacitor.

For the TPS65023x, connect the PGND pins of the device to the PowerPAD<sup>™</sup> land of the PCB, and connect the analog ground connections (AGND) to the PGND at the PowerPAD. It is essential to provide a good thermal and electrical connection of all GND pins using multiple vias to the GND-plane. Keep the common path to the AGND pins, which return the small signal components, and the high current of the output capacitors as short as possible to avoid ground noise. The VDCDCx line must be connected right to the output capacitor and routed away from noisy components and traces (for example, the L1, L2, and L3 traces).

Layout

www.ti.com

### 8.2 Layout Example

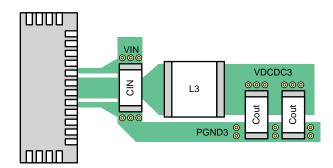

Figure 14. Layout Example of a DC-DC Converter

## 9 Conclusion

The TPS65023 provides a low-cost, comprehensive power solution for the i.MX 7 Solo and Dual family of application processors. This design demonstrates the ability to use external components to adjust the output of the TPS65023 to provide the required voltage rails for the i.MX 7. There is a schematic for a simple sequencing circuit that fits the power-on and the power-off sequence required by the i.MX 7. If DDR3, LPDDR2, or LPDDR3 is desired instead of DDR3L, the output voltage of DCDC3 can be adjusted by changing the resistor value in the resistor divider and in the sequencing circuit. All in all, the TPS65023 is a solution with the flexibility and ability to meet the various power requirements demanded by the i.MX 7.

#### 10 References

- 1. Texas Instruments, *TPS65023x Power Management IC for Li-Ion and Li-Polymer Powered Systems*, TPS65023, TPS65023B Data Sheet (SLVS670)

- 2. NXP Semiconductors, *i.MX 7Dual Family of Applications Processors Data Sheet* (IMX7DCEC), Rev. 2, 06/2016

- 3. NXP Semiconductors, *i.MX* 7Solo Family of Applications Processors Data Sheet (IMX7SCEC), Rev. 2, 06/2016

TEXAS INSTRUMENTS

www.ti.com

Page

## **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from B Revision (May 2017) to C Revision                                             | Page |

|----------------------------------------------------------------------------------------------|------|

| Changed the TPS65023 Power and Sequencing Circuit for i.MX 7 Powering Requirements schematic |      |

| Changes from A Revision (February 2017) to B Revision                                        | Page |

| Changed Freescale to NXP                                                                     | 2    |

#### Changes from Original (November 2016) to A Revision

| • | Changed caption of Figure 6 | 1  |

|---|-----------------------------|----|

| • | Changed caption of Figure 7 | 1  |

| • | Changed caption of Figure 6 | 9  |

| • | Changed caption of Figure 7 | 10 |

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated