# Charging Super Capacitor With eFuse

Rakesh Panguloori Power Switches

#### **ABSTRACT**

Backup power management solutions are typically used in end equipment, such as solid state drives (SSDs), storage systems, data concentrators, and smart meters, where an unexpected power disruption can cause malfunction or data loss. Super capacitors or large hold-up capacitors are used as storage elements to provide enough backup power to maintain data communication prior to the whole system's shutdown.

This application report discusses how an eFuse can be used as simple charger circuit for the super capacitor. This report also provides design and measurement results showing the performance benefits of using eFuse as SuperCap charger.

#### Contents 1 Introduction 2 2 3 4 Test Results 8 5 6 **List of Figures** 1 2 3 4 5 Thermal Shutdown Time Plot for TPS25940A eFuse 6 6 7 8 9 10 11 12 13 14 **List of Tables** 1 2

Introduction www.ti.com

#### **Trademarks**

All trademarks are the property of their respective owners.

### 1 Introduction

Copyright © 2017, Texas Instruments Incorporated

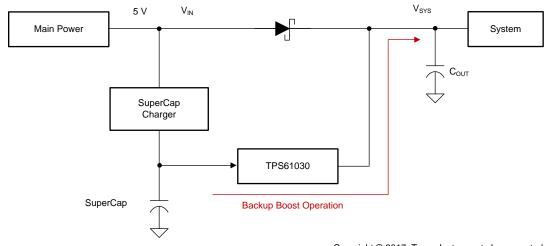

Figure 1. Simplified Block Diagram of the Backup Power System

Figure 1 shows a typical block diagram of a backup power system. The main components are:

- a super capacitor

- a charger circuit for the super capacitor

- a boost converter TPS61030

- a Schottky diode

During normal operation, the main power directly connects to the system, and the backup super capacitor charges through the SuperCap charger circuit. In case of main power loss, the system voltage  $V_{\text{SYS}}$  drops below the programmed output voltage level of boost converter. Then the boost converter immediately starts regulating the system voltage and uses the stored energy of the super capacitor for backup operation.

During backup operation, the Schottky diode prevents the current flow from  $V_{\text{SYS}}$  to  $V_{\text{IN}}$  to prevent any additional load on the backup power system. Similarly, the SuperCap charger circuit must have reverse current blocking capability to avoid draining the super capacitor. When the main power restores, it is important to limit the charging (inrush) current for the discharged super capacitor to avoid disturbance on the system voltage.

As the super capacitors are sensitive to overvoltages, protection against overvoltage is required especially when the difference between the system voltage and the voltage rating of the super capacitor is wide. In this application report, the system voltage and the maximum working voltage of the super capacitor are close, so overvoltage protection is not considered.

# 2 Discrete Implementation of Super Capacitor Charger Circuit

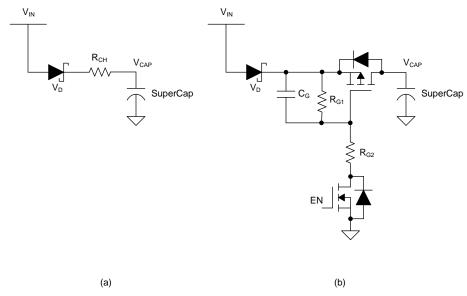

Figure 2. SuperCap Charger Circuit (a) Resistor-Diode Network (b) P-FET-based Discrete Circuit

Figure 2 (a) shows discrete charging circuit for the super capacitor. The resistor  $R_{CH}$  controls the charging current, and the Schottky diode prevents reverse current flow when the main power  $V_{IN}$  is at low voltage. Figure 3 illustrates the charging profile of a 5-F super capacitor using resistor-diode network. The current set resistor  $R_{CH}$  is chosen as 25  $\Omega$  to limit maximum charging current  $I_{CH}$  max to 200 mA as per Equation 1.

$$I_{CH\_max} = \frac{(V_{IN} - V_{D})}{R_{CH}} = \frac{(5 - 0.3)}{25} \approx 200 \text{ mA}$$

(1)

As seen in Figure 3, the charging current decreases exponentially with the increase of super capacitor voltage  $V_{CAP}$ . Though this charger circuit is simple, the circuit results in:

- · Long charging time due to exponential charging profile

- Lower storage usage as the super capacitor is charged to a voltage V<sub>IN</sub>- V<sub>D</sub>

- No controllability—the charging starts as soon as main power V<sub>IN</sub> restores. If the application demands, this circuit realization requires additional series switch for controllability.

Figure 3. Charging Profile of 5-F Super Capacitor Using Figure 2 (a)

The circuit configuration, shown in Figure 2 (b), uses a P-channel MOSFET to manage the charging current of the super capacitor. The active component P-FET provides handle to control the charge flow; however, this discrete circuit also has several challenges:

- As shown in Figure 4, the charging current increases exponentially with the increase of super capacitor voltage V<sub>CAP</sub>. The RC components around the gate of P-FET must be adjusted through several iterations to restrict the inrush current within the desired maximum limit.

- Lower storage usage due to Schottky diode drop

- In case of short circuit on super capacitor side, there is no limit on short circuit current whereas in discrete circuit (Figure 2 (a)), the current set resistor R<sub>CH</sub> limits the short circuit current to I<sub>CH max</sub>.

Figure 4. Charging Profile of 5-F Super Capacitor Using P-FET-based Discrete Circuit

www.ti.com eFuse Solution

### 3 eFuse Solution

Copyright © 2017, Texas Instruments Incorporated

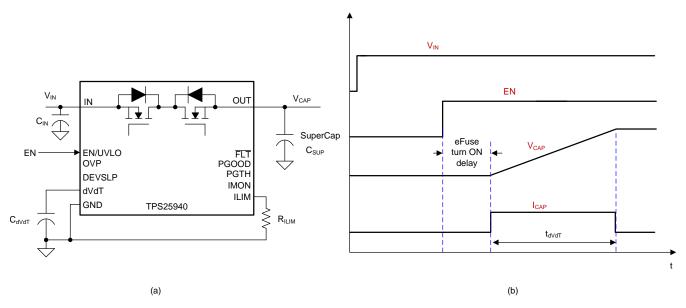

Figure 5. SuperCap Charger Circuit (a) eFuse Solution (b) Typical Operating Waveforms

Figure 5 (a) shows SuperCap charger solution using TPS25940A eFuse. Figure 5 (b) illustrates the operating waveforms during the charging of a super capacitor. When the eFuse is enabled, the super capacitor voltage starts building up after the eFuse turn ON delay. The ramp rate of the super capacitor voltage  $V_{CAP}$  can be adjusted by an external capacitor  $C_{dVdT}$  at the dVdT pin as per Equation 2. This in turn defines the charging current  $I_{CAP}$  of the super capacitor, as seen in Equation 3.

The eFuse-based SuperCap charger circuit overcomes the challenges of discrete solutions as follows:

- The integrated back-to-back FET configuration along with true reverse current blocking feature of TPS25940A eFuse eliminates the necessity of series Schottky diode.

- As there is no Schottky diode drop, the super capacitor charges to full supply voltage V<sub>IN</sub>, thus using the complete storage capacity of the super capacitor.

- The TPS25940A eFuse has an EN/UVLO pin to control the ON or OFF state of the internal FET and hence provides full controllability on the charging path of the super capacitor.

- The constant charging current profile with eFuse significantly reduces the charging time over discrete solutions.

- eFuse solution provides quick termination of transient short circuit currents and offers robust short circuit protection.

The total ramp time  $t_{dVdT}$  of  $V_{CAP}$  from 0 to  $V_{IN}$  for TPS25940A can be calculated using Equation 2.

$$t_{dVdT} = 8.3 \times 10^4 \times V_{IN} \times C_{dVdT}$$

(2)

The charging current of the super capacitor I<sub>CAP</sub> can be calculated as Equation 3.

$$I_{CAP} = C_{SUP} \times \left(\frac{V_{IN}}{t_{dVdT}}\right)$$

(3)

eFuse Solution www.ti.com

The constant charging current  $I_{CAP}$  sets a linear output ramp profile throughout the charging interval  $t_{dVdT}$ . The eFuse also has current limit function to limit output current to a value programmed by a resistor at the  $I_{LIM}$  pin. Equation 4 gives the relationship between  $I_{LIM}$  and  $R_{ILIM}$ . To ensure safe operation, the eFuse control logic limits the charging current to the lower of the two currents as determined in Equation 3 and Equation 4.

$$I_{LIM} = \frac{89}{R_{ILIM}} \tag{4}$$

#### Where:

- I<sub>LIM</sub> is overload current limit in Amp

- R<sub>ILIM</sub> is the current limit resistor in kΩ

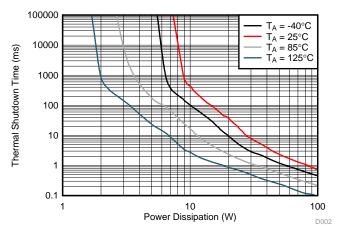

While charging the super capacitor, the eFuse experiences significant power stress. The instantaneous power dissipation across the device is  $(V_{IN}-V_{CAP}) \times I_{CAP}$ . As the super capacitor charges, the voltage difference across the device decreases, and the power dissipated decreases as well. For a successful design, the power dissipation during charging interval  $t_{dVdT}$  should not exceed the shutdown limits as shown in Figure 6. The average power dissipated in the device during charging interval  $t_{dVdT}$  is given by Equation 5.

$$P_{D\_STARTUP} = 0.5 \times V_{IN} \times I_{CAP}$$

(5)

It is important to determine the correct ramp time  $t_{\text{dVdT}}$  and hence charging current for a given super capacitor (capacitance) such that the eFuse monotonically charges the super capacitor without reaching thermal shutdown.

Figure 6. Thermal Shutdown Time Plot for TPS25940A eFuse

www.ti.com eFuse Solution

# 3.1 Setting Output Voltage Ramp Time ( $t_{dVdT}$ )

# 3.1.1 Using System Equations

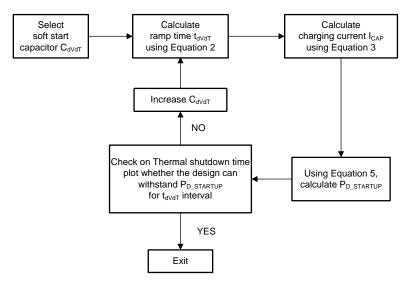

This approach is iterative and requires several calculations to arrive at appropriate  $t_{dVdT}$  for a particular output capacitance. As shown in Figure 7, the design starts with a certain value of soft start capacitor  $C_{dVdT}$  and then influences it in the right direction, so the design does not violate startup power stress considerations.

Figure 7. Design Flow Chart to Determine t<sub>dVdT</sub>

# 3.1.2 Using Online Design Calculation Tool

The TPS25940A eFuse has online design calculator[2], which uses the same design equations explained above. The designer must feed the supply voltage  $V_{IN}$  and the super capacitance value  $C_{SUP}$  in row 5 and 8 respectively. Then the designer must modify  $C_{dVdT}$  value in row 55 until the startup power dissipation falls within the acceptable limits and satisfies the system to have glitch-free startup.

### 3.1.3 Using Storage Capacity of the Super Capacitor

Substituting charging current I<sub>CAP</sub> from Equation 3 into Equation 5 gives Equation 6.

$$P_{D\_STARTUP} = 0.5 \times C_{SUP} \times \left(\frac{V_{IN}^{2}}{t_{dVdT}}\right)$$

(6)

Equation 7 shows the energy required to fully charge the super capacitor.

$$E_{SUP} = 0.5 \times C_{SUP} \times V_{IN}^{2} = P_{D\_STARTUP} \times t_{dVdT}$$

(7)

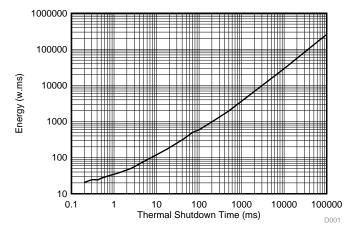

To charge a super capacitor to its rated capacity without thermal shutdown, the area under the curve at a particular operating point in Figure 6 should be equal to the energy capacity of the super capacitor  $E_{SUP}$ . Figure 8 shows the relation between energy  $E_{SUP}$  and ramp time at  $T_A = 85^{\circ}$ C, which derives from Figure 6. As super capacitors are restricted to operate less than 85°C for better life, maximum ambient temperature of 85°C is considered.

Test Results www.ti.com

In this design approach, first the energy required to charge super capacitor is calculated and then the corresponding ramp time (thermal shutdown time) is inferred from Figure 8. With the obtained ramp time, soft start capacitor  $C_{\text{dVdT}}$  is calculated using Equation 2. The result is then approximated to a standard capacitor value.

Figure 8. Averaged Energy Versus Thermal Shutdown Time at  $T_A = 85$ °C for Figure 6

### 4 Test Results

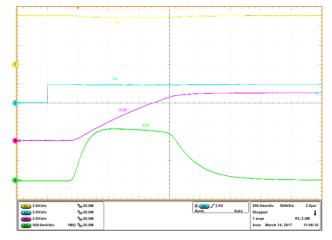

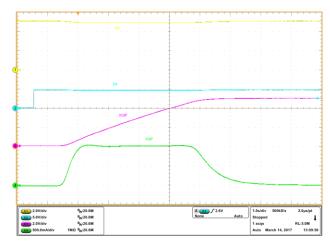

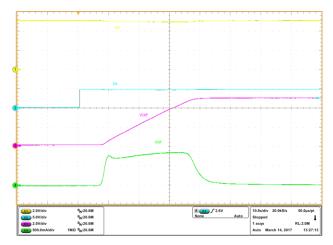

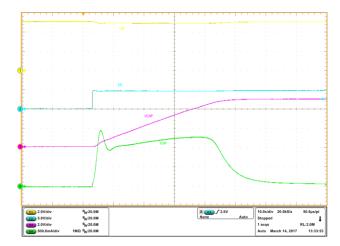

In this section, measured charging profiles of various super capacitors are shown from Figure 9 to Figure 12. Table 1 shows the calculations based on the design approach discussed in Section 3.1.3. It is clear that any capacity of super capacitor can be charged easily using eFuse through proper selection of soft-start capacitor  $C_{\text{dVdT}}$ .

Table 1. Output Ramp Time Calculations and Measurement Results

| SUPER<br>CAPACITOR<br>(F) | C <sub>dVdT</sub> CALCULATIONS            |                                            |                                               |                                    | MEASURED RESULTS       |                         |                  |

|---------------------------|-------------------------------------------|--------------------------------------------|-----------------------------------------------|------------------------------------|------------------------|-------------------------|------------------|

|                           | REQUIRED<br>ENERGY TO<br>CHARGE TO<br>5 V | t <sub>dVdT</sub> (ms)<br>FROM<br>Figure 8 | C <sub>dVdT</sub> (uF)<br>USING<br>Equation 2 | STANDARD<br>C <sub>dVdT</sub> (uF) | t <sub>dVdT</sub> (ms) | CHARGING<br>CURRENT (A) | TEST<br>WAVEFORM |

| 0.5                       | 6250                                      | 2000                                       | 4.82                                          | 4.7                                | 1800                   | 1.3                     | Figure 9         |

| 1                         | 12500                                     | 4000                                       | 9.64                                          | 10                                 | 4200                   | 1                       | Figure 10        |

| 5                         | 62500                                     | 22000                                      | 53.02                                         | 68                                 | 30000                  | 0.8                     | Figure 11        |

| 10                        | 125000                                    | 46000                                      | 110.84                                        | 100                                | 41000                  | 1.1                     | Figure 12        |

www.ti.com Test Results

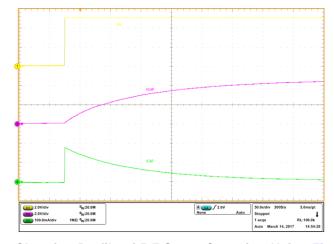

As shown in Figure 9, the super capacitor fully charges to supply voltage 5 V. In case of discrete circuits, the super capacitor reaches maximum of 4.7 V (refer Figure 3 and Figure 4).

Figure 9. Charging Profile of 0.5-F Super Capacitor Using TPS25940A eFuse

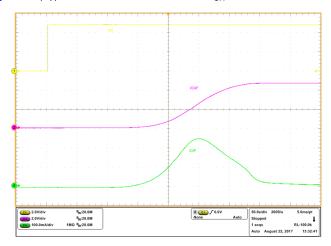

From Figure 9 and Figure 10, it is clear that higher charging currents can be allowed at lower output capacitance without reaching thermal shutdown.

Figure 10. Charging Profile of 1-F Super Capacitor Using TPS25940A eFuse

Test Results www.ti.com

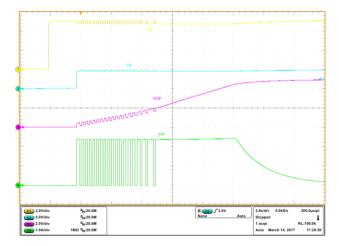

The time to charge 5-F super capacitor with discrete circuits is greater than 400 s whereas the time is just 30 s with eFuse as illustrated in Figure 11.

Figure 11. Charging Profile of 5-F Super Capacitor Using TPS25940A eFuse

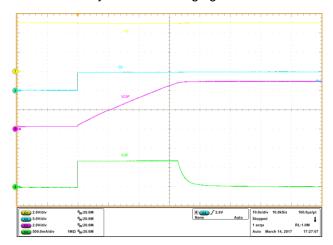

Figure 12. Charging Profile of 10-F Super Capacitor Using TPS25940A eFuse

www.ti.com Test Results

Figure 13 highlights the key advantage of using eFuse. If the designer places inadequate value of  $C_{\text{dVdT}}$  (here OPEN), the charging current gets safely limited to a value set by  $R_{\text{ILIM}}$ . For Figure 13 test case,  $I_{\text{LIM}}$  is set to 2.1 A. Because the charging current is higher, the device enters into thermal shutdown and attempts to charge again after auto-retry delay of 128 ms. The built-in over temperature cutoff of eFuse protects the internal FET and any further system damage.

Figure 13. Charging Profile of 5-F Super Capacitor, When  $C_{dVdT}$  is OPEN and  $I_{LIM}$  set to 2.1A

Figure 14 demonstrates another key feature Safe during Single Point Failure of TPS25940A eFuse. For example, during a single failure, such as SHORT to an external current limit resistor and inadequate value of  $C_{\text{dVdT}}$  (here OPEN), the device safely limits the charging current to 670 mA (Typical).

Figure 14. Charging Profile of 5-F Super Capacitor, When  $C_{dVdT}$  is OPEN and  $I_{LIM}$  is SHORT

Comparison Summary www.ti.com

# 5 Comparison Summary

In this section, comparison between discrete and eFuse charger solutions is shown for a 5F super capacitor charger application. As shown in Table 2, the eFuse solution offers full controllability on the charging path and better storage capacity usuage. Additionally, several integrated protection features of eFuse provides design freedom in the selection of external components for the charger circuit.

**Table 2. Comparison Table**

| PARAMETER                                 | SCHOTTKY DIODE BASED<br>DISCRETE CHARGING CIRCUIT          | P-FET-BASED DISCRETE<br>CHARGING CIRCUIT | eFUSE CHARGING CIRCUIT |

|-------------------------------------------|------------------------------------------------------------|------------------------------------------|------------------------|

| Controllability                           | No                                                         | Yes                                      | Yes                    |

| Storage capacity utilization              | 87%                                                        | 87%                                      | 100%                   |

| Charging time for 5-<br>F super capacitor | ≈ 400 s                                                    | ≈ 325 s                                  | ≈ 30 s                 |

| Short circuit protection                  | Yes, R <sub>CH</sub> limits the current                    | No                                       | Yes                    |

| Overvoltage protection                    | Requires additional circuitry                              | Requires additional circuitry            | Yes                    |

| Thermal protection                        | R <sub>CH</sub> limits the current and provides protection | No                                       | Yes                    |

### 6 Conclusion

The programmable charging current, true reverse current blocking capability, and the monotonous voltage ramp-up profile with eFuse makes it preferable choice for charging larger capacity super capacitors. Further, built-in thermal protection feature and *Safe during Single Point Failure* feature avoids damage to the eFuse and any disturbance to the system voltage. In the similar way, eFuse can be used to charge large holdup capacitor in backup power systems.

# 7 References

- 1. TPS25940, 18V, 5A,  $42m\Omega$  eFuse With Integrated Reverse Current Protection and DevSleep Support (SLVSCF3)

- 2. TPS2594x Design Calculation Tool (http://www.ti.com/product/TPS25940/toolssoftware)

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ("TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/sampterms.htm">http://www.ti.com/sc/docs/sampterms.htm</a>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated