# ESD224 HDMI® 2.0 Compliance and Protection

Cameron Phillips

#### ABSTRACT

This application report presents HDMI<sup>®</sup> 2.0 Compliance and ESD clamping data for the ESD224 4-channel HDMI ESD protection device. The low clamping and high-differential bandwidth provided by the on-chip ESD protection network of the ESD224 makes it possible to be able to cleanly pass HDMI 2.0 signals while providing robust protection to downstream HDMI devices.

#### Contents

| 1 | Introduction to ESD224                         | 2  |

|---|------------------------------------------------|----|

| 2 | HDMI® Simulations During Design                | 2  |

| 3 | HDMI® Compliance Data From Testing with TDP158 | 7  |

| 4 | ESD224 Protection of Down Stream Devices       | 11 |

| 5 | Summary                                        | 12 |

| 6 | References                                     | 12 |

#### List of Figures

| 1  | Model Plus Lumped Elements for S-Parameter          | 2  |

|----|-----------------------------------------------------|----|

| 2  | ESD224 Bandwidth and Calibration Board              | 3  |

| 3  | Insertion Loss From Simulation and Measurements     | 3  |

| 4  | HDMI® 2.0 TDR Schematic With ESD224                 | 4  |

| 5  | TDR Simulation With ESD224                          | 5  |

| 6  | TDR Measurement Data                                | 5  |

| 7  | HDMI® 2.0 Compliance Test Bench Circuit With ESD224 | 6  |

| 8  | Eye Diagram from Simulation With ESD224             | 6  |

| 9  | TDP158RSBEVM With ESD224                            | 7  |

| 10 | EVM Connected Between HDMI® Source and Sink         | 7  |

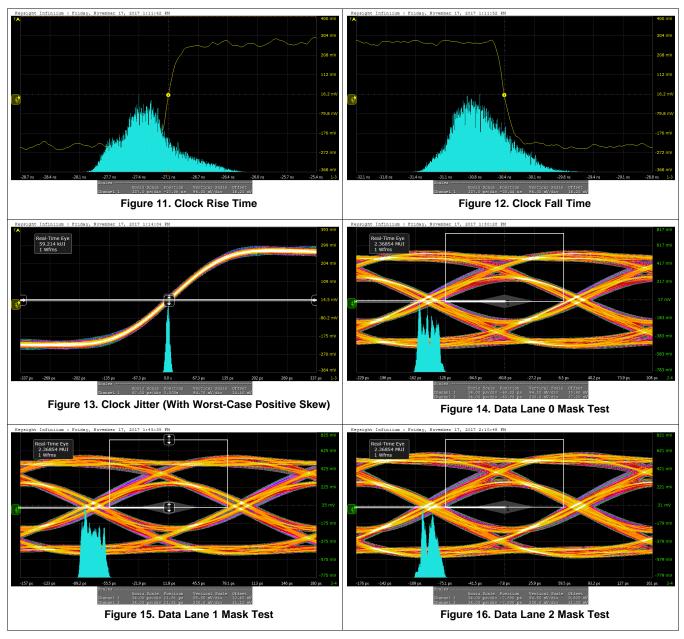

| 11 | Clock Rise Time                                     | 10 |

| 12 | Clock Fall Time                                     | 10 |

| 13 | Clock Jitter (With Worst-Case Positive Skew)        | 10 |

| 14 | Data Lane 0 Mask Test                               | 10 |

| 15 | Data Lane 1 Mask Test                               | 10 |

| 16 | Data Lane 2 Mask Test                               | 10 |

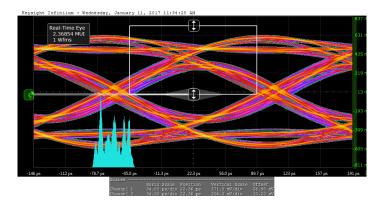

| 17 | TDP158RSBEVM Without ESD224 Data Lane 2 Mask Test   | 11 |

| 18 | ESD224 Clamping PCB                                 | 11 |

| 19 | ESD224 ESD Clamping Waveform +8-kV With BCM7250     | 12 |

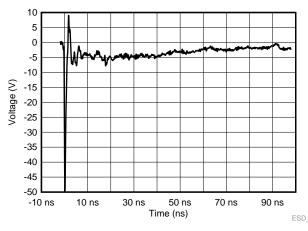

| 20 | ESD224 ESD Clamping Waveform –8-kV With BCM7250     | 12 |

|    |                                                     |    |

#### List of Tables

| 1 | Sink Impedance Characteristics for 3.4 Gbps < $R_{bit} \le 6.0$ Gbps at TP2 | 4 |

|---|-----------------------------------------------------------------------------|---|

| 2 | HDMI® Test Report                                                           | 8 |

| 3 | Summary of Results with Margins                                             | 9 |

# TEXAS INSTRUMENTS

www.ti.com

#### Trademarks

HDMI is a registered trademark of HDMI Licensing, LLC. Keysight, Infiniium are trademarks of Keysight Technologies, Inc.. All other trademarks are the property of their respective owners.

## 1 Introduction to ESD224

The ESD224 is a bidirectional TVS ESD protection diode array for high-speed applications such as HDMI 2.0 applications. The ESD224 employs on-chip differentially matched series elements to enhance downstream ESD clamping performance while maintaining the signal compliance for HDMI. Due to the presence of the on-chip series elements for enhanced ESD clamping, the device is in a non-flow-through DQA package. The ESD224 is suitable to protect both the TMDS data lines (D0±, D1±, D2±) and TMDS clock lines (CLK±). See *ESD224 Low Clamping 4-Channel ESD Protection Device for HDMI Interface* for more information.

This document describes the modeling environment and RF simulations performed during device design and demonstrates the devices RF performance through comparisons of modeled and silicon data. The ESD224 was evaluated for HDMI 2.0 compliance in a reference design using the TI TDP158 HDMI retimer. ESD clamping and protection performance was evaluated by measuring the downstream clamping performance of the ESD224 on an application board employing a common set-top box (STB) system-on-achip (SoC).

# 2 HDMI® Simulations During Design

## 2.1 Bandwidth

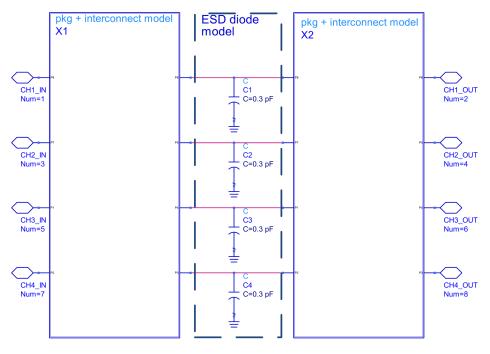

The goal of the ESD224 was to provide a low clamping device while still being able to pass HDMI 2.0 (6 Gbps). In order to prove this during the concept phase, a 3D model with the internal structure was built for the lead frame of the device. Using this model in the Advanced Design System (ADS) from Keysight<sup>™</sup>, and adding in the lumped elements could give us the S-parameter data needed to show HDMI compliance. The lumped elements of the device are represented by a capacitor, because if the ESD diode is not turned on for an ESD event, the diodes can just be represented by their junction capacitance. Figure 1 shows the S-parameter model generation that was created during the Design Phase of ESD224 development.

Figure 1. Model Plus Lumped Elements for S-Parameter

Observe the ADS schematic in Figure 1 only has a lumped capacitance added for the ESD clamp and not the detailed on-die design structure. The S-parameter file for the internal structure (X1 and X2 in Figure 1) without the main ESD diode was modeled in a separate environment using a detailed 3D buildup of the silicon die, bond wires, and package. Therefore, the only parameter that needs to be added is the ESD clamp capacitance, which was calculated to be 0.3 pF, based on design and process considerations. This is a good approximation for a first-order model. When the lumped capacitance of the ESD diodes is added to the S-parameter model of rest of the device, the resulting lumped capacitance was 0.5 pF, and then confirmed in measurements of 0.5 pF at 1 MHz.

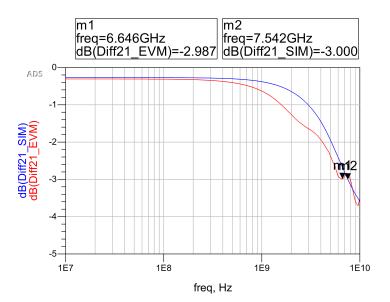

The model in Figure 1 allowed the frequency response of the ESD224 device to be simulated and optimized using ADS. The bandwidth of the device is shown by plotting the insertion loss over frequency and measuring where the –3 dB point occurs. For HDMI 2.0, the –3 dB point needs to be greater than 6 Gbps (3 GHz). Once the device design was finalized, characterization boards were designed and fabricated to measure the actual bandwidth of the ESD224. Figure 2 shows the board design. Since the bandwidth of the device itself is of primary concern, a calibration board was made to mimic the connectors and traces without the ESD224. The calibration board was then used to de-embed the ESD224 from the bandwidth board and show the bandwidth of the device alone (see Figure 3). In this graph, the plot Diff21\_SIM is the differential bandwidth as measured on the calibration board.

Figure 2. ESD224 Bandwidth and Calibration Board

Figure 3. Insertion Loss From Simulation and Measurements

M1 is the -3 dB point of the measured results while M2 is the -3 dB point of the simulation results. It can be seen that the measured and simulated results diverge after approximately 1 GHz due to inconsistency in the simulation model vs the measured result. What is important is the simulation and measured results are a close approximation for a first-order model. This means that we are confident enough in our data to continue on with the testing.

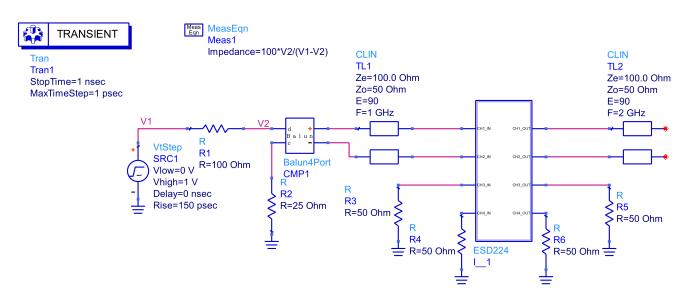

#### 2.2 Time Domain Response

Using the ADS *Time Domain Function*, it is also possible to simulate the *Time Domain Response* (TDR) test required for HDMI 2.0. TDR analysis uses a voltage source to generate a pulse with a specific rise time and then measure the reflections. TDR analyzes the impedance versus time to see the changes in impedance due to the connector, board traces, and the device itself. The TDR requirements of HDMI 2.0 are shown in Table 1.

| Table 1. Sink Impedance Characteristics for | 3.4 Gbps < R <sub>bi</sub> | $_{t} \leq 6.0$ Gbps at TP2 |

|---------------------------------------------|----------------------------|-----------------------------|

|---------------------------------------------|----------------------------|-----------------------------|

| ltem                                        | Value                         |

|---------------------------------------------|-------------------------------|

| TDR Rise Time at TP2 (10%–90%)              | ≤ 200 ps                      |

| Through Connection Impedance <sup>(1)</sup> | $100 \ \Omega \pm 15\%^{(2)}$ |

| Sink Termination Impedance                  | 90 Ω to 100 Ω                 |

<sup>(1)</sup> Impedance from TP2 to *Sink Termination*.

<sup>(2)</sup> A single excursion is permitted out to a maximum or minimum of 100  $\Omega$  ±25% and of duration less than 250 ps.

Figure 4. HDMI® 2.0 TDR Schematic With ESD224

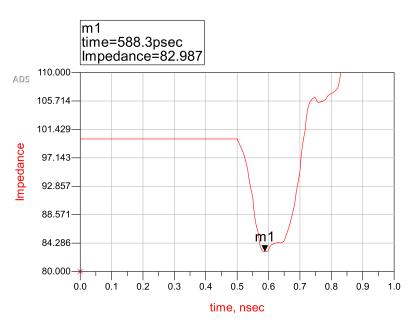

Using the simulation setup in Figure 4 the results were obtained in Figure 5. When this simulation is run, the result shows a TDR that meets the requirement of a single excursion of 100  $\Omega$  ±25% for 250-ps maximum rise time as shown in Table 1.

Figure 5. TDR Simulation With ESD224

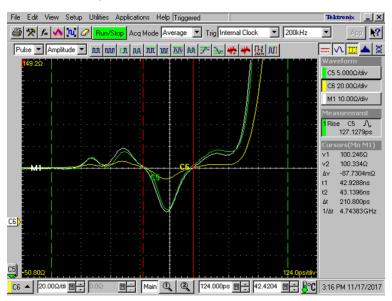

Simulated TDR results were verified using actual TDR measurments. The same board that was used to do the bandwidth measurements of the ESD224 was used to do the TDR measurements. Two of the connectors were connected to an oscilloscope to do the measurement while the other side was left open. Figure 6 shows the measurement data taken. This measurement was taken at 150-ps rise time in compliance with the HDMI 2.0 requirement.

Figure 6. TDR Measurement Data

Figure 6 shows two single-ended measurements, C5 and C6, and the differential measurement of M1. Note that each of these graphs have a different scaling. The M1 plot is on 10  $\Omega$ /div while the C5 graph is 5  $\Omega$ /div and the C6 plot is 20  $\Omega$ /div. The middle line of the X axis set at 100  $\Omega$  for the M1 differential measurement. The first two peaks that show up in the plots are from the SMA connector and the traces leading up to the actual device. The device shows up as the valley in the middle of the graph. This valley is representative of the ESD224 device which is dominated by the lumped capacitance of the ESD diode

#### HDMI® Simulations During Design

inside the IC. As is shown by the red cursors on the graph, the excursion is at 210 ps and from the M1 plot it can be seen that the minimum point is > 80  $\Omega$ , both of which meet the requirement of the HDMI 2.0 standard. The small peak after the device is the second connector and associated traces but since the device overshadows it, it looks like just one lump. After the last connector, the board connection is open so the impedance goes to infinity.

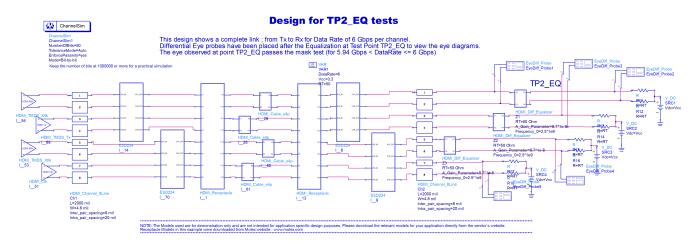

## 2.3 HDMI® 2.0 Simulation

After having confirmed good correlation in the bandwidth and TDR measurements between the simulated and measured device data, the ESD224 was simulated in a HDMI 2.0 compliance test bench to ensure that it could pass the required eye diagram. The ADS software from Keysight Technologies contains an *HDMI 2.0 Compliance Test Bench*. The ESD224 S-Parameter model generated earlier was inserted in the appropriate location in the ADS HDMI test bench.

Figure 7. HDMI® 2.0 Compliance Test Bench Circuit With ESD224

Running the simulation yielded a passing eye diagram for HDMI 2.0.

Figure 8. Eye Diagram from Simulation With ESD224

## **3 HDMI® Compliance Data From Testing with TDP158**

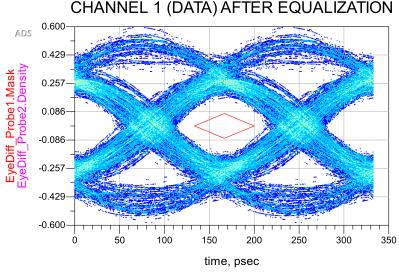

With the confidence from the simulations of bandwidth, TDR, and HDMI 2.0 compliance test bench, the ESD224 was placed onto the TDP158RSBEVM.

Figure 9. TDP158RSBEVM With ESD224

The TDP158 evaluation module (EVM) is used to characterize the HDMI 2.0 retimer from Texas Instruments. The TDP158EVM board had all of the relevant items for HDMI 2.0 compliance testing so to modify it for HDMI compliance with the ESD224 was straightforward. The ESD224s (U8, U9) were placed near the HDMI connector for best protection of the HDMI port. After making the board, the HDMI 2.0 testing needed to be done. This involved sending signals to the retimer on the clock, and data lines having them pass through the ESD224, and then were read on an oscilloscope running HDMI 2.0 compliance software. Figure 10 shows this setup.

Figure 10. EVM Connected Between HDMI® Source and Sink

The HDMI 2.0 compliance test consists of testing VL, rise time and fall time, inter- and intra-pair skew, differential voltage, clock duty cycle, clock jitter, data eye diagram, and differential impedance. More information about the HDMI compliance tests is found in *TI ESD Protection Devices and the HDMI CTS*.

# 3.1 Measured Data

Table 2 shows the results of the HDMI compliance tests.

| Table 2 | HDMI® | Test | Report |

|---------|-------|------|--------|

|---------|-------|------|--------|

|                         | Overall Result: Pass                                                    |  |  |  |  |

|-------------------------|-------------------------------------------------------------------------|--|--|--|--|

|                         | Test Configuration Details                                              |  |  |  |  |

| Device Description      |                                                                         |  |  |  |  |

| Device ID               | Transmitter                                                             |  |  |  |  |

| Fixture Type            | N1080H04                                                                |  |  |  |  |

| Probe Connection        | 4 Probes                                                                |  |  |  |  |

| Probe Head Type         | N5380A/B                                                                |  |  |  |  |

| Lane Connection         | 1 Data Lane                                                             |  |  |  |  |

| HDMI Specification      | 2.0                                                                     |  |  |  |  |

| HDMI Test Type          | TMDS Physical Layer Tests                                               |  |  |  |  |

|                         | Test Session Details                                                    |  |  |  |  |

| Infiniium™ SW Version   | 05.52.0004                                                              |  |  |  |  |

| Infiniium Model Number  | DSOX91604A                                                              |  |  |  |  |

| Infiniium Serial Number | MY50270161                                                              |  |  |  |  |

| Application SW Version  | 2.12.0001                                                               |  |  |  |  |

| Debug Mode Used         | No                                                                      |  |  |  |  |

| Probe (Channel 1)       | Model: 1169A                                                            |  |  |  |  |

|                         | Serial: US49410841                                                      |  |  |  |  |

|                         | Head: N5380A/B                                                          |  |  |  |  |

|                         | Atten: Calibrated (15 NOV 2017 13:33:51), Using Cal Atten (2.0177E+000) |  |  |  |  |

|                         | Skew: Calibrated (15 NOV 2017 13:34:04), Using Cal Skew                 |  |  |  |  |

| Probe (Channel 2)       | Model: 1169A                                                            |  |  |  |  |

|                         | Serial: US44005778                                                      |  |  |  |  |

|                         | Head: N5380A/B                                                          |  |  |  |  |

|                         | Atten: Calibrated (15 NOV 2017 13:28:35), Using Cal Atten (2.1007E+000) |  |  |  |  |

|                         | Skew: Calibrated (15 NOV 2017 13:28:48), Using Cal Skew                 |  |  |  |  |

| Probe (Channel 3)       | Model: 1169A                                                            |  |  |  |  |

|                         | Serial: US49411926                                                      |  |  |  |  |

|                         | Head: N5380A/B                                                          |  |  |  |  |

|                         | Atten: Calibrated (15 NOV 2017 13:29:49), Using Cal Atten (2.0610E+000) |  |  |  |  |

|                         | Skew: Calibrated (15 NOV 2017 13:30:01), Using Cal Skew                 |  |  |  |  |

| Probe (Channel 4)       | Model: 1169A                                                            |  |  |  |  |

|                         | Serial: US53270572                                                      |  |  |  |  |

|                         | Head: N5380A/B                                                          |  |  |  |  |

|                         | Atten: Calibrated (15 NOV 2017 13:31:07), Using Cal Atten (2.1060E+000) |  |  |  |  |

|                         | Skew: Calibrated (15 NOV 2017 13:31:23), Using Cal Skew                 |  |  |  |  |

| Last Test Date          | 2017-11-17 14:12:54 UTC -06:00                                          |  |  |  |  |

Table 3 shows a summary of the results showing the margin of passing.

| Pass | Test Name                                                  | Actual<br>Value | Margin | Pass Limits                      |

|------|------------------------------------------------------------|-----------------|--------|----------------------------------|

| Yes  | HF1-2: Clock Rise Time                                     | 142.907 ps      | 90.5 % | VALUE >= 75.000 ps               |

| Yes  | HF1-2: Clock Fall Time                                     | 142.120 ps      | 89.5 % | VALUE >= 75.000 ps               |

| Yes  | HF1-6: Clock Duty Cycle(Minimum)                           | 49.230          | 23.1 % | >=40%                            |

| Yes  | HF1-6: Clock Duty Cycle(Maximum)                           | 49.990          | 16.7 % | <=60%                            |

| Yes  | HF1-7: Differential Clock Voltage Swing, Vs (TP1)          | 506 mV          | 13.3 % | 400 mV < VALUE < 1.200 V         |

| Yes  | HF1-7: Clock Jitter (TP2_EQ with Worst Case Positive Skew) | 136 mTbit       | 54.7 % | VALUE <= 300 mTbit               |

| Yes  | HF1-7: Clock Jitter (TP2_EQ with Worst Case Negative Skew) | 134 mTbit       | 55.3 % | VALUE <= 300 mTbit               |

| Yes  | HF1-5: D0 Maximum Differential Voltage                     | 571 m           | 26.8 % | VALUE <= 780 m                   |

| Yes  | HF1-5: D0 Minimum Differential Voltage                     | –540 m          | 30.8 % | VALUE >= -780 m                  |

| Yes  | HF1-2: D0 Rise Time                                        | 62.478 ps       | 47.0 % | VALUE >= 42.500 ps               |

| Yes  | HF1-2: D0 Fall Time                                        | 59.785 ps       | 40.7 % | VALUE >= 42.500 ps               |

| Yes  | HF1-8: D0 Mask Test (TP2_EQ with Worst Case Positive Skew) | 0.000           | 50.0 % | No Mask Failures                 |

| Yes  | HF1-8: D0 Mask Test (TP2_EQ with Worst Case Negative Skew) | 0.000           | 50.0 % | No Mask Failures                 |

| Yes  | HF1-1: VL Clock +                                          | 2.894 V         | 25.8 % | 2.300 V <= VALUE <= 3.100 V      |

| Yes  | HF1-1:Clock + VSwing                                       | 257 mV          | 14.3 % | 200 mV <= VALUE <= 600 mV        |

| Yes  | HF1-1: VL Clock –                                          | 2.891 V         | 26.1 % | 2.300 V <= VALUE <= 3.100 V      |

| Yes  | HF1-1:Clock - VSwing                                       | 257 mV          | 14.3 % | 200 mV <= VALUE <= 600 mV        |

| Yes  | HF1-4: Intra-Pair Skew - Clock                             | 116 mTbit       | 11.3 % | -150 mTbit <= VALUE <= 150 mTbit |

| Yes  | HF1-1: VL D0+                                              | 2.570 V         | 45.0 % | 2.300 V <= VALUE <= 2.900 V      |

| Yes  | HF1-1: D0+ VSwing                                          | 444 mV          | 22.0 % | 400 mV <= VALUE <= 600 mV        |

| Yes  | HF1-1: VL D0-                                              | 2.531 V         | 38.5 % | 2.300 V <= VALUE <= 2.900 V      |

| Yes  | HF1-1: D0- VSwing                                          | 453 mV          | 26.5 % | 400 mV <= VALUE <= 600 mV        |

| Yes  | HF1-4: Intra-Pair Skew - Data Lane 0                       | 14 mTbit        | 45.3 % | -150 mTbit <= VALUE <= 150 mTbit |

| Yes  | HF1-5: D1 Maximum Differential Voltage                     | 573 m           | 26.5 % | VALUE <= 780 m                   |

| Yes  | HF1-5: D1 Minimum Differential Voltage                     | -534 m          | 31.5 % | VALUE >= -780 m                  |

| Yes  | HF1-2: D1 Rise Time                                        | 66.171 ps       | 55.7 % | VALUE >= 42.500 ps               |

| Yes  | HF1-2: D1 Fall Time                                        | 66.123 ps       | 55.6 % | VALUE >= 42.500 ps               |

| Yes  | HF1-8: D1 Mask Test (TP2_EQ with Worst Case Positive Skew) | 0.000           | 50.0 % | No Mask Failures                 |

| Yes  | HF1-8: D1 Mask Test (TP2_EQ with Worst Case Negative Skew) | 0.000           | 50.0 % | No Mask Failures                 |

| Yes  | HF1-1: VL D1+                                              | 2.560 V         | 43.3 % | 2.300 V <= VALUE <= 2.900 V      |

| Yes  | HF1-1: D1+ VSwing                                          | 440 mV          | 20.0 % | 400 mV <= VALUE <= 600 mV        |

| Yes  | HF1-1: VL D1-                                              | 2.527 V         | 37.7 % | 2.300 V <= VALUE <= 2.900 V      |

| Yes  | HF1-1: D1- VSwing                                          | 479 mV          | 39.5 % | 400 mV <= VALUE <= 600 mV        |

| Yes  | HF1-4: Intra-Pair Skew - Data Lane 1                       | –13 mTbit       | 45.7 % | -150 mTbit <= VALUE <= 150 mTbit |

| Yes  | HF1-5: D2 Maximum Differential Voltage                     | 609 m           | 21.9 % | VALUE <= 780 m                   |

| Yes  | HF1-5: D2 Minimum Differential Voltage                     | –563 m          | 27.8 % | VALUE >= -780 m                  |

| Yes  | HF1-2: D2 Rise Time                                        | 64.868 ps       | 52.6 % | VALUE >= 42.500 ps               |

| Yes  | HF1-2: D2 Fall Time                                        | 71.854 ps       | 69.1 % | VALUE >= 42.500 ps               |

| Yes  | HF1-8: D2 Mask Test (TP2_EQ with Worst Case Positive Skew) | 0.000           | 50.0 % | No Mask Failures                 |

# Table 3. Summary of Results with Margins

|      | , , , ,                                                    |                 |        |                                  |  |  |

|------|------------------------------------------------------------|-----------------|--------|----------------------------------|--|--|

| Pass | Test Name                                                  | Actual<br>Value | Margin | Pass Limits                      |  |  |

| Yes  | HF1-8: D2 Mask Test (TP2_EQ with Worst Case Negative Skew) | 0.000           | 50.0 % | No Mask Failures                 |  |  |

| Yes  | HF1-1: VL D2+                                              | 2.514 V         | 35.7 % | 2.300 V <= VALUE <= 2.900 V      |  |  |

| Yes  | HF1-1: D2+ VSwing                                          | 488 mV          | 44.0 % | 400 mV <= VALUE <= 600 mV        |  |  |

| Yes  | HF1-1: VL D2-                                              | 2.461 V         | 26.8 % | 2.300 V <= VALUE <= 2.900 V      |  |  |

| Yes  | HF1-1: D2- VSwing                                          | 486 mV          | 43.0 % | 400 mV <= VALUE <= 600 mV        |  |  |

| Yes  | HF1-4: Intra-Pair Skew - Data Lane 2                       | 2 mTbit         | 49.3 % | -150 mTbit <= VALUE <= 150 mTbit |  |  |

Table 3. Summary of Results with Margins (continued)

Figure 11 through Figure 16 illustrate pictures of the key data measurements.

These eye diagrams can be compared to the EVM board without any ESD protection.

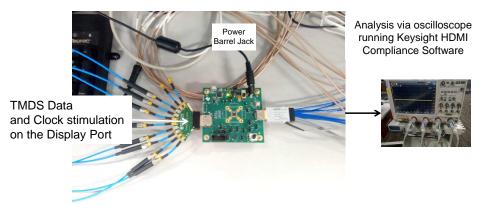

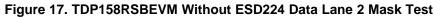

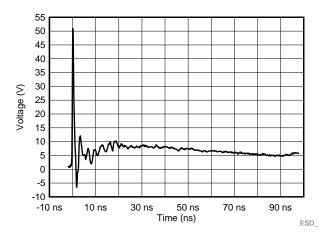

# 4 ESD224 Protection of Down Stream Devices

The ESD224 has internal circuitry that allows the device to have a low system-side clamping voltage during ESD tests. In order to show the low clamping voltage of the device, a board was built with the ESD224 protecting the HDMI lines of the BCM7250 Broadcom SoC used in STBs. This board allowed the HDMI lines to be struck with an ESD pulse in various scenarios. These scenarios are striking the line through a cable, striking the BCM7250 chip with just ESD224 protection, striking BCM7250 chip with ESD224 and common-mode choke (CMC) protection, and striking BCM7250 with TPD4E02B04 and CMC protection for comparison.

Figure 18. ESD224 Clamping PCB

In order to know what the clamping voltage that the BCM7250 downstream sees, SMA headers were placed hanging off of the HDMI lines to see the clamping waveform during an ESD strike. The device was then struck on the individual HDMI lines and the clamping voltage measured on an oscilloscope.

It is also important to note that the BCM7250 was powered on so that all of its internal ESD structures were biased to the correct level. The board was struck with  $\pm 8$  kV according to the IEC 61000-4-2 standard and the clamping waveform was captured. The clamping voltage of an ESD diode is defined at 30 ns. This shows that the clamping voltage is 7.8 V at 30 ns for +8-kV ESD strike and -5 V at 30 ns for -8-kV ESD strike.

Summary

www.ti.com

Figure 19. ESD224 ESD Clamping Waveform +8-kV With BCM7250

Figure 20. ESD224 ESD Clamping Waveform –8-kV With BCM7250

This clamping waveform is a reflection also of how much current the BCM7250 draws. The internal series clamping circuit is designed to limit the residual ESD current flowing through the downstream device and drop a portion of the clamping voltage across the series clamping circuit to reduce the voltage presented to the system side.

When the system device downstream fails, the leakage into that pin will change. For the BCM7250 the leakage into the pin during powered on mode and before the ESD strike is 8.67  $\mu$ A. After the ESD strike occurs, the leakage was 8.7  $\mu$ A, showing that the device has not been damaged.

## 5 Summary

The process from design to validation that TI undergoes is thorough, allowing TI to accurately predict the behavior of the devices during every stage of the device cycle. The ESD224 device was specifically made with the specifications in order to provide the most robust solution possible. Even though the ESD224 is a non-flow through device, the ESD224 is an ultra-low clamping, HDMI-compliant ESD protection device. It provides protection for the TMDS data and clock lines while also allowing the system to be compliant with the HDMI protocol.

## 6 References

Texas Instruments, ESD224 Low Clamping 4-Channel ESD Protection Device for HDMI Interface Data Sheet

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated