# An empirical analysis of the impact of board layout on LDO thermal performance

Gerard Copeland

#### **ABSTRACT**

This application report investigates the impact of the printed circuit board (PCB) layout on low dropout (LDO) regulator thermal performance, specifically the junction-to-ambient thermal resistance,  $\theta_{JA}$ . This parameter is measured for the TPS745 (WSON package), TPS7B82-Q1 (TO-252 package), and TLV755P (SOT-23 package) devices. Each device is tested with five layouts, each containing increasing amounts of copper coverage on both internal and external layers. Increasing the amount of copper coverage reduces  $\theta_{JA}$ , but reaches a point of diminishing returns. Copper coverage is more effective on packages with thermal pads. These results are used to provide layout tips for system designers to improve thermal performance. Although the devices tested in this study are exclusively LDOs, the effects of the PCB layout and conclusions drawn in this application report are extended to other power dissipative devices.

#### Contents

| 1     | Introduction                                              |

|-------|-----------------------------------------------------------|

| 2     | Procedure                                                 |

| 3     | Test Results and Discussion                               |

| 4     | Conclusion                                                |

| 5     | Future Study                                              |

| 6     | References                                                |

| Appen | •                                                         |

| Appen | dix B Thermal Test Results                                |

|       | List of Figures                                           |

| 1     | TPS745 (WSON) 1S0P Approximation Layout                   |

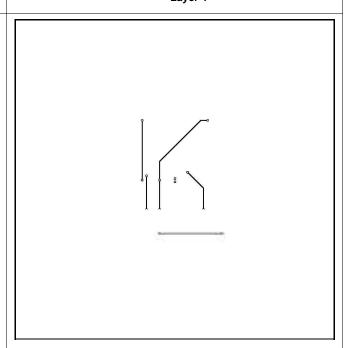

| 2     | TPS745 (WSON) Internally Disconnected Layout              |

| 3     | TPS745 (WSON) JEDEC High-K Approximation Layout           |

| 4     | TPS745 (WSON) Thermally Enhanced Layout                   |

| 5     | TPS745 (WSON) Thermally Saturated Layout                  |

| 6     | TPS745 (WSON) 1S0P Approximation Layout Test Results      |

| 7     | TPS745 (WSON) $\theta_{JA}$ vs. Board Layout              |

| 8     | TPS7B82-Q1 (TO-252) $\theta_{JA}$ vs. Board Layout        |

| 9     | TLV755P (SOT-23) $\theta_{JA}$ vs. Board Layout           |

| 10    | $\theta_{JA}$ Reduction for Each Device                   |

| 11    | Normalized $\theta_{JA}$ for Each Device vs. Board Layout |

| 12    | TPS745 (WSON) 1S0P Approximation Top Layer                |

| 13    | TPS745 (WSON) 1S0P Approximation Internal Layer 1         |

| 14    | TPS745 (WSON) 1S0P Approximation Internal Layer 2         |

| 15    | TPS745 (WSON) 1S0P Approximation Bottom Layer             |

| 16    | TPS745 (WSON) Internally Disconnected Top Layer           |

| 17    | TPS745 (WSON) Internally Disconnected Internal Layer 1    |

| 18    | TPS745 (WSON) Internally Disconnected Internal Layer 2    |

| 19    | TPS745 (WSON) Internally Disconnected Bottom Layer        |

| 20 | TPS745 (WSON) JEDEC High-K Approximation Top Layer              |    |

|----|-----------------------------------------------------------------|----|

| 21 | TPS745 (WSON) JEDEC High-K Approximation Internal Layer 1       |    |

| 22 | TPS745 (WSON) JEDEC High-K Approximation Internal Layer 2       |    |

| 23 | TPS745 (WSON) JEDEC High-K Approximation Bottom Layer           | 16 |

| 24 | TPS745 (WSON) Thermally Enhanced Top Layer                      | 17 |

| 25 | TPS745 (WSON) Thermally Enhanced Internal Layer 1               | 17 |

| 26 | TPS745 (WSON) Thermally Enhanced Internal Layer 2               | 17 |

| 27 | TPS745 (WSON) Thermally Enhanced Bottom Layer                   | 17 |

| 28 | TPS745 (WSON) Thermally Saturated Top Layer                     | 18 |

| 29 | TPS745 (WSON) Thermally Saturated Internal Layer 1              | 18 |

| 30 | TPS745 (WSON) Thermally Saturated Internal Layer 2              |    |

| 31 | TPS745 (WSON) Thermally Saturated Bottom Layer                  |    |

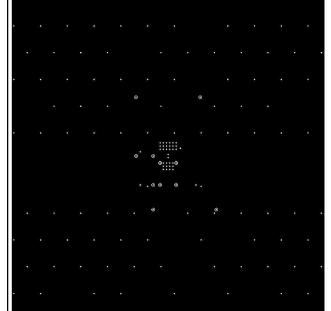

| 32 | TPS7B82-Q1 (TO-252) 1S0P Approximation Top Layer                |    |

| 33 | TPS7B82-Q1 (TO-252) 1S0P Approximation Internal Layer 1         |    |

| 34 | TPS7B82-Q1 (TO-252) 1S0P Approximation Internal Layer 2         |    |

| 35 | TPS7B82-Q1 (TO-252) 1S0P Approximation Bottom Layer             |    |

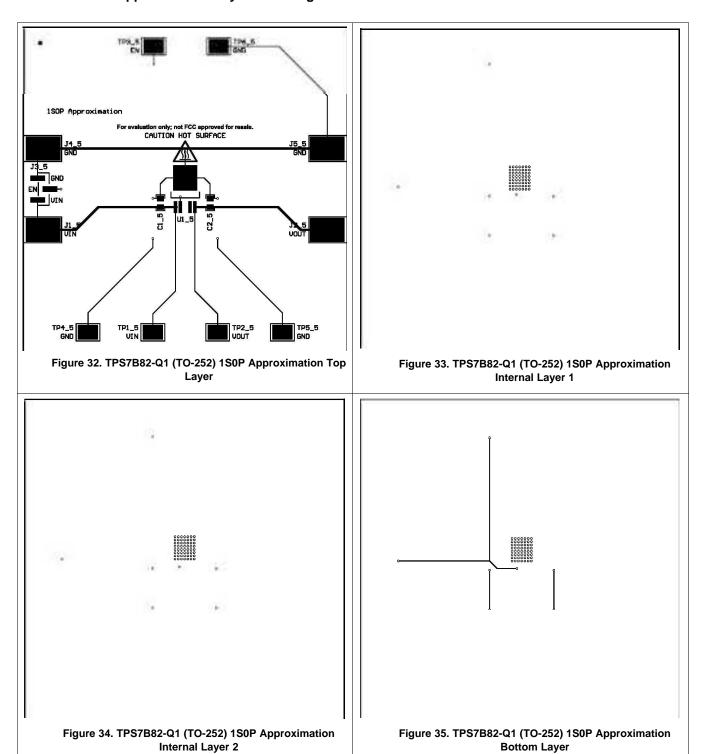

| 36 | TPS7B82-Q1 (TO-252) Internally Disconnected Top Layer           |    |

|    |                                                                 |    |

| 37 | TPS7B82-Q1 (TO-252) Internally Disconnected Internal Layer 1    |    |

| 38 | TPS7B82-Q1 (TO-252) Internally Disconnected Internal Layer 2    |    |

| 39 | TPS7B82-Q1 (TO-252) Internally Disconnected Bottom Layer        |    |

| 40 | TPS7B82-Q1 (TO-252) JEDEC High-K Approximation Top Layer        |    |

| 41 | TPS7B82-Q1 (TO-252) JEDEC High-K Approximation Internal Layer 1 |    |

| 42 | TPS7B82-Q1 (TO-252) JEDEC High-K Approximation Internal Layer 2 |    |

| 43 | TPS7B82-Q1 (TO-252) JEDEC High-K Approximation Bottom Layer     |    |

| 44 | TPS7B82-Q1 (TO-252) Thermally Enhanced Top Layer                | 22 |

| 45 | TPS7B82-Q1 (TO-252) Thermally Enhanced Internal Layer 1         | 22 |

| 46 | TPS7B82-Q1 (TO-252) Thermally Enhanced Internal Layer 2         | 22 |

| 47 | TPS7B82-Q1 (TO-252) Thermally Enhanced Bottom Layer             | 22 |

| 48 | TPS7B82-Q1 (TO-252) Thermally Saturated Top Layer               | 23 |

| 49 | TPS7B82-Q1 (TO-252) Thermally Saturated Internal Layer 1        | 23 |

| 50 | TPS7B82-Q1 (TO-252) Thermally Saturated Internal Layer 2        | 23 |

| 51 | TPS7B82-Q1 (TO-252) Thermally Saturated Bottom Layer            | 23 |

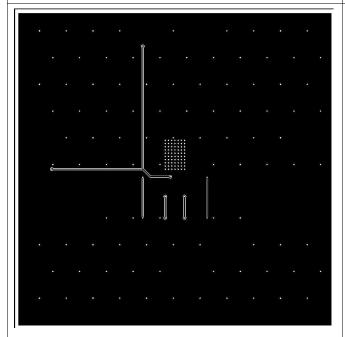

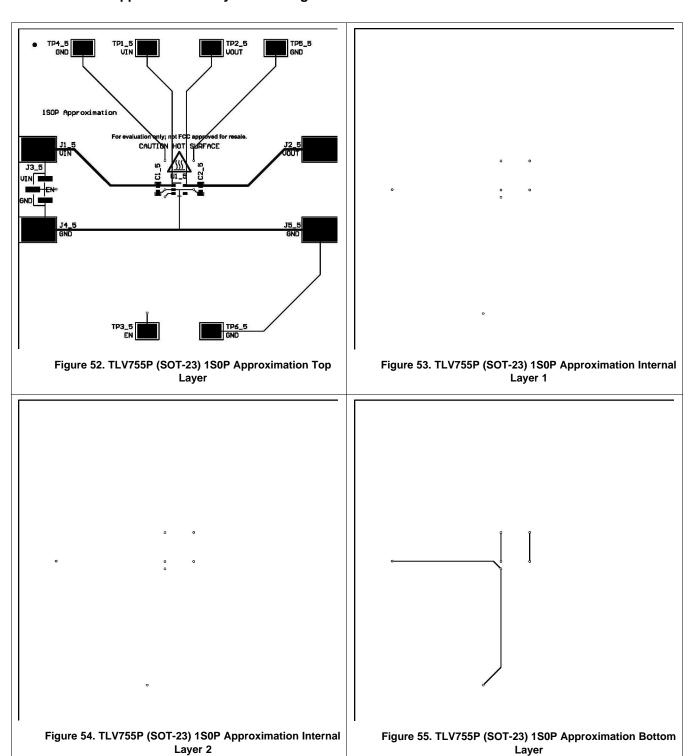

| 52 | TLV755P (SOT-23) 1S0P Approximation Top Layer                   | 24 |

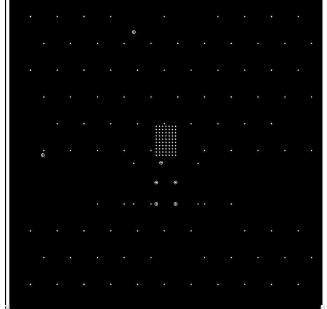

| 53 | TLV755P (SOT-23) 1S0P Approximation Internal Layer 1            |    |

| 54 | TLV755P (SOT-23) 1S0P Approximation Internal Layer 2            |    |

| 55 | TLV755P (SOT-23) 1S0P Approximation Bottom Layer                |    |

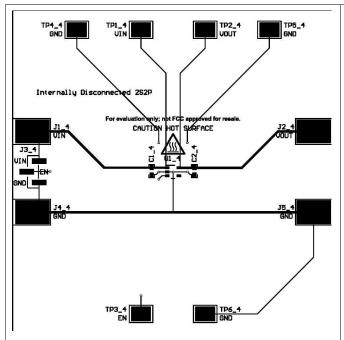

| 56 | TLV755P (SOT-23) Internally Disconnected Top Layer              |    |

| 57 | TLV755P (SOT-23) Internally Disconnected Internal Layer 1       |    |

| 58 | TLV755P (SOT-23) Internally Disconnected Internal Layer 2       |    |

| 59 | TLV755P (SOT-23) Internally Disconnected Bottom Layer.          |    |

| 60 | TLV755P (SOT-23) Internally Disconnected Bottom Layer           |    |

|    |                                                                 |    |

| 61 | TLV755P (SOT-23) JEDEC High-K Approximation Internal Layer 1    |    |

| 62 | TLV755P (SOT-23) JEDEC High-K Approximation Internal Layer 2    |    |

| 63 | TLV755P (SOT-23) JEDEC High-K Approximation Bottom Layer        |    |

| 64 | TLV755P (SOT-23) Thermally Enhanced Top Layer                   |    |

| 65 | TLV755P (SOT-23) Thermally Enhanced Internal Layer 1            |    |

| 66 | TLV755P (SOT-23) Thermally Enhanced Internal Layer 2            |    |

| 67 | TLV755P (SOT-23) Thermally Enhanced Bottom Layer                | 27 |

| www.ti.com | Introduct                                             | tior |

|------------|-------------------------------------------------------|------|

| 68         | TLV755P (SOT-23) Thermally Saturated Top Layer        | 28   |

| 69         | TLV755P (SOT-23) Thermally Saturated Internal Layer 1 | 28   |

| 70         | TLV755P (SOT-23) Thermally Saturated Internal Layer 2 | 28   |

| 71         | TLV755P (SOT-23) Thermally Saturated Bottom Layer     | 28   |

|            | List of Tables                                        |      |

| 1          | Layout Identifiers and Descriptions                   |      |

| 2          | Maximum Ambient Temperature vs. Power Dissipation     | 29   |

|            |                                                       |      |

#### **Trademarks**

All trademarks are the property of their respective owners.

#### 1 Introduction

LDOs are the most common DC/DC converter in electronic power designs due to their relative simplicity and cost advantage. As applications become increasingly integrated and compact, power designs must become smaller and cheaper, resulting in more LDO content. As a result, thermal performance is an even more important system design factor as LDOs are linear converters and inherently power dissipative. While JEDEC has standardized the method to measure and report semiconductor thermal metrics in a uniform manner, the standard is not fully optimized for thermal performance. One of the most significant factors that affects thermal performance falls on the system designer, PCB layout. The goal of this application report is to aid these designers by investigating the effect of PCB layout on the thermal performance of LDOs. Although the LDOs thermal performance in small SMD packages application report and the AN-1520 a guide to board layout for best thermal resistance for exposed packages application report previously discussed this topic, this study aims to be more applicable by collecting data in a functional setting. This setting includes functional PCB layouts with passive components that emulate TI Evaluation Modules (EVMs), and thermal measurements taken through active powering. Active powering refers to placing the LDO in a normal operation and varying the input voltage and the load current to increase the power dissipation and generate heat at the junction of the device.

The most popular metric for evaluating semiconductor thermal performance is the junction-to-ambient thermal resistance,  $\theta_{JA}$ . Equation 1 shows that this parameter is defined as the difference between the operating temperature and junction temperature of a device per watt of power dissipated in the device:

$$\theta_{JA} = \frac{T_J - T_A}{P_D} \tag{1}$$

A design with a smaller  $\theta_{JA}$  has a lower junction temperature for a given level of power dissipation, improving longevity and reliability. Semiconductor and IC package thermal metrics application report explains that the two factors that have a large impact on  $\theta_{JA}$  are the PCB layout and IC package. Three LDOs in common packages, the TPS745 (WSON package), TPS7B82-Q1 (TO-252 package), and TLV755P (SOT-23 package) are tested with five different PCB layouts and are chosen to investigate how much these two factors affect thermal performance.

The dependence of semiconductor thermal performance on additional external factors including air flow, altitude, and ambient temperature has resulted in the need for JEDEC to standardize measurement procedures and test boards for  $\theta_{JA}$  and other thermal metrics. For this application report, approximations of the Low Effective Thermal Conductivity Test Board, described in

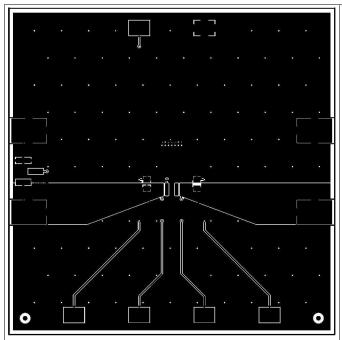

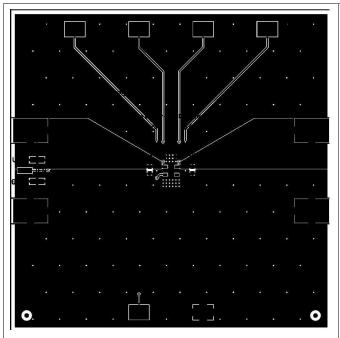

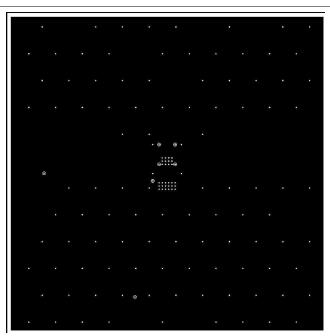

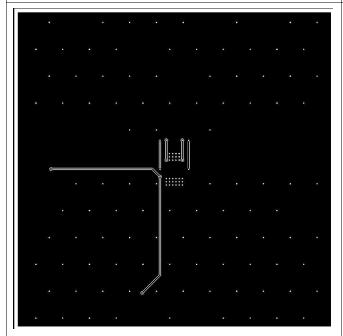

https://www.jedec.org/system/files/docs/JESD51-3.PDF, and the High Effective Thermal Conductivity Test Board, described in https://www.jedec.org/system/files/docs/jesd51-7.PDF, are designed for each package along with three custom layouts. The area and layer stack of each board follow the JEDEC standard test board approximations: 4layer PCBs with an area of 9-in² (3-in by 3-in). The outer layers contain two ounce copper thickness while the inner layers contain one ounce copper thickness. The five layouts fabricated for each package contain increasing amounts of copper connected to the device with the intent to measure  $\theta_{JA}$  and show an inverse relationship versus copper coverage. To improve the consistency of the results across the three packages, the amount of copper used for heat sinking in each type of layout is kept equal. In order of least to greatest copper content, the layout types are referred to as:

- 1S0P Approximation

- · Internally Disconnected

Introduction www.ti.com

- JEDEC High-K Approximation

- Thermally Enhanced

- · Thermally Saturated

Thermal vias are also included in the thermal landing pad for all WSON and TO-252 layouts according to the JEDEC standard specified in <a href="https://www.jedec.org/system/files/docs/JESD51-9.pdf">https://www.jedec.org/system/files/docs/JESD51-9.pdf</a>. These vias have a 20 millimeter (mm) diameter, 10-mm hole size, and 17-µm copper plating.

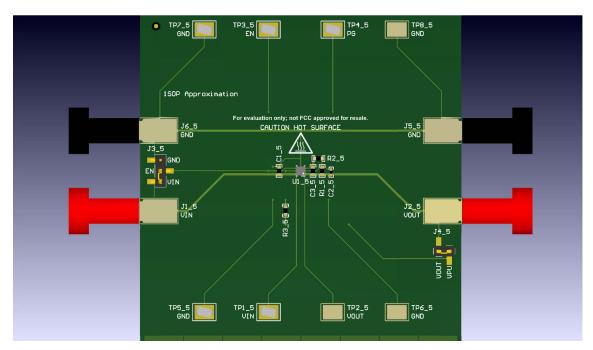

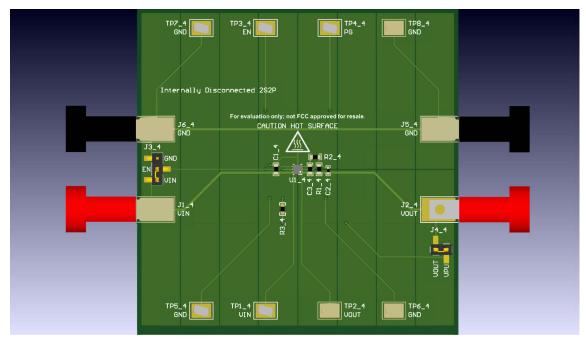

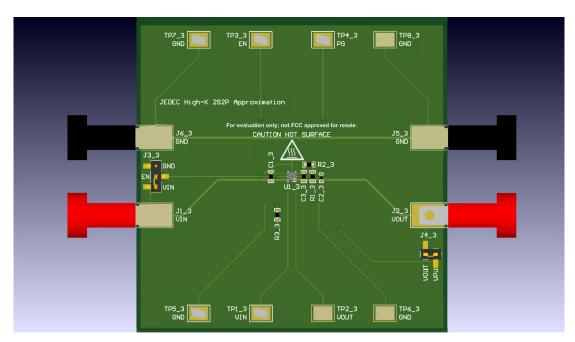

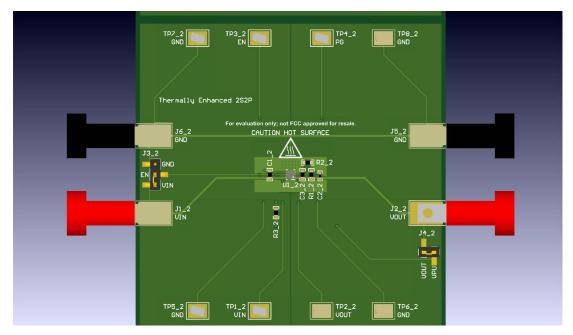

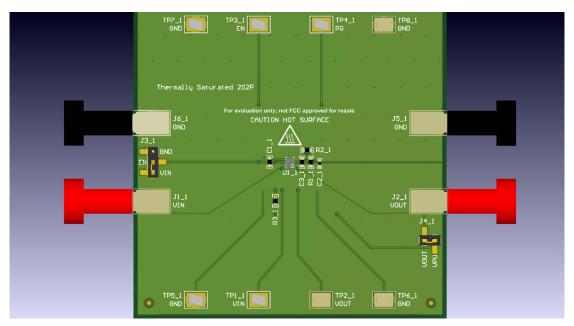

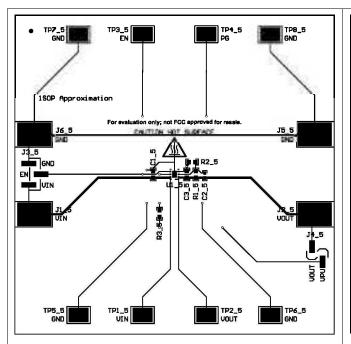

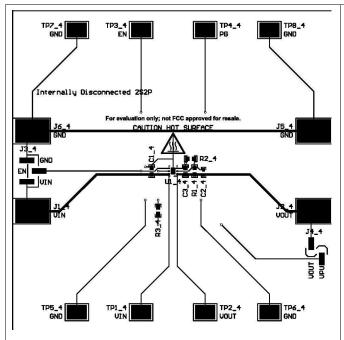

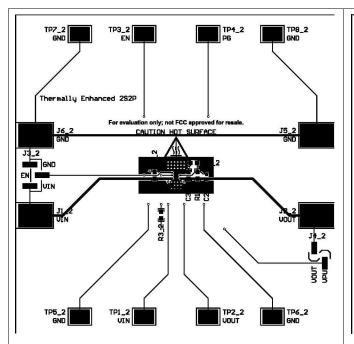

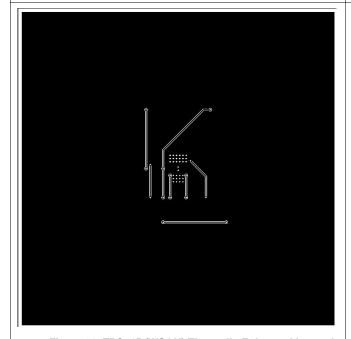

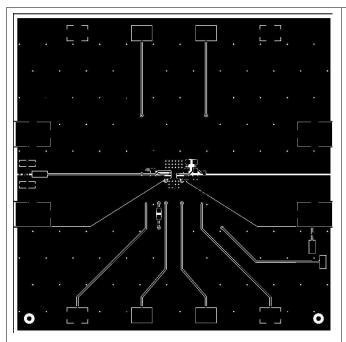

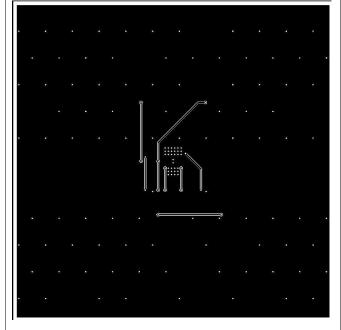

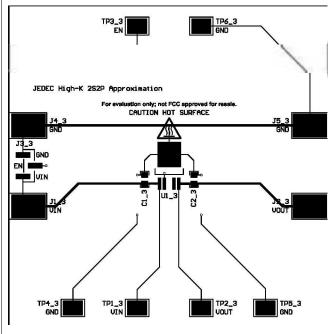

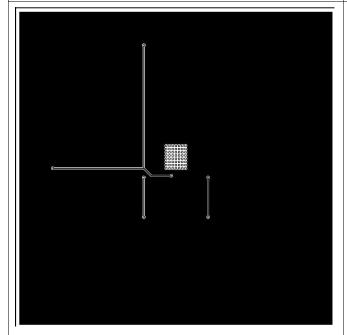

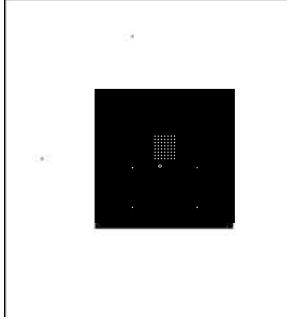

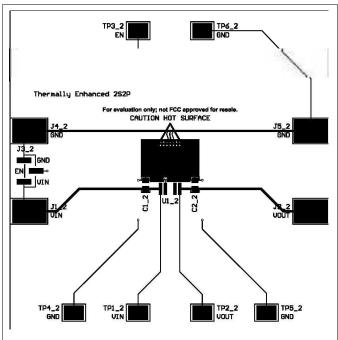

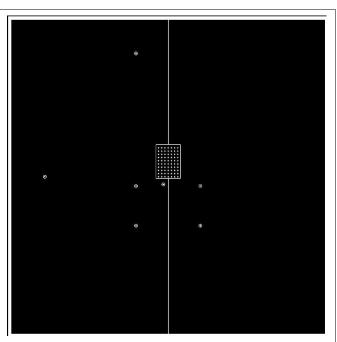

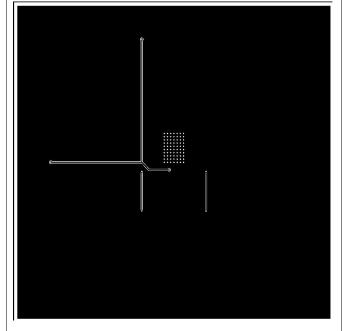

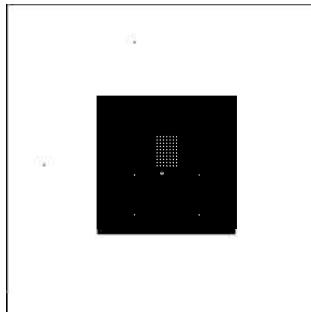

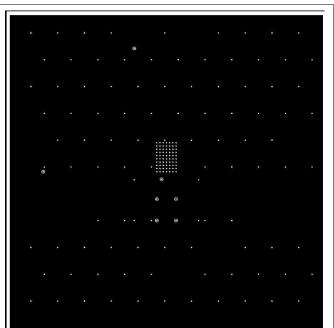

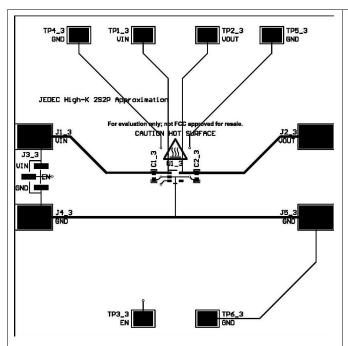

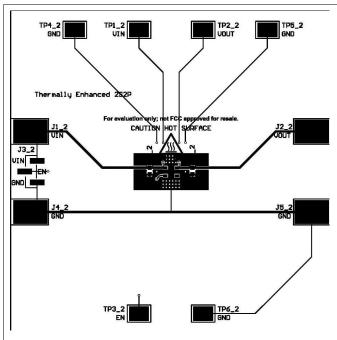

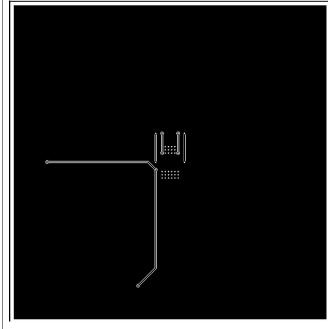

Two different  $\theta_{JA}$  values are used as benchmarks for comparison. The first is  $\theta_{JA,\ datasheet}$  as specified in the Thermal Information table in the datasheet of each device as  $R_{\theta JA}$ .  $\theta_{JA,\ datasheet}$  is derived using a thermal model of the JEDEC High-K Thermal Test Board and is the most popular metric used by designers to evaluate thermal performance. The second value is  $\theta_{JA,1S0P}$ , as measured with the 1S0P Approximation layout. This value provides an example of the expected thermal performance for a worst-case layout. Figure 1 through Figure 5 show 3D generated images for each of the layouts designed for the TPS745 in the WSON package. Drawings of all four layers for each layout can be found in Appendix A. Table 1 provides descriptions for each design layout and copper coverage.

**Table 1. Layout Identifiers and Descriptions**

| BOARD                         | ATTRIBUTE               | DESCRIPTION                                   | CONNECTED<br>COPPER<br>AREA(in²) | DISCONNECTED<br>COPPER<br>AREA(in²) |  |

|-------------------------------|-------------------------|-----------------------------------------------|----------------------------------|-------------------------------------|--|

|                               | Top Layer               | Traces only                                   |                                  | None                                |  |

|                               | Internal Layer 1        | No copper                                     |                                  |                                     |  |

| 1S0P<br>Approximation         | Internal Layer 2        | No copper                                     | None                             |                                     |  |

| ripproximation                | Bottom Layer            | Traces only                                   |                                  |                                     |  |

|                               | Additional Thermal Vias | None                                          |                                  |                                     |  |

|                               | Top Layer               | Traces only                                   |                                  |                                     |  |

|                               | Internal Layer 1        | Medium, unconnected, discontinuous planes (1) |                                  |                                     |  |

| Internally<br>Disconnected    | Internal Layer 2        | Medium, unconnected, discontinuous planes (1) | 0.07                             | 16.8                                |  |

| Biocomiocica                  | Bottom Layer            | Traces and one small ground plane             |                                  |                                     |  |

|                               | Additional Thermal Vias | None                                          |                                  |                                     |  |

|                               | Top Layer               | Traces only                                   |                                  | 8.53                                |  |

|                               | Internal Layer 1        | One large ground plane                        |                                  |                                     |  |

| JEDEC High-K<br>Approximation | Internal Layer 2        | Traces and one large, unconnected plane       | 10.2                             |                                     |  |

| приомпанон                    | Bottom Layer            | One medium ground plane                       |                                  |                                     |  |

|                               | Additional Thermal Vias | None                                          |                                  |                                     |  |

|                               | Top Layer               | Traces and one small ground plane             |                                  |                                     |  |

| Thermally                     | Internal Layer 1        | Small ground plane and two unconnected planes |                                  | 8.43                                |  |

| Enhanced                      | Internal Layer 2        | Traces and one medium ground plane            | 10.5                             |                                     |  |

|                               | Bottom Layer            | One medium ground plane                       |                                  |                                     |  |

|                               | Additional Thermal Vias | Only around the device                        |                                  |                                     |  |

|                               | Top Layer               | Large ground and power planes                 |                                  |                                     |  |

|                               | Internal Layer 1        | One large ground plane                        |                                  | None                                |  |

| Thermally<br>Saturated        | Internal Layer 2        | Traces and one large ground plane             | 34.1                             |                                     |  |

|                               | Bottom Layer            | One large ground plane                        |                                  |                                     |  |

|                               | Additional Thermal Vias |                                               |                                  |                                     |  |

<sup>&</sup>lt;sup>(1)</sup> Intended to represent high density applications without a dedicated ground plane.

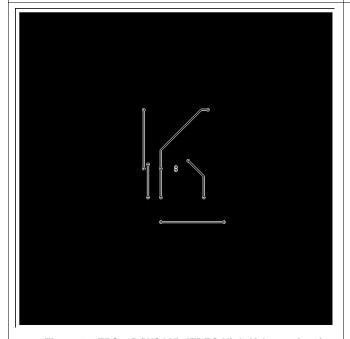

www.ti.com Introduction

Figure 1. TPS745 (WSON) 1S0P Approximation Layout

Figure 2. TPS745 (WSON) Internally Disconnected Layout

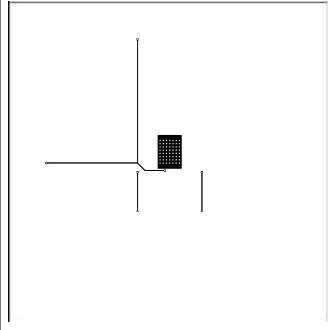

Introduction www.ti.com

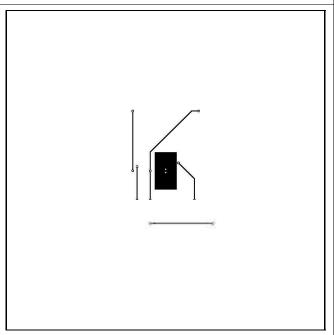

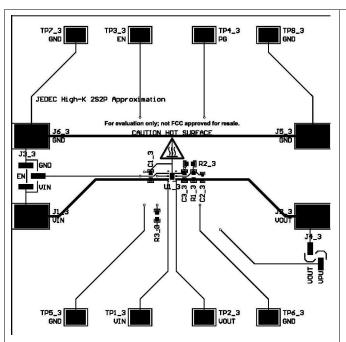

Figure 3. TPS745 (WSON) JEDEC High-K Approximation Layout

Figure 4. TPS745 (WSON) Thermally Enhanced Layout

www.ti.com Procedure

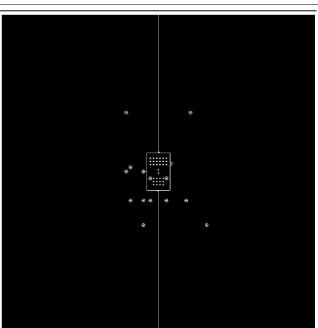

Figure 5. TPS745 (WSON) Thermally Saturated Layout

#### 2 Procedure

Most modern LDOs include a thermal shutdown feature to protect the device from excessive damage at high junction temperatures. For a given level of power dissipation, an LDO with thermal shutdown has a maximum ambient temperature it can operate at before thermal shutdown is triggered and the device shuts off. Equation 2 shows the substitution of the thermal shutdown temperature for the junction temperature and the rearrangement of Equation 1:

$$T_{A,max} = T_{SD} - \theta_{JA} \times P_{D}$$

(2)

The *Measuring the thermal impedance of LDOs in Situ application report* explains how this equation provides a way to determine  $\theta_{JA}$  without needing direct access to the junction of the device. First, a small amount of power dissipation is chosen so that the maximum operating ambient temperature is essentially the thermal shutdown temperature of the LDO. A hot oven is used to set the ambient temperature and the LDO is allowed to soak for five minutes. The hot oven must then be turned off to stop any airflow as JEDEC standard models assume no forced convection. An oscilloscope is then used to monitor whether the LDO is shutting off the output. This behavior indicates that thermal shutdown has been triggered. If the LDO does not enter thermal shutdown, the ambient temperature is increased, and the procedure is repeated to determine the maximum operating ambient temperature. This procedure is repeated for increasing levels of power dissipation to provide a sufficient linear regression when calculating  $\theta_{JA}$  by using Equation 2.

There are some limitations to the accuracy of this procedure as the ambient temperature and power dissipation are susceptible to change while making the measurement. Turning the hot oven off to ensure natural convection causes the ambient temperature to gradually decrease. Removing any cooling due to the convection created by the hot oven simultaneously increases the junction temperature of the device. Due to the bandgap of the LDO reference drift over temperature, the output voltage decreases, increasing the power dissipated in the pass transistor. The accuracy of the measured  $\theta_{JA}$  is also reduced by the measurement accuracy of the hot oven, which is typically  $\pm 2^{\circ}C$ . To address these limitations, a wide range of power dissipation levels must be chosen to illustrate a wide maximum ambient temperature range. Equation 2 shows that  $\theta_{JA}$  is defined as the slope of the trendline between these two variables. As such, verifying that linearity is maintained across a wide range of temperatures and power dissipation increases the credibility of the  $\theta_{JA}$  measurement.

Test Results and Discussion www.ti.com

The major advantage of this procedure lies in its relative simplicity. It can be used to measure  $\theta_{JA}$  on any board since it does not require modifications to the PCB or LDO to measure the specific board or junction temperature, allowing for a more functional PCB layout and testing environment that is more applicable to system designers at the slight expense of accuracy. Because the goal of this application report is to aid designers by investigating general trends between PCB layout and thermal performance across multiple packages, the creation of a functional test setup is prioritized.

#### 3 Test Results and Discussion

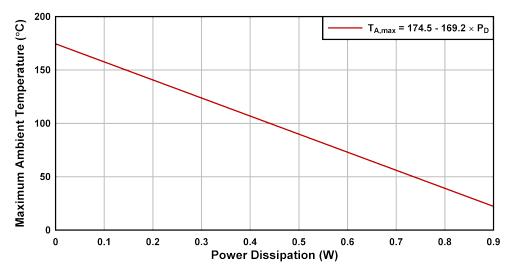

Figure 6 shows the maximum ambient temperature versus power dissipation for the TPS745 (WSON package) in the 1S0P Approximation layout. The slope of the trendline indicates a  $\theta_{JA}$  of 169.2 C/W. The range and linearity of the data collected support the expected relationship between the power dissipation of the LDO and the maximum operating ambient temperature described by Equation 2.

Figure 6. TPS745 (WSON) 1S0P Approximation Layout Test Results

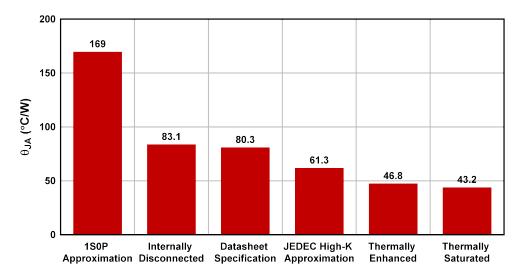

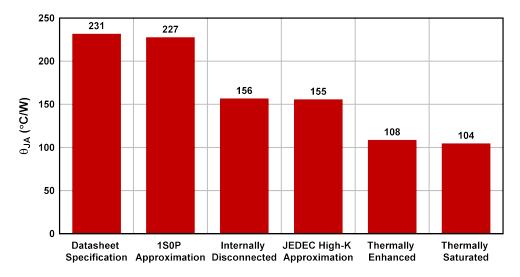

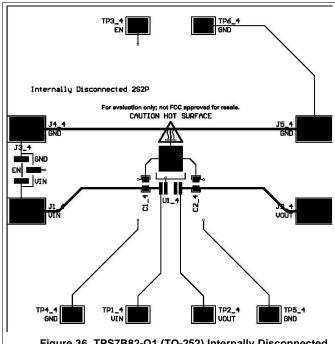

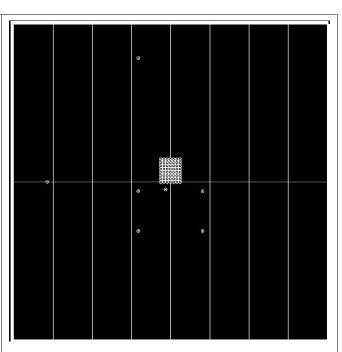

See Appendix B for similar data is collected for all packages and layouts. Figure 7 and Figure 8 provide the resulting  $\theta_{JA}$  values for the TPS745 (WSON) and TPS7B82-Q1 (TO-252). These packages display similar trends in thermal performance across all five layouts. The Internally Disconnected layout reduces  $\theta_{JA}$  by almost 50% despite only having a connected copper area of 0.07-in², showing that including copper on the internal layers can significantly improve thermal performance, even if this copper is not directly connected to the LDO. The remaining layouts with increasing copper and thermal vias content show further, smaller reductions of  $\theta_{JA}$  until the maximum reduction is reached at slightly larger than 70%. Based on the data collected, a thermally efficient layout is crucial for the WSON and TO-252 packages. If the layout is inefficient,  $\theta_{JA}$  is significantly larger than the datasheet specified value, resulting in more complex thermal performance calculations, a reduced maximum operating ambient temperature, and potentially degraded device longevity and reliability.

Figure 7. TPS745 (WSON)  $\theta_{JA}$  vs. Board Layout

Figure 8. TPS7B82-Q1 (TO-252)  $\theta_{JA}$  vs. Board Layout

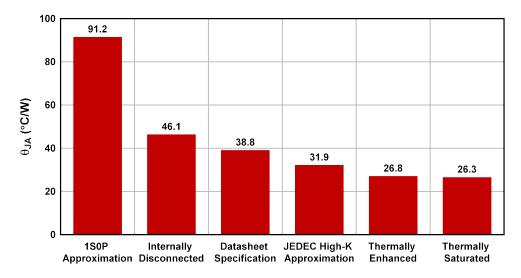

Figure 9 shows the measured  $\theta_{JA}$  values for the TLV755P (SOT-23). The difference in the  $\theta_{JA}$  trend for the SOT-23 package is due to the lack of a thermal pad. The JEDEC standard does not permit the addition of thermal vias on the High-K Thermal Test Board for packages without thermal pads. A small amount of heat is able to dissipate to the internal and bottom layers, resulting in very similar performance between the 1S0P Approximation and the thermal model of the JEDEC High-K Test Board from which the datasheet specification is derived. To prevent identical performance across multiple different layouts, one thermal via is included underneath the device on the Internally Disconnected layout to connect the top layer ground trace to the bottom ground plane. In comparison, the JEDEC High-K Approximation layout has similar performance with two vias connecting the top ground trace to the internal layers. Adding one more via does not provide enough heat transferring capability to warrant much improvement in  $\theta_{JA}$  despite the additional copper present in the JEDEC High-K Approximation layout.

Test Results and Discussion www.ti.com

The Thermally Enhanced and Thermally Saturated boards displayed about a 33% reduction to  $\theta_{\text{JA}}$  compared to the JEDEC High-K Approximation board, significantly larger than the same comparison for the TPS745 and TPS7B82-Q1. This is explained by the lack of a thermal pad in the SOT-23 package. The Thermally Enhanced and Thermally Saturated layouts are the only layouts that include copper planes on the top layer. The lack of a thermal pad in this package results in the majority of heat dissipating on the top layer. As such, the inclusion of top layer copper is much more effective. Furthermore, the additional thermal vias included in the Thermally Enhanced and Thermally Saturated packages are the only path for heat to spread to the internal and bottom layers. In contrast, the TPS745 and TPS7B82-Q1 layouts include thermal vias directly under the thermal pad, reducing the effectiveness of additional thermal vias.

Figure 9. TLV755P (SOT-23)  $\theta_{JA}$  vs. Board Layout

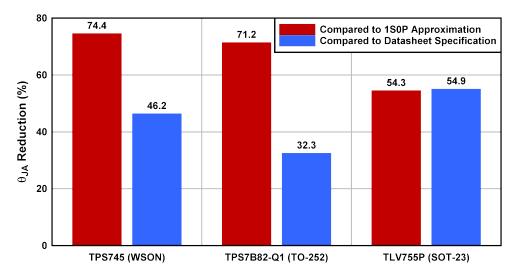

Figure 10 compares the effectiveness of PCB layout versus the package type. The effectiveness is calculated as a percentage reduction of  $\theta_{JA}$ . As calculated with Equation 3, a thermally efficient layout is capable of reducing the  $\theta_{JA}$  specified in the datasheet by between 32% and 55% depending on the package. The datasheet specified  $\theta_{JA}$  can be used to provide a conservative estimate of the rise in junction temperature of the LDO. However, referring to Equation 2, the empirical rise in junction temperature can be reduced by 32% to 55% with a thermally efficient layout. Accounting for this improvement allows for a higher operating ambient temperature, a higher level of power dissipation, or some combination of the two. A comparison to the 1S0P Approximation layout using Equation 4 illustrates the importance of a thermally efficient layout. Compared to this worst-case layout, a thermally efficient layout provides a measured  $\theta_{JA}$  that is up to four times smaller.

Reduction of

$$\theta_{JA}$$

compared to Datasheet Specification =  $\left(1 - \frac{\theta_{JA,saturated}}{\theta_{JA,datasheet}}\right) \times 100$  (3)

Reduction of

$$\theta_{JA}$$

compared to 1S0P Approximation =  $\left(1 - \frac{\theta_{JA,saturated}}{\theta_{JA,1S0P}}\right) \times 100$  (4)

Figure 10.  $\theta_{JA}$  Reduction for Each Device

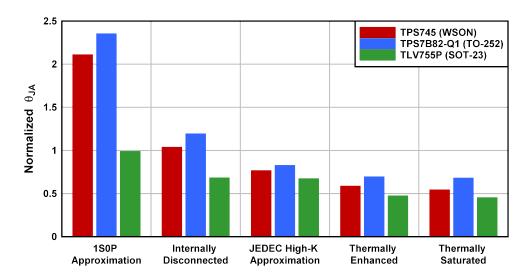

Figure 11 normalizes the results from the Figure 7, Figure 8, and Figure 9 relative to the datasheet specification using Equation 5.

$$\theta_{\text{JA,normalized}} = \frac{\theta_{\text{JA,measured}}}{\theta_{\text{JA,datasheet}}}$$

(5)

This figure condenses the data collected across the three packages to illustrate the important findings of this study. Firstly, there is an inverse relationship between PCB copper content and  $\theta_{\text{JA}}$  that saturates as the copper content increases. This relationship is observable regardless of package. As shown by the significant drop between the 1S0P Approximation and Internally Disconnected layouts, the copper content does not need to be connected to the LDO to improve thermal performance. Additional thermal vias around the device also improve thermal performance by providing more paths for the heat generated by the LDO to dissipate to the internal and bottom layers. These vias are especially important for packages like the SOT-23 that do not have a dedicated thermal pad. However, as shown by the minimal improvement between the Thermally Enhanced and Thermally Saturated layouts, the improvement in  $\theta_{\text{JA}}$  from the additional thermal vias saturates.

Figure 11. Normalized  $\theta_{\text{JA}}$  for Each Device vs. Board Layout

Conclusion www.ti.com

#### 4 Conclusion

The thermal performance of the LDO in terms of its junction-to-ambient thermal resistance,  $\theta_{JA}$ , is highly dependent on the PCB design. However, the impact of the PCB is ultimately limited by the package of the LDO. Packages with thermal pads, like the WSON and TO-252 packages, are more thermally dissipative and, therefore, see a larger overall reduction in  $\theta_{JA}$  at 74% and 71% respectively when compared to the worst-case 1S0P approximation layout. The SOT-23 package sees a smaller, but still significant, reduction at 54%. Figure 10 illustrates that  $\theta_{JA}$  can be reduced between 32% and 55% with a thermally optimized layout compared to the data sheet specifications. This result indicates that using the datasheet specified  $\theta_{JA}$  for thermal calculations provides a conservative estimate of thermal performance. However, a designer must keep in mind that a thermally efficient layout allows for a higher operating ambient temperature, a higher level of power dissipation, or some combination of these two advantages.

Figure 11 shows that regardless of package type, thermal performance saturates as copper content in the PCB increases. For all three packages, The Thermally Enhanced layout contained about half the copper area of the Thermally Saturated layout, but provided a  $\theta_{JA}$  within 8%. Similarly, the improvement in thermal performance due to additional thermal vias also saturates. Stitching additional vias through the PCB yields little benefit as seen from the Thermally Saturated layouts. A design with sufficient thermal performance can be achieved with a layout similar to the Thermally Enhanced board. For more compact designs, see Figure 9, which show the results from the TLV755P (SOT-23) measurements. These results indicate that copper must be maximized on the top and bottom layers as these layers are not surrounded by additional PCB material and are therefore the most effective for heat dissipation. Additional thermal vias only need to be included around the device to effectively spread the heat generated by the LDO to other copper layers. These vias are especially critical when designing with packages that do not have a thermal pad, like the SOT-23 package. In these cases, thermal vias can also be placed directly under the device where the most heat is generated. Packages with thermal pads maximize the amount of thermal vias in the landing pad according to https://www.jedec.org/system/files/docs/JESD51-9.pdf. Lastly, data from all Internally Disconnected layouts Figure 11 show that additional copper on internal layers must be included if possible and have a positive impact on thermal performance, even if not directly connected to the LDO.

#### 5 Future Study

There are a couple of areas that can be addressed in a future study. The first is to investigate these or similar layouts' effect on ultra small (less than 1 mm²) packages like the DSBGA and X2SON that traditionally have poor thermal performance. Due to poor heat dissipative capability inherent to small packages, the PCB layout can have a reduced effect on the thermal performance compared to the WSON, TO-252, and SOT-23 packages. Another more complex extension of this study can develop an equation or Figure of Merit (FOM) that incorporates connected copper area, disconnected copper area, the location of these areas relative to the board stack up, number of thermal vias, and so forth. This FOM, which would correlate to an equivalent thermal impedance of the board, can be applied to provide a more targeted value for the expected  $\theta_{1A}$  of a given layout.

#### 6 References

- 1. LDOs thermal performance in small SMD packages application report

- 2. AN-1520 a guide to board layout for best thermal resistance for exposed packages application report

- 3. Semiconductor and IC package thermal metrics

- 4. Low effective thermal conductivity test board for leaded surface mount packages

- 5. High effective thermal conductivity test board for leaded surface mount packages

- 6. Test boards for area array surface mount package thermal measurements

- 7. Measuring the thermal impedance of LDOs in Situ application report

## Thermal Test Board Layouts

### A.1 TPS745 (WSON) Drawings

#### A.1.1 1S0P Approximation Layout Drawings

Figure 12. TPS745 (WSON) 1S0P Approximation Top Layer

Figure 13. TPS745 (WSON) 1S0P Approximation Internal Layer 1

Figure 14. TPS745 (WSON) 1S0P Approximation Internal Layer 2

Figure 15. TPS745 (WSON) 1S0P Approximation Bottom Layer

#### A.1.2 Internally Disconnected Layout Drawings

Figure 16. TPS745 (WSON) Internally Disconnected Top Layer

Figure 17. TPS745 (WSON) Internally Disconnected Internal Layer 1

Figure 18. TPS745 (WSON) Internally Disconnected Internal Layer 2

Figure 19. TPS745 (WSON) Internally Disconnected Bottom Layer

#### A.1.3 JEDEC High-K Approximation Layout Drawings

Figure 20. TPS745 (WSON) JEDEC High-K Approximation Top Layer

Figure 21. TPS745 (WSON) JEDEC High-K Approximation Internal Layer 1

Figure 22. TPS745 (WSON) JEDEC High-K Approximation Internal Layer 2

Figure 23. TPS745 (WSON) JEDEC High-K Approximation Bottom Layer

#### A.1.4 Thermally Enhanced Layout Drawings

Figure 24. TPS745 (WSON) Thermally Enhanced Top Layer

Figure 25. TPS745 (WSON) Thermally Enhanced Internal Layer 1

Figure 26. TPS745 (WSON) Thermally Enhanced Internal Layer 2

Figure 27. TPS745 (WSON) Thermally Enhanced Bottom Layer

#### A.1.5 Thermally Saturated Layout Drawings

Figure 28. TPS745 (WSON) Thermally Saturated Top Layer

Figure 29. TPS745 (WSON) Thermally Saturated Internal Layer 1

Figure 30. TPS745 (WSON) Thermally Saturated Internal Layer 2

Figure 31. TPS745 (WSON) Thermally Saturated Bottom Layer

#### A.2 TPS7B82-Q1 (TO-252) Drawings

#### A.2.1 1S0P Approximation Layout Drawings

#### A.2.2 Internally Disconnected Layout Drawings

Figure 36. TPS7B82-Q1 (TO-252) Internally Disconnected Top Layer

Figure 37. TPS7B82-Q1 (TO-252) Internally Disconnected Internal Layer 1

Figure 38. TPS7B82-Q1 (TO-252) Internally Disconnected Internal Layer 2

Figure 39. TPS7B82-Q1 (TO-252) Internally Disconnected Bottom Layer

#### A.2.3 JEDEC High-K Approximation Layout Drawings

Figure 40. TPS7B82-Q1 (TO-252) JEDEC High-K Approximation Top Layer

Figure 41. TPS7B82-Q1 (TO-252) JEDEC High-K Approximation Internal Layer 1

Figure 42. TPS7B82-Q1 (TO-252) JEDEC High-K Approximation Internal Layer 2

Figure 43. TPS7B82-Q1 (TO-252) JEDEC High-K Approximation Bottom Layer

21

#### A.2.4 Thermally Enhanced Layout Drawings

Figure 44. TPS7B82-Q1 (TO-252) Thermally Enhanced Top Layer

Figure 45. TPS7B82-Q1 (TO-252) Thermally Enhanced Internal Layer 1

Figure 46. TPS7B82-Q1 (TO-252) Thermally Enhanced Internal Layer 2

Figure 47. TPS7B82-Q1 (TO-252) Thermally Enhanced Bottom Layer

#### A.2.5 Thermally Saturated Layout Drawings

Figure 48. TPS7B82-Q1 (TO-252) Thermally Saturated Top Layer

Figure 49. TPS7B82-Q1 (TO-252) Thermally Saturated Internal Layer 1

Figure 50. TPS7B82-Q1 (TO-252) Thermally Saturated Internal Layer 2

Figure 51. TPS7B82-Q1 (TO-252) Thermally Saturated Bottom Layer

#### A.3 TLV755P (SOT-23) Drawings

#### A.3.1 1S0P Approximation Layout Drawings

#### A.3.2 Internally Disconnected Layout Drawings

Figure 56. TLV755P (SOT-23) Internally Disconnected Top Layer

Figure 57. TLV755P (SOT-23) Internally Disconnected Internal Layer 1

Figure 58. TLV755P (SOT-23) Internally Disconnected Internal Layer 2

Figure 59. TLV755P (SOT-23) Internally Disconnected Bottom Layer

#### A.3.3 JEDEC High-K Approximation Layout Drawings

Figure 60. TLV755P (SOT-23) JEDEC High-K Approximation Top Layer

Figure 61. TLV755P (SOT-23) JEDEC High-K Approximation Internal Layer 1

Figure 62. TLV755P (SOT-23) JEDEC High-K Approximation Internal Layer 2

Figure 63. TLV755P (SOT-23) JEDEC High-K Approximation Bottom Layer

#### A.3.4 Thermally Enhanced Drawings

Figure 64. TLV755P (SOT-23) Thermally Enhanced Top Layer

Figure 65. TLV755P (SOT-23) Thermally Enhanced Internal Layer 1

Figure 66. TLV755P (SOT-23) Thermally Enhanced Internal Layer 2

Figure 67. TLV755P (SOT-23) Thermally Enhanced Bottom Layer

#### A.3.5 Thermally Saturated Layout Drawings

Figure 68. TLV755P (SOT-23) Thermally Saturated Top Layer

Figure 69. TLV755P (SOT-23) Thermally Saturated Internal Layer 1

Figure 70. TLV755P (SOT-23) Thermally Saturated Internal Layer 2

Figure 71. TLV755P (SOT-23) Thermally Saturated Bottom Layer

## Thermal Test Results

#### **B.1** Thermal Performance Data

**Table 2. Maximum Ambient Temperature vs. Power Dissipation**

|                            | TPS745 (WSON)      |                         | TPS7B82-Q1 (TO-252) |                         | TLV755P (SOT-23)   |                         |

|----------------------------|--------------------|-------------------------|---------------------|-------------------------|--------------------|-------------------------|

| Board                      | P <sub>D</sub> (W) | T <sub>A,max</sub> (°C) | P <sub>D</sub> (W)  | T <sub>A,max</sub> (°C) | P <sub>D</sub> (W) | T <sub>A,max</sub> (°C) |

|                            | 0.00               | 175                     | 0.00                | 182                     | 0.00               | 165                     |

| 1COD Approximation         | 0.26               | 130                     | 0.51                | 135                     | 0.20               | 124                     |

| 1S0P Approximation         | 0.51               | 88                      | 1.00                | 90                      | 0.39               | 80                      |

|                            | 0.90               | 23                      | 1.70                | 27                      | 0.62               | 24                      |

|                            | 0.00               | 178                     | 0.00                | 178                     | 0.00               | 164                     |

| Internally Disconnected    | 0.59               | 129                     | 1.00                | 134                     | 0.25               | 126                     |

|                            | 1.14               | 83                      | 1.95                | 88                      | 0.49               | 88                      |

|                            | 0.00               | 178                     | 0.00                | 180                     | 0.00               | 163                     |

| JEDEC High-K Approximation | 0.74               | 130                     | 1.53                | 133                     | 0.27               | 122                     |

|                            | 1.49               | 87                      | 3.01                | 84                      | 0.53               | 81                      |

|                            | 0.00               | 179                     | 0.00                | 178                     | 0.00               | 166                     |

| Thermally Enhanced         | 0.83               | 135                     | 1.77                | 129                     | 0.36               | 128                     |

|                            | 1.73               | 98                      | 3.51                | 84                      | 0.69               | 91                      |

|                            | 0.00               | 177                     | 0.00                | 177                     | 0.00               | 164                     |

| Thermally Saturated        | 0.84               | 139                     | 1.81                | 128                     | 0.38               | 127                     |

|                            | 1.64               | 106                     | 3.62                | 82                      | 0.76               | 85                      |

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated