# Optimizing High Side FET Voltage Ringing of Multiphase Voltage Regulators Part 1-Mechanism of High-Side FET Voltage Ringing

Leon Liang/Chasel Chen/Wilson Guo

### ABSTRACT

With the rapid growth demand of the server and communication market, high current CPU and ASIC are popular in server and communication system design. Multiphase power solutions are widely adopted for supplying CPU and AISC. However, to achieve high-power density, each power stage needs to deliver more energy to the load. In turn, the process of how to optimize the high-side FET voltage ringing becomes a challenge. This serial application report demonstrates the challenges of a low voltage ringing design.

#### Contents

| 1 | Introduction                                                             | . 2 |

|---|--------------------------------------------------------------------------|-----|

| 2 | Simulation Circuit Model                                                 | . 2 |

| 3 | Mechanism of High-Side FET Voltage Ring In Multiphase Voltage Regulators | . 4 |

| 4 | Conclusion                                                               | 10  |

| 5 | References                                                               | 10  |

### List of Figures

| 1  | The Top Layer Layout of the TPS53667EVM-769               | 2  |

|----|-----------------------------------------------------------|----|

| 2  | Equivalent Parasitic Parameter Circuit                    | 3  |

| 3  | VIN Part of Equivalent Circuit Model                      | 3  |

| 4  | Simulation Waveform of the High-side FET Voltage          | 4  |

| 5  | High-side FET Voltage Ringing Waveform on TPS53667EVM-769 | 4  |

| 6  | TDK 0402 Capacitor Impedance versus Frequency             | 5  |

| 7  | TDK Different Size Capacitor Impedance versus Frequency   |    |

| 8  | Simplified Circuit of VIN Part                            | 6  |

| 9  | Simulation Result of Current Distribution                 | 7  |

| 10 | Simulation Result of High-side FET Voltage and Bypass Cap | 7  |

| 11 | Voltage Stress Waveform with 3.3 nF                       | 8  |

| 12 | Voltage Stress Waveform with 1 µF                         | 8  |

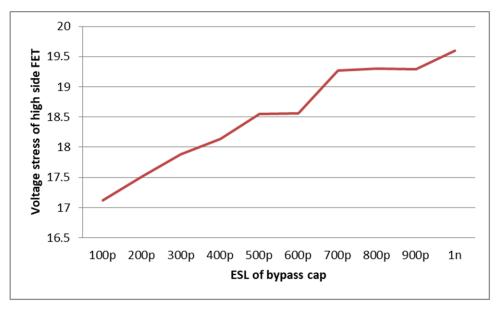

| 13 | Simulation Result About Bypass Cap ESL                    | 9  |

| 14 | Simulation Circuit of the Voltage Inside and Outside IC   | 9  |

| 15 | Simulation Result About the Voltage Test Point and FET    | 10 |

|    |                                                           |    |

#### List of Tables

2

### Trademarks

All trademarks are the property of their respective owners.

### 1 Introduction

In order to reduce the FET voltage ringing, system designers usually add an RC snubber between the switching node and ground, however, it only reduces the low-side FET voltage ringing. High-side FET voltage ringing still depends on parasitic parameters by input capacitors and PCB layout. With improper layout and selected input capacitors, excessive voltage ringing can be seen. This application report shows the voltage ringing mechanism of formation and discusses how to reduce the high-side voltage ringing in the design by appropriate input bypass capacitor selection and layout design to improve system reliability.

### 2 Simulation Circuit Model

In real design, Printed Circuit Board (PCB) trace and capacitors have inherent parasitic inductance (ESL) and FET has inherent parasitic capacitance (Coss). These factors generate voltage ringing while FET is turning on and off. In addition, larger output current leads to higher voltage ringing on the FET.

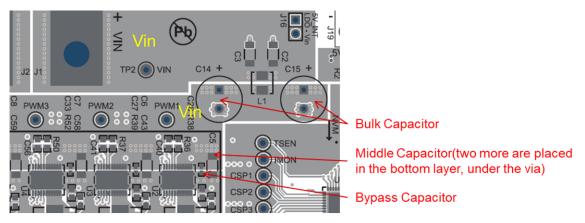

Figure 1 is the TI TPS53667 EVM PCB layout. The VIN filter capacitors can be divided into three categories:

- The bulk capacitor is placed in the far terminal of VIN. These bulk capacitors are usually electrolytic capacitors of hundreds of μF. The bulk capacitor is used to store energy.

- The middle capacitor is placed midway from the bulk capacitor to the IC VIN pin.

- The bypass capacitor is placed as close as possible to the IC VIN pin. Since the space near VIN pin is

narrow, the bypass capacitor is under a small package like 0402. On the other hand, a smaller

package leads to a smaller cap ESL.

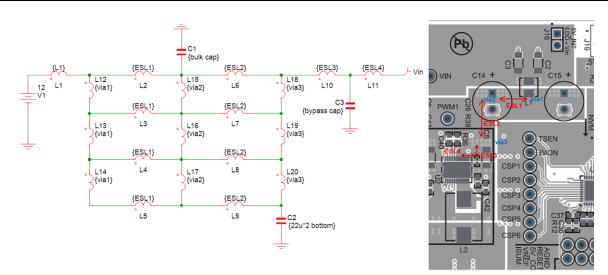

These three kinds of capacitors divide the VIN copper trace into three parts. Each part has a respective ESL because of PCB parasitic inductance, as shown in Figure 2.

Figure 1. The Top Layer Layout of the TPS53667EVM-769

Figure 2. Equivalent Parasitic Parameter Circuit

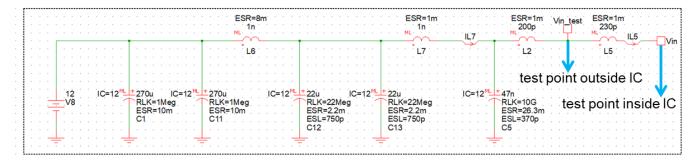

Figure 3. VIN Part of Equivalent Circuit Model

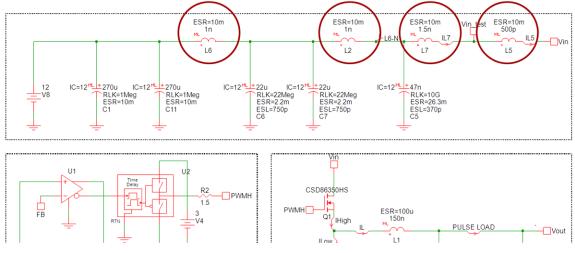

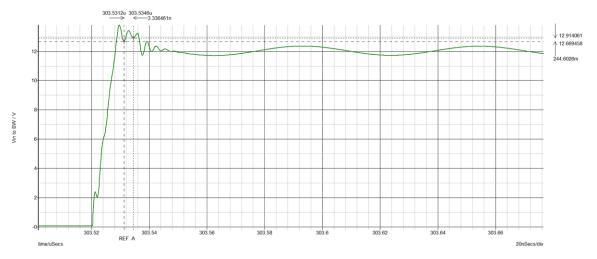

Using this model in Simplis, you can get the simulation waveform of the high-side FET voltage stress ringing in Figure 4.

www.ti.com

Figure 4. Simulation Waveform of the High-side FET Voltage

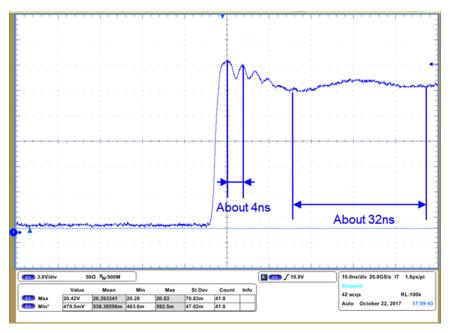

Figure 5 shows the waveform of the high-side FET voltage stress which is tested on the board.

Figure 5. High-side FET Voltage Ringing Waveform on TPS53667EVM-769

Compared to Figure 4 and Figure 5, both of them have low frequency and high frequency resonance. It does present the parasitic parameters playing as the major factor for the voltage ringing of high-side FET.

# 3 Mechanism of High-Side FET Voltage Ring In Multiphase Voltage Regulators

# 3.1 Bypass Capacitor Characteristics

4

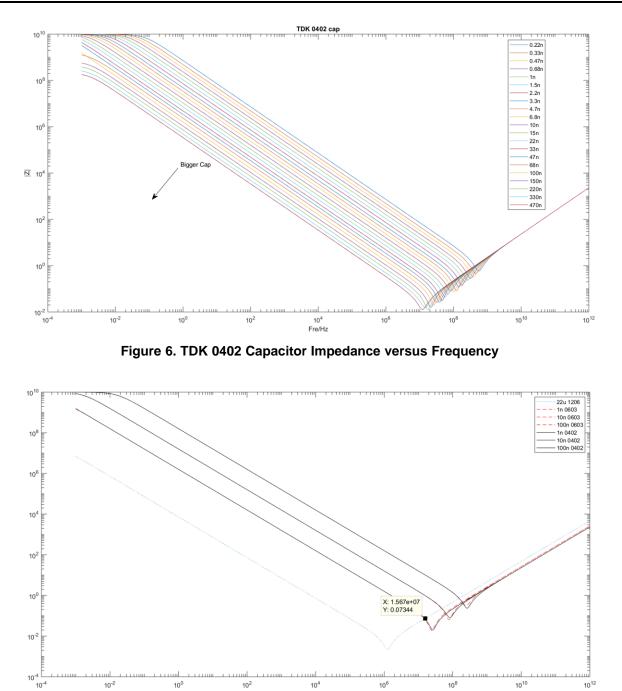

When using C3 (the bypass cap in Figure 2) to filter high frequency noise, its ESL plays a crucial role and cannot be ignored. Figure 6 shows the impedance of the 0402 capacitor with different volume. Figure 7 shows the impedance with a different package. Apparently, with a larger package, the capacitor has larger ESL and higher impedance in high frequency. Therefore, use a big cap (bulk cap) to filter low frequency noise and a small cap (bypass cap) for the high frequency noise.

Figure 7. TDK Different Size Capacitor Impedance versus Frequency

# 3.2 High and Low Frequency Resonance

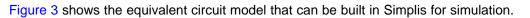

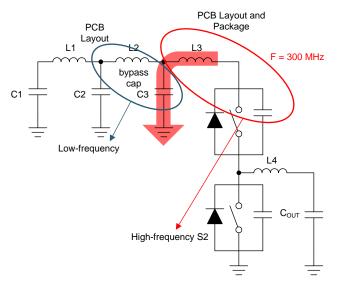

To better understand the origin of the high and low frequency resonance, simplify the circuit of the VIN part as shown in Figure 8.

www.ti.com

Figure 8. Simplified Circuit of VIN Part

In Figure 8, C1 is the bulk capacitor, C2 is the middle capacitor, and C3 is the bypass. The ESLs of divided VIN copper wires are L1, L2, and L3.

Later, you use these component numbers in Figure 8 to represent the corresponding device. The details can be seen in Table 1.

| NUMBER | COMPONENT            | DESCRIPTION                              |

|--------|----------------------|------------------------------------------|

| C1     | Bulk capacitor       | -                                        |

| C2     | Middle capacitor     | -                                        |

| С3     | Bypass capacitor     | -                                        |

| L1     | VIN copper wire ESL1 | ESL from C1 to C2                        |

| L2     | VIN copper wire ESL2 | ESL from C2 to C3                        |

| L3     | VIN copper wire ESL3 | ESL from C3 to VIN pin and ESL inside IC |

**Table 1. Component Comparison Table**

The high frequency is mainly affected by C3, Coss\_S1, L3, and ESL of C3. When C3 >> Coss\_S1, C3 can be ignored. The low frequency is mainly affected by L2, C2, and C3. When C2 >> C3, C2 can be ignored.

# 3.3 The Influence of C3 (Bypass Cap)

### 3.3.1 The Volume of C3 (Bypass Cap)

6

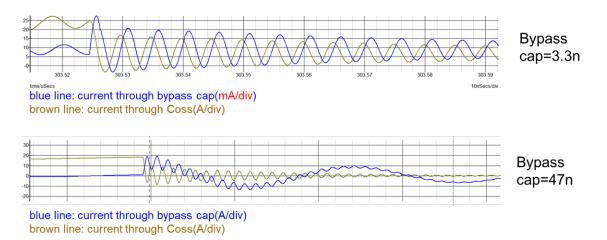

C3 significantly dominates the low frequency resonance. In Figure 7, with the same package, when the capacitance increases, the impedance decreases. The lower impedance bypass channel leads more current to flow through the bypass cap. The low frequency resonance is enhanced, and the high frequency resonance weakens. In fact, this has the same function as the bypass cap. Figure 9 shows the simulation result of the current flow through the bypass cap and the Coss\_S1. The bypass cap is 3.3 nF, the only mA level current flows through the bypass cap, and the high frequency resonance peak current is 17 A. When the bypass cap changes to 47 nF, there is 10 A peak resonant current flow through the bypass cap. The high frequency resonance peak current drops to 10 A. In a conclusion, a large amount of current was bypassed into the low frequency resonant path.

### Figure 9. Simulation Result of Current Distribution

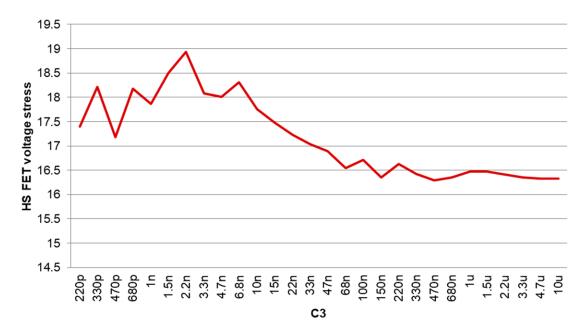

Figure 10 shows the simulation result of the relationship between the high-side FET voltage stress and the bypass cap. In this simulation, the package of the bypass cap stays with the 0402. The result shows that a bigger cap volume decreases the voltage stress. Moreover, when a bypass cap is larger than 68 nF, the downtrend of voltage stress slows down.

### Figure 10. Simulation Result of High-side FET Voltage and Bypass Cap

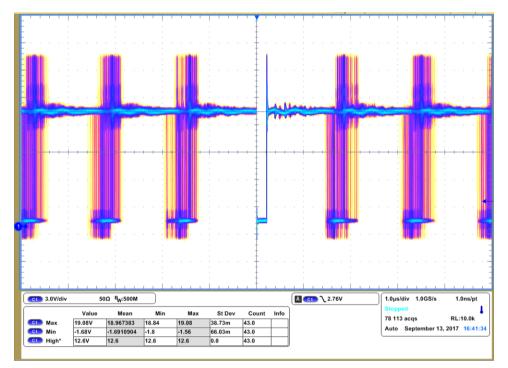

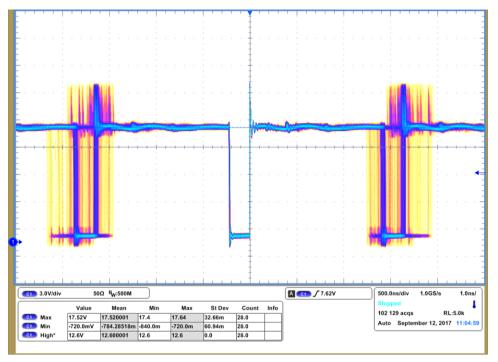

Figure 11 and Figure 12 show the test waveform of high-side FET voltage stress with a bypass cap of 3.3 nF and 47 nF. Compared to these two figures, you can see the voltage stress drop from 19.08 V to 17.52 V.

Test Conditions: Vin = 12.6 V; 5phase 228 A, 45.6 A per phase

- Figure 11: Bypass cap: 3.3 nF

- Figure 12: Bypass cap: 47 nF

www.ti.com

Figure 11. Voltage Stress Waveform with 3.3 nF

Figure 12. Voltage Stress Waveform with 1 µF

#### 3.3.2 The ESL of C3 (Bypass Cap)

From the previous analysis in Section 3.2, the ESL of the bypass is also the resonant component in high frequency. The larger package of the bypass cap has larger impedance in high frequency. Accordingly, the low frequency resonance weakens and the voltage stress increases. This is not expected. Figure 11 shows the simulation result.

Figure 13. Simulation Result About Bypass Cap ESL

### 3.3.3 The Placement of C3 (Bypass Cap)

The placement of the bypass cap decides the ESL of the VIN copper wire between the bypass cap and IC VIN pin. This ESL is part of L3. A larger L3 stores more current at the beginning of the voltage ring. This current is the initial energy of the resonant process, so try to decrease this ESL and place the bypass cap as close as possible.

### 3.4 Voltage Stress Point and FET

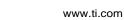

The VIN pin connects to the FET by copper connection inside the IC. This part generates ESL too. When you test voltage stress, you can only set the test point outside the VIN pin. Actually, this is not the real voltage stress of FET. The following research is about the comparison of the voltage stress test point and FET. Divide L3 into two parts: C3 to VIN pin and VIN pin to FET, as Figure 15 shows.

Figure 14. Simulation Circuit of the Voltage Inside and Outside IC

According to the simulation result, the test point voltage ringing is different with FET voltage ringing.

Figure 15. Simulation Result About the Voltage Test Point and FET

# 4 Conclusion

The high-side FET voltage ringing mechanism is very complex. This application report demonstrates the key factor for the ringing. The design engineer can refer to the mechanism to optimize their PCB layout.

### 5 References

• TDK Page

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated