# Optimizing High Side FET Voltage Ringing of Multiphase Voltage Regulators Part 2

Leon Liang/Wilson Guo/Chasel Chen

#### ABSTRACT

With the rapid demand growth of the server and communication market, high-current CPUs and ASICs are popular in server and communication system design. Multiphase power solutions are widely adopted for supplying CPUs and ASICs. However, to achieve high power density, each power stage must deliver more energy to the load. This makes optimizing the voltage ringing of the high-side FET a challenge. This serial application report demonstrates the challenges of a low-voltage ringing design.

#### Contents

| 1 | Introduction                                    | 1 |

|---|-------------------------------------------------|---|

| 2 | Copper and Via Parasitic Parameter Introduction | 1 |

|   | Improper PCB Layout Example                     |   |

|   | 4. Conclusion                                   |   |

|   | References                                      |   |

#### List of Figures

| 1 | PCB Trace Parasitic Inductance                          | 2 |

|---|---------------------------------------------------------|---|

| 2 | Parasitic Inductance of the PCB Via                     | 2 |

| 3 | Improper PCB Layout Sample                              | 3 |

| 4 | Equivalent Simulation Circuit of an Improper PCB layout | 3 |

| 5 | On-Board Test High-Side FET VDS Waveform                | 4 |

| 6 | Simulation Waveform                                     | 5 |

| 7 | Layout Recommendation                                   | 5 |

| 8 | Simulation Results Based on Layout Recommendation       | 6 |

|   |                                                         |   |

## Trademarks

All trademarks are the property of their respective owners.

#### 1 Introduction

To reduce the FET voltage ringing, system designers usually add an RC snubber between the switching node and ground. However, these only reduce the low-side FET voltage ringing. High-side FET voltage ringing still depends on the parasitic parameters of the input capacitors, and the PCB layout. Improper layout and input capacitors can result in excessive voltage ringing. This serial application report shows the voltage ringing mechanism of the formation, and discusses how to reduce the high-side voltage ringing in the design with appropriate input bypass capacitor selection, and layout design, that improves system reliability.

## 2 Copper and Via Parasitic Parameter Introduction

Ideally, the PCB copper trace and via are just a 0  $\Omega$  wire that connects different parts on the board. However, when considering a high-frequency signal, the parasitic parameters of the copper trace and via significantly impact the MOSFET voltage stress.

1

Copyright © 2019, Texas Instruments Incorporated

#### Improper PCB Layout Example

www.ti.com

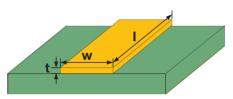

A PCB trace is made up of the parasitic resistor, inductance, and capacitor. Parasitic inductance is the focus when decreasing the voltage ring of the FET, as the FET has a high-impedance feature in highfrequency ranges. See Figure 1 for a formula that calculates the approximate parasitic inductance of the copper trace.

Figure 1. PCB Trace Parasitic Inductance

As shown in Figure 1, the length has more influence than the width when considering the parasitic inductance of the PCB trace. Thus, the bypass cap must be placed close to the Vin pin.

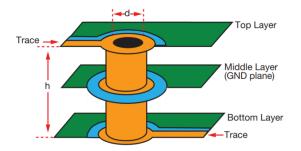

See Figure 2 to view the parasitic inductance of the PCB via.

Figure 2. Parasitic Inductance of the PCB Via

To decrease via inductance effects, add more vias near the bypass cap pads. The parallel vias can lower the impedance, and the high-frequency noise can be easily absorbed.

An alternative to the experience formula shown in Figure 1 is software. Software can also be used to calculate the parasitic parameter. The software extraction process can usually consider more practice parameters.

The example shown in Section 3 uses software to extract the PCB trace, and the parameters of the vias.

#### 3 Improper PCB Layout Example

#### 3.1 Improper PCB Layout and Related Parasitic Parameters

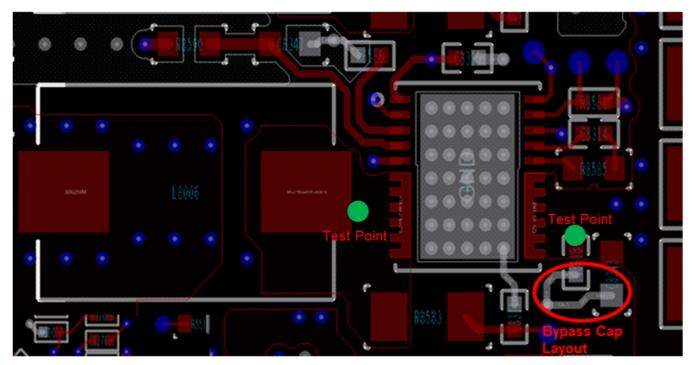

Figure 3 illustrates an improper PCB layout example. The bypass cap is connected to the inner GND plane through a via and a single wire, which leads to high parasitic inductance. This inductance can make the bypass cap ineffective, and increase the FET voltage stress.

www.ti.com

Figure 3. Improper PCB Layout Sample

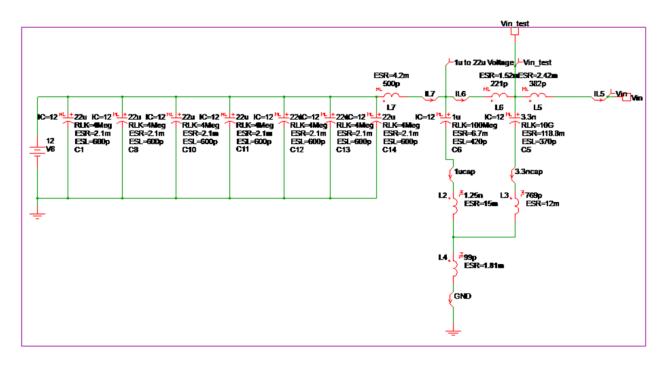

As seen in Figure 4, the previously discussed parasitic parameters of the PCB can be extracted. Figure 4 also shows equivalent circuits.

# Figure 4. Equivalent Simulation Circuit of an Improper PCB layout

Improper PCB Layout Example

### 3.2 The Comparison Between Test Waveform and Simulation

Since the test probe can hardly touch the FET pin, the parasitic inductance is divided into two portions in the following discussion. The first one is above the equivalent circuit, and the second one is the parasitic inductance between the test point and FET pin. It is extracted as 382 pH.

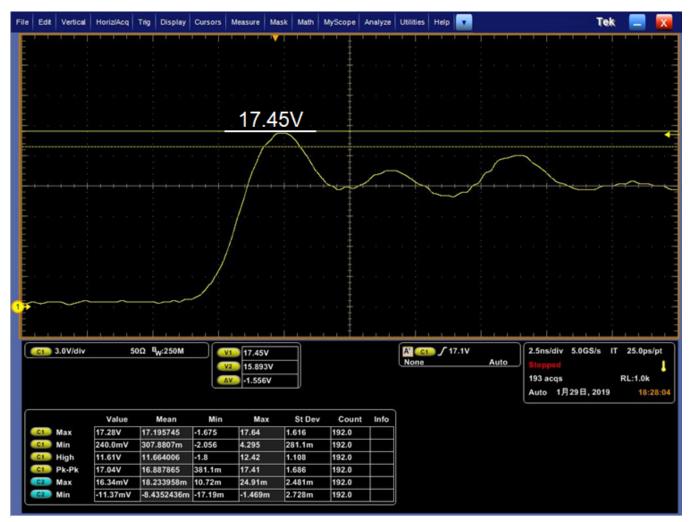

Figure 5 displays test results on the real board. The high-side FET voltage stress is 17.45 V, and is not the normal dampened oscillation waveform. This is because the parasitic parameter causes different oscillation frequencies.

Figure 5. On-Board Test High-Side FET VDS Waveform

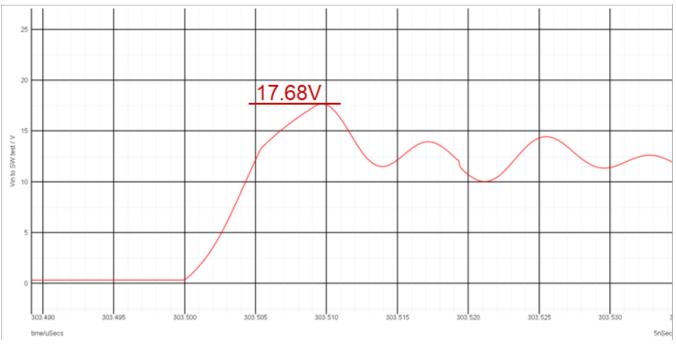

Figure 6 shows the simulation results after setting the simulation test point with the same test condition. The FET voltage stress is 17.68 V in simulation.

www.ti.com

Improper PCB Layout Example

#### Figure 6. Simulation Waveform

Between Figure 5 and Figure 6, both the shape and peak values are well-correlated.

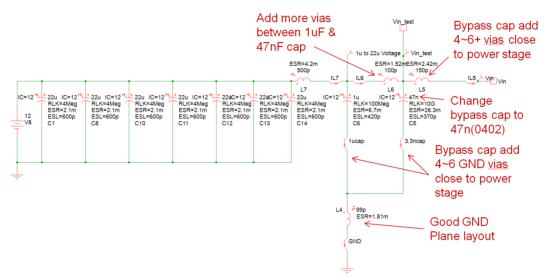

## 3.3 Layout recommendation

To decrease the peak ringing voltage, optimize the PCB layout, and change the bypass cap from 3.3 nF to 47 nF with the same package (0402). Figure 7 is the detailed layout recommendation for this case.

As more vias are added near the bypass caps, and with good GND-plane layout, the inductances decrease. A bigger bypass cap with the same package can also help decrease the bypass path impedance. Moreover, the bypass cap must be placed on the same side as the Vin and ground. Otherwise, the bypass path impedance becomes larger.

Figure 7 shows the changed parasitic inductance of the PCB trace and vias after optimization.

## Figure 7. Layout Recommendation

www.ti.com

#### Improper PCB Layout Example

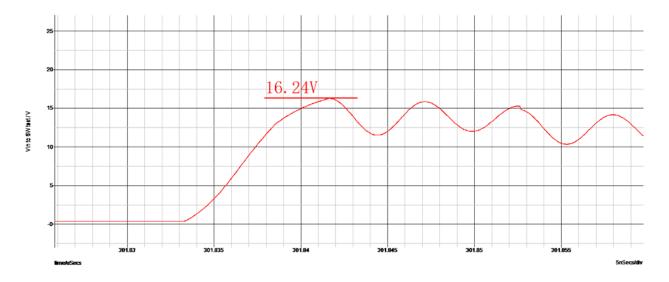

#### 3.4 Optimizing Result

Figure 8 shows the simulation results with a modified PCB. With the same test conditions, the peak, highside FET VDS voltage can be reduced from 17.68 V to 16.24 V, which is a 1.44 V (or 8.2%) improvement.

#### Figure 8. Simulation Results Based on Layout Recommendation

Consequently, PCB layout and bypass cap play an important role in reducing high-side FET voltage ringing.

## 4 4. Conclusion

High-side FET voltage ringing in high-current, multiphase applications can be optimized by:

- PCB layout Optimization

- The bypass cap must be placed on the same side of the power stage to reduce parasitic inductance from the via

- The bypass cap must be connected through solid VIN and GND placement to reduce parasitic inductance from the trace

- Choosing the correct bypass cap type, package, and capacitance is also crucial in reducing the FET voltage ringing.

# 5 References

6

- Home TDK Electronics

- Texas Instruments, Analog Engineer's Pocket Reference

- Texas Instruments, Optimizing High Side FET Voltage Ringing of Multiphase Voltage Regulators Part 1

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated