# Generating Negative and Positive Voltage Rail With Boost Converter TLV61048

Jasper Li

### ABSTRACT

Many applications require negative and positive voltage rails to power the amplifiers from a 3.3-V or 5-V power supply. Taking the TLV61048 device as an example, this document demonstrates a simple, cost-effective boost converter and discrete charge pump circuit to generate ±12-V voltage rails.

#### Contents

| Introduction                    | 1                                                                                      |

|---------------------------------|----------------------------------------------------------------------------------------|

| Operating Principle             | 1                                                                                      |

| External Components Calculation |                                                                                        |

| Circuit Design With TLV61048    | 5                                                                                      |

| References                      |                                                                                        |

|                                 | Operating Principle<br>External Components Calculation<br>Circuit Design With TLV61048 |

#### List of Figures

| 1 | TLV61048 Boost Converter Schematic      | 2 |

|---|-----------------------------------------|---|

| 2 | Operating Waveform at 100-mA Loading    | 2 |

| 3 | Boost With Discrete Charge Pump Circuit | 3 |

| 4 | Simplified Operating Waveform           | 3 |

| 5 | Designed Circuit With TLV61048          | 5 |

| 6 | Startup Waveform by EN Pin              | 6 |

| 7 | Load Regulation of the Negative Rail    | 6 |

|   |                                         |   |

#### List of Tables

### Trademarks

All trademarks are the property of their respective owners.

# 1 Introduction

The application report first introduces the operating principle of the discrete charge pump circuit to generate negative voltage based on boost converter. Then the report derives formulas to calculate the external component values of the charge pump circuit. Finally, the TLV61048 device is used as example to verify the circuit designed in the lab.

# 2 Operating Principle

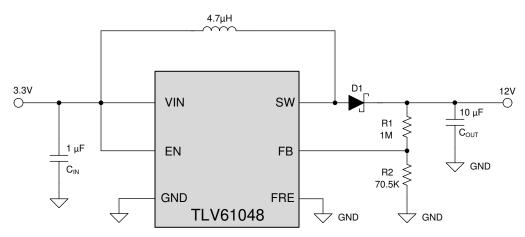

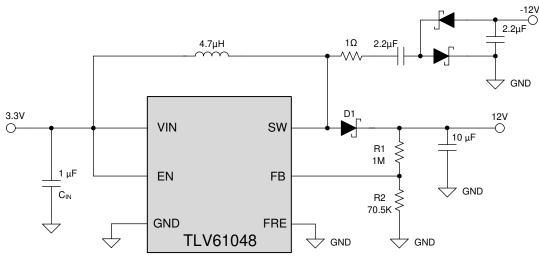

A typical boost circuit for 3.3-V input, 12-V output based on the TLV61048 device is shown in Figure 1. The TLV61048 device is a peak-current-control boost converter IC which integrates a power switch with current limit up to 3.7 A. The switching frequency can be configured through the FRE pin. If the FRE pin is connected to GND, the switching frequency of the device is 1 MHz.

1

**Operating Principle**

www.ti.com

Figure 1. TLV61048 Boost Converter Schematic

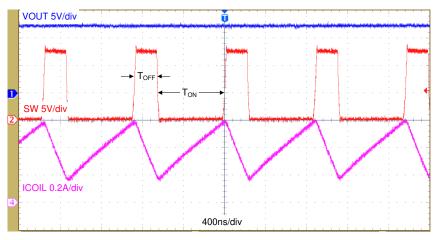

Figure 2 shows the operating waveform at 100-mA loading. The integrated power N-MOSFET switches on and off to regulate the output voltage, which is set by R1 and R2.

- During T<sub>oN</sub>, the internal low-side FET is on. The SW pin voltage is zero and inductor current lineally increases. The output voltage is sustained by the output capacitor.

- During T<sub>OFF</sub>, the internal N-MOSFET is off. The inductor flows through the Schottky diode D1 to charge the output capacitor.

The sum of  $T_{ON}$  and  $T_{OFF}$  is the switching cycle  $T_{SW}$ , approximately 1 µs. The device operates at Continue Conductive Mode (CCM) in Figure 2, as the inductor current is always higher than zero.

Figure 2. Operating Waveform at 100-mA Loading

At CCM, the duty cycle can be calculated using Equation 1:

$$\mathsf{D} = \mathsf{1} - \frac{\eta \times \mathsf{V}_{\mathsf{IN}}}{\mathsf{V}_{\mathsf{OUT}}}$$

where:

2

- η is the efficiency

- $V_{IN}$  is the input voltage of the boost converter

- V<sub>OUT</sub> is the output voltage of the boost

(1)

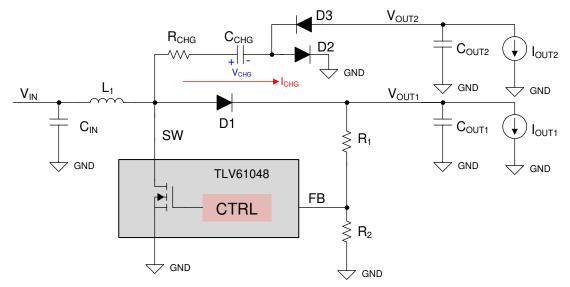

The power components of the typical boost converter with discrete circuit to generate a negative voltage is shown in Figure 3. The positive rail is  $V_{OUT1}$ , while the negative voltage rail is  $V_{OUT2}$ . The external components for negative voltage rail comprise of a resistor  $R_{CHG}$ , and a capacitor  $C_{CHG}$  and two diodes, D2 and D3.

www.ti.com

- During  $T_{OFF}$ , the fly capacitor  $C_{CHG}$  is charged to SW pin voltage through the  $R_{CHG}$  and D2.

- During  $T_{ON}$ , the energy of the  $C_{CHG}$  flows into the  $C_{OUT2}$  through  $R_{CHG}$  and D3.

Figure 3. Boost With Discrete Charge Pump Circuit

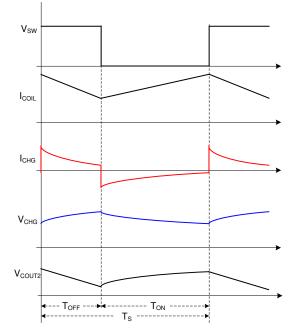

Figure 4 shows the simplified operating waveform of the circuit, where:

- V<sub>sw</sub> is the SW pin voltage waveform at CCM

- I<sub>COIL</sub> is the inductor current

- I<sub>CHG</sub> is the current through the C<sub>CHG</sub>

- $V_{CHG}$  is the voltage across the  $C_{CHG}$

Figure 4. Simplified Operating Waveform

## External Components Calculation

# 3 External Components Calculation

At stable condition, the average current through the  $C_{CHG}$  and  $C_{OUT2}$  within one switching cycle must be zero. Thus the average current of  $I_{CHG}$  during  $T_{ON}$  is defined by Equation 2.

$$I_{CHG1} = \frac{T_S}{T_{ON}} \times I_{OUT2} = \frac{1}{D} \times I_{OUT2}$$

(2)

The average current through  $C_{CHG}$  during  $T_{OFF}$  can be calculated by Equation 3 .

$$I_{CHG2} = \frac{I_{ON}}{T_{OFF}} \times I_{CHG1} = \frac{1}{1 - D} \times I_{OUT2}$$

(3)

From Equation 2 and Equation 3, the voltage ripple of the C<sub>CHG</sub> can be calculated with Equation 4.

$$\Delta V_{CHG} = I_{CHG1} \times \frac{1}{C_{CHG}} \times T_{ON} = \frac{I_{OUT2}}{C_{CHG}} \times T_{SW}$$

(4)

As all the energy of the  $C_{OUT2}$  is provided by during  $C_{CHG}$  during  $T_{ON}$ , the  $C_{CHG}$  voltage reaches valley and  $V_{OUT2}$  reaches peak at the end of  $T_{ON}$ . The waveform in Figure 4 demonstrates this behavior. This means that the voltage ripple of the  $C_{CHG}$  would impact the voltage level of the  $V_{OUT2}$ . So  $C_{CHG}$  voltage ripple should be set to typical 1% of its DC voltage.

The DC voltage of the  $C_{CHG}$  can be calculated with Equation 5. Ignoring the voltage drops of the  $R_{CHG}$ , the  $V_{CHG}$  is equal to  $V_{OUT1}$ .

$$V_{CHG} = (V_{OUT1} + V_{D1}) - I_{CHG2} \times R_{CHG} - V_{D2}$$

where:

- V<sub>OUT1</sub> is positive rail voltage set by the feedback resistor

- V<sub>D1</sub> is forward voltage of D1.

- I<sub>CHG1</sub> is the average current during T<sub>OFF</sub>

- V<sub>D2</sub> is the forward voltage of D2

The voltage ripple of the  $C_{OUT2}$  is defined by Equation 6. The output voltage ripple can also be set to 1% of its DC voltage.

$$\Delta V_{\text{COUT2}} = I_{\text{OUT2}} \times \frac{1}{C_{\text{OUT2}}} \times (1 - D) \times T_{\text{SW}}$$

(6)

The DC voltage of  $C_{OUT2}$  can be estimated through Equation 7, closed to ( $V_{OUT1} - 0.3$ ) if ignoring the  $R_{CHG}$  voltage drop.

$$-V_{\text{COUT2}} = V_{\text{CHG}} - I_{\text{CHG1}} \times R_{\text{CHG}} - V_{\text{D3}} = \left(V_{\text{OUT1}} + V_{\text{D1}}\right) - \left(V_{\text{CHG1}} + I_{\text{CHG2}}\right) \times R_{\text{CHG}} - 2 \times V_{\text{D2}}$$

where:

4

$R_{CHG} \times C_{CHG} = T_S$

•  $V_{CHG}$  is DC voltage of the  $C_{CHG}$

through the  $R_{CHG}$  is closed to the average current.

•  $V_{D3}$  is the forward voltage of the D3, equal to VD2

The R<sub>CHG</sub> is to limit the peak current through the capacitor, internal MOSFET, and D2 and D3. From Equation 7, high R<sub>CHG</sub> will result in low C<sub>OUT2</sub> voltage. Thus the R<sub>CHG</sub> cannot be too large. It is suggested to select R<sub>CHG</sub> as Equation 8, which means the time constant of the R<sub>CHG</sub> and C<sub>CHG</sub> is equal to the switching cycle.

$$P_{\text{RCHG}} = R_{\text{CHG}} \times \left( D \times I_{\text{CHG1}}^2 + (1 - D) \times I_{\text{CHG2}}^2 \right)$$

(9)

www.ti.com

(7)

(8)

(5)

www.ti.com

# 4 Circuit Design With TLV61048

This section uses the TLV61048 device as an example to demonstrate the design process introduced in this application report.

The input and output electrical requirements follow:

- Input voltage V<sub>IN</sub>: 3.3 V

- Positive rail voltage V<sub>OUT1</sub>: 12 V

- Negative rail voltage V<sub>OUT2</sub>: -12 V

- Maximum output current of V<sub>OUT1</sub> and V<sub>OUT2</sub>: 100 mA

- Voltage ripple of V<sub>OUT2</sub>: 120 mV

Based on this requirement, the design process is as shown in the following list when setting the switching frequency to 1 MHz:

- Duty cycle D: 75% by Equation 1

- Average current during T<sub>ON</sub>, I<sub>CHG1</sub>= 133 mA by Equation 2

- Average current during T<sub>ON</sub>, I<sub>CHG2</sub>= 400 mA by Equation 3

- DC voltage of the C<sub>CHG</sub> at zero loading,  $V_{CHG} \approx 12$  V by Equation 5

- Voltage ripple of V<sub>CHG</sub> is 1% of its DC voltage,  $\Delta V_{CHG} \approx 120 \text{ mV}$

- Effective capacitance of C<sub>CHG</sub>, 0.83 µF by Equation 4

- Current limit resistor, R<sub>CHG</sub> = 1.2 Ω by Equation 8

- Power loss of R<sub>CHG</sub>, 60 mW by Equation 9

- Effective capacitance of C<sub>OUT2</sub>, 0.6 µF by Equation 6

- DC voltage of  $C_{CHG}$  at 100 mA,  $V_{CHG}$ = 11.5 V by Equation 5

- DC voltage of C<sub>OUT2</sub> at 100 mA, V<sub>OUT2</sub> = -11 V by Equation 7

Using the external components value closed to the previous calculation result , the final circuit is shown in Figure 5. The effective capacitance of the 2.2- $\mu$ F capacitor at 12-V bias condition is around 0.8  $\mu$ F.

Figure 5. Designed Circuit With TLV61048

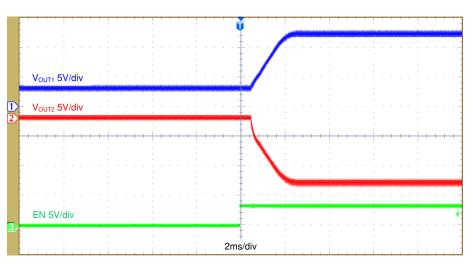

The startup waveform through the EN pin at a 100-mA condition is shown in Figure 6. After the EN pin becomes logic high, the voltage of  $V_{OUT1}$  and  $V_{OUT2}$  ramp up to the setting value smoothly.

5

www.ti.com

Figure 6. Startup Waveform by EN Pin

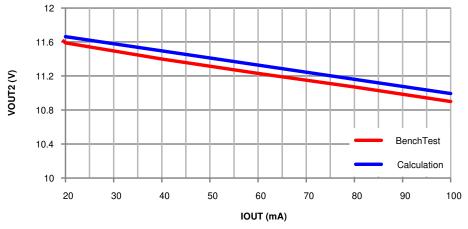

The absolute value of V<sub>OUT2</sub> from 20 mA to 100 mA is shown in Figure 7. The voltage gap between the calculation result by Equation 7 and the bench test result is approximately 100 mV. Because of the voltage drop of the resistor and the Schottky diode, the V<sub>OUT2</sub> absolute value is 11.6 V at 20-mA loading and is 11 V at 100-mA loading.

Figure 7. Load Regulation of the Negative Rail

# 5 References

1. Texas Instruments, Design for a Discrete Charge Pump

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated