# Application Report **Powering Sensitive ADC Designs with the TPS62913 Low-Ripple and Low-Noise Buck Converter**

# TEXAS INSTRUMENTS

Rob Reeder, Steve Schnier

### ABSTRACT

- The power supply design demonstrates a simplified and efficient implementation of the TPS62913 low ripple and low noise buck converter to power an ADC12DJ5200RF, reducing power consumption by 1.5W (15% power savings).

- The Analog, Digital, and Clock rails are all supplied using the switching regulator without the need for a lowdroppout linear regulator (LDO) while maintaining the same performance as the original design.

- The design is applicable to the ADC12DJ5200 and other ADCs that require low noise power supplies that are size constrained and thermal constrained. Examples of applications are RF converters in the GSPS region such as RADAR, test and measurement instrumentation, and communications.

- Short description of ADC12DJ5200 and overview of the EVM modifications to use a switching supply only, without the need for LDOs.

- Key measurement results and comparison to previous implementation, including output noise density, SNR, SFDR, and PSMR.

## **Table of Contents**

| 1 Introduction and System Description | 2    |

|---------------------------------------|------|

| 1.1 Introduction                      | 2    |

| 1.2 Block Diagram                     | 4    |

| 1.3 Design Considerations             | 7    |

| 2 Tests and Results                   | 8    |

| 2.1 Test Methodology                  | 8    |

| 2.2 Test Conditions                   | .11  |

| 2.3 Test Results                      |      |

| 3 Conclusion                          | . 16 |

| 4 References                          | . 17 |

| 5 Appendix                            | . 18 |

## Trademarks

All other trademarks are the property of their respective owners.

## 1 Introduction and System Description

#### **1.1 Introduction**

High speed analog to digital converters are notoriously sensitive to power supply noise. The most common solution to minimize that noise is to use linear power supplies, or a switch mode power supply (SMPS) from the main bus rail followed by a low droput regulator. Compared to a linear supply, there are two big advantages of being able to use a SMPS alone: the reduction in power loss and the size of the power supply. To use a SMPS alone requires careful consideration of the switching supply selected, as well as the design and layout of the SMPS to achieve the desired results of the same performance with lower power dissipation and smaller board space.

This application note uses the ADC12DJ5200 as an example of a high performance ADC where the supplies have been changed from a SMPS+LDO approach to a SMPS-only approach. This methodology can be used for many other noise sensitive applications as well. The TPS62913 low-ripple and low-noise buck converter used in this application note is specifically designed to help engineers design power supplies that meet the noise and ripple requirements for noise sensitive applications.

#### 1.1.1 ADC12DJ5200 Noise and Ripple Requirements

The ADC12DJ5200RF is a 12bit GSPS RF-analog-to-digital converter (ADC) that can directly sample input frequencies from DC to above 8GHz. ADC12DJ5200RF can be configured as a dual-channel, 5.2 GSPS ADC or single-channel, 10.4 GSPS ADC. These operating modes allow programmable tradeoffs in channel count and Nyquist bandwidth. Useable input frequency range of up to 8 GHz enables direct RF sampling of L-band, S-band, C-band, and X-band for frequency agile systems. The ADC12DJ5200RF uses a high-speed JESD204C output interface with up to 16 serialized lanes supporting up to 17.16 Gbps line rate. Deterministic latency and multi-device synchronization is supported through JESD204C subclass-1. The interface is backwards compatible with JESD204B receivers. Innovative synchronization features, including noiseless aperture delay (TAD) adjustment and SYSREF windowing, simplify system design for multichannel applications. Optional digital down converters (DDCs) are available to provide digital conversion to baseband and to reduce the interface rate. A programmable FIR filter allows on-chip equalization.

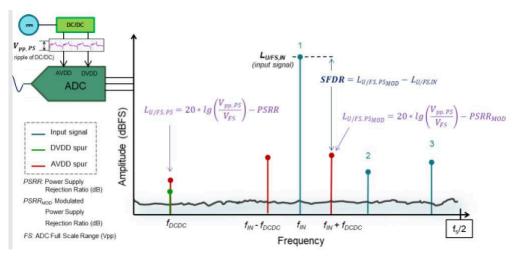

The original product evaluation module (EVM) implements low-noise LDOs in addition to the DC/DC buck regulators to minimize any impairments from the supply network. While the DC accuracy of the supply rail is specified for the ADC12DJ5200RF, there is no specification on supply voltage noise and supply voltage ripple. Any supply ripple or noise appears attenuated on the output spectrum of the ADC. This attenuation can be expressed as Power Supply Rejection Ration (PSRR) and PSRR<sub>MOD</sub> (or PSMR) as shown in Figure 1-1.

Figure 1-1. Power supply noise and ripple in the ADC output spectrum

TEXAS INSTRUMENTS

www.ti.com

PSRR is the attenuation of the ADC input supply ripple to the ADC output spectrum at the switching frequency fundamental of the DC-DC converter ( $f_{DCDC}$ ). PSRR<sub>MOD</sub> (or PSMR) is the attenuation from the ADC input to the modulated spur in the output spectrum ( $f_{in}$  -  $f_{DCDC}$ ,  $f_{in}$  +  $f_{DCDC}$ ).

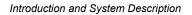

PSRR is usually less of a concern since it is typically >40 dB and outside of the frequency of interest, however some analog rails can have PSRR of <40 dB, as shown in Figure 1-2, which shows the most sensitive supplies of the ADC12DJ5200RF are the analog supply rails of VA11 and VA19. More important is PSMR, since the attenuation from the supply rail to the modulated spur can be low for sensitive analog rails such as VA11 and VA19 on the ADC12DJ5200RF.

#### 1.1.2 Power Supply Requirements for Wideband RF PLL and Clocks

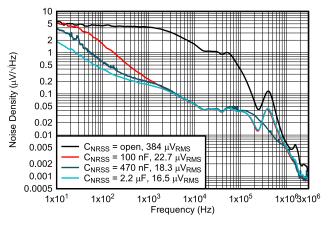

On the ADC12DJ5200 evaluation module, an RF PLL is used as a frequency synthesizer for clocking the ADC. Similar to high speed ADCs, higher frequencies command larger supply currents. At the same time, higher frequencies require lower clock jitter and therefore lower phase noise. Phase noise is directly impacted by the power supply noise and ripple. Since the LMX is powered from a 3.3-V supply rail, the PSRR is measured from the 3.3-V rail to the spurs of the output specturm. The LMX PSRR has a low-pass behavior with increasing attenuation at frequencies above the PLL loop bandwidth. The most sensitive frequency range for supply noise is before and around the PLL corner frequency, and heavily depends on the PLL filter characteristics. At low frequencies the noise is dominated by the external oscillator noise. Therefore, it is key to have a low-noise DC-DC converter design with <20  $\mu V_{RMS}$  noise (100 Hz to 100 kHz) and low spectral noise density of ~0.1 uV/ $\sqrt{(Hz)}$  before the PLL corner frequency in the range of 1kHz to 100kHz to achieve clock jitter of 100 fs and lower. The performance of the TPS62913 is shown in Figure 1-3.

Figure 1-3. TPS62913 Output Noise Density vs Frequency for 12Vin to 3.3Vout at 2.2MHz

|                        | Note |  |

|------------------------|------|--|

| BW = 100 Hz to 100 kHz |      |  |

The TPS62913 has been designed specifically for low noise with the addition of an external noise reduction filter cap, which also provides the means to adjust the softstart time. Using a 470 nF  $C_{NR/SS}$  cap provide the noise performance desired and a 5 ms softstart time.

#### 1.1.3 TPS62913 Low-Noise and Low-Ripple Buck Converter

The TPS62912 and TPS62913 devices are a family of high-efficiency, low-noise and low-ripple synchronous buck converters. The devices are ideal for noise sensitive applications that would normally use an LDO for post regulation such as high-speed ADCs, Clock and Jitter Cleaner, Serializer, De-serializer, and Radar applications. The device operates at a fixed switching frequency of 2.2 MHz or 1 MHz, and can be synchronized to an external clock. To further reduce the output voltage ripple, the device integrates loop compensation to operate with an optional second-stage ferrite bead L-C filter. This allows an output voltage ripple below 10  $\mu$ VRMS. Low-frequency noise levels, similar to a low-noise LDO, are achieved by filtering the internal voltage reference with a capacitor connected to the NR/SS pin. The optional spread spectrum modulation scheme spreads the DC/DC switching frequency over a wider span, which lowers the mixing spurs.

### 1.2 Block Diagram

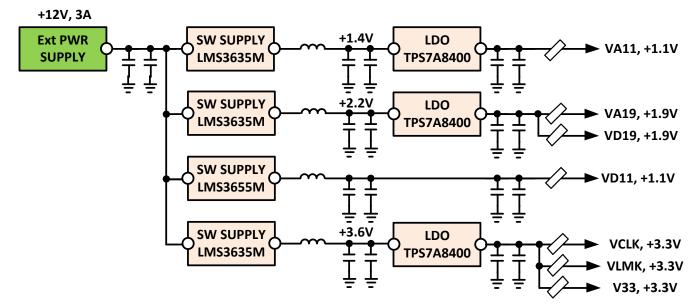

The original ADC12DJ5200 Rev C evaluation module used several SMPS with LDO followers to provide power to the ADC and clock rails. The 3.3V clock rails require low phase noise and low jitter. The 1.1 V analog rail (VA11) requires a separate LDO for the low noise requirements, while the 1.9 V analog and digital rails (VA19 and VD19) is supplied by a single supply as shown in Figure 1-4.

Figure 1-4. Original Power Block Diagram for ADC12DJ5200 Rev C Evaluation Module

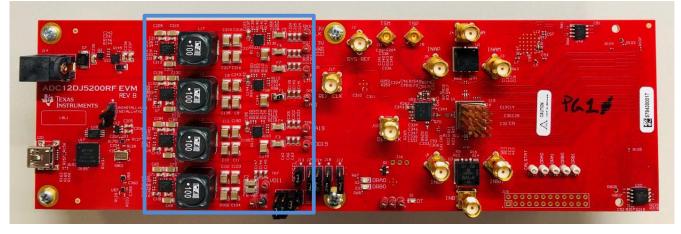

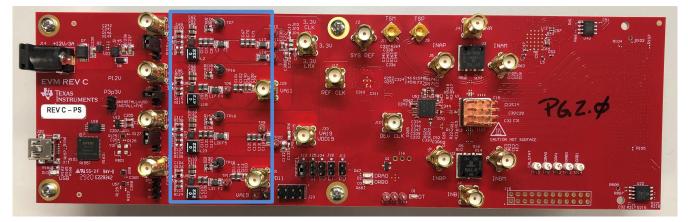

The original EVM power supply is outlined in blue and shown in Figure 1-5.

Figure 1-5. Image of board with Switchers and LDO's outlined in Blue

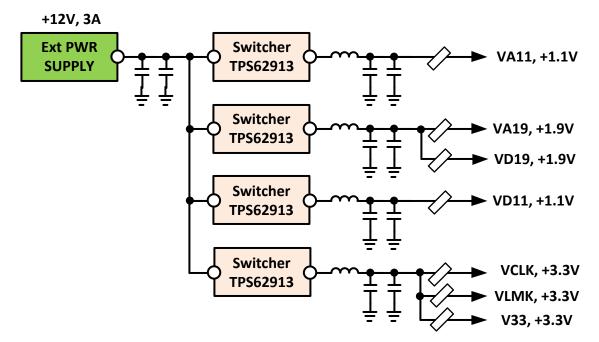

In the revised design, the LDOs are removed and the TPS62913 low-ripple, low-noise SMPS is used instead. This design presents a simplified power supply network for the ADC, where all three power domains are supplied from a DC/DC regulator, with a separate supply for the 3.3-V clock, as shown in Figure 1-6. This implementation improves the efficiency and reduces the part count in comparison to a solution using LDOs while maintaining the output voltage ripple and noise requirements of the ADC and clock for good performance.

Figure 1-6. Power Block Diagram for ADC12DJ5200 Rev C Evaluation Module with TPS62913

The updated EVM power supply with the TPS62913 is outlined in blue and shown in Figure 1-7.

#### Figure 1-7. Image of board with TPS62913 Switchers outlined in Blue

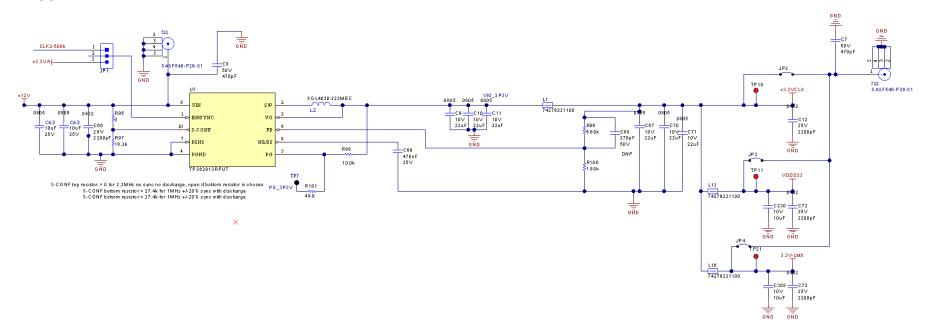

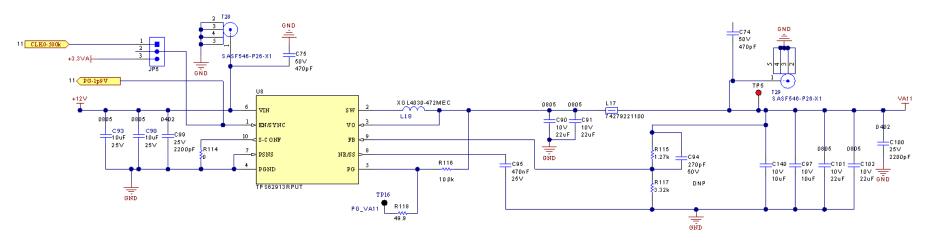

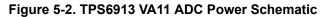

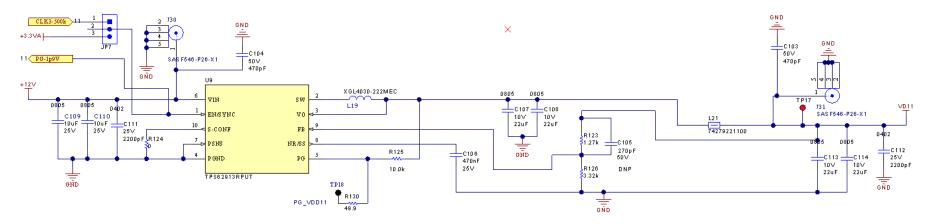

The schematics for the 3.3-V, 1.1-V, and 1.9-V rails can be found in the Appendix.

#### Table 1-1. ADC12DJ5200 Evaluation Module Component Comparison

| Component                | Original Rev C                   | Rev C with TPS62913         |

|--------------------------|----------------------------------|-----------------------------|

| Switching Power Supplies | 4 x LMS3635M (4mm x 5mm ea)      | 4 x TPS62913 (2mm x 2mm ea) |

| LDO's                    | 3 x TPS7A8400 (3.5mm x 3.5mm ea) | None                        |

| Size of Power Supplies   | 116.75 sqmm + passives           | 16 sqmm + passives          |

6

EXAS

*TRUMENTS*

www.ti.com

#### **1.3 Design Considerations**

The ADC12DJ5200 is a high performance multi giga sample per second (GSPS) ADC and is sensitive to noise and spurious contents that result from high current in the switching elements, output capacitor ESL, and the magnetics involved when using a standard DC/DC converter. Utilizing the TPS62913 low-ripple, low-noise converter enables a significant reduction in noise and ripple without using a post-regulation LDO through the converters' unique low-ripple and low-noise design features.

The converter's analog and clock inputs often get most of the scrutiny when it comes to addressing low noise on their inputs. Keep in mind that power supplies are inputs too. Because we think of them as DC biasing circuits we often don't think of them as relating to RF performance. However, this is not true. When designing power supply domains for any high-speed converter, here are some useful tips in maximizing power supply noise immunity:

- Decouple all power supply rails and bus voltages as they come onto the system board and near/at the ADC itself.

- Remember that approximately 20 dB/decade noise suppression is gained for each additional filtering stage.

- Decouple for both high and low frequencies, which might require multiple capacitor values.

- Series ferrite beads are commonly used at the power entry point. just before the decoupling capacitor to ground. This should be done for each individual supply voltage coming in on the system board whether it comes from an LDO or switcher regulator.

- For added capacitance, use tightly stacked power and ground plane pairs (≤4 mil spacing) this adds inherent high-frequency (>500MHz) decoupling to the PCB design.

- Keep supplies away from sensitive analog circuitry such as the front-end stage of the ADC and clocking circuits if possible.

- Some components could be located on the opposite side of the PCB for added isolation.

- Follow the IC manufacture recommendations; if they are not directly stated in the application note or data sheet, then study the evaluation board. These are great vehicles to learn from.

Applying these points above can help provide a solid power supply design yielding datasheet performance in many applications.

## 2 Tests and Results

## 2.1 Test Methodology

#### Power Supply Rejection Ratio (PSRR)

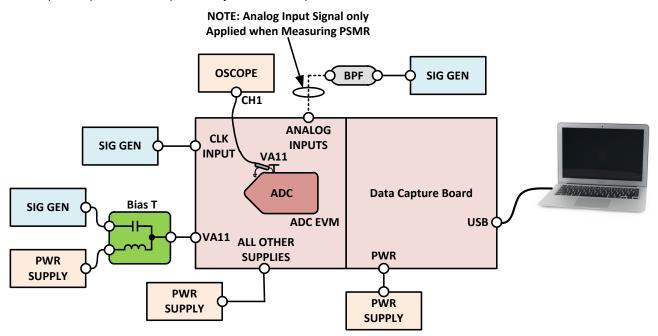

The PSRR is typically measured as shown in Figure 2-1using HSDC-Pro software to display and measure the digital output FFT spectrum. Each supply is tested individually, using a bias T, which can be purchased off the shelf from various companies. The bias T is used to combine the AC and DC signal to the individual supply under test. It's worth noting that the bias T must have a high enough current rating to supply enough bias to the supply under test. If not, the measurement could produce unreliable results.

After setting up the EVM or system board as you normally would, next, isolate the supply under test. Then apply the bias T to that supply, setting the appropriate DC voltage using an external lab bench power supply. Apply power to the rest of the board's power supplies as you normally would, keeping those supplies at nominal. Next, select a low frequency, 10 MHz or less to start and inject the sinewave signal source to the bias T. This is called the error signal. It is also important to use a signal generator that is used for the applied error signal, is clean with low phase noise. This is so that the converter's inherent performance is not otherwise degraded during testing. The signal generator should also be able to provide enough power to accommodate for the losses through the cabling, bias T and pcb.

Start the signal low in amplitude, slowly bringing the amplitude up until a spur comes out of the noise floor, the error spur should be high enough in the FFT spectrum where it is repeatable. The error spur should show at the error test frequency injected. Lets say the error spur amplitude captured is -85 dB.

Next use an oscilloscope or spectrum analyzer to note the level of the error signal injected. Make sure the error signal amplitude reading is taken at the ADC's power pin and note the peak to peak voltage injected at that pin. Once this is found, PSRR can be found using some simple math.

For example, if the voltage measured was 10mVpp and the converter's fullscale voltage is 1.2 Vpp. Then simply take the ratio of those two numbers or  $20^{10m/1.2} = -41.6 \text{ dB}$ . To find PSRR, subtract this number from the error spur amplitude found previously in the FFT spectrum or PSRR = -85 - -41.6 = -43.4 dB.

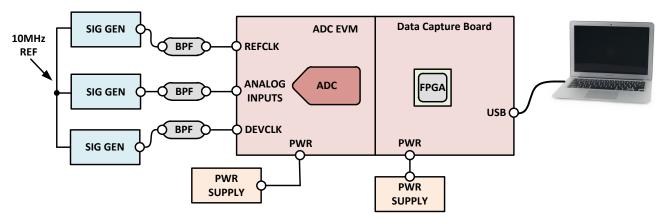

#### Figure 2-1. Test Configuration for PSRR and PSMR Measurement

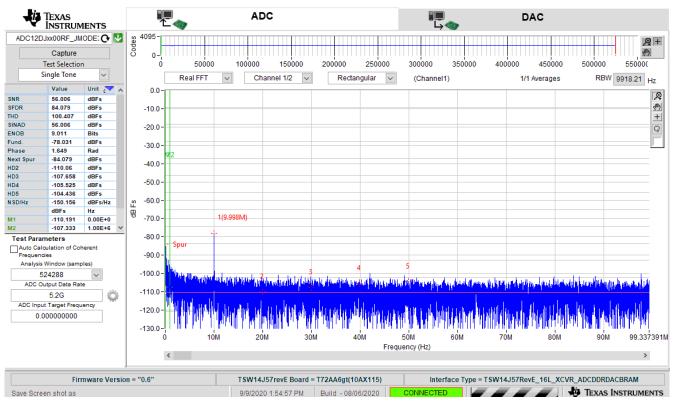

An example of PSRR, with a forced error signal injected on the VA11 supply at 10 MHz with a -1 dBm amplitude level from the signal generator is shown in Figure 2-2.

Figure 2-2. Example of Power Supply Rejection Ratio with Forced Error Signal

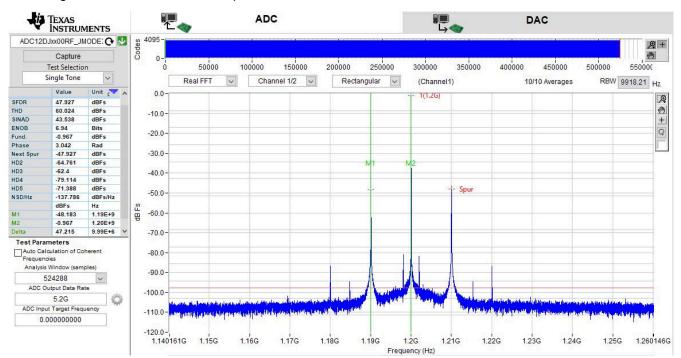

An example of PSMR, with a forced error signal injected at 10 MHz with a -1 dBm amplitude level from the signal generator is shown in Figure 2-3. This figure proves how leaky spurs through a power supply can modulate, 10 MHz in this example, with the analog input signal frequency of 1.2 GHz. Notice the 10 MHz sidebands off the carrier signal and its intermodulation spurs within the same area.

Figure 2-3. Example of Power Supply Modulation Ratio with Forced Error Signal

#### Signal-to-Noise Ratio (SNR, dBFS)

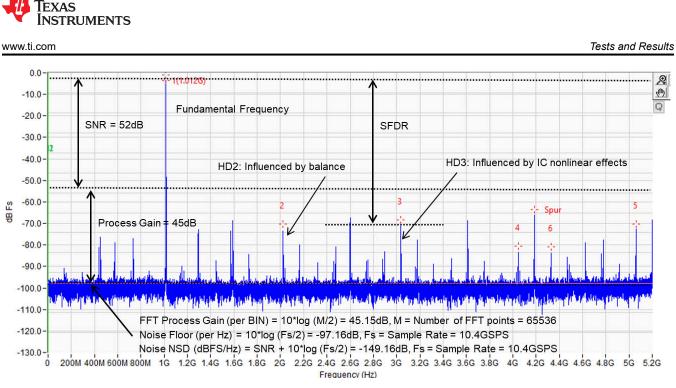

The SNR is the ratio of the rms signal amplitude to the rms value of the sum of all spectral components excluding DC, HD2 to HD9, fS / 2, fS / 2 – fIN. The difference between SNR (dBc) and SNRFS is the difference between the fundamental amplitude and full scale.

#### Harmonic Distortion (dBc or dBFS)

A harmonic is a spectral component that is an integer multiple of the driven analog input frequency. For example, the frequency of the second harmonic is twice the analog input. Most ADCs have specifications for one or more harmonics. Typically, the second and third harmonics are singled out because they account for the worst performance of all the harmonics. Harmonic distortion, no matter the order, is the ratio of the rms signal amplitude to the rms value of the specified harmonic component, reported in dBc or dBFS. ADCs are nonlinear devices, therefore output FFT captured will be rich in spectral components.

#### Spurious-Free Dynamic Range (SFDR, dBc or dBFS)

The SFDR is the ratio of the rms value of the signal to the rms value of the peak spurious spectral component for the analog input frequency that produces the worst result. In most cases, SFDR is either the second or third harmonic (HD2 or HD3) of the input signal applied to the ADC.

#### Noise Spectral Density (NSD, dBFS/Hz)

The NSD is defined the entire noise power, per unit of bandwidth, sampled at an ADC's input. NSD is effectively the ADCs' SNR plus the power of the noise spread across the entire Nyquist band, which is equal to half the sample frequency, or Fs/2. Therefore, NSD = SNR + 10\*log(Fs/2).

Figure 2-4. Test Configuration for SNR, SFDR, HD, and NSD Measurement

For a visual description of how to read SNR, SFDR, Harmonic Distortion, and NSD, refer to Figure 2-5.

Figure 2-5. FFT showing SNR, SFDR, NSD, and Harmonic Distortion

### 2.2 Test Conditions

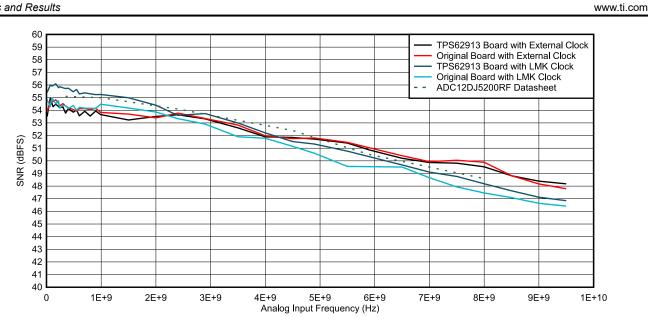

The original design and the new design with the TPS62913 were tested in identical conditions for comparison.

AC or dynamic single tone FFT tests are are made with the analog signal applied to the A/D converter at a specific set of frequencies across the converter's analog input bandwidth. A signal of -1dB below full scale (or dBFS) is used for these frequency tested at the maximum rated sampling value or 5.2 GSPS. The input supply is 12V nominal, and the ambient temperature is 25 C nominal.

The ADC is operated at the sampling clock frequency of 5.2 GHz, which is derived from an external signal generator. The test results are shown using an external clock or the on-board LMK clock. The device register settings are set per the ADC12DJ5200RF data sheet, using the GUI available on the product page, to JMODE3. The FFT is set to 65536 points with no averaging.

### 2.3 Test Results

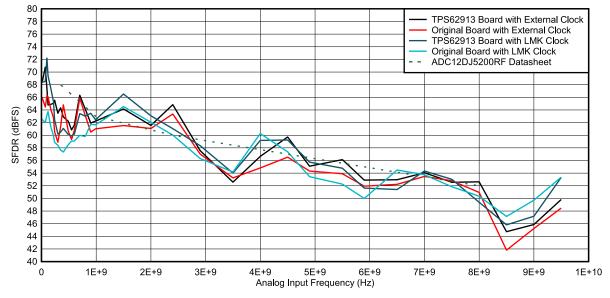

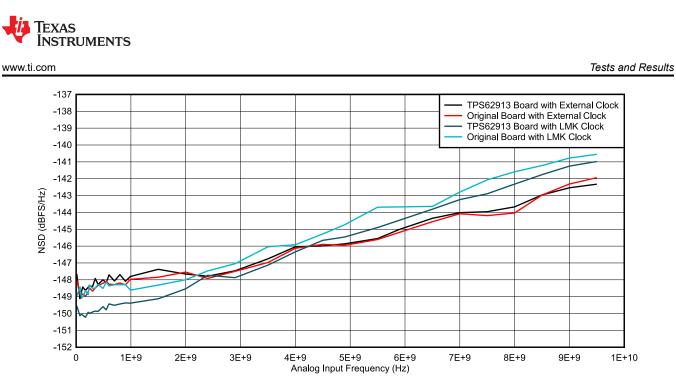

Performance tables and graphs comparing the original ADC12DJ5200RF Original EVM with the TPS62913 modified board are shown below.

| Frequency (Hz) | Original ADC12DJ5200RF EVM SNR<br>(dBFS) | TPS62913 ADC12DJ5200RF EVM SNR<br>(dBFS) |  |  |

|----------------|------------------------------------------|------------------------------------------|--|--|

| 349656677.2    | 54.345                                   | 53.771                                   |  |  |

| 989659118.7    | 53.829                                   | 53.659                                   |  |  |

| 2399751282     | 53.775                                   | 53.643                                   |  |  |

| 4499754333     | 51.754                                   | 51.846                                   |  |  |

| 5899769592     | 51.036                                   | 50.864                                   |  |  |

| 7999812317     | 49.889                                   | 49.525                                   |  |  |

Table 2-1. Signal to Noise (SNR) Comparison Table

| Table 2-2. S | Spurious-Free D | ynamic Range | (SFDR) Com | parison Table |

|--------------|-----------------|--------------|------------|---------------|

|--------------|-----------------|--------------|------------|---------------|

| Frequency (Hz) | Original ADC12DJ5200RF EVM SFDR<br>(dBFS) | TPS62913 ADC12DJ5200RF EVM SFDR<br>(dBFS) |

|----------------|-------------------------------------------|-------------------------------------------|

| 349656677.2    | 61.327                                    | 63.344                                    |

| 989659118.7    | 61.015                                    | 62.243                                    |

| 2399751282     | 63.357                                    | 64.835                                    |

| 4499754333     | 56.525                                    | 59.718                                    |

| 5899769592     | 51.946                                    | 52.896                                    |

| 7999812317     | 50.945                                    | 52.623                                    |

Figure 2-7. Spurious-Free Dynamic Range Comparison Graph

Figure 2-8. Noise Spectral Density Comparison Graph

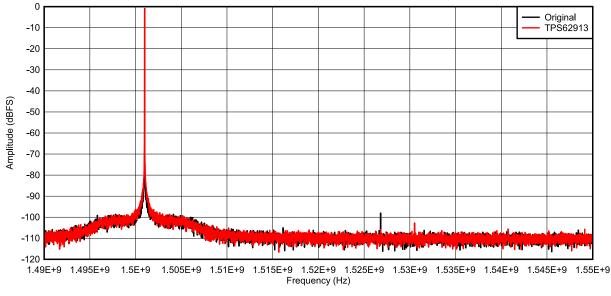

The next plot, Figure 2-9, shows how no PSMR is observed with an analog input signal frequency of 1.2 GHz applied when using the original power design with SMPS and LDO, and the TPS62913 switching supply only.

Figure 2-9. PSMR Comparison of Original and TPS62913

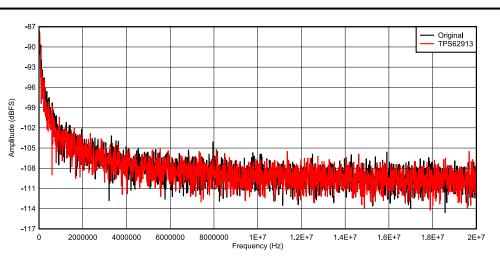

Additionally, no visible modulation of the switcher power supply spur is seen around the carrier and at DC as seen in Figure 2-10.

Figure 2-10. PSMR Comparison of Original and TPS62913 at DC

| Configuration                                         | Input Current | Input Power |

|-------------------------------------------------------|---------------|-------------|

| Original Power Supply Configuration with SMPSs + LDOs | 828.2 mA      | 9.938 W     |

| TPS62913 Power Supplies only                          | 704.3 mA      | 8.4516 W    |

| Input Current and Power Savings                       | 123.9 mA      | 1.4864 W    |

| Table 2-3. Power Loss Compar | rison |

|------------------------------|-------|

|------------------------------|-------|

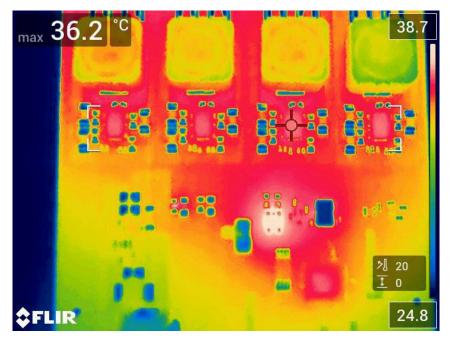

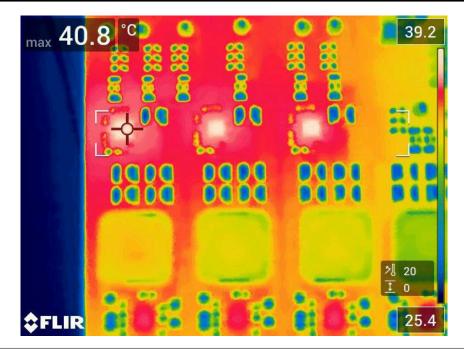

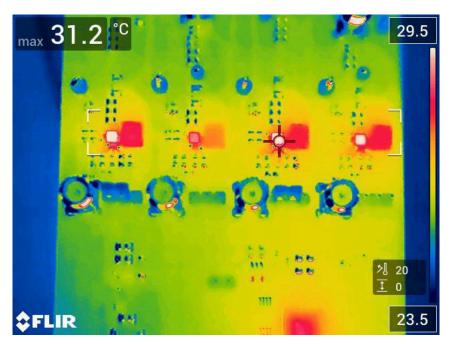

Below are thermal images of the power supplies running when taking data for the performance comparison tables.

Note

Original Board DC/DC Max Temp is 36.2 C

#### Figure 2-11. Original Switching Converters

www.ti.com

STRUMENTS

EXAS

Note

Original Board LDO Max Temp is 40.8 C

Figure 2-12. Original LDOs

Figure 2-13. TPS62913 Switching Converters

Note

TPS62913 Max Temp is 31.2 C

## **3 Conclusion**

As shown by the test results, a simplified power supply design using the TPS62913 low-ripple and low-noise buck converts can provide similar performance to the traditional SMPS + LDO approach. The Analog, Digital, and Clock rails are all supplied using the switching regulator without the need for a low-dropout linear regulator (LDO) while maintaining the same performance as the original design. The SNR, SFDR, and NSD performance is similar to the SMPS + LDO approach. Use of the TPS62913 design reduces the power consumption by 1.5W (15% power savings), reduces the size of the design, and reduces the temperature rise of the power supply components.

Although this design used the ADC12DJ5200, other ADCs that require low noise power supplies that are size constrained and thermal constrained can also use this approach. Examples of applications are RF converters in the GSPS region such as RADAR, test and measurement instrumentation, and communications.

## 4 References

Texas Instruments, ADC12DJ5200RF, 10.4-GSPS Single-Channel or 5.2-GSPS Dual-Channel, 12-bit, RF-Sampling Analog-to-Digital Converter (ADC)

References

Texas Instruments, TPS6291x 3-V to 17-V, 2-A/3-A Low Noise and Low Ripple Buck Converter with Integrated Ferrite Bead Filter Compensation

## 5 Appendix

Figure 5-1. TPS62913 3.3V Clock Power Schematic

Figure 5-3. TPS62913 VD11 ADC Power Schematic

Figure 5-4. TPS62913 VA19 ADC Power Schematic

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated