# Designing with small DC/DC converters: HotRod<sup>™</sup> QFN vs. Enhanced HotRod<sup>™</sup> QFN Packaging

1

Rich Nowakowski Product Marketing, Texas Instruments

Simon Zhao Systems Engineering, Texas Instruments

# Introduction

There have been significant advancements in semiconductor packaging in the last two decades, especially with DC/DC converters that integrate power metal-oxide semiconductor field-effect transistors (MOSFETs). Through-hole and leaded packages have been replaced with single-outline no-lead and quad flat no-lead (QFN) packages capable of handling high output currents in very small form factors. Smaller semiconductor packages often pose design and layout challenges that new packaging technologies can help resolve, and new QFN packaging technology is available for DC/DC converters with improvements over traditional wire-bond and flip-chip QFN packages. Unfortunately, DC/DC converters deliver and dissipate significant heat and are subject to package and circuit board parasitic effects, and comparing one package technology to another is often inconclusive since the die are different.

In this article, we will take a look at two point-of-load DC/DC converters, providing up to 20 A with the same die, to directly compare a traditional flip-chip HotRod<sup>™</sup> package and the new flip-chip Enhanced HotRod<sup>™</sup> QFN package, demonstrating thermal, switch-node ringing, transient, efficiency and layout differences to help you decide if the Enhanced HotRod QFN package is more advantageous for your application, and if it can help improve power-supply density and performance enough to overcome any potential skepticism around adopting new technology.

## **Design considerations**

The Enhanced HotRod QFN package includes a more flexible layout, which gives you the ability to place external components closer to the integrated circuit (IC) and reduce parasitic effects by improving the interconnect between the die and the leadframe. Increasingly, semiconductor manufacturers are designing DC/DC converters for smaller circuits, with tighter spacing inside the DC/DC converter, and in smaller packages. As such, a multilayer leadframe offers design advantages and flexibility inside the IC compared to a single-layer leadframe. For this comparison, we used an Enhanced HotRod QFN package DC/DC converter with a 0.5-mm pin pitch to more easily accommodate soldering manufacturing preferences and board-level reliability requirements.

To demonstrate the performance of each package type, we designed and built two different power supplies, attempting to make the design and operating conditions of each power supply as identical as possible. We selected the 16-V, 20-A **TPS548B27** and **TPS548B28** synchronous buck converters for the comparison. Both are available in 3-mm-by-4-mm QFN packages. The only difference between the two devices is the mechanical construction of each package.

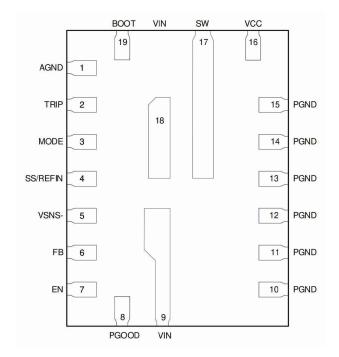

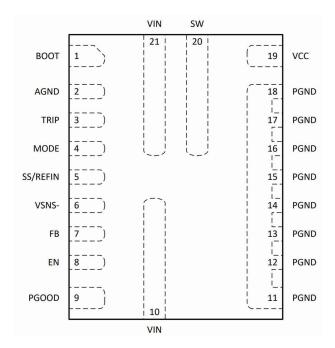

Figure 1 shows the TPS548B27 19-pin Enhanced HotRod QFN package with a 0.5-mm pin pitch. Figure 2 shows the TPS548B28 21-pin HotRod package with a 0.4-mm pin pitch. Close inspection of the pinout shows the same circuit integrated into each package. We moved several pins to the smaller sides of the Enhanced HotRod QFN package to accommodate a 0.5-mm pin pitch, and reduced the number of PGND pins. This change was made possible by the Enhanced HotRod QFN without metal rework of the die, and is a good example demonstrating the flexibility of this new package technology.

For each design, the input voltage is 12 V, the output voltage is 1 V and the output current for each device is capable of 20 A. These requirements are typical for powering a high-performance processor such as a high-current field-programmable gate array or an application-specific integrated circuit processor. A 600-kHz switching frequency was chosen for each power supply, and both designs use the Coilcraft XAL7070-301MEB inductor rated at 300 nH with a DC resistance of 1.06 m $\Omega$ . Each design also uses the same amount of ceramic input and output capacitance, in order to optimize the designs for high power density and a small solution size.

Figure 1. Enhanced HotRod QFN package example (top view)

Figure 2. HotRod package example (top view)

#### Layout comparison

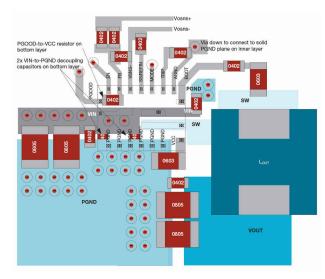

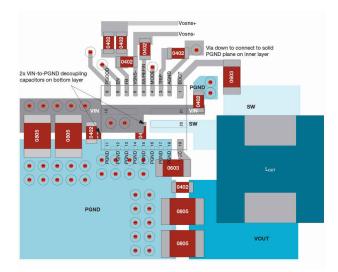

Figure 3 shows the circuit board layout for the Enhanced HotRod QFN package. Figure 4 shows the layout for the HotRod package. The evaluation module is laid out in a manner typical of a user application, with the top, bottom and internal layers using 2-ounce copper. The top-side ground traces are connected to the bottom and internal ground planes with multiple via groupings placed around the board. The input decoupling capacitors and bootstrap capacitor are all located as close to the IC as possible in each design. An additional input bulk capacitor was used to limit the noise entering the converter from the input supply, and terminated critical noise-sensitive analog circuits to the quiet analog ground island on the top layer. The layout of each design is very similar, in order to make it easier to detect any difference in performance between the two packages.

Figure 3. Enhanced HotRod QFN package layout

Figure 4. HotRod package layout

# **Thermal comparison**

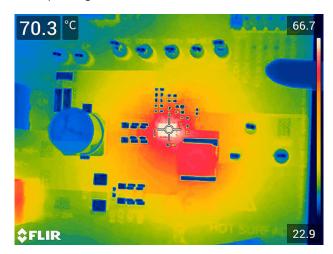

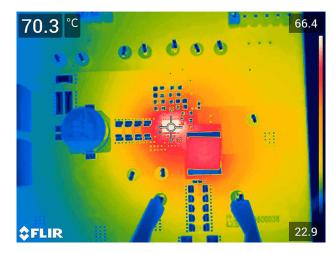

Each circuit board was operated at a 15-A current and measured the IC temperature of each design while operating under the same conditions. The IC temperature of the Enhanced HotRod QFN package was 70.3°C, shown in **Figure 5**. The HotRod package was also 70.3°C, shown in **Figure 6**. No other notable differences were observed. It is safe to conclude that any temperature variation between the two package examples would likely be caused by the IC's lot-tolot process variations, such as the drain-to-source onresistance ( $R_{DS(on)}$ ) or the switching frequency. The Enhanced HotRod QFN package offered no improvement or degradation of thermal performance compared to the HotRod package.

Figure 5. Enhanced HotRod QFN package thermal image

*Figure 6.* HotRod package thermal image

# **Efficiency comparison**

Table 1 shows the efficiency and power-dissipationcomparisons between the two packages. A 3.3-V biaswas applied to the VCC pin of each device in order toeliminate any losses from the internal linear regulator,which provides power to the IC. Linear regulatorlosses may differ from lot-to-lot process variations;you can remove them by applying the external 3.3-V bias voltage and obtaining the closest efficiencycomparison. The efficiency and power-dissipation resultsfrom each package are very similar, but the HotRodpackage design had 50 mW less power dissipated,or 0.2% higher efficiency, at only 15 A, which is

negligible. The Enhanced HotRod QFN package offered no improvement, with the slightest degradation of efficiency compared to the HotRod package.

| Package                           | IOUT (A) | Efficiency | Dissipation (W) |

|-----------------------------------|----------|------------|-----------------|

| Enhanced<br>HotRod QFN<br>package | 5.0      | 90.1%      | 0.55            |

|                                   | 10.0     | 89.6%      | 1.16            |

| paonago                           | 15.0     | 87.2%      | 2.21            |

|                                   | 20.0     | 84.6%      | 3.65            |

| HotRod                            | 5.0      | 90.1%      | 0.55            |

| package                           | 10.0     | 89.6%      | 1.16            |

|                                   | 15.0     | 87.4%      | 2.16            |

|                                   | 20.0     | 84.6%      | 3.65            |

Table 1. Efficiency comparison: 12-V input, 1-V output

#### Load transient comparison

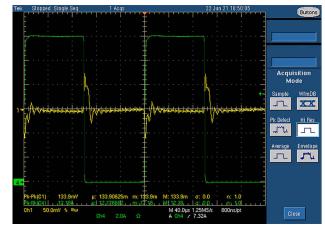

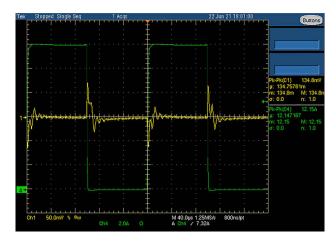

A load transient test was performed with a 0% to 60% load step at a 20-A full-load condition, or 0 A to 12 A and then 12 A to 0 A. The rising load step had an 8-A/µs slew rate. When comparing the transient response waveforms shown in **Figure 7** and **Figure 8**, the Enhanced HotRod QFN package design was very similar to the HotRod package design, with only a 1-mV difference between the total output voltage overshoot and undershoot, because of the load transient. The Enhanced HotRod QFN design offered a hardly noticeable, but very slight improvement of load transient performance compared to the HotRod package. **Table 2** shows the results.

| Package                           | VIN  | VOUT | FSW        | Load<br>step   | Slew<br>Rate | Vpeak-<br>peak |

|-----------------------------------|------|------|------------|----------------|--------------|----------------|

| Enhanced<br>HotRod QFN<br>package | 12 V | 1 V  | 600<br>kHz | 0 A to<br>12 A | 8 A/µs       | 133.9<br>mV    |

| HotRod<br>package                 |      |      | KHZ        |                |              | 134.8<br>mV    |

Table 2. Load transient conditions and results

Figure 7. Enhanced HodRod QFN package transient response

Figure 8. HotRod package transient response

## Switch-node ringing comparison

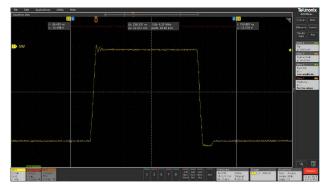

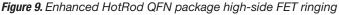

The effects of parasitic inductance are visible when observing the switch-note ringing of the power supply's high-side MOSFET. Under close inspection of **Figure 9** and **Figure 10**, the voltage overshoot of the Enhanced HotRod QFN package design was 0.1 V lower than the HotRod package design shown in **Table 3**, which is noticeable. It is difficult to ascertain where the difference in voltage ringing originates, but it is safe to assume that the Enhanced HotRod QFN package does not degrade switch-node ringing performance. It is probable, however, that mechanical construction of the Enhanced HotRod QFN package slightly improves switch-node ringing of the high-side MOSFET by reducing the internal parasitic inductance of the IC.

| Package                        | VIN  | VOUT | FSW     | Ringing |

|--------------------------------|------|------|---------|---------|

| Enhanced HotRod<br>QFN package | 12 V | 1 V  | 600 kHz | 0.7 V   |

| HotRod package                 |      |      |         | 0.8 V   |

Table 3. Switch-node ringing conditions and results

Figure 10. HotRod package high-side FET ringing

## Conclusion

The Enhanced HotRod QFN package offered no noteworthy degradation of performance compared to the HotRod package under the established operating conditions. Under very close inspection, the power dissipation showed a difference of 50 mW, but only at 15-A load current. On the other hand, the Enhanced HotRod QFN package offered a 0.1-V improvement in switch-node ringing and a 1-mV improvement in load transient output voltage overshoot and undershoot, which is relatively negligible. **Table 4** summarizes the results.

| Package                   | Enhanced HotRod<br>QFN package | HotRod QFN    |

|---------------------------|--------------------------------|---------------|

| Temperature at 15 A       | 70.3°C                         | 70.3°C        |

| Efficiency difference     | 87.2% at 15 A                  | 87.4% at 15 A |

| VOUT over- and undershoot | 133.9 mV                       | 134.8 mV      |

| Ringing                   | 0.7 V                          | 0.8 V         |

Table 4. Results summary

It is easy to view new packaging technologies with skepticism, since comparison results are often inconclusive, with too many variables. In this case, however, the circuit differences are minimal and the measurement results are very similar. Designing with the Enhanced HotRod QFN package is a low-risk alternative when new DC/DC converters become available using the package, and allows suppliers to address parasitic effects inside the package.

The Enhanced HotRod QFN package offers a novel approach to improving the footprint of the integrated circuit and achieving better ringing performance and has the potential to provide a more user-friendly and flexible layout compared to other existing packaging technologies.

#### **Additional Resources**

- Enhanced HotRod™ QFN Package: Achieving Low EMI Performance in Industry's Smallest 4-A Converter

- HotRod QFN

- Understanding Flip Chip QFN (HotRod) and Standard QFN Performance Differences

**Important Notice:** The products and services of Texas Instruments Incorporated and its subsidiaries described herein are sold subject to TI's standard terms and conditions of sale. Customers are advised to obtain the most current and complete information about TI products and services before placing orders. TI assumes no liability for applications assistance, customer's applications or product designs, software performance, or infringement of patents. The publication of information regarding any other company's products or services does not constitute TI's approval, warranty or endorsement thereof.

HotRod<sup>™</sup> and Enhanced HotRod<sup>™</sup> are trademarks of Texas Instruments. All trademarks are the property of their respective owners.

© 2021 Texas Instruments Incorporated

Power

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated