# Using a second stage filter to reduce voltage ripple

Rich Nowakowski Product Marketing Engineer

# Sarmad Abedin

Power Design Services Engineer

### Introduction

Advanced processors and system-on-chip (SoC) with integrated point-to-point serial communication or an analog front end (AFE) require a power supply with low output-voltage ripple to maintain signal integrity and improve performance. The output-voltage ripple requirement of the processor's point-of-load (POL) power supply can be below 2-mV, which is about one-tenth of the ripple for a typical design, putting heavy design constraint on the synchronous buck converter. Since the processor's output current requirements exceed the capabilities of a linear post-regulator, employing a second-stage filter, a higher switching frequency and additional output capacitance greatly reduce the POL's ripple. Synchronous-buck converters are available with several different control architectures, each having a unique method to ensure stability when designing for low-ripple voltage. This article compares three different control architectures: externally-compensated voltagemode, constant on-time and selectable-compensation current-mode to achieve 1-mV output voltage ripple complete with test data using the same electrical specifications and comparison of output voltage ripple, solution size, load transients and efficiency.

### Selecting and bounding the application

Three different power supplies were designed and built to demonstrate the performance of each control mode under similar operating conditions. For each design, the input voltage is 12 V, the output voltage is 1 V and the output current for each device is capable of 15-A. These requirements are typical for powering a high-performance SoC that integrates sensitive analog circuitry, requiring low output voltage ripple.

To bound the filter design and performance expectations, the allowable ripple voltage is ±0.15 percent, or ±1.5 mV (3 mVpp) of the output voltage. Our comparison features three TI DC/DC converters: a 15-A D-CAP3<sup>™</sup> buck converter (**TPS548A28**), a 20-A internally compensated advanced current-mode (ACM) buck converter (**TPS543B22**) and a 15-A voltage-mode buck converter (**TPS56121**). We selected output voltage, output current and operating frequencies as close as possible to one another within the converter's capability to support similar second-stage filter components.

### Designing the second-stage filter

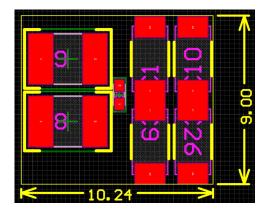

Even with low equivalent series resistance (ESR) ceramic output capacitors, it is not practical to use a buck converter's inductor and capacitor (LC) output filter to achieve low output voltage ripple. Designers will likely need to use a second-stage LC filter in order to achieve output ripple below 5-mV. For more information about the design of a second-stage filter or the ripple measuring techniques, please see resources section. The value of the inductor of the second-stage filter can be calculated using Equation 1 and solving for L2. The inductor L2 is the second-stage inductor, C1 is the primary-stage output capacitor of the buck converter, and C2 is the second-stage capacitor network. For all three designs, the same second-stage filter was used (as shown in Table 1), occupying a circuit board area of 92mm<sup>2</sup> (as shown in Figure 1).

Switching Frequency =  $1/(2\pi^*\sqrt{L2^*Cs})$ , where Cs = 1/(1) $\left(\frac{1}{C1} + \frac{1}{C2}\right)$

| Part<br>Number | Control<br>Architecture | Switching<br>Frequency | Second-<br>Stage<br>Inductance | Second-<br>Stage<br>Capacitance |

|----------------|-------------------------|------------------------|--------------------------------|---------------------------------|

| TPS548A28      | D-CAP3                  | 800 kHz                | 2 x 0.68 µH                    | 4x 100 μF +<br>0.1 μF           |

| TPS543B22      | ACM                     | 1000 kHz               | 2 x 0.68 µH                    | 4x 100 μF +<br>0.1 μF           |

| TPS56121       | Voltage-<br>Mode        | 500 kHz                | 2 x 0.68 µH                    | 4 x 100 μF +<br>0.1 μF          |

Table 1. Converter control architecture and second-stage filter.

Figure 1. Circuit board area of second-stage filter at 92mm<sup>2</sup>.

Once the second-stage inductor value (L2) is chosen and the components are assembled, the next step is to re-compensate the DC/DC converter's control loop with the addition of the second-stage inductance and capacitance to ensure stability. It is important to mention that each control architecture has its own unique technique to re-compensate the control loop after adding the second stage filter, if needed. The output voltage ripple, efficiency penalty and stability of each control architecture were evaluated and then summarized the results.

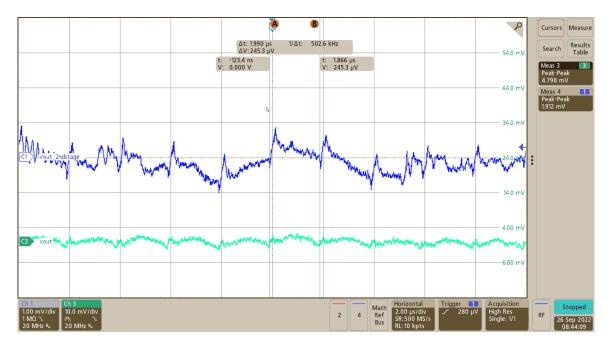

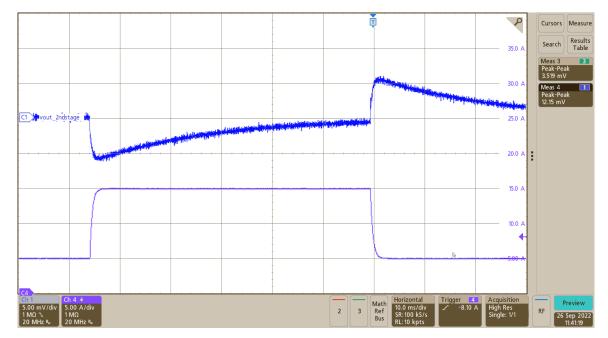

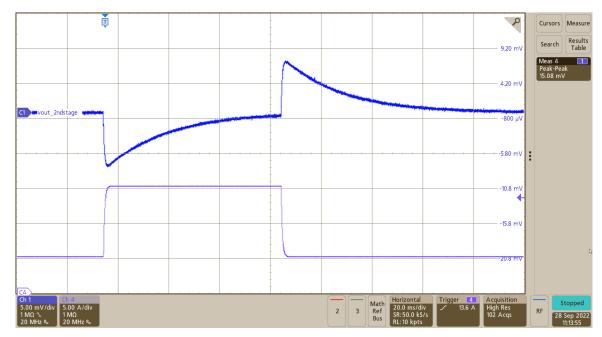

### Voltage-mode control architecture

Pulse-width modulation (PWM) with voltage-mode control architecture is accomplished by comparing a voltage error signal from the output voltage and reference voltage to a constant sawtooth-ramp waveform. The ramp is initiated by a clock signal from an oscillator. The TPS56121 employs externallycompensated, type-3 compensation addressing a double-pole power stage that allows the converter to be re-compensated after the addition of a second-stage filter. Adjusting external resistor and capacitor values after the addition of a second stage filter ensures stability. The output voltage peak-to-peak ripple without an additional filter is 4.8-mV. With the additional filter applied, the output voltage ripple is 1.9-mV (as shown in Figure 2). In this case, the TPS56121 design required no loop compensation adjustments to ensure stability. Figure 3 shows a load transient waveform with a 10-A load-step, and the output voltage waveform after the implementation of the second-stage filter shows no sign of instability.

Figure 2. TPS56121 output voltage ripple with and without additional second-stage filter.

Figure 3. Transient response of TPS56121 using voltage-mode control.

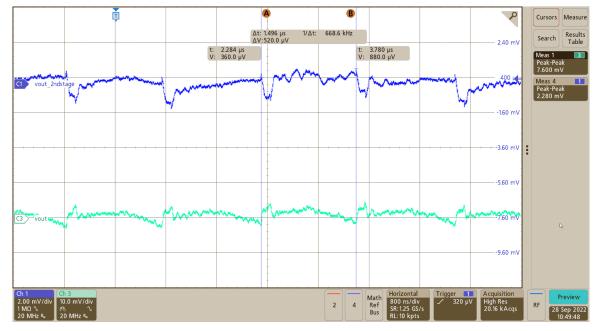

#### **D-CAP3 control architecture**

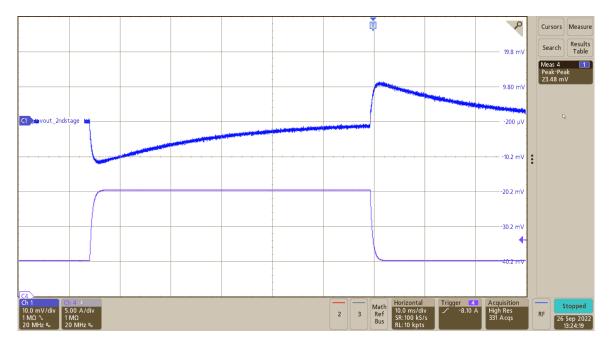

D-CAP3 uses a one-shot timer to generate an on-time pulse that is proportional to the input voltage and the output voltage. When the falling feedback voltage equals the reference voltage, a new PWM on-pulse is generated. The ramp is emulated by the output inductor. A signal from an internal ripple-injection circuit is fed directly into the comparator with its offset voltage eliminated, reducing the need for output voltage ripple from the capacitor's ESR. One advantage of D-CAP3 and other constant on-time converters is additional loop compensation circuitry is not required. But, the control loop may have the ability adjusted by an adjustable ramp, if the device supports this feature, and the addition of feed forward capacitance at the output voltage feedback resistor divider network. The **TPS548A28** output voltage peak-to-peak ripple without an additional filter is 7.6-mV. With the additional filter applied, the output voltage ripple is 2.3-mV (as shown in **Figure 4**). In this case, the **TPS548A28** design required

no adjustments to ensure stability. **Figure 5** shows a load transient waveform with the same 10-A load-step as the previous converter, and the output voltage waveform after the implementation of the second-stage filter shows no sign of instability.

Figure 4. TPS548A28 output voltage ripple with and without additional second-stage filter.

Figure 5. Transient response of TPS548A28 using D-CAP3 control.

# Advanced current mode (ACM) control architecture

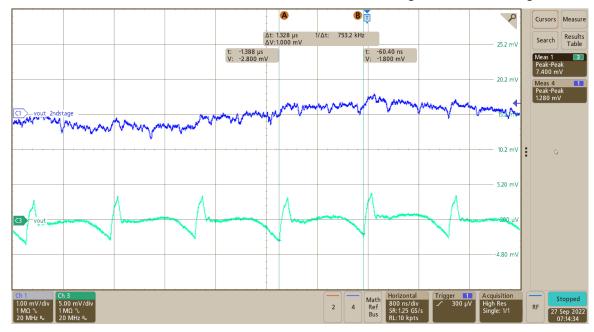

Internally-compensated ACM is a ripple-based, peakcurrent-mode control scheme that uses an internally generated ramp to represent the inductor current. This control mode provides a balance between the faster transient response of non-linear control modes, like D-CAP3, and the broad capacitor stability of other externally-compensated, fixed-frequency control architectures, like voltage-mode control. ACM is a newer control architecture that allows the loop to be compensated with a single resistor instead of a resistor and capacitor network. The **TPS543B22** has three selectable PWM ramp options to optimize the control loop performance when a second stage filter is implemented. Interestingly, we noticed that its evaluation module has capacitor and inductor solder pads on the circuit board to conveniently accommodate secondstage filter components. The **TPS543B22** output voltage peak-to-peak ripple without an additional filter is 7.4mV. With the additional filter applied, the output voltage ripple is 1.3-mV (as shown in **Figure 6**). The **TPS543B22** design required no adjustments to the ramp to ensure stability. **Figure 7** shows a load transient waveform with the same 10-A load-step as the previous converter, and the output voltage waveform after the implementation of the second-stage filter shows no sign of instability.

Figure 6. TPS543B22 output voltage ripple with and without additional second-stage filter.

Figure 7. Transient response of TPS543B22 using ACM control.

### **Efficiency penalty**

The full-load efficiency of each DC/DC converter was measured with and without the additional second-stage filter to compare the power losses. The results are shown in **Table 2**. The second-stage filter contributes negligible power loss and efficiency penalty. The deficiency and power loss differences were measured because each DC/DC converter has unique power MOSFETs, which lead to an inaccurate efficiency conclusion. It is the designer's decision to determine if the efficiency penalty and additional required board space of 92mm<sup>2</sup> is worth the output voltage ripple improvement.

Designers have traditionally used an additional low dropout (LDO) regulator to post-regulate the output voltage of a DC/DC converter and achieve low output voltage ripple. If a designer prefers to use anLDO instead of a second-stage filter, the 4-A **TPS7A54** can be paralleled to provide up to 8-A. For example, if the LDO has a 175-mV voltage drop, two LDOs will dissipate 1.4-W at 8-A versus 0.02-W of the second-stage filter. The LDO will have a lower output voltage ripple noise of 4  $\mu$ V, but if the second-stage filter provides acceptable low output voltage ripple for the SoC and AFE, the advantages are a smaller design, less power loss and lower component cost.

| P/N       | lout (A) | Filter                 | Efficiency | Power Loss<br>(W) |

|-----------|----------|------------------------|------------|-------------------|

| TPS543B22 | 15       | Primary                | 86.43%     | 2.358             |

|           |          | Primary +<br>Secondary | 86.33%     | 2.378             |

|           |          | Difference             | -0.1%      | -0.02             |

| TPS548A28 | 15       | Primary                | 83.98%     | 2.829             |

|           |          | Primary +<br>Secondary | 83.87%     | 2.850             |

|           |          | Difference             | -0.11%     | -0.021            |

| TPS56121  | 15       | Primary                | 89.19%     | 1.834             |

|           |          | Primary +<br>Secondary | 89.34%     | 1.806             |

|           |          | Difference             | -0.15%     | -0.028            |

Table 2. Efficiency and power loss comparison.

## Conclusion

A second-stage filter is an easy, small, efficient and low-cost solution to design and provide low output voltage ripple for high current loads. There is no perfect control mode for every design situation, but a secondstage filter can be implemented in many buck converter control architectures. If you are designing with a network interface card SoC or a remote radio unit using an AFE, a second-stage filter will provide much lower ripple than a standard buck converter. **Table 3** summarizes the ripple and the efficiency and size trade-offs associated with each device.

| Device        | Current<br>Capability<br>(A) | Control<br>Architectu<br>re | Ripple<br>Voltage<br>(mV) | Filter Size       | Power<br>Loss<br>penalty<br>(W) |

|---------------|------------------------------|-----------------------------|---------------------------|-------------------|---------------------------------|

| TPS543B2<br>2 | 20                           | ACM                         | 1.3                       | 92mm <sup>2</sup> | 0.020                           |

| TPS548A2<br>8 | 15                           | D-CAP3                      | 2.3                       | 92mm <sup>2</sup> | 0.021                           |

| TPS56121      | 15                           | Voltage<br>Mode             | 1.9                       | 92mm <sup>2</sup> | 0.028                           |

Table 3. Ripple, size and efficiency trade-offs.

## References

- 1. Texas Instruments: Power Tips: Designing a twostage LC filter

- 2. Texas Instruments: *Reducing noise on the output of a switching regulator*

- 3. Texas Instruments: *Control-Mode Quick Reference Guide -Step-Down Non-Isolated DC/DC*

# **Related Websites**

- **TPS548A28** 2.7-V to 16-V, 15-A synchronous buck converter with remote sense and 3-V LDO

- TPS543B22 4-V to 18-V input, advanced current mode, 20-A synchronous SWIFT<sup>™</sup> step-down converter

- **TPS56121** 4.5-V to 14-V, 15-A synchronous SWIFT™ buck converter

- **TPS7A54** 4-A, low-VIN (1.1-V), low-noise, highaccuracy, ultra-low dropout voltage regulator

**Important Notice:** The products and services of Texas Instruments Incorporated and its subsidiaries described herein are sold subject to TI's standard terms and conditions of sale. Customers are advised to obtain the most current and complete information about TI products and services before placing orders. TI assumes no liability for applications assistance, customer's applications or product designs, software performance, or infringement of patents. The publication of information regarding any other company's products or services does not constitute TI's approval, warranty or endorsement thereof.

All trademarks are the property of their respective owners.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated