# DP83869 1000Base-X Link Detection

## Aniruddha Khadye

#### **ABSTRACT**

The DP83869 supports multiple operating modes as defined in the DP83869 data sheet. This application note is only applicable while the DP83869 is operating in RGMII-to-1000Base-X mode and Gigabit Media Converter mode.

When the DP83869 is used in 1000Base-X mode or Gigabit Media Converter mode, register monitoring at start-up is necessary to confirm that the link is established. In the case that the link is not established, this application note provides details on remedial actions that can be taken to establish the link.

|   | Contents                                      |   |

|---|-----------------------------------------------|---|

| 1 | Introduction                                  | 2 |

| 2 | 1000Base-X Link-Up                            | 2 |

| 3 | Example Flowchart                             | 3 |

| 1 | List of Figures  1000Base-X Link-Up Flowchart | 3 |

|   | List of Tables                                |   |

| 1 | 1000Base-X Link-Up Table                      | 2 |

### **Trademarks**

All trademarks are the property of their respective owners.

Introduction www.ti.com

#### 1 Introduction

When an Ethernet communication system uses a discrete Ethernet PHY, the PHY is generally connected to a host controller with a MAC entity. The MAC sends and receives Ethernet data through the PHY through standard MAC interfaces (RGMII, SGMII, and so forth). The host controller uses the Serial Management Interface (MDC and MDIO signals) to check the PHY status and configuration.

Typically, after power up, reset or link loss, a host controller polls for the link up status before it attempts to initiate the data transfer over the MAC interface. The link status is stored in PHY registers for the host controller to read via the MDIO-MDC interface. In RGMII-to-1000Base-X mode or Gigabit Media Converter mode, reading additional bits is required to ensure to verify that auto negotiation and link-up successfully completed. Under certain conditions, additional intervention by the host controller may be necessary. This is described in the following sections.

## 2 1000Base-X Link-Up

The DP83869 1000Base-X link status is stored in the FX\_STS register bit [1] (0xC01[1]). If this bit is 1, then the link is valid. If this bit is 0, then there is no link.

Along with the FX\_STS register, the host controller must also check the Serdes Synchronization status bit in the SERDES\_SYNC\_STS register (0x4F[8]). This bit indicates if a valid signal from link partner is detected. If this bit is 1, then synchronization is established, but if the bit is 0, then synchronization is not established.

In most cases, when the Serdes Synchronization status bit is set, the PHY is able to complete autonegotiation and achieve a successful 1000Base-X link-up (FX\_STS bit[1]=1). However, in rare cases, the link is not established even when the Serdes Synchronization status bit is set to 1 (FX\_STS bit[1] =0). In such cases, the host controller must write 1 to FX\_CTRL register (0xC00[9]) to restart auto negotiation. Table 1 lists the possible combinations of the link status bit and Serdes Sync status bit, the interpretation for each condition, and any follow-up action that should be undertaken by the host controller.

SERDES SYNC STATUS BIT **LINK STATUS BIT** COMMENTS 0xC01[1] 0x4F[8] No valid signal detected from link partner 0 0 Valid signal detected and synchronization 0 established but no link up. Restart auto negotiation through the 0xC00[9] register Link-up successful 1 1 Not Applicable. Link will not be established if 1 0 SerDes does not have synchronization.

Table 1. 1000Base-X Link-Up Table

www.ti.com Example Flowchart

## 3 Example Flowchart

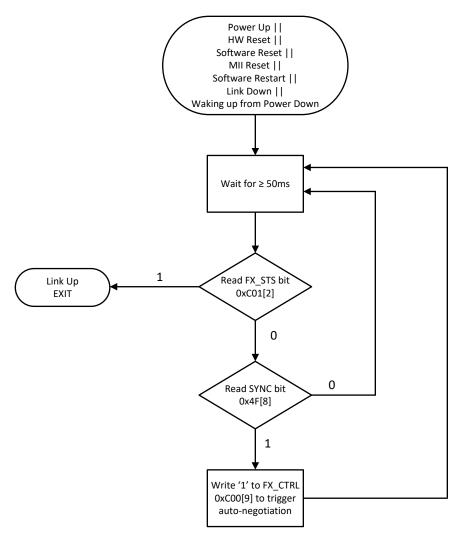

Figure 1 shows an example of how a host controller can implement the logic for restarting auto negotiation.

Figure 1. 1000Base-X Link-Up Flowchart

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated