# Application Report Splitter Mode Operations With the DS90Ux941AS-Q1

# TEXAS INSTRUMENTS

Davor Glisic, Casey McCrea

#### ABSTRACT

More and more In-Vehicle Infotainment (IVI) systems use multiple displays for delivering entertainment and information content to end users, but using multiple application processors (APs) to drive multiple displays, or developing APs that can drive multiple displays, can be expensive. The DS90Ux941AS-Q1 brings functionality that allows designs of more economical IVI system designs with only a single AP for delivering content to two symmetric or asymmetric displays. In these systems, the AP receives and combines two video frames into a superframe while the DS90Ux941AS-Q1 performs splitting of the superframe, and forwarding of the resultant frames, to the compatible FPD-Link III deserializers and attached displays.

The DS90Ux941AS-Q1 is compatible with the FPD-Link III DS90Ux948-Q1, DS90Ux928Q-Q1, or DS90Ux926Q-Q1 deserializers, and can supply 1- or 2-lane high-speed serial streams over cost-effective,  $50-\Omega$ , single-ended coaxial cables or  $100-\Omega$ , differential shielded twisted-pair (STP) and shielded twisted-quad (STQ) cables.

This application report discusses superframe formatting requirements, provides guidance on configuring the DS90Ux941AS-Q1 for splitter applications, and gives programming examples.

# **Table of Contents**

| 1 Introduction                                                                  | 3              |

|---------------------------------------------------------------------------------|----------------|

| 2 Superframe Requirements                                                       | 4              |

| 2.1 Left/Right 3D Format                                                        |                |

| 2.2 Alternate Line 3D Format                                                    | <mark>5</mark> |

| 2.3 Alternate Pixel 3D Format                                                   | <mark>6</mark> |

| 3 Video Processing Status Monitoring                                            |                |

| 3.1 VIDEO_3D_STS Register (Address = 58h) [reset = 0h]                          |                |

| 4 Superframe Splitting                                                          |                |

| 5 Frame Cropping                                                                | 9              |

| 5.1 Cropping Control Registers                                                  |                |

| 5.2 Cropping Options                                                            |                |

| 6 Splitter Mode Pixel Clocks                                                    |                |

| 6.1 SPLIT_CLK_CTL0_SPLIT_CLK_CTL0_P1 Register (Address = 3Eh) [reset = 81h]     | 15             |

| 6.2 SPLIT_CLK_CTL1_SPLIT_CLK_CTL1_P1 Register (Address = 3Fh) [reset = 2h]      |                |

| 7 Programming Example                                                           |                |

| 8 Summary                                                                       |                |

| 9 References                                                                    |                |

| 10 Handling Interrupts With the DS90Ux941AS-Q1                                  |                |

| 10.1 Interrupt Control and Status (INTB and REM_INTB Pin)                       |                |

| 10.2 Handling Interrupts in Splitter Mode Using Remote Interrupt Pin (REM_INTB) |                |

| 10.3 REM_INTB_CTRL Register (Address = 30h) [reset = 0h]                        |                |

| 11 High-Speed GPIO Operation in Splitter Mode                                   |                |

| 11.1 Introduction                                                               |                |

| 11.2 High-Speed Control Configuration                                           |                |

| 11.3 Back Channel Frequency Configuration                                       |                |

| 11.4 Splitter Mode GPIO                                                         |                |

| 11.5 GPIO_0_Config Register (Address = Dh) [reset = 20h]                        |                |

| 11.6 GPIO_1_and_GPIO_2_Config Register (Address = Eh) [reset = 0h]              |                |

| 11.7 GPIO_3_Config Register (Address = Fh) [reset = 0h]                         |                |

| Revision History                                                                | 28             |

1

# List of Figures

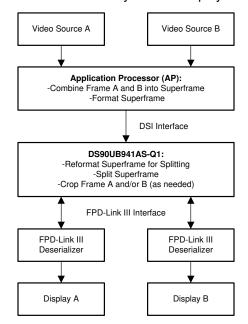

| Figure 1-1. Superframe Creation and Splitting System Block Diagram              | 3              |

|---------------------------------------------------------------------------------|----------------|

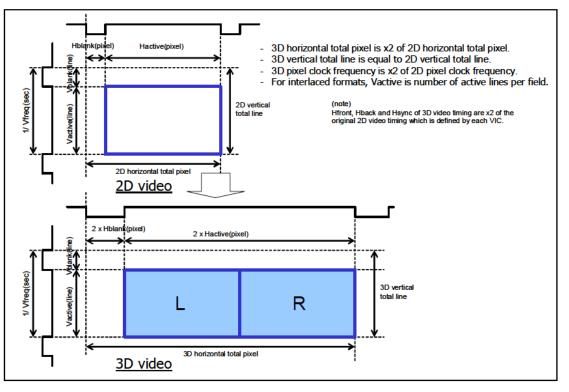

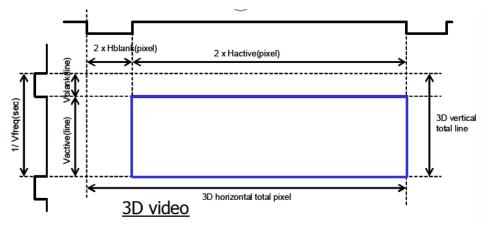

| Figure 2-1. HDMI 1.4b Side-by-Side (Full) 3D Format                             | 4              |

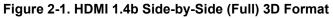

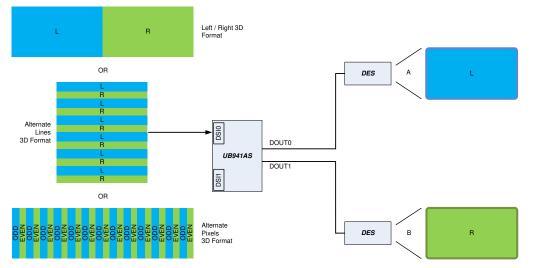

| Figure 2-2. HDMI 1.4b Alternate Line 3D Format                                  |                |

| Figure 2-3. HDMI 1.4b Alternate Pixel 3D Format                                 |                |

| Figure 4-1. Symmetric Splitting                                                 | <mark>8</mark> |

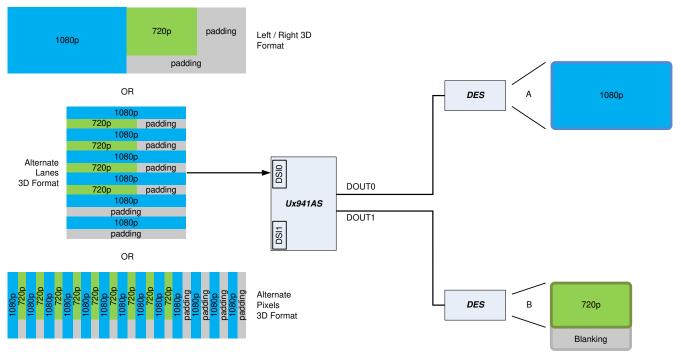

| Figure 5-1. Asymmetric Splitting With Cropping                                  |                |

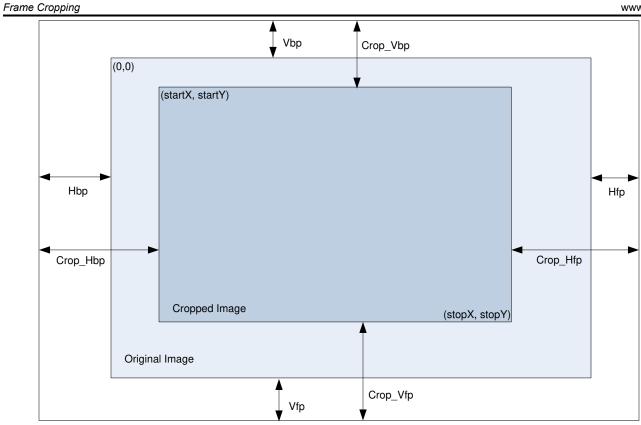

| Figure 5-2. Cropping Example.                                                   |                |

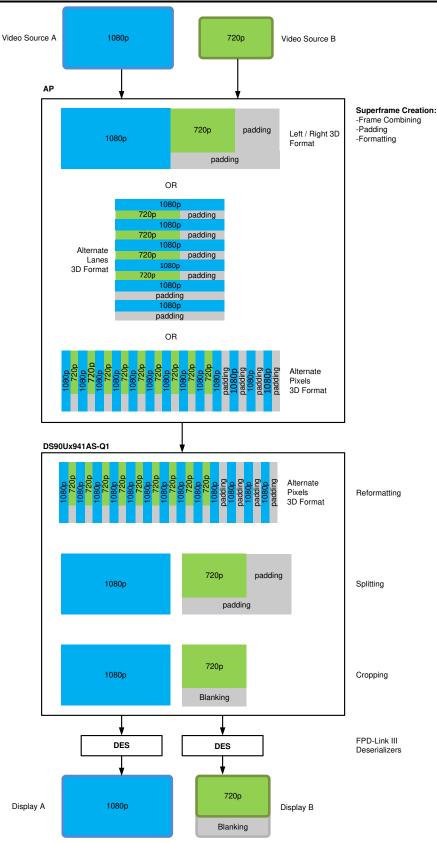

| Figure 8-1. Superframe Creation and Splitting Flow Diagram                      |                |

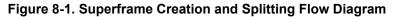

| Figure 10-1. Receiver Interrupt Propagation Block Diagram                       |                |

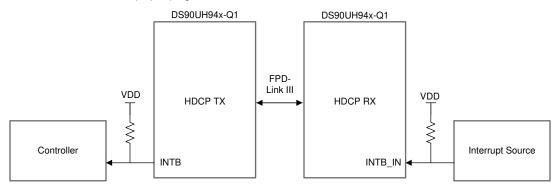

| Figure 10-2. Interrupt Propagation in Splitter Mode Block Diagram               |                |

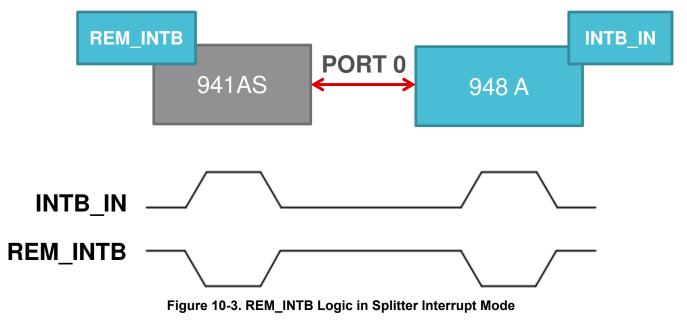

| Figure 10-3. REM_INTB Logic in Splitter Interrupt Mode                          |                |

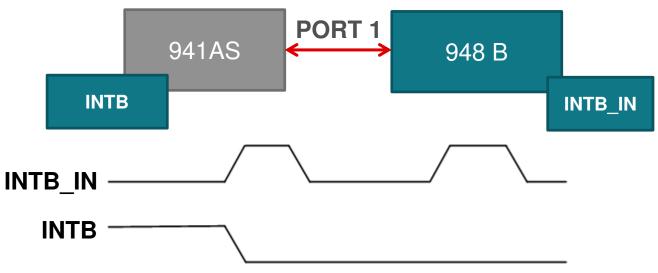

| Figure 10-4. INTB Logic in Splitter Interrupt Mode                              |                |

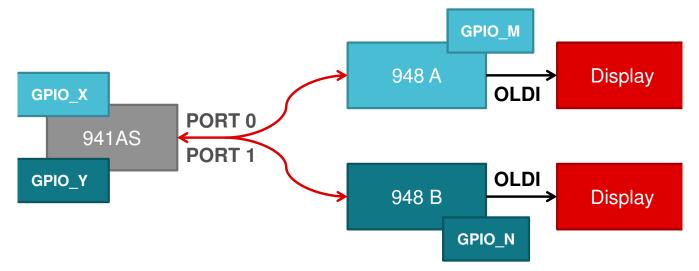

| Figure 10-5. Example Splitter Mode Interrupt Routing With Standard GPIO Signals |                |

| Figure 10-6. Example GPIO Logic with Standard GPIO Pass-Throughs                |                |

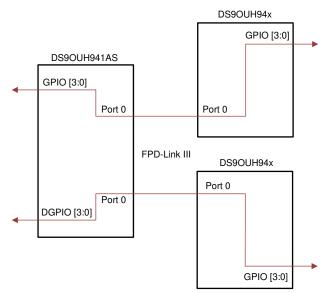

| Figure 11-1. Splitter Mode GPIO Block Diagram                                   | 26             |

# List of Tables

| Table 3-1. VIDEO_3D_STS Register Field Descriptions                     | 7   |

|-------------------------------------------------------------------------|-----|

| Table 5-1. CROP_START_X0_CROP_START_X0_P1 Register Field Descriptions   | 11  |

| Table 5-2. CROP_START_X1_CROP_START_X1_P1 Register Field Descriptions   |     |

| Table 5-3. CROP_STOP_X0_CROP_STOP_X0_P1 Register Field Descriptions     | .11 |

| Table 5-4. CROP_STOP_X1_CROP_STOP_X1_P1 Register Field Descriptions     | .11 |

| Table 5-5. CROP_START_Y0_CROP_START_Y0_P1 Register Field Descriptions   | 12  |

| Table 5-6. CROP_START_Y1_CROP_START_Y1_P1 Register Field Descriptions   | 12  |

| Table 5-7. CROP_STOP_Y0_CROP_STOP_Y0_P1 Register Field Descriptions     |     |

| Table 5-8. CROP_STOP_Y1_CROP_STOP_Y1_P1 Register Field Descriptions     |     |

| Table 6-1. SPLIT_CLK_CTL0_SPLIT_CLK_CTL0_P1 Register Field Descriptions |     |

| Table 6-2. SPLIT_CLK_CTL1_SPLIT_CLK_CTL1_P1 Register Field Descriptions |     |

| Table 10-1. REM_INTB_CTRL Register Field Description                    | 22  |

| Table 11-1. DES_CAP1 Register Field Description                         |     |

| Table 11-2. DES_CAP2 Register Field Description                         |     |

| Table 11-3. Back Channel Frequency Settings                             |     |

| Table 11-4. GPIO_0_Config Register Field Descriptions                   |     |

| Table 11-5. GPIO_1_and_GPIO_2_Config Register Field Descriptions        |     |

| Table 11-6. GPIO_1_and_GPIO_2_Config Register Field Descriptions        | 28  |

# Trademarks

All trademarks are the property of their respective owners.

# **1** Introduction

The DS90Ux941AS-Q1 splitter and cropping functions allow system designers to use cost-effective IVI systems with only a single AP for delivering content to two symmetric or asymmetric displays. An application processor can receive and combine two video frames into a superframe, and perform the necessary video data formatting to ensure that the data is compatible with the DS90Ux941AS-Q1 signal processing functions (see Figure 1-1). The DS90Ux941AS-Q1 performs further video formatting and splits of the superframe into two symmetric frames before forwarding them to the compatible FPD-Link III deserializers and attached displays. If necessary, the DS90Ux941AS-Q1 can also crop either one or both resultant frames for the formation of asymmetric frames before forwarding the frames to the deserializers and asymmetric displays.

Figure 1-1. Superframe Creation and Splitting System Block Diagram

3

# **2 Superframe Requirements**

The DS90Ux941AS-Q1 supports superframe options with the following formats:

- Left/Right 3D format

- Alternate Line 3D format

- Alternate Pixel 3D format

For the first two options, the DS90Ux941AS-Q1 reorganizes the superframe into an alternating pixel format for easy splitting at the DS90Ux941AS-Q1 output. For the Alternate Pixel option, the superframe is already in the proper format for splitting.

For proper transition between operating modes, only enable 3D modes when the DSI input is disabled.

# 2.1 Left/Right 3D Format

The DS90Ux941AS-Q1 can format a superframe as a dual side-by-side (left or right) image consistent with the side-by-side 3D format specified in the HDMI 1.4b specification. The system designer can reprogram the DS90Ux941AS-Q1 to reformat the left or right formatted video into a single image with alternating pixels for superframe splitting. The resultant superframe has the same number of lines of the same size, but the pixels are reordered. The DS90Ux941AS-Q1 can split the superframe and send the frame to two independent FPD-Link III deserializers.

The following are requirements for proper operation:

- Images must have identical video format (lines, pixels, blanking intervals).

- Pixel clock used must be twice the frequency as required for sending a single image.

- Horizontal blanking components (front porch, sync period, back porch) must be twice the number of pixels as required for a single image.

- Vertical blanking periods must be the same number as required for a single image. Note that the total time spent on vertical blanking in the dual image is twice that of the time spent in the single image, as the vertical blanking happens for two times the number of lines in a single image.

- The maximum line size allowed for the combined image is 8191 pixels (24-bit).

The system designer can set the LEFT\_RIGHT\_3D register bit in the BRIDGE\_CFG2 register (register 0x56[7]) to enable left or right input mode. Software must also set the 2D image line size, IMG\_LINE\_SIZE (registers 0x32 and 0x33), as well as the IMG\_DELAY control (registers 0x34 and 0x35). The IMG\_DELAY is used to properly delay image regeneration, and is typically set to a small value (for example, 12 clocks). IMG\_LINE\_SIZE is used to configure the active line size, and is set to 1280 pixels by default to align with the default 720p60 timing (1280x720 at 60 fps).

The designer can also monitor the left or right video processing in the VIDEO\_3D\_STS register (register 0x58).

# 2.2 Alternate Line 3D Format

The DS90Ux941AS-Q1 can format a superframe as a dual-image with alternating lines consistent with the Alternate Line 3D format specified in the HDMI 1.4b specification. The DS90Ux941AS-Q1 can be programmed to reformat the alternate line formatted video into a single image with alternating pixels for superframe splitting. The resultant superframe has half the number of video lines that are twice the length. This superframe can be split by the DS90Ux941AS-Q1 at the FPD-Link III output and send the new frames to two independent deserializers.

The following are requirements for proper operation:

- Images must have identical video format (lines, pixels, blanking intervals)

- Pixel clock used must be twice the frequency as required for sending a single image

- Vertical blanking components (front porch, sync period, back porch) must be twice the number of video line periods as required for a single image.

- Horizontal blanking periods must be the same number of pixels as required for a single image. Note that the total time spent on horizontal blanking in the dual image is twice that of the time spent in the single image, as the horizontal blanking happens for two times the number of lines in a single image.

- The maximum line size allowed is 4095 pixels (24-bit).

Figure 2-2. HDMI 1.4b Alternate Line 3D Format

The designer can set the ALT\_LINES\_3D register bit in the BRIDGE\_CTL register (register 0x4F[4]) to enable the alternate line mode.

Alternate Line video processing status can be monitored in the VIDEO\_3D\_STS register (register 0x58).

5

# 2.3 Alternate Pixel 3D Format

The DS90Ux941AS-Q1 formats a superframe as a dual-image with alternating pixels. The DS90Ux941AS-Q1 does not require any special processing on this image format. This superframe can be split by the DS90Ux941AS-Q1 and sent to two independent deserializers.

The following are requirements for proper operation:

- Images must have identical video format (lines, pixels, blanking intervals).

- Pixel clock used must be twice the frequency as required for sending a single image.

- Horizontal blanking components (front porch, sync period, back porch) must be twice the number of pixels as required for a single image.

- Vertical blanking periods must be the same number as required for a single image. Note that the total time spent on vertical blanking in the dual image is twice that of the time spent in the single image, as the vertical blanking happens for two times the number of lines in a single image.

- The maximum line size allowed is 4095 pixels (24-bit).

Figure 2-3. HDMI 1.4b Alternate Pixel 3D Format

Alternate Pixel mode is the default mode of operation for the DS90Ux941AS-Q1.

If splitter mode is enabled, there are two options to properly regenerate Horizontal Sync timing. The preferred option is to use the default setting for the IMG\_DELAY, and enable a register override of the Horizontal Sync and Horizontal Back porch periods for each port using the IMG\_HSYNC\_CTLx registers. Front Porch value may be determined from total line length - (Active line length + Horizontal Back Porch + Horizontal Sync). The second option is to allow automatic generation of the Horizontal Sync timing and set the IMG\_DELAY value in registers 0x34 0x35 to greater than the Horizontal Sync period plus the Horizontal Back Porch period for the 3D image in pixels.

# **3 Video Processing Status Monitoring**

The VIDEO\_3D\_STS register may be used to monitor the Left/Right video and Alternate Line video processing status for errors. If any processing error occurs, the register field is set to 1 and only cleared on read. It is important to read the register carefully based on the different splitting configuration for the LINE\_MISMATCH field.

# 3.1 VIDEO\_3D\_STS Register (Address = 58h) [reset = 0h]

VIDEO\_3D\_STS is described in Table 3-1.

#### Table 3-1. VIDEO\_3D\_STS Register Field Descriptions Bit Field Reset Description Туре 7-3 RESERVED 0h Reserved R 2 LINE OV ERR R/RC 0h Line Buffer Overflow: When set to a 1, an error has been detected in the 3D video line buffers due to receiving a video line that was too long for the buffer. For Alternate Line 3D mode, this flag is set if a video line contains 4096 or more pixels. For Left/Right 3D, or Alternate Pixel 3D modes, this flag is set if a video line contains 8192 or more pixels. This flag will be cleared on read. 1 LINE VID ERR R/RC 0h Line Video Error: When set to a 1, an error has been detected in the 3D video processing likely due to invalid line length or blanking intervals. This flag is cleared on read. LINE MISMATCH R/RC 0h 0 Line Mismatch Error. Alternate Line 3D mode: When set to a 1, odd or even video line length mismatch has been detected. This occurs if the odd and even lines of a video are note the same length. This flag is cleared on read. Left/Right 3D mode: When set to a 1, a line length error has been detected. This occurs if the received video line is not twice the IMG LINE SIZE value. If the received line length is less than IMG\_LINE\_SIZE, an error may not be detected. This flag is cleared on read. If the image is cropped in the horizontal dimension, this error flag may not be accurate.

7

# 4 Superframe Splitting

The superframe may be split at the DS90Ux941AS-Q1, as shown in Figure 4-1. Splitter options must be configured prior to enable to enabling DSI inputs. This ensures the device enters the appropriate mode prior to forwarding video. Splitter mode can be enabled by either register settings or strap mode. For register settings, select the Forced Splitter Mode selection on the FPD3\_TX\_MODE control in the Dual\_CTL1 register (0x58 [2:0] = 111). Mode\_SEL [1:0] can be configured for splitter mode based on the voltage ratio set by the pullup and pulldown resistor. The *Device Functional Modes* section of the *DS90UB941AS-Q1 data sheet* provides information on the hardware configuration.

Figure 4-1. Symmetric Splitting

# 5 Frame Cropping

Asymmetric splitting of frames can be accomplished by cropping the resultant output images. The input video requirements are the same as those for the symmetric splitting. The superframe must include two identical size images. Those images are cropped in both the horizontal and vertical dimensions to produce reduced size images. Note that the clock frequency remains half the frequency of the superframe. In addition, the horizontal and vertical blanking intervals are increased by the magnitude of the cropping.

Figure 5-1 shows one superframe stream input on the DSI0 (DSI1 also possible) that is split into two different video resolutions. When the superframe is received, it is reformatted to the alternate pixels 3D format before the superframe is split into two images. The cropping function is then performed on either one or both of the resultant images to get the desired resolutions before the images are forwarded to the compatible deserializers and attached displays.

## Figure 5-1. Asymmetric Splitting With Cropping

The engineer can enable image cropping on each image to handle asymmetric splitting. To crop each image, the engineer must program the horizontal and vertical dimensions in the registers described in Section 5.1. The origin of the frame begins at the start of the active video as shown in the figure Figure 5-2 below. Typically, for asymmetric split, the difference between the active videos in both horizontal and vertical dimensions is added to the front porch of the smaller video. However, in the SuperFrame image, the resultant image can be offset such that the front porch and back porch can have different values. Figure 5-2 shows the relation between the resultant crop image and the blanking parameters.

9

Figure 5-2. Cropping Example

# **5.1 Cropping Control Registers**

Cropping is controlled by the CROP\_START\_X/Y and CROP\_STOP\_X/Y registers for each port.

#### 5.1.1 CROP\_START\_X0\_CROP\_START\_X0\_P1 Register (Address = 36h) [reset = 0h]

CROP\_START\_X0\_CROP\_START\_X0\_P1 is described in Table 5-1.

#### Table 5-1. CROP\_START\_X0\_CROP\_START\_X0\_P1 Register Field Descriptions

| Bit | Field                                   | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|-----------------------------------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0 | CROP_START_X_7:0C<br>ROP_START_X_P1_7:0 | R/W  | Oh    | Crop Start X0 Register.<br>In Splitter or Independent 2:2 modes, this controls the selected FPD-<br>Link III port.<br>Image Cropping Start X position (bits 7:0).<br>The Image Cropping Start X position indicates the horizontal starting<br>position for the portion of the video line to forward. Pixels prior to the<br>start X position will not be forwarded, replaced with blank (DE is de-<br>asserted). Pixel positions range from 0 to N-1, where N is the line<br>length in pixels. |

#### 5.1.2 CROP\_START\_X1\_CROP\_START\_X1\_P1 Register (Address = 37h) [reset = 0h]

CROP\_START\_X1\_CROP\_START\_X1\_P1 is described in Table 5-2.

#### Table 5-2. CROP\_START\_X1\_CROP\_START\_X1\_P1 Register Field Descriptions

| Bit | Field                                          | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|------------------------------------------------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CROP_ENABLE_CROP_<br>ENABLE_P1                 | R/W  | 0h    | Crop Start X1 Register.<br>In Splitter or Independent 2:2 modes, this controls the selected FPD-<br>Link III port.<br>Enable Video Cropping:<br>Setting this bit to a 1 enables cropping of video for the selected port.<br>Cropping is controlled by setting the X,Y start and stop positions<br>using the CROP_START_X/Y and CROP_STOP_X/Y registers.                                                                                                            |

| 6-5 | RESERVED                                       | R    | 0h    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4-0 | CROP_START_X_12:8_<br>CROP_START_X_P1_12:<br>8 | R/W  | Oh    | Image Cropping Start X position (bits 12:8).<br>In Splitter or Independent 2:2 modes, this controls the selected FPD-<br>Link III port.<br>The Image Cropping Start X position indicates the horizontal starting<br>position for the portion of the video line to forward. Pixels prior to the<br>start X position are not forwarded, replaced with blank (DE will be<br>deasserted). Pixel positions range from 0 to N-1 where N is the line<br>length in pixels. |

#### 5.1.3 CROP\_STOP\_X0\_CROP\_STOP\_X0\_P1 Register (Address = 38h) [reset = 0h]

CROP\_STOP\_X0\_CROP\_STOP\_X0\_P1 is described in Table 5-3.

#### Table 5-3. CROP\_STOP\_X0\_CROP\_STOP\_X0\_P1 Register Field Descriptions

| Bit | Field                                 | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|---------------------------------------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0 | CROP_STOP_X_7:0CR<br>OP_STOP_X_P1_7:0 | R/W  |       | Image Cropping Stop X position (bits 7:0).<br>In Splitter or Independent 2:2 modes, this controls the selected FPD-<br>Link III port.<br>The Image Cropping Stop X position indicates the position of the last<br>pixel to be forwarded when cropping is enabled. Pixels following the<br>Stop X position are not forwarded, replaced with blank (DE is<br>deasserted). Pixel positions range from 0 to N-1 where N, is the line<br>length in pixels. |

#### 5.1.4 CROP\_STOP\_X1\_CROP\_STOP\_X1\_P1 Register (Address = 39h) [reset = 0h]

CROP\_STOP\_X1\_CROP\_STOP\_X1\_P1 is described in Table 5-4.

#### Table 5-4. CROP\_STOP\_X1\_CROP\_STOP\_X1\_P1 Register Field Descriptions

| Bit | Field    | Туре | Reset | Description |

|-----|----------|------|-------|-------------|

| 7-5 | RESERVED | R    | 0h    | Reserved.   |

| Та  | Table 5-4. CROP_STOP_X1_CROP_STOP_X1_P1 Register Field Descriptions (continued) |      |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|-----|---------------------------------------------------------------------------------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Bit | Field                                                                           | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 4-0 | CROP_STOP_X_12:8C<br>ROP_STOP_X_P1_12:8                                         | R/W  | Oh    | Image Cropping Stop X position (bits 12:8).<br>In Splitter or Independent 2:2 modes, this controls the selected FPD-<br>Link III port.<br>The Image Cropping Stop X position indicates the position of the last<br>pixel to be forwarded when cropping is enabled. Pixels following the<br>Stop X position are not forwarded, replaced with blank (DE is<br>deasserted). Pixel positions range from 0 to N-1, where N is the line<br>length in pixels. |  |  |  |  |  |  |

#### 5.1.5 CROP\_START\_Y0\_CROP\_START\_Y0\_P1 Register (Address = 3Ah) [reset = 0h]

CROP\_START\_Y0\_CROP\_START\_Y0\_P1 is described in Table 5-5.

#### Table 5-5. CROP\_START\_Y0\_CROP\_START\_Y0\_P1 Register Field Descriptions

| Bit | Field                                   | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|-----------------------------------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0 | CROP_START_Y_7:0C<br>ROP_START_Y_P1_7:0 | R/W  | Oh    | Crop Start Y0 Register.<br>In Splitter or Independent 2:2 modes, this controls the selected FPD-<br>Link III port.<br>Image Cropping Start Y position (bits 7:0).<br>The Image Cropping Start Y position indicates the first video line to<br>be forwarded when cropping is enabled. Pixels prior to the Start Y<br>position is not forwarded, replaced with blank lines (DE is<br>deasserted). Line positions range from 0 to N-1 where N is the<br>number of lines in the frame. In Splitter or Independent 2:2 modes,<br>this controls the selected FPD-Link III port. |

#### 5.1.6 CROP\_START\_Y1\_CROP\_START\_Y1\_P1 Register (Address = 3Bh) [reset = 0h]

CROP\_START\_Y1\_CROP\_START\_Y1\_P1 is described in Table 5-6.

#### Table 5-6. CROP\_START\_Y1\_CROP\_START\_Y1\_P1 Register Field Descriptions

| Bit | Field                                          | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|------------------------------------------------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-5 | RESERVED                                       | R    | 0h    | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4-0 | CROP_START_Y_12:8_<br>CROP_START_Y_P1_12:<br>8 | R/W  | Oh    | Image Cropping Start Y position (bits 12:8).<br>In Splitter or Independent 2:2 modes, this controls the selected FPD-<br>Link III port.<br>The Image Cropping Start Y position indicates the first video line to<br>be forwarded when cropping is enabled. Video lines following the<br>Start Y position are not forwarded, replaced with blank lines (DE is<br>deasserted). Line positions range from 0 to N-1 where N is the<br>number of lines in the frame. |

#### 5.1.7 CROP\_STOP\_Y0\_CROP\_STOP\_Y0\_P1 Register (Address = 3Ch) [reset = 0h]

CROP\_STOP\_Y0\_CROP\_STOP\_Y0\_P1 is described in Table 5-7.

#### Table 5-7. CROP\_STOP\_Y0\_CROP\_STOP\_Y0\_P1 Register Field Descriptions

| Bit | Field                                 | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|---------------------------------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0 | CROP_STOP_Y_7:0CR<br>OP_STOP_Y_P1_7:0 | R/W  | Oh    | Crop Stop Y0 Register.<br>In Splitter or Independent 2:2 modes, this controls the selected FPD-<br>Link III port.<br>Image Cropping Stop Y position (bits 7:0).<br>The Image Cropping Stop Y position indicates the last video line to<br>be forwarded when cropping is enabled. Video lines following the<br>Stop Y position are not forwarded, replaced with blank lines (DE is<br>deasserted). Line positions range from 0 to N-1, where N is the<br>number of lines in the frame. |

#### 5.1.8 CROP\_STOP\_Y1\_CROP\_STOP\_Y1\_P1 Register (Address = 3Dh) [reset = 0h]

CROP\_STOP\_Y1\_CROP\_STOP\_Y1\_P1 is described in Table 5-8.

|     | Table 5-8. CROP_STOP_Y1_CROP_STOP_Y1_P1 Register Field Descriptions |      |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|-----|---------------------------------------------------------------------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Bit | Field                                                               | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| 7-5 | RESERVED                                                            | R    | 0h    | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 4-0 | CROP_STOP_Y_12:8C<br>ROP_STOP_Y_P1_12:8                             | R/W  | Oh    | Image Cropping Stop Y position (bits 12:8).<br>In Splitter or Independent 2:2 modes, this controls the selected FPD-<br>Link III port.<br>The Image Cropping Stop Y position indicates the last video line to<br>be forwarded when cropping is enabled. Video lines following the<br>Stop Y position are not forwarded, replaced with blank lines (DE is<br>deasserted). Line positions range from 0 to N-1 where N is the<br>number of lines in the frame. |  |  |  |  |  |

# 5.2 Cropping Options

In addition to the cropping options, the Horizontal Sync width and Horizontal Back Porch period may be modified. Front Porch value may be determined from total line length - (Active line length + Horizontal Back Porch + Horizontal Sync). Typically, these values are automatically generated based on the input video (half of the values in the dual image), but these can be overridden by setting the IMG\_HSYNC\_CTL registers. The Horizontal Sync period and the Horizontal Back Porch can be individually overridden by setting the HSYNC\_OV\_EN or HBACK\_OV\_EN controls, as well as the IMG\_HSYNC and IMG\_HBACK parameters. When overriding the IMG\_HBACK parameter, the resultant back porch is half of the programmed value, rounded up, plus one extra pixel. When overriding the IMG\_HSYNC and HBACK values are reduced, then the difference is added to the horizontal front porch. If the HSYNC and HBACK values are increased, then the difference is subtracted from the horizontal front porch.

# 6 Splitter Mode Pixel Clocks

By default, asymmetric splitting generates each resultant image at half the frequency of the superframe image. Options exist to use external reference clocks or M/N divided versions of the DPHY Lane clock for each resultant image. To avoid jitter clocks, TI recommends programming M to a value of 1. To prevent short pulse-widths to the Dual-Image buffer memories, the splitter mode dividers must have N greater than M. Additionally, the 1 divided by the ratio M/N must be an integer. The default settings for M/N provide a half clock frequency normally required for splitting symmetric video. The use of the half ratio results in an image with significant horizontal blanking; increasing the N value reduces the horizontal blanking. Note that this does not affect the vertical blanking.

# 6.1 SPLIT\_CLK\_CTL0\_SPLIT\_CLK\_CTL0\_P1 Register (Address = 3Eh) [reset = 81h]

SPLIT\_CLK\_CTL0\_SPLIT\_CLK\_CTL0\_P1 is described in Table 6-1.

#### Table 6-1. SPLIT\_CLK\_CTL0\_SPLIT\_CLK\_CTL0\_P1 Register Field Descriptions

| Bit | Field                                    | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|------------------------------------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SPLIT_CLK_DIV_EN_SP<br>LIT_CLK_DIV_EN_P1 | R/W  | 1h    | Splitter Mode Clock Control Register 0.<br>This controls the selected FPD-Link III port.<br>Splitter mode clock divider enable.<br>This register enables the splitter mode clock divider. In splitter mode,<br>if this register is set to 0, the pixel clock for splitter operation is<br>disabled. The divider should be disabled prior to changing the<br>Splitter Divider settings, SPLIT_CLK_SEL, SPLIT_CLK_DIV_M, and<br>SPLIT_CLK_DIV_N. In addition, changes to divider settings must<br>only be done when the DSI input is disabled to ensure proper mode<br>transition.<br>These values are ignored if Splitter mode is disabled. This controls<br>the selected FPD-Link III port. |

| 6-5 | SPLIT_CLK_SEL                            | R/W  | Oh    | Splitter mode clock select.<br>This register selects the clock source for the FPD-Link III transmit<br>side of the splitter operation for the selected port.<br>00 : Input pixel clock divided by 2 (default).<br>01 : M/N divider from the DPHY input clock.<br>10 : M/N divider from the external clock on the REFCLK0 pin.<br>11 : M/N divider from the external clock on the REFCLK1 pin.                                                                                                                                                                                                                                                                                               |

| 4-0 | SPLIT_CLK_DIV_M_SPLI<br>T_CLK_DIV_M_P1   | R/W  | 1h    | Splitter mode clock divider M value.<br>This register controls the M setting for the M/N divider used to<br>generate the splitter mode pixel clock from the selected input clock.<br>The default settings for M/N provide a half clock frequency normally<br>required for splitting symmetric video.<br>These values are ignored if Splitter mode is disabled. This controls<br>the selected FPD-Link III port.                                                                                                                                                                                                                                                                             |

# 6.2 SPLIT\_CLK\_CTL1\_SPLIT\_CLK\_CTL1\_P1 Register (Address = 3Fh) [reset = 2h]

SPLIT\_CLK\_CTL1\_SPLIT\_CLK\_CTL1\_P1 is described in Table 6-2.

#### Table 6-2. SPLIT\_CLK\_CTL1\_SPLIT\_CLK\_CTL1\_P1 Register Field Descriptions

| Bit | Field                                 | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|---------------------------------------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0 | SPLIT_CLK_DIV_N_SPLI<br>T_CLK_DV_N_P1 | R/W  | 2h    | Splitter Mode Clock Control Register 1.<br>This controls the selected FPD-Link III port.<br>Splitter mode clock divider N value.<br>This register controls the N setting for the M/N divider used to<br>generate the splitter mode pixel clock from the selected input clock.<br>The default settings for M/N provide a half clock frequency normally<br>required for splitting symmetric video.<br>These values are ignored if Splitter mode is disabled. This controls<br>the selected FPD-Link III port. |

# 7 Programming Example

The example code configures the devices for splitting a 2560x720 (2x1280x720, 60 fps, 100-MHz PCLK) superframe with Left/Right 3D from a 4-Lane DSI source to two remote displays with standard 720p and 480p resolutions. The 720p display is assumed to be connected to FPD-Link Port 0, while the 480p display is assumed to be connected to FPD-Link Port 0, while the device for cropping the Port1 video after the splitting and before forwarding the data to the 720p display.

| WriteI2C (0x01,0x08)  | //Disable DSI                                                   |

|-----------------------|-----------------------------------------------------------------|

| WriteI2C (0x1E,0x01)  | //Select FPD-Link III Port 0                                    |

| WriteI2C (0x4F,0x8C)  |                                                                 |

| WriteI2C (0x5B,0x07)  | //Force Splitter mode                                           |

| WriteI2C (0x56,0x80)  | //Enable Left/Right 3D processing to allow superframe splitting |

| WriteI2C (0x32,0x00)  | //Set the line size to 1280(LSB)                                |

| WriteI2C (0x33,0x05)  | //Set the line size to 1280 (MSB)                               |

| //Crop Port0 720p ima | ge                                                              |

| WriteI2C (0x1E,0x01)  | //Select FPD-Link III Port 1                                    |

| WriteI2C (0x36,0x00)  | //Set crop start X position to 0 (LSB)                          |

| WriteI2C (0x37,0x80)  | //Set crop start X position to 0 (MSB) and enable cropping      |

| WriteI2C (0x38,0xFF)  | //Set crop stop X position to 1279 (LSB)                        |

| WriteI2C (0x39,0x04)  | //Set crop stop X position to 1279 (MSB)                        |

| WriteI2C (0x3A,0x00)  | //Set crop start Y position to 0 (LSB)                          |

| WriteI2C (0x3B,0x00)  | //Set crop start Y position to 0 (MSB)                          |

| WriteI2C (0x3C,0xCF)  | //Set crop stop Y position to 719 (LSB)                         |

| WriteI2C (0x3D,0x02)  | //Set crop stop Y position to 719 (MSB)                         |

| //Crop Port1 480p ima |                                                                 |

| WriteI2C (0x1E,0x02)  | //Select FPD-Link III Port 1                                    |

| WriteI2C (0x36,0x00)  | //Set crop start X position to 0 (LSB)                          |

| WriteI2C (0x37,0x80)  | //Set crop start X position to 0 (MSB) and enable cropping      |

| WriteI2C (0x38,0x7F)  | //Set crop stop X position to 639 (LSB)                         |

| WriteI2C (0x39,0x02)  | //Set crop stop X position to 639 (MSB)                         |

| WriteI2C (0x3A,0x00)  | //Set crop start Y position to 0 (LSB)                          |

| WriteI2C (0x3B,0x00)  | //Set crop start Y position to 0 (MSB)                          |

| WriteI2C (0x3C,0xDF)  | //Set crop stop Y position to 479 (LSB)                         |

| WriteI2C (0x3D,0x01)  | //Set crop stop Y position to 479 (MSB)                         |

|                       | SI parameter on DSI PortO                                       |

| WriteI2C (0x40,0x04)  | //Select DSI Port 0 digital registers                           |

| WriteI2C (0x41,0x05)  |                                                                 |

| WriteI2C (0x42,0x1E)  | //Write TSKIP_CNT value for 300 MHz DSI clock frequency         |

| WriteI2C (0x01,0x00)  | //Enable DSI                                                    |

# 8 Summary

The DS90Ux941AS-Q1 provides video processing functions system designers can use to create IVI systems with multiple displays using cost-effective application processors. Engineers can split superframes symmetrically or asymmetrically by following the suggestions and programming examples given in this report.

Summary

# 9 References

- DS90UB941AS-Q1 DSI to FPD-Link III Bridge Serializer (SNLS640)

- High-Definition Multimedia Interface Specification Version 1.4a (March 4, 2010), HDMI Licensing, LLC.

# 10 Handling Interrupts With the DS90Ux941AS-Q1

# 10.1 Interrupt Control and Status (INTB and REM\_INTB Pin)

The HDCP Transmitter can generate an interrupt signal to the attached controller through the INTB pin. This method allows the controller to process some portion of the authentication flow, or to indicate errors in the link status or authentication. The INTB pin is an open-drain, active-low signal that may be shared with other interrupt sources. The HDCP Interrupt Control Register (HDCP\_ICR, address 0xC6) enables the various interrupt conditions, while the HDCP Interrupt Status Register (HDCP\_ISR, address 0xC7) is used to monitor the interrupt conditions. Bit 0 of the HDCP\_ICR is the global interrupt enable that must be set along with at least one other interrupt enable to generate an interrupt on the active low INTB pin.

Upon an interrupt detection, the controller must read the HDCP\_ISR register to determine the interrupt condition. Bit 0 of the HDCP\_ISR indicates whether or not an interrupt occurred, and the individual status bits indicate which conditions were triggered. The read of the HDCP\_ISR also clears the interrupt, which releases the INTB pin. If desired, the controller may then read the HDCP\_STS register to determine the current device status. For details on the available interrupt conditions, see the HDCP\_ICR and HDCP\_ISR register definitions in the data sheet.

The Receiver interrupt—which is bit 5 of HDCP\_ICR and HDCP\_ISR registers—is a special case. This interrupt is used to propagate an external interrupt from the HDCP Receiver INTB\_IN pin to the HDCP Transmitter interrupt pin (INTB). The interrupt is active low and is handled similarly to other interrupt conditions. When the controller detects a falling edge of the interrupt signal, the HDCP Transmitter latches on the interrupt condition, sets the IS\_RX\_INT bit in the HDCP\_ISR register, and asserts the INTB pin low. To clear the interrupt signal, the controller must read the HDCP\_ISR to release the INTB and clear the HDCP\_ISR. The controller may then check the HDCP\_STS:RX\_INT bit to determine the current status of the HDCP Receiver's INTB\_IN pin. The INTB pin remains deasserted until the next falling edge of the INTB\_IN signal. Figure 10-1 shows a typical diagram for the Receiver interrupt propagation.

Figure 10-1. Receiver Interrupt Propagation Block Diagram

The sequence for handling the Receiver Interrupt is as follows:

- 1. INTB\_IN is pulled low by a downstream device.

- 2. HDCP Transmitter pulls INTB low.

- 3. Controller detects the INTB low and reads the HDCP\_ISR register to determine the interrupt source. This clears the interrupt at HDCP Transmitter, which releases the INTB.

- 4. The controller typically accesses the remote interrupt source to process the downstream interrupt, which clears the interrupt condition driving INTB\_IN.

- 5. System is ready to capture another interrupt condition.

# 10.2 Handling Interrupts in Splitter Mode Using Remote Interrupt Pin (REM\_INTB)

The DS90Ux941AS-Q1 includes a dedicated remote interrupt pin (REM\_INTB). This pin provides a pass-through of the INTB signal from an attached FPD-Link III deserializer (for example, the DS90Ux948-Q1). During a valid link connection, the value of the deseralizer INTB\_IN is reflected to the DS90Ux941-Q1 REM\_INTB pin. In Dual FPD3 mode, the REM\_INTB pin indicates the INTB\_IN from the attached dual-capable deserializer.

If multiple deserializers are connected, the REM\_INTB typically indicates a combined interrupt from INTB\_IN pins of multiple deserializers. The combined interrupt is asserted if either connection reports a remote interrupt. If desired, the Remote Interrupt Control (REM\_INTB\_CTRL, address 0x30) allows independent remote interrupts from both deserializers. Figure 10-2 shows a typical diagram for the receiver interrupt propagation for independent remote interruption.

Figure 10-2. Interrupt Propagation in Splitter Mode Block Diagram

Selection 0001 of REM\_INTB\_MODE field brings a port 0 remote interrupt to the REM\_INTB pin, and a port 1 remote interrupt to the INTB pin. For the INTB pin, the remote interrupt is combined with the HDCP interrupt register sources, but HDCP interrupts are only active if they are enabled through the HDCP\_ICR register.

Note that in splitter mode, the latching behavior and logic states differ on port 0 and port 1

## Port 0 (REM\_INTB):

- REM\_INTB outputs the opposite logic level of INTB\_IN at the remote deserializer

- REM\_INTB does not latch like non-splitter mode

#### Port 1 (INTB):

- INTB latches low after INTB\_IN transitions from low to high

- INTB latch can be cleared to high by reading the HDCP\_ISR register (0xC7)

- If INTB\_IN is still high when 0xC7 is read, then the interrupt will not clear. INTB\_IN must return to logic low before 0xC7 is read in order to clear the INTB latch

#### Figure 10-4. INTB Logic in Splitter Interrupt Mode

The sequence for handling the receiver interrupts in splitter mode is as follows:

#### Port 0:

- 1. INTB\_IN is pulled high or low by a downstream device on port 0

- 2. The REM\_INTB pin on the DS90Ux941AS-Q1 will output the opposite logic level of INTB\_IN automatically

- 3. Since REM\_INTB does not latch in splitter mode, the system SW must be configured to ignore proceeding transitions until the interrupt is serviced

- 4. The system SW can take action to access the remote interrupt source on port 0 (ex. Touch controller) to clear the INTB\_IN signal back to the original low or high state

- 5. REM\_INTB will revert to the opposite logic level of INTB\_IN

#### Port 1:

- 1. INTB\_IN is pulled high by a downstream device on port 1

- 2. The INTB pin on the DS90Ux941AS-Q1 will transition from high to low and latch to the low state

- 3. If the controller detects the INTB low and HDCP interrupt functionality is enabled, the controller reads the HDCP\_ISR register to determine the interrupt source. This clears the interrupt at the HDCP Transmitter and releases the INTB, provided that the interrupt came from one of the HDCP Receiver devices.

- 4. If INTB is still not cleared, then the interrupt came from a remote interrupt source attached to INTB\_IN, and the controller must access the status register of the remote interrupt source (ex. Touch controller) to clear the downstream interrupt and return INTB\_IN to logic low on port 1

- 5. Once the INTB\_IN pin returns to logic low on port 1, the controller reads he HDCP\_ISR register to clear the INTB latch and return INTB to logic high on the DS90Ux941AS-Q1

If the above interrupt logic can not be used by the system, then alternatively standard GPIO mode may be used to signal interrupts from peripheral devices (ex. Touch controllers) attached to each remote deserializer in splitter

mode. With standard GPIO signaling, neither signal will latch and the logic level of the remote GPIO signal will match the logic level of the local GPIO signal (no inversion). GPIO configuration is described in section 3.4

Figure 10-5. Example Splitter Mode Interrupt Routing With Standard GPIO Signals

Figure 10-6. Example GPIO Logic with Standard GPIO Pass-Throughs

## 10.3 REM\_INTB\_CTRL Register (Address = 30h) [reset = 0h]

REM\_INTB\_CTRL is described in Table 10-1.

#### Table 10-1. REM\_INTB\_CTRL Register Field Description

| Bit | Field    | Туре | Reset | Description |

|-----|----------|------|-------|-------------|

| 7-4 | RESERVED | R    | 0h    | Reserved    |

|     | Table 10-1. REM_INTB_CTRL Register Field Description (continued) |                        |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|-----|------------------------------------------------------------------|------------------------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit | Field                                                            | Type Reset Description |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 3-0 | REM_INTB_MODE                                                    | R/W                    | Oh | Allows choosing different pins to output the remote interrupt. if<br>multiple links are available (Not in Dual FPD-Link III operation), the<br>REM_INTB is typically a combined interrupt from both ports. See<br>selection 0001 below for the exception that allows independent<br>remote interrupts from both ports.<br>Determines the pin that Remote Interrupt outputs on:<br>0000: NOT ENABLED<br>0001: REM_INTB indicates port 0 remote interrupt, INTB indicates<br>port1 remote interrupt<br>0001x,01xx Reserved<br>1000: GPIO0<br>1001: GPIO1<br>1010: GPIO2<br>1011: GPIO3<br>1100: D_GPIO1<br>1101: D_GPIO3<br>1111: D_GPIO3 |  |  |

# 11 High-Speed GPIO Operation in Splitter Mode

# 11.1 Introduction

The DS90Ux94x-Q1 family of devices incorporates both forward and reverse communication channels using one or two links. Forward channel data typically carries video information, but can also include additional bandwidth for other communications. The back channel signaling provides slower speed communication in the reverse direction. GPIO signals may be sent in both forward and reverse directions over either one or both links.

# 11.2 High-Speed Control Configuration

The High-Speed control channel mode can be configured by setting the following register control in the deserializer using the I2C register interface. HSCC Modes must only be enabled after the deserializer detects a valid receiver Lock condition (through the LOCK pin or LOCK status in register 0x0C). This ensures that the serializer has properly determined the deserializer capabilities prior to enabling the high-speed modes. In addition, if Receiver Lock is lost, HSCC mode must be disabled until a valid lock condition is restored

HSCC mode is split into two registers. The first two bits are under HSCC\_MODE\_2:1 field in Table 11-2. Bit 0 is under HSCC\_MODE\_0 field in Table 11-1.

## 11.2.1 DES\_CAP1 Registers (Address = 20h)

DES\_CAP1 is described inTable 11-1

| Bit | Field                                          | Туре | Reset                                                                                                                                                                                                                                                                                                                                                                                                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|-----|------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7   | FREEZE_DES_CAP<br>FREEZE_DES_CAP_<br>1         | R    | Oh                                                                                                                                                                                                                                                                                                                                                                                                         | If PORT1_SEL is set, this register indicates Port1<br>Capabilities<br>Freeze Deserializer Capabilities<br>Prevent auto-loading of the Deserializer Capabilities by the<br>Bidirectional Control Channel. The Capabilities are frozen at<br>the values written in registers 0x20 and 0x21.                                                                                                                                                                     |  |

| 6   | HSCC_MODE_0<br>_HSCC_MODE_P1_0                 | R/W  | 0h High-Speed Control Channel bit 0<br>Lowest bit of the 3-bit HSCC indication. The other 2 bits an<br>contained in Deserializer Capabilities 2. This field<br>automatically configured by Bidirectional Control Channel<br>once RX Lock has been detected. Software may overwrite<br>this value, but must also set the FREEZE DES CAP bit to<br>prevent overwriting by the Bidirectional Control Channel. |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 5   | RESERVED                                       | R    | 0h                                                                                                                                                                                                                                                                                                                                                                                                         | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 4   | RESERVED                                       | R    | 0h                                                                                                                                                                                                                                                                                                                                                                                                         | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 3   | DUAL_LINK_CAP<br>DUAL_LINK_CAP_1               | R/W  | Oh                                                                                                                                                                                                                                                                                                                                                                                                         | Dual link Capabilities<br>Indicates if the Deserializer is capable of dual link operation<br>This field is automatically configured by the Bidirectional<br>Control Channel once RX Lock has been detected.<br>Software may overwrite this value, but must also set the<br>FREEZE DES CAP bit to prevent overwriting by the<br>Bidirectional Control Channel.                                                                                                 |  |

| 2   | DUAL_CHANNEL_CA<br>P<br>DUAL_CHANNEL_CA<br>P_1 | R/W  | Oh                                                                                                                                                                                                                                                                                                                                                                                                         | Dual Channel 0/1 Indication<br>In a dual-link capable device, indicates if this is primary or<br>secondary channel.<br>0: Primary channel (channel 0)<br>1: Secondary channel (channel 1)<br>This field is automatically configured by the Bidirectional<br>Control Channel once RX Lock has been detected.<br>Software may overwrite this value, but must also set the<br>FREEZE DES CAP bit to prevent overwriting by the<br>Bidirectional Control Channel. |  |

| 1   | VID_24B_HD_AUD<br>VID_24B_HD_AUD_P<br>1        | R/W  | Oh                                                                                                                                                                                                                                                                                                                                                                                                         | Deserializer supports 24-bit video concurrently with HD<br>audio<br>This field is automatically configured by the Bidirectional<br>Control Channel once RX Lock has been detected.<br>Software may overwrite this value, but must also set the<br>FREEZE DES CAP bit to prevent overwriting by the<br>Bidirectional Control Channel.                                                                                                                          |  |

Table 11-1. DES\_CAP1 Register Field Description

|     | Table 11-1. DES_CAP1 Register Field Description (continued) |      |       |                                                                                                                                                                                                                                                                                                                             |  |  |

|-----|-------------------------------------------------------------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit | Field                                                       | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                 |  |  |

| 0   | DES_CAP_FC_GPIO<br>DES_CAP_FC_GPIO_<br>P1                   | R/W  | Oh    | Deserializer supports GPIO in the Forward Channel Frame<br>This field is automatically configured by the Bidirectional<br>Control Channel once RX Lock has been detected.<br>Software may overwrite this value, but must also set the<br>FREEZE DES CAP bit to prevent overwriting by the<br>Bidirectional Control Channel. |  |  |

. . .

#### 11.2.2 DES\_CAP2 Registers (Address = 21h)

...

----

DES\_CAP2 is described inTable 11-2

|     | Table 11-2. DES_CAP2 Register Field Description |      |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|-----|-------------------------------------------------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit | Field                                           | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 7-4 | RESERVED                                        | R    | 0h    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 3   | FC_BCC_CRC6                                     | R/W  | 0h    | Enabled enhanced CRC and start sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 2   | RGB_CHKSUM_ERR                                  | R    | Oh    | RGB Checksum Error Detected:<br>If RGB Checksum is enabled through the HDCP Transmitter<br>HDCP_DBG register, this bit will indicate if a checksum<br>error is detected.                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 1-0 | HSCC_MODE_2:1<br>HSCC_MODE_P1_2:1               | 0,RW | Oh    | High-Speed Control Channel bit 0<br>Upper bits of the 3-bit HSCC indication. The lowest bit is<br>contained in Deserializer Capabilities 1.<br>000: Normal Frame, GPIO Mode<br>001: High-Speed GPIO mode, 1 GPIO<br>010: High-Speed GPIO mode, 2 GPIOs<br>011: High-Speed GPIO mode, 4 GPIOs<br>100: Reserved<br>101: Reserved<br>110: High-Speed, Forward Channel SPI Mode<br>111: High-Speed, Reverse Channel SPI Mode<br>In Single Link devices, only Normal back channel frame<br>modes are supported |  |  |  |

## **11.3 Back Channel Frequency Configuration**

The deserializer includes oscillator divider control to support additional back-channel frequencies other than the default 5-Mbps speed. The engineer can configure the OSC\_DIVIDER controls in register 0x32, as well as the BC\_FREQ\_SELECT control in register 0x23[2], to control the oscillator divider. The supported frequencies are 100 MHz/N or 50 MHz/N. Table 11-3 lists the back-channel frequency settings.

The non-default settings of the OSC\_DIVIDER are for evaluation purposes only, as they may cause other functions in the device to operate at unexpected frequencies. Note that if BC\_HIGH\_SPEED is set to a 1, only even values of N are supported.

|             | Table 11-0. Dack channel frequency beamings |                            |                            |                           |  |  |  |

|-------------|---------------------------------------------|----------------------------|----------------------------|---------------------------|--|--|--|

| OSC_Divider | DIV Ratio<br>N                              | BC_FREQ_SELECT (Mbps)<br>0 | BC_FREQ_SELECT (Mbps)<br>1 | BC_HIGH_SPEED (Mbps)<br>1 |  |  |  |

| 0x0         | 1                                           | 50                         | 100                        | N/A                       |  |  |  |

| 0x1         | 2                                           | 25                         | 50                         | 100                       |  |  |  |

| 0x2         | 3                                           | 16.67                      | 33.33                      | N/A                       |  |  |  |

| 0x3         | 4                                           | 12.5                       | 25                         | 50                        |  |  |  |

| 0x4         | 5                                           | 10                         | 20                         | N/A                       |  |  |  |

| 0x5         | 6                                           | 8.33                       | 16.67                      | 33                        |  |  |  |

| 0x6         | 7                                           | 7.14                       | 14.28                      | N/A                       |  |  |  |

| 0x7         | 8                                           | 6.25                       | 12.5                       | 25                        |  |  |  |

| 0x8         | 9                                           | 5.55                       | 11.11                      | N/A                       |  |  |  |

| 0x9         | 10                                          | 5 (default)                | 10                         | 20                        |  |  |  |

| 0xA         | 11                                          | 4.55                       | 9.1                        | N/A                       |  |  |  |

#### Table 11-3. Back Channel Frequency Settings