# **TP-15**

TP-15 Reducing DC Errors in Op Amps (Addendum to AN241 & 242)

Literature Number: SNOA723

# Reducing DC Errors in Op Amps

Robert J. Widlar Apartado Postal 541 Puerto Vallarta, Jalisco Mexico

**Abstract.** An IC op amp design that reduces bias currents below 100 pA over a  $-55^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  temperature range is discussed. Super-gain bipolar transistors with on-wafer trimming are used, providing low offset voltage and drift. The key to low bias current is the control of high temperature leakage currents along with the development of reasonably accurate nanoampere current sources with low parasitic capacitance.

#### introduction

A bipolar replacement for the LM108 [1] drastically reduces offset voltage, bias current and temperature drift. This design, the LM11, does not depend on new technology. Instead, the improvements result from a better understanding of transistor behavior, new circuit techniques and the application of proven offset trimming methods. Table I summarizes the results obtained. The combination of low offset voltage and low bias current is unique to IC op amps, while the performance at elevated temperatures represents an advance in the state of the art.

TABLE I. Input error terms of the LM11 show an improvement over FET op amps even at room temperature. There is little degradation in performance from -55°C to 125°C. Other important specifications are somewhat better than LM108A.

| 30mcWhat Better than Elw 100A. |                       |     |                                                                                                   |       |

|--------------------------------|-----------------------|-----|---------------------------------------------------------------------------------------------------|-------|

| Parameter                      | T <sub>j</sub> = 25°C |     | $\begin{array}{c} -55^{\circ}\text{C} \leq \text{T}_{j} \\ \leq +125^{\circ}\text{C} \end{array}$ | Units |

|                                | Тур                   | Max | Max                                                                                               |       |

| Input Offset Voltage           | 0.1                   | 0.3 | 0.6                                                                                               | mV    |

| Input Offset Current           | 0.5                   | 10  | 30                                                                                                | pА    |

| Input Bias Current             | 25                    | 50  | 150                                                                                               | pА    |

| Offset Voltage Drift           | 1                     |     | 3                                                                                                 | μV/°C |

| Offset Current Drift           | 20                    |     |                                                                                                   | fA/°C |

| Bias Current Drift             | 0.5                   |     | 0.5                                                                                               | pA/°C |

# junction FETs

At first glance, field effect transistors seem to be the ideal input stage for an op amp, mainly because they have a low gate current, independent of their operating current. Practically, they do provide an attractive combination of performance characteristics in a relatively simple design. But there are serious shortcomings.

For one, FETs do not match as well as bipolar devices: the offset voltage is at least an order of magnitude worse. Laser trimming can compensate for this to some extent. But with FETs, low offset voltage does not guarantee low drift, as it

National Semiconductor Technical Paper 15 December 1980

does with bipolars. FETs are also sensitive to mechanical strains and subject to offset shifts during assembly or with temperature cycling.

Typically, long term stability is about 100  $\mu$ V/year, although this can go to 1 mV/year with no prior warning in early life. This contrasts to a 10  $\mu$ V/year long term stability for bipolar pairs.

Lastly, although the input current of FETs is low at room temperature, it doubles for every 10°C increase. This, coupled with high offset voltage drift, makes FETs much less attractive as operating temperature is increased.

#### **MOS FETs**

Field effect transistors, with a metal gate and oxide insulation, give the ultimate in low input current. Practically, this advantage disappears when diodes are included to protect the gate from static charges encountered in normal handling. Further, the offset voltage problems of JFETs go double for MOS FETs. They are also subject to offset shifts due to contamination.

Interesting designs are on the horizon for various chopperstabilized complementary MOS ICs. These solve most offset voltage problems, but not that of input leakage current. Even at moderate temperatures, this input current will seriously degrade the low offset voltage and drift even with relatively low source resistances. Chopper-stabilized amplifiers have added problems with overload recovery and noise, especially with high source impedances. These problems have limited solutions, but chopper stabilization is not usually suitable for general purpose applications.

# bipolar op amps

Offset voltage, its drift or long term stability has not been a serious problem with bipolar-input op amps. Such techniques as cross-coupling or zener-zap trimming have reduced offset voltage to  $25~\mu V$  in production. The real problem has been bias current. The LM108, introduced in 1968, has represented the state of the art in low bias currents for standard bipolar devices. At 3 nA, maximum over temperature, the bias current is lower than FETs above  $85^{\circ} C$ .

A Darlington version of the LM108, the LM216, provided bias currents in the 50 pA range; but this design was seriously marred by high offset voltage, drift, excessive low frequency noise and anomalous leakage currents at higher temperatures.

Improvements in this design were thwarted by the inability to provide nanoampere bleed currents to stabilize the Darlington input and the erroneous belief that uncontrollable surface states created the anomalous leakage.

#### a new design

With bipolar transistors, there is a tradeoff between current gain and breakdown voltage. Super-gain transistors are devices that have been diffused for maximum current gain at the expense of breakdown voltage (which is typically a couple volts for a current gain of 5000). These low voltage transistors can be operated in a cascode connection with standard transistors to give a composite device with both high gain and breakdown voltage.

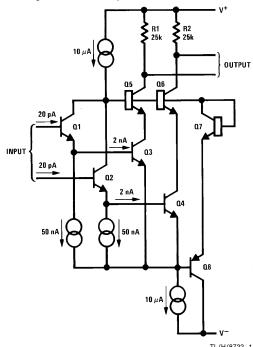

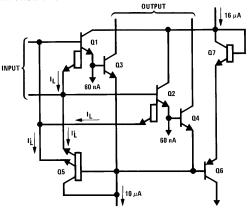

Figure 1 shows a modified Darlington input stage for a super-gain op amp. Common base standard transistors (Q5 and Q6, drawn with a wider base) are bootstrapped to the super-gain input transistors so that the latter are operated at near zero collector base voltage. In addition to permitting the use of super-gain inputs, this connection also isolates the input transistors from common-mode variations, increasing common-mode rejection.

Figure 1. Bootstrapped input stage using super-gain transistors in modified-Darlington connection. The objectionable characteristics of the Darlington are virtually eliminated by operating the input transistors at a much larger current than the base current of the transistors they are driving.

The usual problems with the Darlington connection are avoided by providing a bleed current that operates the input transistors, Q1 and Q2, at a current much higher than the base current of the transistors they are driving, Q3 and Q4. This is necessary because the base currents are not that well matched, especially over temperature, and have excess low frequency noise.

#### a nanoampere current source

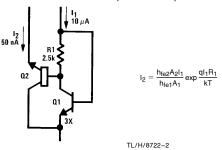

A circuit that generates the 50 nA bleed current is shown in Figure 2. A super-gain transistor operated in the forward mode is used to bias a standard transistor in the reverse mode. The reverse connection is used because the capacitance of an ordinary collector tub would reduce the common-mode slew rate from 2 V/ $\mu$ s to 0.02 V/ $\mu$ s.

Figure 2. Forming a nanoampere current source with low parasitic capacitance. Design takes advantage of predictable  $V_{BE}$  difference between standard and super-gain transistors and fact that  $V_{BE}$  of a transistor is the same when operated in forward or reverse mode.

At first look, this biasing scheme would seem to be subject to a number of process variations. This is not so. For one, the  $V_{BE}$  of a transistor depends on the base Gummel number  $(Q_B/\overline{\mu}_B)$ , the number of majority carriers per unit area divided by their effective mobility. Since the Gummel number and the effective area are unchanged when the collector and emitter are interchanged, the  $V_{BE}$  will be the same in either connection, provided that base recombination is not excessive. In standard IC transistors, reverse  $h_{fe}$  is about 30, indicating that recombination is not a significant factor. Measured reverse  $h_{fe}$  is much lower, but this is the result of a parasitic PNP that does not affect  $V_{BE}$  or  $\alpha_E$ , the common base current gain.

The bleed current depends also on the ratio of super-gain to standard transistor  $h_{\rm fe},$  as indicated by the equation in Figure 2. Intuition suggests that super-gain  $h_{\rm fe}$  will increase much faster than standard transistor  $h_{\rm fe}$  with increasing emitter diffusion time, giving lower bleed current with higher super-gain  $h_{\rm fe}.$  However, measurements with variances of standard LM108 processing indicate that the bleed current remains within 25% of design center.

As shown in Figure 2, higher current ratios can be obtained by increasing the area of Q1 relative to Q2 or by including R1. The equation in Figure 2 assumes that  $I_1$  varies as absolute temperature. If the voltage drop across R1 is equal to kT/q, changes in the  $V_{BE}$  of Q1 with small changes in  $I_1$  will be cancelled by changes in the voltage drop across R1. This makes input bias current essentially unaffected by variations in supply or common-mode voltage as long as  $I_1$  is reasonably well controlled.

## leakage currents

The input leakage currents of bipolar op amps can be kept under control because small geometry devices are satisfactory and because the collector-base junction can be operated at an arbitrarily low voltage if bootstrapping is used.

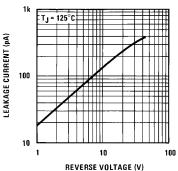

Simple theory predicts that bulk leakage saturates for reverse biases above 2kT/q. But generation in the depletion zone dominates below 125°C. Because the depletion width varies with reverse bias, so does leakage. The characteristics of a high quality junction plotted in *Figure 3* show that leakage current can be reduced with lower bias.

TL/H/8722-3

Figure 3. Voltage sensitivity of collector base leakage indicates that generation in the depletion zone dominates even at 125°C.

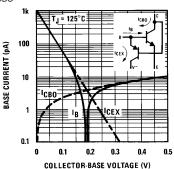

When more than one junction is involved, minimum leakage is not necessarily obtained for zero bias. This is illustrated in Figure 4, a plot of  $I_{\rm CBO}$  for a junction isolated NPN transistor. A parasitic PNP is formed between the base and the isolation as diagrammed in the inset. Zero leakage is obtained when  $V_{\rm CB}$  is set so that the PNP diffusion current equals  $I_{\rm CBO}$  of the NPN.

TI /H/8722-4

Figure 4. Plot above explains "anomalous" leakage of NPN transistors in ICs. As collector base bias is reduced, base current reverses then increases exponentially. This excess current is the forward diffusion current of parasitic PNP to substrate (see inset).

# input protection

The input clamps perform a dual function. Most important, they protect the emitter base junction of the input transistors from damage by in-circuit overloads or static charges in handling. Secondly, they limit the voltage change across

junction capacitances on low current nodes under transient conditions. This minimizes recovery delays.

The clamp circuitry is shown in Figure 5. Emitters are added on the input transistors and cross-coupled to limit the differential input voltage. Another transistor, Q5, has been added to limit voltage on the input transistors if the inputs are driven below  $V^-$ .

TL/H/8722-5

Figure 5. Separate clamps are used for differential and common-mode overloads. Leakage currents, I<sub>CES</sub> of forward and reverse connected transistors, cancel.

The differential clamp transitors do contribute to input current because  $V_{CB}>0$ , so collector current is not zero for  $V_{BE}\cong 0$  (I $_{CES}\cong 100$  pA at  $125^{\circ}\text{C}$ ). The common-mode input clamp, Q5, is also operated at  $V_{BE}=0$  and  $V_{CB}>0$ , although in the inverted mode. The resulting error is diffusion current, dependent only on the characteristic  $V_{BE}$  of the transistors. Thus, the current contributed by the differential clamp transistors is cancelled, within a couple percent, by that from the common-mode clamp.

# bias current

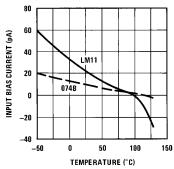

Figure 6 shows some results of the design approach described here. A room temperature bias current of 25 pA is obtained, and this his held to 60 pA over a  $-55^{\circ}$ C to 125°C temperature range. The figure also shows the results of

TL/H/8722-6

Figure 6. Input bias current of the LM11 remains low over military temperature range. Improvements in development give even better results (074B). Offset current is usually below 1 pA.

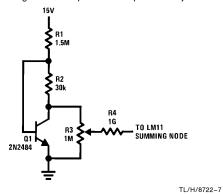

some improvements in development that have reduced bias current to 20 pA over the full operating temperature range. Figure 6 shows that bias current is very nearly a linear function of temperature, at least from  $-55^{\circ}$ C to  $+100^{\circ}$ C. This, coupled with the fact that bias current is virtually unaffected by changes in common-mode or supply voltage, suggests that bias current compensation can be provided for critical applications. An appropriate circuit is shown in Figure 7. Details are given in reference [2], but properly set up it should be possible to hold bias currents to less than 20 pA over a -55°C to +100°C temperature range or 5 pA over a 15°C to 55°C range with a simple room temperature adjustment.

Figure 7. Bias current of LM11 varies linearly with temperature so it can be effectively compensated with this circuit. Bias currents less than 5 pA over 15°C to 55°C range or 20 pA over -55°C

# noise

The broadband noise of a bipolar transistor is given by

to +100°C are practical.

$$e_n = kT\sqrt{2\Delta f/ql_c}. (1)$$

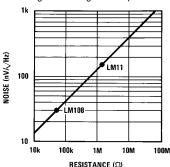

Therefore, operating the input transistors at low collector current does increase noise. Because the noise of most op amps is greater than the theoretical noise voltage of the input transistors, the noise increase from low current input buffers is not as great as might be expected. In addition,

TL/H/8722-8

Figure 8. Increased noise of LM11 is consequence of low collector current in input transistors. But in high impedance applications, op amp noise is masked by the thermal noise of source resistance given above.

when operating from higher source resistances, op amp noise is obscured by resistor noise, as shown in Figure 8.

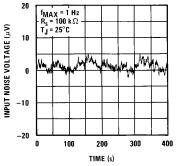

Low frequency noise is not as easily accounted for as broadband noise, but lower operating currents increase noise in much the same fashion. The low frequency noise of the LM11, shown in Figure 9, is a bit less than FETs but greater than that of the LM108 when it is operated from source resistances less than 500 k $\Omega$ .

TL/H/8722-9

Figure 9. Low frequency noise of LM11 is high compared to other bipolar devices but somewhat less than FETs. It is equal to LM108 operating from 500 kΩ source resistances.

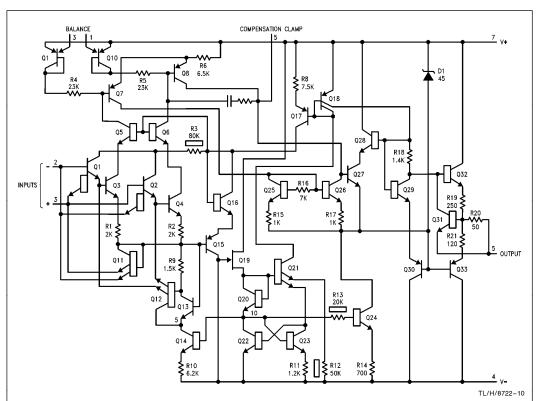

### complete circuit

A schematic diagram of an IC op amp using the techniques described is shown in Figure 10. Other than the input stage, the circuitry is much like the LM112, a compensated version of the LM108 that includes offset balancing.

One significant change has been the inclusion of wafer level trimming for offset voltage. This is done using zener-zap trimming across portions of the input stage collector load resistors, R4 and R5. This kind of zener is simply the emitter base junction of an NPN transistor. When pulsed with a large reverse current at wafer sort, the junction is destroyed by the formation of a low resistance filament between the emitter and base contact beneath the protective oxide. This shorts out a portion of the collector load resistor. The process is repeated on binary weighted segments until the offset voltage has been minimized.

Offset voltage of the LM11 is conservatively specified at 300 µV. Although low enough for most applications, offset voltage trimming is provided for fine adjustment. Balance range is determined by the resistance of the balance potentiometer, varying from  $\pm 5$  mV at 100 k $\Omega$  to  $\pm 400~\mu V$  at 1 k $\Omega$ . Incidentally, when nulling offset voltages of 300  $\mu$ V, the thermal matching of balance-pot resistance to the internal resistors is not a significant factor.

The actual balancing is done on the emitters of lateral PNP transistors, Q9 and Q10, that imbalance the collector loads of the input stage. This particular arrangement was used so that no damage would result from accidental connection of the balance pins to voltages outside either supply. Not obvious is that a balance pin voltage 15V more negative than can effectively short these PNP transistors with a parallel P-channel MOS transistor, forcing the output to one limit or another.

Figure 10. Complete schematic of the LM11. Except for the input stage, circuit is much like the LM112, a compensated version of the LM108 that includes offset balancing.

Although the LM11 is specified to a lower voltage than the LM108, the minimum common-mode voltage is a diode drop further from  $V^-$  because the bleed current generator, Q12 and Q13, has been added.

Proceeding from the input stage, the second stage amplifier is a differential pair of lateral PNPs, Q7 and Q8. These feed a current mirror, Q25 and Q26, which drive a super-gain follower, Q27. The collector base voltage of Q26 is kept near zero by including Q28. The current mirror is bootstrapped to the output so that second stage gain error depends only on how well Q7 and Q8 match with changes in output voltage. This gives a gain of 120 dB in a two stage amplifier. Frequency compensation is provided by MOS capacitor C1.

The output stage is a complementary class-B design with current limiting. Biasing has been altered so that the guaranteed output current is twice the LM108. A zener diode, D1, limits output voltage swing to prevent stressing the MOS capacitor to the point of catastrophic failure in the event of gross supply transients.

The main bias current generator design (Q20-Q23) is due to Dobkin [3]. It is powered by Q19, a collector FET. The circuit is auto-compensated so that output current of Q14 and Q21 varies as absolute temperature and changes by less than 1% for a 100:1 shift in Q19 current.

## speed

With a unity gain bandwidth of 500 kHz and a 0.3 V/ $\mu$ s slew rate the LM11 is not fast. But it is no slower than might be expected for a supply current of only 300  $\mu$ A.

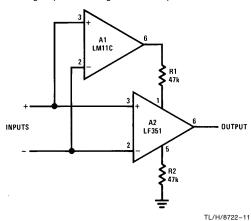

If the precision of the LM11 is required along with greater speed, the circuit in *Figure 11* might be used. Here, the LM11 senses input voltage and makes appropriate adjustments to the balance terminals of a fast FET amplifier. The main signal path is through the fast amplifier.

Figure 11. The LM11 can zero offset of fast FET op amp in either inverting or non-inverting configurations. Speed is that of fast amplifier. FET amplifier can be capacitively coupled to critical input to eliminate its leakage current.

Surprisingly, this connection will work even as a voltage follower. The common-mode slew recovery of the LM11 is about 10  $\mu s$  to 1 mV, even for 30V excursions. This was accomplished by minimizing or bootstrapping stray capacitances and providing clamping to limit the voltage excursion across the strays.

When bias current is an important consideration, it will be advisable to ac couple the FET op amp to the critical input. Reference [2] discusses this and other practical aspects of fast operation with the LM11.

#### conclusions

A new IC op amp has been described that can not only increase the performance of existing equipment but also creates new design possibilities. Op amp error has been reduced to the point where other problems can dominate. Many of the practical difficulties encountered in high impedance circuitry are discussed in reference [4] along with solutions. A number of tested designs using these techniques are given in reference [2].

The LM11 is not the result of any breakthrough in processing technology. It is simply a modification of ICs that have been in volume production for over 10 years. The improvements have resulted primarily from an understanding of strange behavior observed on the earlier ICs and taking advantage of certain inherent characteristics of bipolar transistors that were not fully appreciated.

As users of the LM11 may have discovered, the offset voltage and bias current specifications are quite conservative. It seems possible to offer 50  $\mu V$  offset voltage and perhaps 1  $\mu V/^{\circ} C$  drift even on low cost parts. Taking full advantage of 5 pA bias current would require guarded 10-pin TO-5 packages or 14-pin DIP packages. Further, the feasibility of reducing low frequency noise to 2  $\mu V$  and 0.1 pA, peak to peak, has been demonstrated on prototype parts.

#### acknowledgement

The author would like to acknowledge the contributions of Dennis Foltz for solving the rather formidable production test problems of the LM11.

#### references

- [1] R.J. Widlar, "IC op amp beats FETs on input current", National Semiconductor AN-29, December 1969.

- [2] R.J. Widlar, R. Pease and M. Yamatake, "Applying a new precision op amp", National Semiconductor AN-242, April 1980.

- [3] R. Dobkin, U.S. patent no. 3930172.

- [4] R.J. Widlar, "Working with high impedance op amps", National Semiconductor AN-241, February 1980.

# LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959

Fax: 1(800) 737-7018

National Semiconductor Europe

Fax: (+49) 0.180-530 85 86

Email: onjwge@tevm2.nsc.com

Deutsch Tel: (+49) 0.180-530 85 85

English Tel: (+49) 0.180-532 78 32

Français Tel: (+49) 0.180-532 35

Italiano Tel: (+49) 0.180-534 16 80

National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600

Fax: (852) 2736-9960

National Semiconductor Japan Ltd. Tel: 81-043-299-2309 Fax: 81-043-299-2408

# IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

# Products Applications

Audio www.ti.com/audio Communications and Telecom www.ti.com/communications **Amplifiers** amplifier.ti.com Computers and Peripherals www.ti.com/computers dataconverter.ti.com Consumer Electronics www.ti.com/consumer-apps **Data Converters DLP® Products** www.dlp.com **Energy and Lighting** www.ti.com/energy DSP dsp.ti.com Industrial www.ti.com/industrial Clocks and Timers www.ti.com/clocks Medical www.ti.com/medical Interface interface.ti.com Security www.ti.com/security

Logic Space, Avionics and Defense <u>www.ti.com/space-avionics-defense</u>

Power Mgmt power.ti.com Transportation and Automotive www.ti.com/automotive

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID <u>www.ti-rfid.com</u>

OMAP Mobile Processors www.ti.com/omap

Wireless Connectivity www.ti.com/wirelessconnectivity

TI E2E Community Home Page <u>e2e.ti.com</u>