### **Design Goals**

| Supply                  | Load                                       | Comparator Output Status (OUT) |                            |

|-------------------------|--------------------------------------------|--------------------------------|----------------------------|

| Operating Voltage Range | MAX Operating Voltage (V <sub>OVER</sub> ) | SUPPLY < V <sub>OVER</sub>     | SUPPLY ≥ V <sub>OVER</sub> |

| 12 V to 36 V            | 30 V                                       | V <sub>OL</sub> < 0.4 V        | V <sub>OH</sub> = SUPPLY   |

### **Design Description**

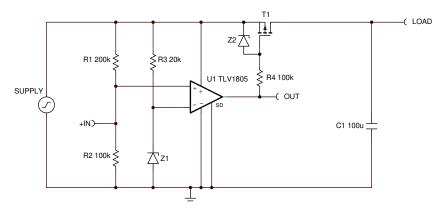

This overvoltage protection circuit uses a high-voltage comparator with a push-pull output stage to control a P-Channel MOSFET that connects the SUPPLY to the LOAD. When the SUPPLY voltage exceeds the overvoltage threshold ( $V_{OVER}$ ), the output of the comparator goes HIGH and disconnects the LOAD from the SUPPLY by opening the P-Channel MOSFET. Likewise, when the SUPPLY voltage is below  $V_{OVER}$ , the output of the comparator is LOW and connects the LOAD to the SUPPLY.

### **Design Notes**

- 1. Select a high-voltage comparator with a push-pull output stage.

- 2. Select a reference voltage that is below the lowest operating voltage range for the SUPPLY.

- 3. Calculate values for the resistor divider so the critical overvoltage level occurs when the input to the comparator (+IN) reaches the comparator's reference voltage.

- 4. Limit the source-gate voltage of the P-Channel MOSFET so that it remains below the device's maximum allowable value.

1

### **Design Steps**

- 1. Select a high-voltage comparator with a push-pull output stage that can operate at the highest possible SUPPLY voltage. In this application, the highest SUPPLY voltage is 36 V.

- Determine an appropriate reference level for the overvoltage detection circuit. Since the lowest operating voltage for the SUPPLY is 12 V, a 10 V zener diode (Z<sub>1</sub>) is selected for the reference (V<sub>REF</sub>).

- 3. Calculate value of R3 by considering the minimum bias current to keep the  $Z_1$  regulating at 10V. A minimum bias current of 100  $\mu$ A is used along with the minimum SUPPLY voltage of 12 V.

$$R_3 = \frac{SUPPLY~(min) - V_{ZENER}}{I_{BIAS}~(min)} = \frac{12V - 10V}{100 \mu A} = 20 \ k\Omega$$

Calculate the resistor divider ratio needed so the input to the comparator (+IN) crosses the reference voltage (10 V) when the SUPPLY rises to the target overvoltage level (V<sub>OVER</sub>) of 30 V.

$$V_{\text{REF}} = V_{\text{OVER}} \times \left(\frac{R_2}{R_1 + R_2}\right)$$

$$\left(\frac{R_2}{R_1 + R_2}\right) = \frac{V_{\text{REF}}}{V_{\text{OVER}}} = \frac{10V}{30V} = 0.333$$

5. Select values for R<sub>1</sub> and R<sub>2</sub> that yield the resistor divider ratio of 0.333 V by using the following equation or using the online at *Voltage Divider Calculator*.

If using the following equation, choose a value for  $R_2$  in the 100 k $\Omega$  range and calculate for  $R_1$ . In this example, a value of 100 k was chosen for  $R_2$ .

$$R_1 = R_2 \left(\frac{V_{\text{OVER}}}{V_{\text{REF}}} - 1\right) = 100 \quad \text{k}\Omega \quad \left(\frac{30V}{10V} - 1\right) = 200 \quad \text{k}\Omega$$

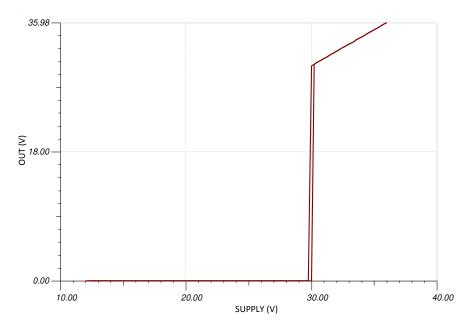

- 6. Note that the TLV1805 which is used in application circuit has 15 mV of hysteresis. This means that the actual switching threshold will be 7.5 mV higher than the switching threshold (VREF) when the SUPPLY is rising and 7.5 mV lower when the SUPPLY is falling. The result of the hysteresis is most easily seen in the DC Simulation curve. Since SUPPLY is resistor divided down by a factor of 3, the net impact to the SUPPLY switching threshold is 3 times this amount.

- 7. Verify that the current through the resistor divider is at least 100 times higher than the input bias current of the comparator. The resistors can have high values to minimize power consumption in the circuit without adding significant error to the resistor divider.

- Select a zener diode (Z<sub>2</sub>) to limit the source-gate voltage (V<sub>SG</sub>) of the P-Channel MOSFET so that it remains below the device's maximum allowable value. It is common for P-Channel, power MOSFETs to have a V<sub>SG</sub> max value of 20 V, so a 16 V zener is placed from source to gate.

- Calculate a value for the current limiting resistor (R<sub>4</sub>). When SUPPLY rises above 16 V and Z<sub>2</sub> begins to conduct, R<sub>4</sub> limits the amount of current that the comparator output will sink when its output is LOW. With a nominal SUPPLY voltage of 24 V, the sink current is limited to 80 μA.

$$I_{\text{SINK}} = \left(\frac{\text{SUPPLY} - V_{Z2}}{R_4}\right) = \left(\frac{24V - 16V}{100 \text{ k}\Omega}\right) = 80 \text{ }\mu\text{A}$$

## **Design Simulations**

## **DC Simulation Results**

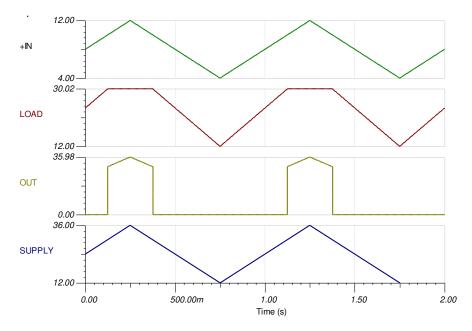

## **Transient Simulation Results**

#### **References:**

- 1. Analog Engineer's Circuit Cookbooks

- 2. SPICE Simulation File SNOAA20

- 3. TI Precision Labs

# **Design Featured Comparator**

| TLV1805-Q1 / TLV1805 |               |  |  |

|----------------------|---------------|--|--|

| Vs                   | 3.3 V to 40 V |  |  |

| V <sub>inCM</sub>    | Rail-to-rail  |  |  |

| V <sub>OUT</sub>     | Push-Pull     |  |  |

| V <sub>os</sub>      | 500 μV        |  |  |

| Hysteresis           | 15 mV         |  |  |

| ۱ <sub>Q</sub>       | 135 µA        |  |  |

| t <sub>PD(HL)</sub>  | 250 ns        |  |  |

| TLV1805              |               |  |  |

## **Design Alternate Comparator**

|                     | TLV3701 / TLV370x-Q1 | TLC3702 / TLC3702-Q1 |

|---------------------|----------------------|----------------------|

| Vs                  | 2.5 V to 16 V        | 4 V to 16 V          |

| V <sub>inCM</sub>   | Rail-to-rail         | -1 V from VDD        |

| V <sub>OUT</sub>    | Push-Pull            | Push-Pull            |

| V <sub>os</sub>     | 250 μV               | 1.2 mV               |

| Hysteresis          | n/a                  | n/a                  |

| Ι <sub>Q</sub>      | 0.56 μΑ              | 9.5 µA/Ch            |

| t <sub>PD(HL)</sub> | 36 µs                | 0.65 µs              |

|                     | TLV3701              | TLC3702              |

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated