## Application Note Designing an Isolated Buck Converter using the LMR38020

Gui He, Yang Wu, Daniel Li

#### ABSTRACT

Fly-Buck<sup>™</sup> converter is a multi-output converter topology implemented with a synchronous buck converter on the primary side and additional isolated outputs can be produced like in a conventional flyback converter on the secondary side of a transformer, It has been widely used in various applications due to many inherent advantages.

This article show cases a simple and cost-effective Fly-Buck<sup>™</sup> solution using the LMR38020 device from Texas Instruments. The operating principle and step-by-step design procedures are presented, along with experimental results and some design tips for optimal design.

## **Table of Contents**

| 1 Introduction                                       | 2  |

|------------------------------------------------------|----|

| 2 Fly-Buck Converter                                 | 2  |

| 3 Fly-Buck Basic Operation                           |    |

| 3.1 Basic Intervals of Steady State Operation        |    |

| 3.2 Impact Of Leakage Inductor On Fly-Buck Operation |    |

| 4 Design A Fly-Buck Converter with LMR38020          |    |

| 4.1 IC Select                                        |    |

| 4.2 Switching Frequency Set                          | 6  |

| 4.3 Transformer Design                               | 6  |

| 4.4 Output Capacitor Selection                       | 7  |

| 4.5 Secondary Output Diode                           |    |

| 4.6 Preload Resistor                                 |    |

| 5 Bench Test Results                                 | 8  |

| 5.1 Typical Switching Waveforms Under Steady State   |    |

| 5.2 Start Up                                         |    |

| 5.3 Efficiency                                       |    |

| 5.4 Load Regulation                                  |    |

| 5.5 Short Circuit                                    |    |

| 5.6 Thermal Performance                              |    |

| 6 Design Considerations                              | 12 |

| 7 Summary                                            |    |

| 8 References                                         |    |

## List of Figures

| Figure 2-1. General Fly-Buck Converter Circuit                                                                | 2 |

|---------------------------------------------------------------------------------------------------------------|---|

| Figure 3-1. Fly-Buck™ Steady State Operation Waveforms                                                        |   |

| Figure 3-2. Fly-Buck Converter Circuit Considering Parasitic                                                  | 4 |

| Figure 3-3. Current Waveforms Affected by Leakage Inductance                                                  | 5 |

| Figure 4-1. Fly-Buck Converter With LMR38020                                                                  | 5 |

| Figure 5-1. LMR38020 Fly-Buck Converter Schematic                                                             | 8 |

| Figure 5-2. LMR38020 Fly-Buck Demo Board                                                                      | 8 |

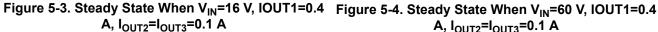

| Figure 5-3. Steady State When V <sub>IN</sub> =16 V, IOUT1=0.4 A, I <sub>OUT2</sub> =I <sub>OUT3</sub> =0.1 A | 9 |

| Figure 5-4. Steady State When VIN=60 V, IOUT1=0.4 A, IOUT2=IOUT3=0.1 A                                        | 9 |

| Figure 5-5. Steady State When VIN=16 V, IOUT1=0.4 A, IOUT2=IOUT3=0 A                                          |   |

| Figure 5-6. Steady State When VIN=60 V, IOUT1=0.4 A, IOUT2=IOUT3=0 A                                          |   |

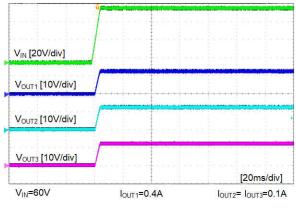

| Figure 5-7. Start Up When V <sub>IN</sub> =16 V, Full Load           | 9  |

|----------------------------------------------------------------------|----|

| Figure 5-8. Start Up When V <sub>IN</sub> =60 V, Full Load           |    |

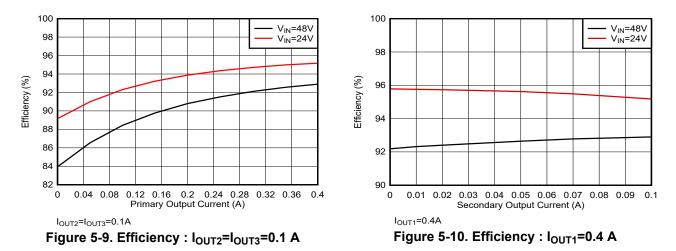

| Figure 5-9. Efficiency : I <sub>OUT2</sub> =I <sub>OUT3</sub> =0.1 A |    |

| Figure 5-10. Efficiency : I <sub>OUT1</sub> =0.4 A                   | 10 |

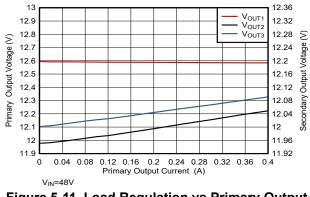

| Figure 5-11. Load Regulation vs Primary Output Current               | 10 |

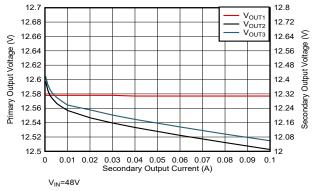

| Figure 5-12. Load Regulation vs Secondary Output Current             | 10 |

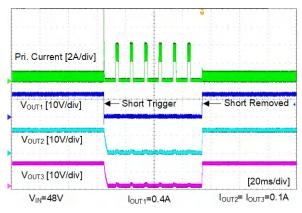

| Figure 5-13. Short Circuit On Primary Output                         | 11 |

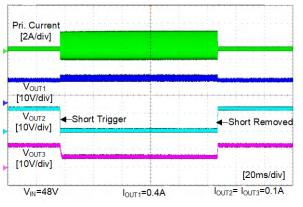

| Figure 5-14. Short Circuit On Secondary Output                       | 11 |

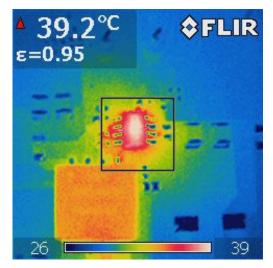

| Figure 5-15. Thermal Performance When VIN=48 V, Full Load            | 11 |

|                                                                      |    |

# List of Tables Table 4-1. Fly-Buck Converter Design Parameters.....

## Trademarks

Fly-Buck<sup>™</sup> is a trademark of Texas Instruments. All trademarks are the property of their respective owners.

## **1** Introduction

Conventionally, the flyback converter topology has been a very popular solution for applications that need multi isolated output voltages. However, Flyback converter design has to employ either an opto-coupler or an auxiliary winding as the feedback circuit for output regulation. The loop compensation becomes difficult and sometimes tricky. And the use of optocoupler not only increases the solution cost but also reduces the circuit reliability. To overcome these drawbacks, the Fly-Buck<sup>™</sup> converter topology, also called isolated buck, are introduced.

A Fly-Buck<sup>™</sup> converter is one of the most suitable options for low power applications in industrial automation, communication power supplies, intelligent electric meters, and so on. The Fly-Buck<sup>™</sup> has the merits of low component count, simple design, high efficiency, and good transient response when compared with the conventional flyback converters.

The LMR38020 is a 4.2 V to 80 V, 2-A synchronous buck converter in the HSOIC-8 package. It's internal compensation saves external component and simplifies the IC pin out, making the LMR38020 ideal for Fly-Buck™ converter applications.

This article presents the basic operating principles of a Fly-Buck<sup>™</sup> converter by going over key waveforms and design equations. The step-by-step design procedure is given through an example of one non-isolated and two isolated outputs.

## 2 Fly-Buck Converter

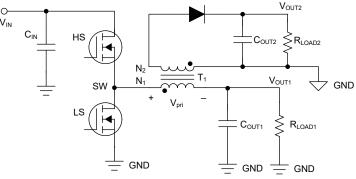

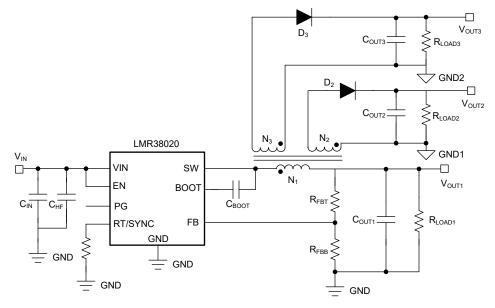

Figure 2-1. General Fly-Buck Converter Circuit

The Fly-Buck<sup>™</sup> converter is based on standard buck converter topology in which the regular inductor is replaced by a coupled inductor or transformer such that one or multiple isolated secondary outputs can be produced. Figure 2-1 shows a Fly-Buck converter with one non-isolated output and one isolated output. Additional isolated output can be easily obtained by more secondary windings coupled to the transformer core.

Basically the closed loop operation is still a buck converter and it regulates the primary output voltage. The secondary output voltage is also regulated via cross regulation by winding coupling.

Therefore the Fly-Buck converter is able to produce a tightly regulated primary output voltage, along with one or more isolated outputs without the need of an optocoupler. This means that designing a Fly-Buck<sup>™</sup> converter is relatively straightforward and similarly to designing a typical buck converter with minor adjustments.

## 3 Fly-Buck Basic Operation

## 3.1 Basic Intervals of Steady State Operation

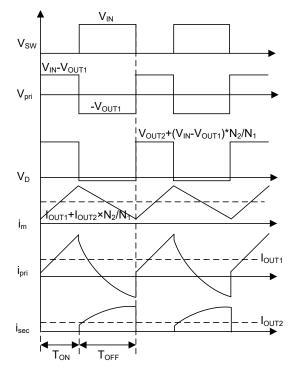

Figure 3-1 shows the typical steady state waveforms of a Fly-Buck<sup>TM</sup> converter in which V<sub>pri</sub> is the primary voltage across the coupled inductor, i<sub>m</sub> is the magnetizing current, i<sub>m</sub> and i<sub>sec</sub> are primary side current and secondary side current.

The operation of the Fly-Buck<sup>™</sup> converter basically has two modes: TON and TOFF.

Figure 3-1. Fly-Buck<sup>™</sup> Steady State Operation Waveforms

## T<sub>ON</sub> Mode

This mode is the same as traditional synchronous buck converter when the main switch(HS) is ON. The voltage stress of the low-side (LS) switch is the input voltage( $V_{IN}$ ). The magnetizing inductance,  $L_m$  is charged by the input voltage minus the primary output voltage as in the regular buck converter. The secondary winding current remains zero for the diode  $D_2$  is reverse biased according to the winding polarity configuration, and  $D_2$  sees voltage stress of ( $N_2/N_1$ )×( $V_{IN}$ - $V_{OUT1}$ )+ $V_{OUT2}$ . The isolated output capacitor  $C_{OUT2}$  is supplying the load current.

## T<sub>OFF</sub> Mode

In this mode LS is ON and HS is OFF. V<sub>pri</sub> becomes negative, forward biasing D<sub>2</sub> to force a secondary current to flow to transfer part of the stored energy in the coupled inductor to the secondary output capacitor, C<sub>OUT2</sub> and the load, R<sub>Load2</sub>.

Unlike the buck converter,  $i_{pri}$  in Fly-buck decreases at a faster rate, owing to supplying current to both loads,  $I_{OUT1}$  and  $I_{OUT2}$ .

The secondary current waveform is determined by the load, leakage inductance, and output capacitance. The current direction of  $i_{pri}$  at the end of one switching cycle (positive or negative) depends on factors including the current ratio of  $I_{OUT2}$ :  $I_{OUT1}$  and current ripple.

The primary output voltage is the same as a buck converter and is given by Equation 1.

$$V_{OUT1} = \frac{T_{ON}}{T_{ON} + T_{FF}} V_{IN} = D \times V_{IN}$$

(1)

The secondary output voltage is given by Equation 2.

$$V_{OUT2} = V_{OUT1} \times \left(\frac{N_2}{N_1}\right) - V_F$$

(2)

where

- $N_1$  and  $N_2$  are the turns of the primary winding and secondary winding

- V<sub>F</sub> is the forward voltage drop of the secondary rectifier diode

#### 3.2 Impact Of Leakage Inductor On Fly-Buck Operation

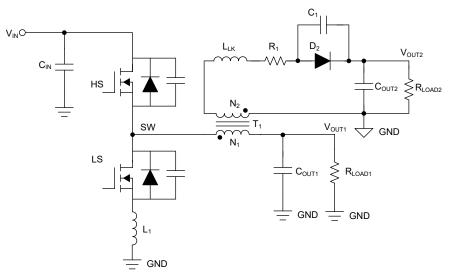

In a real circuit, the transformer has leakage inductance and other parasitic inductance or capacitance as shown in Figure 3-2, which can affect the secondary current waveform.

Figure 3-2. Fly-Buck Converter Circuit Considering Parasitic

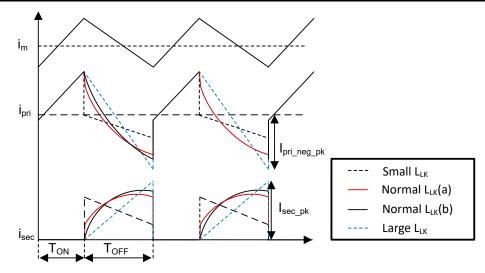

The Figure 3-3 shows the typical current waveform under different levels of leakage inductance(L<sub>LK</sub>).

When  $L_{LK}$  is low, the  $i_{sec}$  ramps up quickly to charge up  $C_{OUT2}$ . With larger  $L_{LK}$ ,  $i_{sec}$  rises linearly,resulting in larger negative peak current for  $i_{pri}$ . If the negative peak current of  $i_{pri}$  reaches the negative current limit of the device, the LS will be turned off and the charging to  $C_{OUT2}$  will be terminated. Consequently this would result in less energy being transferred to the output and produce lower output voltage.

Therefore, the leakage inductance should be minimized and the maximum duty cycle must be chosen carefully to mitigate these issues. When the secondary output has no load, the turn on of LS can force a small current in the secondary side, and it would gradually charge up  $C_{OUT2}$ . Since there is no load to discharge  $C_{OUT2}$ , a net charge will be accumulated on  $C_{OUT2}$  and raise the  $V_{OUT2}$  remarkably. In order to prevent this from happening, a preload must be added to the secondary output to help removing the net charge on  $C_{OUT2}$  so as to maintain the output voltage at the setting point.

TRUMENTS

www.ti.com

Figure 3-3. Current Waveforms Affected by Leakage Inductance

## 4 Design A Fly-Buck Converter with LMR38020

Figure 4-1 shows the schematic for a 12-V output Fly-Buck<sup>™</sup> regulator with two 12-V isolated output.

| Design Parameter                             | Example Value |  |  |

|----------------------------------------------|---------------|--|--|

| Input voltage range (V <sub>IN</sub> )       | 16 V to 60 V  |  |  |

| Primary output voltage (V <sub>OUT1</sub> )  | 12.6 V        |  |  |

| Primary load current (I <sub>OUT1</sub> )    | 0.4 A         |  |  |

| Isolated output voltage (V <sub>OUT2</sub> ) | 12 V          |  |  |

| Isolated load current (I <sub>OUT2</sub> )   | 0.1 A         |  |  |

| Isolated output voltage (V <sub>OUT3</sub> ) | 12 V          |  |  |

| Isolated load current (I <sub>OUT3</sub> )   | 0.1 A         |  |  |

| Switching frequency (f <sub>sw</sub> )       | 250 kHz       |  |  |

|                                              |               |  |  |

| Table 4-1. F | ly-Buck Converte | er Design Parameters |

|--------------|------------------|----------------------|

|--------------|------------------|----------------------|

## 4.1 IC Select

To operate as a Fly-Buck<sup>™</sup> converter, an IC that offers Forced Pulse Width Modulation (FPWM) must be selected to make sure that the part can handle negative inductor current. In this case, the LMR38020FADDA is selected, Which is a 80 V, 2 A synchronous buck converter operating by peak current mode control.

## 4.2 Switching Frequency Set

The switching frequency( $f_{sw}$ ) of the LMR38020 is programmable with the resistor RT placed across the RT/ SYNC pin and GND pin. Equation 3 determines the value of  $R_T$  for a targeted switching frequency.

$$R_{T}(k\Omega) = 30970 \times f_{SW}(kHz)^{-1.027}$$

(3)

EXAS

TRUMENTS

www.ti.com

Smaller sized transformer can be selected when fsw is higher. But when  $f_{sw}$  is high, which means the  $T_s$  is small, if the D is large, there might not be enough energy transferring to isolated side during the small  $t_{off}$ .

Considering D>0.5 when  $V_{IN}=V_{INMIN}=16$  V in this application, 250 kHz is chosen. If  $D_{max}$  is no larger than 0.5, higher  $f_{sw}$  can be selected.

It is normally recommended  $D_{MAX}$ <0.5 in Fly-Buck design. A greater duty can cause lower secondary  $V_{out}$  than the set point. The worst situation happens when  $V_{IN} = V_{IN\_MIN}$ ,  $I_{OUT1}=0$ ,  $I_{OUT2}=I_{OUT1\_MAX}$ . Refer to this article *Pick the Right Turns Ratio for a Fly-Buck*<sup>TM</sup> *Converter* for detailed discussion on this topic.

#### 4.3 Transformer Design

The Fly-Buck<sup>™</sup> transformer has the same mechanism as the flyback converter<sup>[1]</sup>. Thus, they share the same principles in design. For optimal performance, it is important to minimize the transformer leakage inductance and parasitic capacitance. Both the Flyback and Fly-Buck topologies are susceptible to ringing problem from these parasitic.

#### 4.3.1 Turns Ratio

In this Fly-Buck design example, windings are needed to produce one primary output voltage and two secondary output voltages.

Due to the winding coupling, the following voltage relationships are established between the three outputs:

$$V_{OUT2} = V_{OUT1} \times \left(\frac{N_2}{N_1}\right) - V_F$$

(4)

$$V_{OUT3} = V_{OUT1} \times {\binom{N_3}{N_1}} - V_F$$

(5)

$V_F$  is the diode forward voltage drop of  $D_2$  and  $D_3$ . According to the equation, the turns ratio is selected to 1:1:1 assuming the forward drop VF is 0.6V for both diodes.

#### 4.3.2 Magnetic Inductance

The calculation of  $L_{PRI}$  can be the same as calculating the inductance for an ordinary buck regulator, basing on the desired primary ripple current.

Typically, a ripple current of between 20% and 40% of the primary current is used. Equation 6 determines the primary current in a fly-buck converter and Equation 7 determines the required primary inductance.

$$I_{PRI} = I_{OUT1} + I_{OUT2} \times \frac{N_2}{N_1} + I_{OUT3} \times \frac{N_3}{N_1}$$

(6)

$$L_{PRI} = \frac{(V_{IN} - V_{OUT1})}{K \times I_{PRI} \times f_{SW}} \times \frac{V_{OUT1}}{V_{IN}}$$

(7)

Where

6

K=ripple current factor=20% to 40%.

#### 4.3.3 Check I<sub>pk</sub>

Both the positive and negative peak value through the primary winding must not exceed the current limits of the LMR38020.

This peak-to-peak magnetizing current ripple is:

$$\Delta i_{\rm m} = \frac{(V_{\rm IN} - V_{\rm OUT1}) \times D}{L_{\rm PRI} \times f_{\rm SW}}$$

(8)

The positive peak current of I<sub>PRI</sub> is given by Equation 9 :

$$I_{PRI_PK_POS} = \left(I_{OUT1} + I_{OUT2} \times \frac{N_2}{N_1} + I_{OUT3} \times \frac{N_3}{N_1}\right) + \left(\frac{\Delta i_m}{2}\right)$$

(9)

The negative peak current of  $I_{PRI}$  depends on different leakage inductance and parasitic parameters and finding an explicit expression is difficult. Commonly, an empirical and conservative linear approximation can be used, in which the secondary current is represented as a linear function and ramps up from zero at the start of  $T_{off}$  time<sup>[1]</sup>.

$$I_{PRI_{PK_{NEG}}} = I_{0UT1} - \left(\frac{\Delta i_{m}}{2}\right) - \left(I_{0UT2} \times \frac{N_{2}}{N_{1}} + I_{0UT3} \times \frac{N_{3}}{N_{1}}\right) \times \frac{(1+D)}{(1-D)}$$

(10)

This gives a simple estimation of the negative peak current in worst case. However, the conservative estimate may lead to an unnecessary over design of the transformer. In fact the secondary current is usually a convex curve, as shown in Figure 3-3, therefore the actual  $I_{PRL PK NEG}$  is actually smaller than the calculated.

Equation 10 is more close to reality when the leakage inductance is very large, and when I<sub>OUT1</sub>=0, V<sub>IN</sub>=V<sub>INMIN</sub>.

#### 4.4 Output Capacitor Selection

#### 4.4.1 Primary Output Capacitor

As in the regular buck converter, the Fly-Buck primary output capacitor  $C_{OUT1}$  must satisfyEquation 11. In Fly-Buck<sup>TM</sup>, The reflected secondary winding current adds to the primary winding current, leading to the condition that  $C_{OUT1}$  must satisfy Equation 12.

$$C_{\text{OUT1}} > \frac{\Delta i_{\text{m}}}{8 \times f_{\text{SW}} \times \Delta V_{\text{OUT1}}}$$

(11)

$$C_{OUT1} > \frac{\left(I_{OUT2} \times \frac{N_2}{N_1} + I_{OUT3} \times \frac{N_3}{N_1}\right) \times T_{ON(max)}}{\Delta V_{OUT1}}$$

(12)

More output capacitance can be used to improve load transient response. The optimization of output capacitor over the whole line and load ranges can be easily done experimentally.

#### 4.4.2 Secondary Output Capacitor

The secondary output current ( $I_{OUT2}$ ) is sourced by  $C_{OUT2}$  during on time  $T_{ON}$ . The secondary output capacitor ripple voltage can be calculated using Equation 13. Similar conditions apply to  $C_{OUT3}$  for the other secondary output of this design example.

$$C_{OUT2} > \frac{I_{OUT2} \times T_{ON(max)}}{\Delta V_{OUT2}}$$

(13)

#### 4.5 Secondary Output Diode

The secondary output diode must block the maximum input voltage reflected to the secondary side of the transformer. Choose a diode of the voltage rating satisfying Equation 14. And the current rating of the diode must be larger than the secondary output current. Schottky diodes are the best choices. Ultra-fast recovery diodes can also be used. The forward voltage drop of the diode is also an important factor to consider for it limits the maximum secondary output voltage.

$$V_{R} > 1.3 \times \left(V_{IN} \times \frac{N_{2}}{N_{1}} + V_{OUT2}\right)$$

#### 4.6 Preload Resistor

The secondary output must have a preload connected at all time to prevent the output voltage from rising too high under no load conditions. In this example, a 10 k $\Omega$  resistor is used as a preload on the secondary output. Another option is to use a Zener diode to clamp the secondary output voltage.

## **5** Bench Test Results

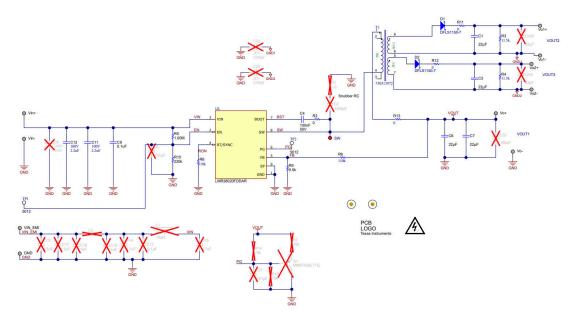

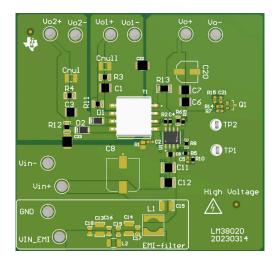

Figure 5-1 shows the LMR38020 Fly-Buck<sup>™</sup> Converter Schematic. Figure 5-2 is the top view of the PCB.

Figure 5-1. LMR38020 Fly-Buck Converter Schematic

Figure 5-2. LMR38020 Fly-Buck Demo Board

Texas

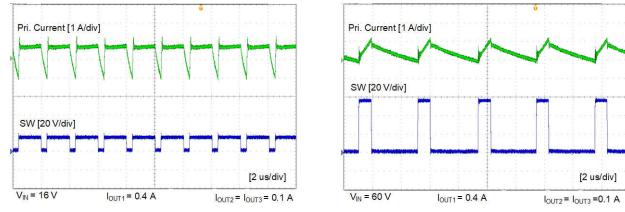

## 5.1 Typical Switching Waveforms Under Steady State

A, IOUT2=IOUT3=0 A

In Figure 5-5, switching frequency f<sub>sw</sub> becomes higher. This normally happens when V<sub>IN</sub>=V<sub>IN MIN</sub> and D>0.5, and toff becomes smaller, hence the primary current hits the negative peak current limit. Therefore, theLMR38020 turns off the LS and start a new cycle at earlier time, causing the switching frequency to increase.

## 5.2 Start Up

#### Bench Test Results

Figure 5-7 and Figure 5-8 show typical start-up behavior. The secondary output voltage tracks the primary output voltage during the soft start sequence.

The secondary voltages' drop during startup for about 18ms can be explained by the IC OCP blaning time (please refer to the data sheet). The heavier secondary load lighter primary load brings more secondary voltage drops during this time. Adding a small amount of preload on the primary side can help reduce these secondary voltage drop during startup..

#### 5.3 Efficiency

The efficiency vs load conditions when  $V_{IN}$ =24V and  $V_{IN}$ =48V are shown in Figure 5-9 and Figure 5-10.

#### 5.4 Load Regulation

The load regulation shown in Figure 5-11 and Figure 5-12, The regulation tolerance on the primary Vout can achieve 1% over the entire load range, and the secondary Vout can achieve<10%. Adding some preload at secondary output can improve the load regulation performance.

Figure 5-12. Load Regulation vs Secondary Output Current

## 5.5 Short Circuit

The LMR38020 enters hiccup protection mode when the primary side output is shorted, as shown in Figure 5-13. Once the short condition is removed, the converter is automatically recovered..

Figure 5-13. Short Circuit On Primary Output

Figure 5-14. Short Circuit On Secondary Output

## **5.6 Thermal Performance**

Figure 5-15 is the thermal image of the example Fly-Buck PCB board under  $V_{IN}$ =48 V and full load (7.2W). The ambient temperature T<sub>a</sub> is 26°C. The highest temperature rise T<sub>rise</sub> is <15°C.

Figure 5-15. Thermal Performance When V<sub>IN</sub>=48 V, Full Load

## 6 Design Considerations

Following are some tips in choosing a proper IC as well as in designing a Fly-Buck™ converter design.

- An IC that offers Forced Pulse Width Modulation (FPWM) needs to be selected and make sure the part can handle negative inductor current. A good example is the LMR38020FADDA.

- To design an (1+n) output Fly-Buck converter, where n is the number of secondary outputs,, the designer needs to choose a buck converter IC having the equivalent rated load current no less than (i<sub>pri</sub>+N<sub>ps1</sub>\*I<sub>sec1</sub>+ N<sub>ps2</sub>\*I<sub>sec2</sub>+...+ N<sub>psn</sub>\*I<sub>secn</sub>), N<sub>psn</sub> is the turns ratio.

- Make sure i<sub>pri\_pk</sub> of the Fly-Buck design does not exceed either the positive nor negate peak current limit of the IC.

- A small preload may be required for the secondary outputs to prevent the output voltage from rising too high under no load in that output. Usually, the preload resistor is in the order or 1kΩ-10kΩ. It is also possible to use a Zener based clamp instead of a preload resistor. This avoids power loss in the Zener under normal operations..

- It is preferred to select the primary output voltage V<sub>pri</sub> for D<sub>max</sub> < 0.5 (V<sub>INMIN</sub>>2\*V<sub>pri</sub>). If D<sub>max</sub> > 0.5, pay attention to check the isolated output voltage regulation under V<sub>INMIN</sub> and making sure it can satisfy design requirements. (Note that a lower L<sub>LK</sub> and lower f<sub>sw</sub> helps to achieve larger duty cycle).

- Do not short secondary V<sub>OUT</sub> to ground for long time if the device does not have a hiccup mode for negative overcurrent protect.

## 7 Summary

The LMR38020 buck converter can easily be configured to implement a simple and cost effective Fly-Buck™ converter to produce one or multiple isolated secondary outputs. The LMR38020 Fly-Buck™ Converter has good regulation accuracy, high efficiency, low-part count, small solution size and low cost.

## 8 References

- Texas Instruments, *Designing a Simple and Low Cost Flybuck Solution with the TPS54308* application note.

- Texas Instruments, *Designing an Isolated Buck (Fly-Buck™) Converter using the LMR*36520 application note.

- Texas Instruments, LMR38020 4.2-V to 80-V, 2-A, Synchronous SIMPLE SWITCHER® Power Converter with 40-µA IQ data sheet.

- Texas Instruments, *Pick the Right Turns Ratio for a Fly-Buck*™ *Converter* application note.

- Texas Instruments, Designing Isolated Rails on the Fly with Fly-Buck Converters application note.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated