# **TMS320TCI6482 EMAC Performance Data**

---

*High-Performance and Multicore Processors**Brighton Feng*

## **Abstract**

The TMS320TCI6842 integrates an EMAC module, which can be used to move data between the devices on the same Ethernet network. It supports 10/100/1000Mbps, and four types of interfaces to the physical layer device (PHY): MII, RMII, GMII and RGMII.

This document provides EMAC bandwidth data measured under various operating conditions. The CPU load relevant to the Ethernet packet transfer is also provided.

## **Contents**

|     |                                               |   |

|-----|-----------------------------------------------|---|

| 1   | Introduction .....                            | 2 |

| 2   | Measurement Methodology and Assumptions ..... | 3 |

| 3   | EMAC performance data .....                   | 5 |

| 3.1 | 1000Mbps bandwidth .....                      | 5 |

| 3.2 | CPU Load for EMAC .....                       | 6 |

| 3.3 | 100Mbps performance data .....                | 7 |

| 4   | Summary .....                                 | 8 |

| 5   | References .....                              | 8 |

## **Figures**

|          |                                                                |   |

|----------|----------------------------------------------------------------|---|

| Figure 1 | Block Diagram of the EMAC Performance Measurement System ..... | 3 |

| Figure 2 | 1000M EMAC Bandwidth & CPU Load vs Packet Size .....           | 5 |

| Figure 3 | 100M EMAC Bandwidth & CPU Load vs Packet Size .....            | 7 |

## 1 Introduction

The TMS320TCI6842 integrates an EMAC (Ethernet Media Access Control) module, which can be used to move data between the device and another host connected to the same Ethernet network. It supports 10/100/1000 Mbps operation, and supports four types of interfaces to the physical layer device (PHY): standard media independent interface (MII), reduced pin count media independent interface (RMII), standard gigabit media independent interface (GMII) and reduced pin count gigabit media independent interface (RGMII). For more details about EMAC of TCI6482 please refer to [TMS320TCI648x DSP EMAC MDIO Module Reference Guide \(SPRUE12\)](#).

This document provides measured bandwidth data achieved on 1GHz TMS320TCI6482 EVM board.

There are two TCI6482 DSPs on the EVM. One of them connects to an MII PHY, which is used to measure 100Mbps operation performance; and the other connects to an RGMII PHY, which is used to measured 1000Mbps operation performance. 10Mbps operation is not measured, because it is rarely used.

The CPU load relevant to the Ethernet packet transfer is also measured, which mainly includes:

- Filling transmit descriptor and starting transfer

- Filling receive descriptor and starting receiver

- Interrupt service for transmit, receive and status update

## 2 Measurement Methodology and Assumptions

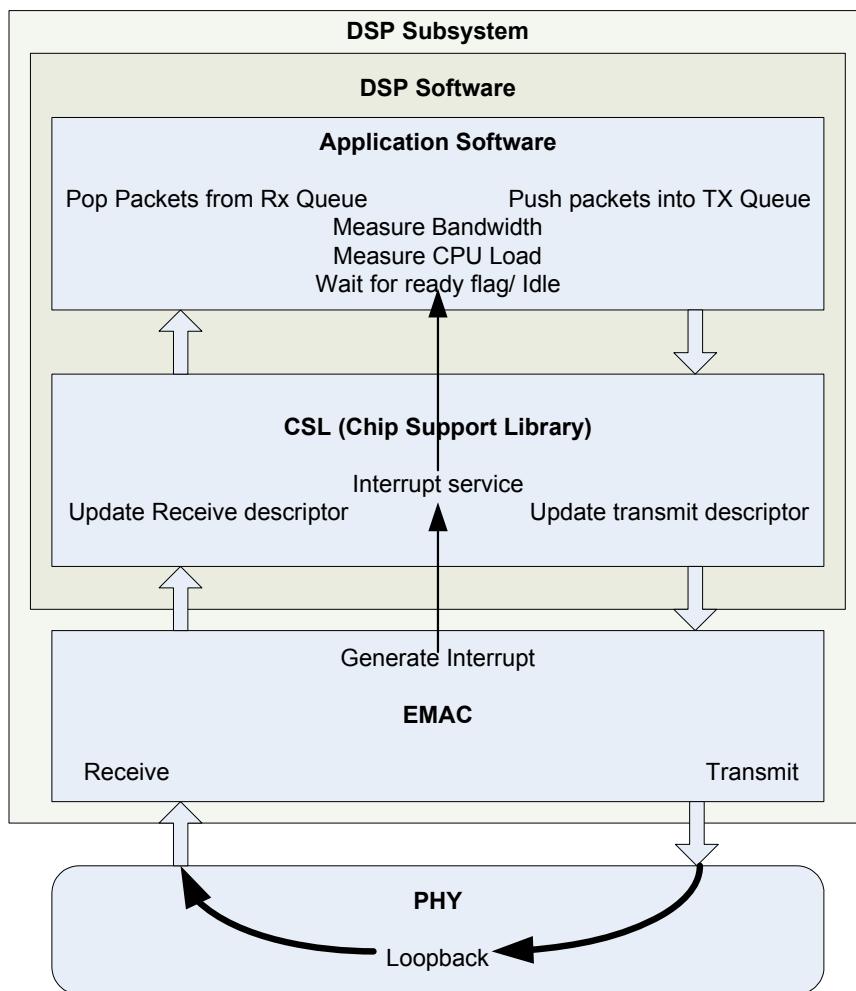

Figure 1 describes the measurement system.

**Figure 1** Block Diagram of the EMAC Performance Measurement System

The application software pushes the transmit packet into a Tx Queue; the CSL library is used to control the EMAC to transmit the packet from the TX Queue to PHY. The Ethernet packets are looped back in the PHY to the Rx port of the EMAC.

When the EMAC receives packets, it generates an interrupt to the CSL. Then, the CSL moves the received packet into the Rx Queue. The application software pops the Ethernet packet from the Rx Queue.

After packets are transmitted, the EMAC generates another interrupt, which triggers the CSL interrupt service routine to continuously transmit additional packets in the Tx Queue.

The bandwidth measured is only for the payload, the formula for calculating bandwidth is:

Bandwidth= (packet payload)\* (total packets transferred)/ (total time used)

Generally, DSP core is faster than EMAC, so after DSP software finishes transmitting or receiving, it waits for next transfer. This period is the idle state. The idle time under this situation is measured; the CPU load is calculated based on the idle time.

(CPU Load for EMAC)= 100% - (idle time between transfer)/ (total time used)

This test performs receive and transmit in parallel, so the bandwidth and CPU load measured is full duplex.

Other assumptions for the performance measurement include:

- 1GHz CPU clock is used.

- 64 Rx and 64 Tx descriptors buffer are used.

- The software is optimized with -o3 option.

- All data and code are in internal memory.

- 32KB L1D and 32KB L1P cache are used.

### 3 EMAC performance data

The actual payload bandwidth is primarily affected by packet size. The CPU load for EMAC transfer is affected by packet size and interrupt pacing. This section provides performance data for different packet size and interrupt pacing.

#### 3.1 1000Mbps bandwidth

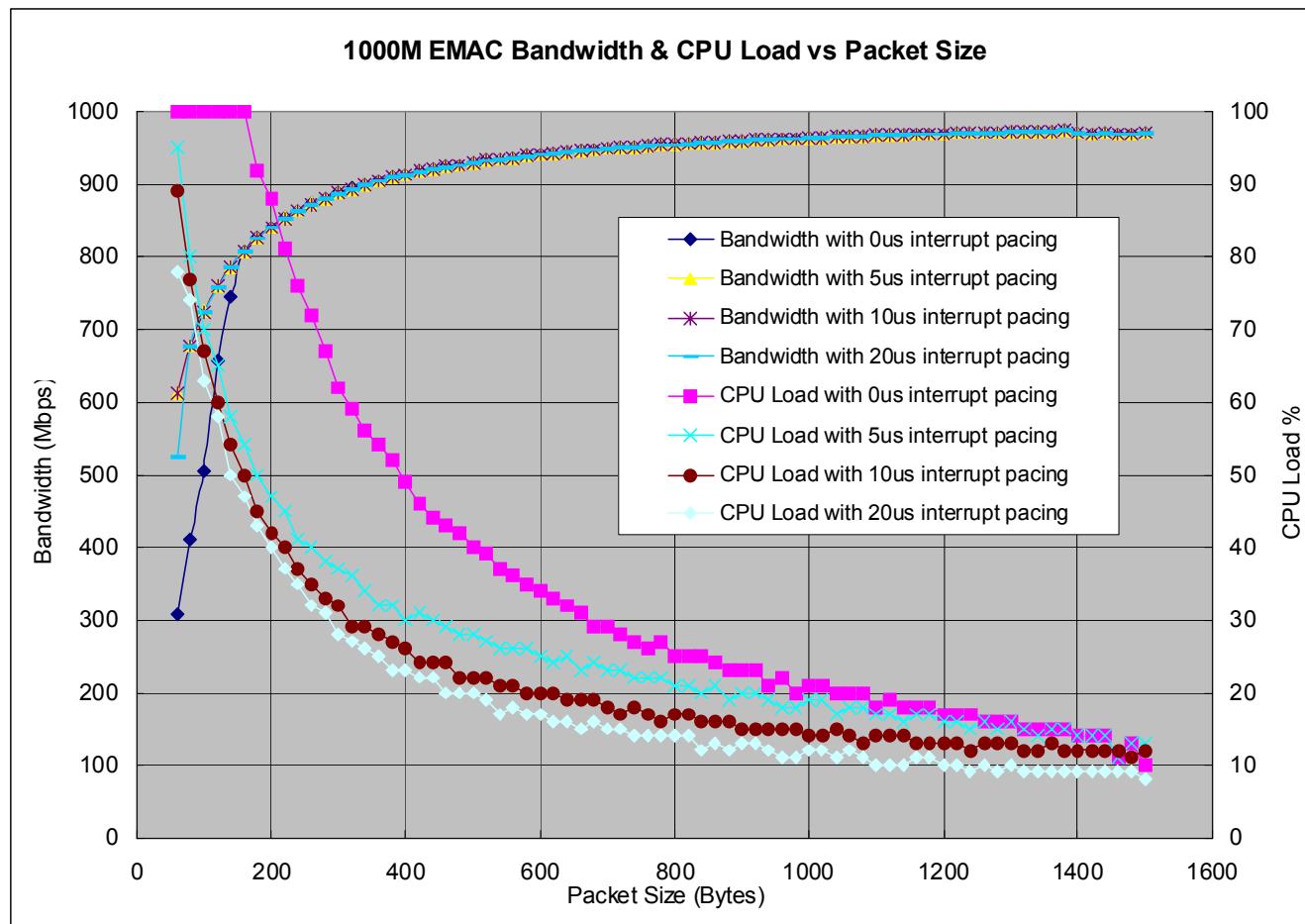

The curves on the top of [Figure 2](#) show the actual payload bandwidth achieved under different conditions. The X axis is packet size (payload size); the Y axis is bandwidth.

**Figure 2** 1000M EMAC Bandwidth & CPU Load vs Packet Size

The actual bandwidth increases with packet size. For packets larger than 200 bytes, the actual bandwidth is higher than 800Mbps; for packets smaller than 200 bytes, the actual bandwidth decreases.

The interrupt pacing has no noticeable effect on bandwidth when the packets are larger than 200 bytes, while it does have a noticeable effect on bandwidth when the packets are smaller than 200 bytes. Longer interrupt pacing increases bandwidth. However, interrupt pacing longer than 10us does not increase bandwidth.

### 3.2 CPU Load for EMAC

The curves on the bottom of [Figure 2](#) show the CPU load for EMAC packet transfer under different conditions. The X axis is packet size (payload size); the right Y axis is CPU load.

The CPU load for the EMAC decreases with increased packet size. The CPU load for the smallest packet size is close to 100%, while it is only about 10% for the largest packet size.

The interrupt pacing also affects the CPU load for the EMAC though the effect is more obvious for small packet sizes. Longer interrupt pacing decreases CPU load.

Longer interrupt pacing decreases the CPU load, while also increasing the transfer delay. Additionally, longer interrupt pacing results in a larger data buffer and more packet descriptors.

(Minimum Data Buffer Size)= (Bandwidth)\*(interrupt pacing)

(Descriptor number)= packets transferred during interrupt pacing = (Interrupt pacing)/(transfer time for one packet)

So, interrupt pacing should be a trade-off that the system designer can control. The figures above show that interrupt pacing longer than 10us can not obviously decrease CPU load further, so interrupt pacing longer than 10us is not necessary.

### 3.3 100Mbps performance data

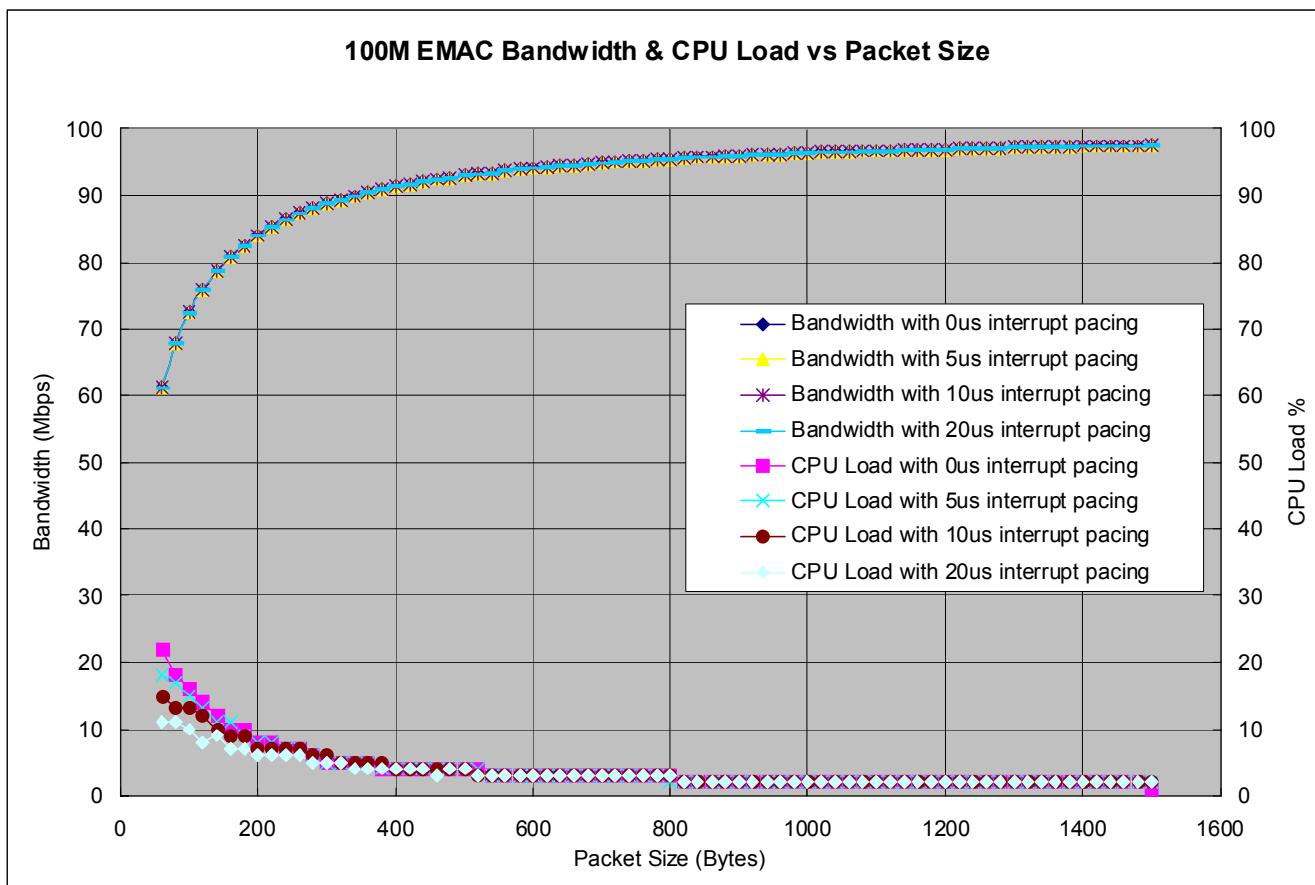

Figure 3 shows the 100Mbps operation performance achieved under different conditions. The X axis is packet size (payload size); the left Y axis is payload bandwidth; the right Y axis is relevant CPU Load for EMAC.

**Figure 3** 100M EMAC Bandwidth & CPU Load vs Packet Size

These results are similar to 1000Mbps operation; to achieve more than 80% theoretical bandwidth, packets should be larger than 200 bytes. The charts don't show noticeable effect of interrupt pacing on the bandwidth of 100Mbps operation.

CPU load is relatively low for 100Mbps operation; it is just about 1/10 of 1000Mbps operation. Longer interrupt pacing decreases CPU load, while interrupt pacing longer than 10us is not necessary.

## 4 Summary

The TCI6482 EMAC performance is dramatically affected by packet size. Packets larger than 200 bytes are recommended to achieve more than 80% of theoretical bandwidth.

For 1000Mbps operation, interrupt pacing affects the CPU load for the EMAC. Longer interrupt pacing can reduce CPU load, while increasing transfer latency. Interrupt pacing longer than 10us does not improve EMAC performance, so it is not recommended.

## 5 References

1. [\*TMS320TCI648x DSP EMAC MDIO Module Reference Guide \(SPRUUE12\)\*](#)

## IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

### Products

|                             |                                                                    |

|-----------------------------|--------------------------------------------------------------------|

| Amplifiers                  | <a href="http://amplifier.ti.com">amplifier.ti.com</a>             |

| Data Converters             | <a href="http://dataconverter.ti.com">dataconverter.ti.com</a>     |

| DLP® Products               | <a href="http://www.dlp.com">www.dlp.com</a>                       |

| DSP                         | <a href="http://dsp.ti.com">dsp.ti.com</a>                         |

| Clocks and Timers           | <a href="http://www.ti.com/clocks">www.ti.com/clocks</a>           |

| Interface                   | <a href="http://interface.ti.com">interface.ti.com</a>             |

| Logic                       | <a href="http://logic.ti.com">logic.ti.com</a>                     |

| Power Mgmt                  | <a href="http://power.ti.com">power.ti.com</a>                     |

| Microcontrollers            | <a href="http://microcontroller.ti.com">microcontroller.ti.com</a> |

| RFID                        | <a href="http://www.ti-rfid.com">www.ti-rfid.com</a>               |

| RF/IF and ZigBee® Solutions | <a href="http://www.ti.com/lprf">www.ti.com/lprf</a>               |

### Applications

|                    |                                                                          |

|--------------------|--------------------------------------------------------------------------|

| Audio              | <a href="http://www.ti.com/audio">www.ti.com/audio</a>                   |

| Automotive         | <a href="http://www.ti.com/automotive">www.ti.com/automotive</a>         |

| Broadband          | <a href="http://www.ti.com/broadband">www.ti.com/broadband</a>           |

| Digital Control    | <a href="http://www.ti.com/digitalcontrol">www.ti.com/digitalcontrol</a> |

| Medical            | <a href="http://www.ti.com/medical">www.ti.com/medical</a>               |

| Military           | <a href="http://www.ti.com/military">www.ti.com/military</a>             |

| Optical Networking | <a href="http://www.ti.com/opticalnetwork">www.ti.com/opticalnetwork</a> |

| Security           | <a href="http://www.ti.com/security">www.ti.com/security</a>             |

| Telephony          | <a href="http://www.ti.com/telephony">www.ti.com/telephony</a>           |

| Video & Imaging    | <a href="http://www.ti.com/video">www.ti.com/video</a>                   |

| Wireless           | <a href="http://www.ti.com/wireless">www.ti.com/wireless</a>             |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2009, Texas Instruments Incorporated