# AM571x Thermal Considerations

Ahmad Rashed

#### ABSTRACT

This application report discusses thermal performance of the Sitara<sup>™</sup> AM571x series processors. The data presented demonstrates the effects of different thermal management strategies in terms of processor junction temperature and power consumption across MPU loading and ambient temperature.

#### Contents

| 1 | Overview         | 2 |

|---|------------------|---|

| 2 | Important Notes  | 2 |

| 3 | Test Overview    | 2 |

| 4 | Data and Results | 3 |

| 5 | References       | 7 |

#### List of Figures

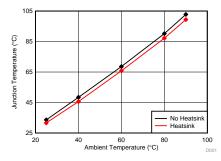

| 1 | OS Idle - OPP_NOM (Junction Temp vs Ambient Temp)                | 4 |

|---|------------------------------------------------------------------|---|

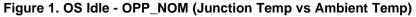

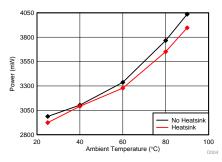

| 2 | OS Idle - OPP_NOM (Power Consumption vs Ambient Temp)            | 4 |

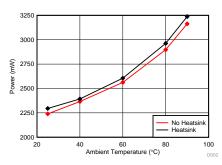

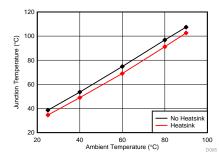

| 3 | Dyrystone(Core 1) @ OPP_NOM (Junction Temp vs Ambient Temp)      | 5 |

| 4 | Dyrystone(Core 1) @ OPP_NOM (Power Consumption vs Ambient Temp)  | 5 |

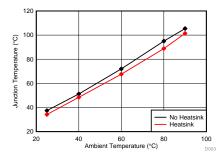

| 5 | Dyrystone(Core 1) @ OPP_OD (Junction Temp vs Ambient Temp)       | 6 |

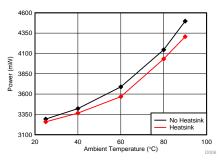

| 6 | Dyrystone(Core 1) @ OPP_OD (Power Consumption vs Ambient Temp)   | 6 |

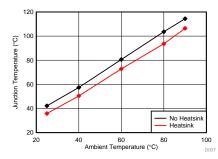

| 7 | Dyrystone(Core 1) @ OPP_HIGH (Junction Temp vs Ambient Temp)     | 7 |

| 8 | Dyrystone(Core 1) @ OPP_HIGH (Power Consumption vs Ambient Temp) | 7 |

|   |                                                                  |   |

#### List of Tables

| <br>3 |

|-------|

|       |

#### Trademarks

Sitara is a trademark of Texas Instruments. Arm, Cortex are registered trademarks of Arm Limited. Linux is a registered trademark of Linus Torvalds. All other trademarks are the property of their respective owners.

Overview

www.ti.com

#### 1 Overview

An internal AM571x board was used in this experiment to gather thermal data with different processor loading and ambient temperature. Ambient temperature was controlled with programmable environmental chamber.

The collected data can be utilized to correlate the thermal performance of the processor and power consumption at a given processor load and junction temperature, based on ambient temperature and thermal management.

Tests were repeated with the following thermal management:

- Bare package (no heatsink)

- Low-cost heatsink

#### 2 Important Notes

The environmental chamber used to collect this data circulates air internally to maintain homogeneous internal temperature, and does not accurately simulate the environment on the bench or end product. This is important to consider in passive cooling applications where air circulation can significantly impact PCB, package, and heatsink power dissipation efficiency.

The data presented in this test was gathered with a typical device, representing nominal silicon process and leakage. Thermal performance and power consumption can vary significantly due to process variation. Extra margin must be designed in to account for worst case process variation (leakage).

#### 3 Test Overview

The following CPU loading schemes were characterized with the internal AM571x board for this report.

#### 3.1 OS Idle

The AM571x processor is idling after booting the out-of-box configuration of Processor SDK Linux<sup>®</sup> v04.02.00. No display was connected to the AM571x board. MPU, GPU, and IVA cores are powered but automatically clock gated while the DSP and IPU cores are both power and clock gated.

#### 3.2 Dhrystone

Dhrystone is a single-threaded benchmark, capable of utilizing approximately 100% of one Arm® Cortex®-A15 core. Dhyrstone is included in the TI Processor SDK. Tests were conducted with the A15 running at 1.0 GHz (OPP\_NOM), 1.188GHz (OPP\_OD), and 1.5GHz (OPP\_HIGH).

#### 3.3 Temperature Measurement

Reported temperature data is measured by on-die sensors to the approximate actual junction temperature. Temperature for each use-case is measured after soaking for 5 minutes. Under lab conditions, it was determined a 5 minute period allows the processor to reach stable temperature.

The TI Processor SDK provides Linux drivers for these sensors, and can be queried from the commandline, for example:

```

# cat /sys/class/thermal/thermal_zone0/temp

71800

```

## 3.4 **OPP Definitions**

Operating performance points (OPP) levels define a max frequency per fixed voltage level in each voltage domain. Table 1 lists frequency of each subsystem per OPP for the AM571x processor.

Dynamic Voltage Frequency Scaling (DVFS) refers to a software technique where the system-on-chip (SoC) supplies with AVS support are changed from one OPP level (voltage and frequency pair) to another in order to either adapt to a changing work-load, or in order to avoid device operation outside of desired temperature bounds.

This SoC only supports DVFS on the MPU domain. For DSP and GPU domains, the OPP levels should be set during boot by the initial bootloader. Ensure that the selected OPP level meets the application's needs and all thermal testing is conducted at the desired OPP level.

|                |               | OPP_NOM             | OPP_OD              | OPP_HIGH            |

|----------------|---------------|---------------------|---------------------|---------------------|

| Voltage Domain | Clock Domain  | Max Frequency (MHz) | Max Frequency (MHz) | Max Frequency (MHz) |

| VD_MPU         | MPU_CLK       | 1000                | 1176                | 1500                |

| VD_DSP         | DSP_CLK       | 600                 | 700                 | 750                 |

| VD_IVA         | IVA_GCLK      | 388.3               | 430                 | 532                 |

| VD_GPU         | GPU_CLK       | 425.6               | 500                 | 532                 |

| VD_CORE        | DDR3 / DDR3L  | 667 (DDR3-1333)     | N/A                 | N/A                 |

|                | CORE_IPUx_CLK | 212.8               | N/A                 | N/A                 |

|                | L3_CLK        | 266                 | N/A                 | N/A                 |

| VD_RTC         | RTC_FCLK      | 0.034               | N/A                 | N/A                 |

#### Table 1. Supported OPP vs Max Frequency

#### 4 Data and Results

This section contains the raw data and graphs of the test experiments described above. All of the data was gathered running the latest Linux Processor SDK. All tests were conducted without an external display installed.

## 4.1 OPP Settings and Linux Thermal Framework

Tests were conducted with Processor SDK 04.02.00, with following OPP levels:

| Default OPP Levels |      |      |      |  |  |  |  |

|--------------------|------|------|------|--|--|--|--|

| MPU GPU DSP IVA    |      |      |      |  |  |  |  |

| NOM                | HIGH | HIGH | HIGH |  |  |  |  |

The MPU domain OPP defaults to NOM when idle and increases to HIGH when under load. OPP levels for DSP and IVA cores can be changed but that must be done by editing the U-Boot defconfig file with the desired OPP level and recompiling.

Applicable to the AM571x, the Linux kernel on this device utilizes the CPUFreq driver to support multiple OPPs for the MPU domain and dynamically change between them. As such a desired max frequency must be set if seeking power consumption at a frequency lower than the max.

Additionally, the Linux thermal framework needs to be disabled, otherwise, the max fequency is reduced as the MPU heats up to prevent thermal shutdown. This should only be done for data gathering purposes when the junction temperature exceeds the levels defined in the device tree and is not recommended for a production system.

З

Data and Results

#### 4.2 **Power and Thermal Chamber Measurements**

The tables shown in the following sections contain power consumption and junction temperature measured running OS Idle and Dhrystone single-core use cases at different controlled ambient temperatures with and without an attached heatsink. This silicon process type is nominal. Dhrystone tests were repeated with MPU at each supported OPP.

Junction temperature and power reported in the following sections were sampled at the same time, and are presented in separate tables to aid comprehension.

## 4.3 OS Idle (MPU @ OPP\_NOM)

| OPP Levels      |      |      |      |  |  |  |  |

|-----------------|------|------|------|--|--|--|--|

| MPU GPU DSP IVA |      |      |      |  |  |  |  |

| NOM             | HIGH | HIGH | HIGH |  |  |  |  |

|                  | Ta (°C) |      |      |      |       |  |  |

|------------------|---------|------|------|------|-------|--|--|

| Therm Mgmt       | 25      | 40   | 60   | 80   | 90    |  |  |

| No Heatsink (°C) | 33.6    | 48.4 | 68.6 | 90.2 | 102.8 |  |  |

| Heatsink (°C)    | 31.6    | 45.6 | 65.8 | 87.2 | 99.4  |  |  |

|                  | Ta (°C) |        |        |        |        |  |

|------------------|---------|--------|--------|--------|--------|--|

| Therm Mgmt       | 25      | 40     | 60     | 80     | 90     |  |

| No Heatsink (mW) | 2295    | 2392.7 | 2605.6 | 2962.6 | 3237.4 |  |

| Heatsink (mW)    | 2239.7  | 2365.9 | 2562.1 | 2897.5 | 3162.9 |  |

Figure 2. OS Idle - OPP\_NOM (Power Consumption vs Ambient Temp)

# 4.4 Dhrystone (MPU @ OPP\_NOM)

| OPP Levels      |      |      |      |  |  |  |  |

|-----------------|------|------|------|--|--|--|--|

| MPU GPU DSP IVA |      |      |      |  |  |  |  |

| NOM             | HIGH | HIGH | HIGH |  |  |  |  |

|                  | Ta (°C) |      |      |      |       |  |  |

|------------------|---------|------|------|------|-------|--|--|

| Therm Mgmt       | 25      | 40   | 60   | 80   | 90    |  |  |

| No Heatsink (°C) | 37.4    | 51.2 | 72   | 95   | 105.4 |  |  |

| Heatsink (°C)    | 34.2    | 48.4 | 67.6 | 88.8 | 101.4 |  |  |

# Figure 3. Dyrystone(Core 1) @ OPP\_NOM (Junction Temp vs Ambient Temp)

|                  | Ta (°C) |        |        |        |        |  |

|------------------|---------|--------|--------|--------|--------|--|

| Therm Mgmt       | 25      | 40     | 60     | 80     | 90     |  |

| No Heatsink (mW) | 2987    | 3103.1 | 3336.9 | 3766.1 | 4035.6 |  |

| Heatsink (mW)    | 2923.7  | 3091.3 | 3277.6 | 3651   | 3896.2 |  |

Figure 4. Dyrystone(Core 1) @ OPP\_NOM (Power Consumption vs Ambient Temp)

## 4.5 Dhrystone (MPU @ OPP\_OD)

| OPP Levels      |      |      |      |  |  |  |  |

|-----------------|------|------|------|--|--|--|--|

| MPU GPU DSP IVA |      |      |      |  |  |  |  |

| OD              | HIGH | HIGH | HIGH |  |  |  |  |

|                  | Ta (°C) |      |      |      |       |

|------------------|---------|------|------|------|-------|

| Therm Mgmt       | 25      | 40   | 60   | 80   | 90    |

| No Heatsink (°C) | 38.6    | 53.6 | 74.8 | 96.8 | 107.4 |

| Heatsink (°C)    | 34.6    | 49   | 69   | 91.2 | 102.6 |

# Figure 5. Dyrystone(Core 1) @ OPP\_OD (Junction Temp vs Ambient Temp)

|                  | Ta (°C) |        |        |        |        |

|------------------|---------|--------|--------|--------|--------|

| Therm Mgmt       | 25      | 40     | 60     | 80     | 90     |

| No Heatsink (mW) | 3292.1  | 3421.1 | 3688.5 | 4145.3 | 4497.2 |

| Heatsink (mW)    | 3258.1  | 3365.6 | 3567.9 | 4032.5 | 4306.4 |

## Figure 6. Dyrystone(Core 1) @ OPP\_OD (Power Consumption vs Ambient Temp)

## 4.6 Dhrystone (MPU @ OPP\_HIGH)

| OPP Levels |      |      |      |  |  |

|------------|------|------|------|--|--|

| MPU        | GPU  | DSP  | IVA  |  |  |

| HIGH       | HIGH | HIGH | HIGH |  |  |

|                  | Ta (°C) |      |      |       |       |

|------------------|---------|------|------|-------|-------|

| Therm Mgmt       | 25      | 40   | 60   | 80    | 90    |

| No Heatsink (°C) | 42.2    | 57.4 | 80.6 | 103.6 | 114.4 |

| Heatsink (°C)    | 35.8    | 50.4 | 72.8 | 93.6  | 106.4 |

# Figure 7. Dyrystone(Core 1) @ OPP\_HIGH (Junction Temp vs Ambient Temp)

|                  | Ta (°C) |        |        |        |        |

|------------------|---------|--------|--------|--------|--------|

| Therm Mgmt       | 25      | 40     | 60     | 80     | 90     |

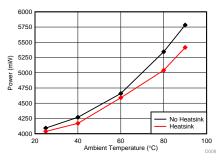

| No Heatsink (mW) | 4092.1  | 4269.2 | 4660.2 | 5344.1 | 5783.1 |

| Heatsink (mW)    | 4037.1  | 4169.4 | 4589.8 | 5040.6 | 5414.9 |

## 5 References

- To learn more about thermal management, visit http://www.ti.com/thermal

- Thermal Design Guide for DSP and ARM Application Processors

- Thermal models can be found in the Models section of Tools and Software in the product folder: http://www.ti.com/product/AM5718/toolssoftware

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated