# Five to Ten Series Cell Lithium-Ion or Lithium-Polymer Battery Protector and Analog Front End

#### **FEATURES**

- 5, 6, 7, 8, 9, or 10 Series-Cell Primary Protection

- PMOS FET Drive for Charge and Discharge FETs

- Capable of Operation with 1-mΩ Sense Resistor

- Supply Voltage Range from 7 V to 50 V

- Low Supply Current of 450 μA Typical

- Integrated 5-V, 25-mA LDO

- Integrated 3.3-V, 25-mA LDO

- Stand-Alone Mode

- Pack Protection Control and Recovery

- Individual Cell Monitoring

- Integrated Cell Balancing

- Programmable Threshold and Delay Time for

- Overvoltage

- Undervoltage

- Overcurrent in Discharge

- Short Circuit in Discharge

- Fixed Overtemperature Protection

- Host Control Mode

- I<sup>2</sup>C Interface to Host Controller

- Analog Interface for Host Cell Measurement and System Charge/Discharge Current

- Host-Controlled Protection Recovery

- Host-Controlled Cell Balancing

#### **APPLICATIONS**

- Cordless Power Tools

- Power Assisted Bicycle/Scooter

- Uninterruptible Power Supply (UPS) Systems

- Medical Equipment

- Portable Test Equipment

#### DESCRIPTION

The bq77PL900 is a five to ten series cell lithium-ion battery pack protector. The integrated I<sup>2</sup>C communications interface allows the bq77PL900 also to be as an analog front end (AFE) for a Host controller. Two LDOs, one 5-V, 25-mA and one 3.3-V, 25-mA, are also included and may be used to power a host controller or support circuitry.

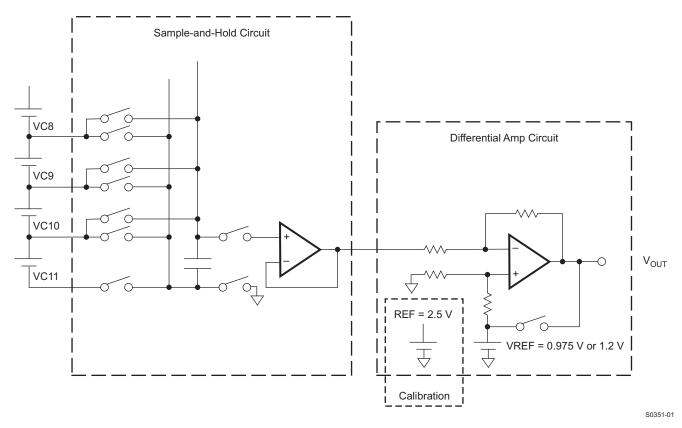

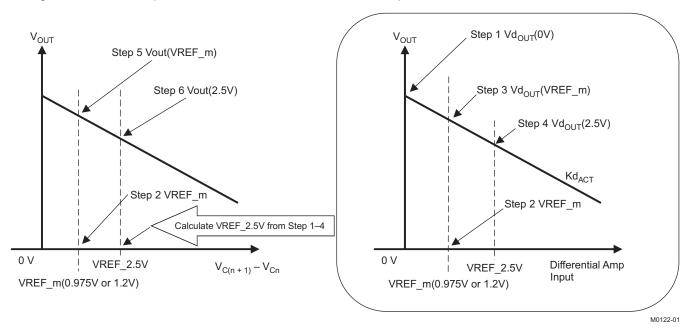

The bq77PL900 integrates a voltage translation system to extract battery parameters such as individual cell voltages and charge/discharge current. Variables such as voltage protection thresholds and detection delay times can be programmed by using the internal EEPROM.

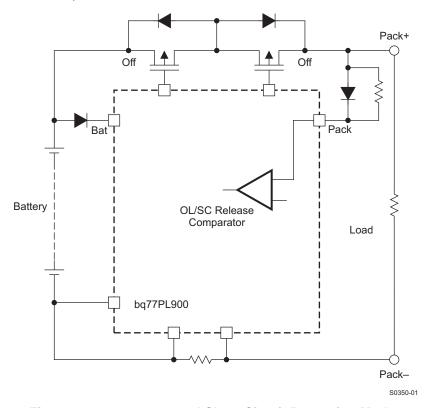

The bq77PL900 can act as a stand-alone self-contained battery protection system (stand-alone mode). It can alternatively be combined with a host microcontroller to offer fuel gauge or other battery management capabilities to the host system (host-control mode).

The bq77PL900 provides full safety protection for overvoltage, undervoltage, overcurrent in discharge, and short circuit in discharge conditions. When the EEPROM programmable safety thresholds are reached, the bq77PL900 turns off the FET drive autonomously. No external components are needed to configure the protection features.

The analog front end (AFE) outputs allow a host controller to observe individual cell voltages and charge/discharge currents. The host controller's analog-to-digital converter connects to the bq77PL900 to acquire these values.

Cell balancing can be performed autonomously, or the host controller can activate it individually via a cell bypass path integrated into the bq77PL900. Internal control registers accessible via the I<sup>2</sup>C interface configure this operation. The maximum balancing bypass current is set via an external series resistor and the internal FET-on resistance (typically 400  $\Omega$ ). Optionally, external bypass cell balance FETs can be used for increased current capability.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

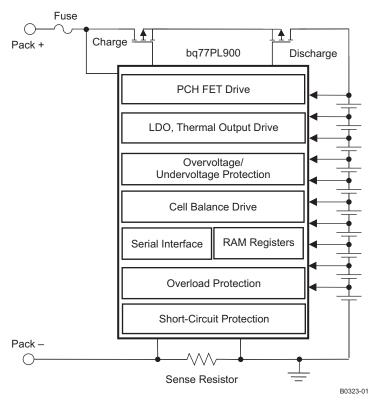

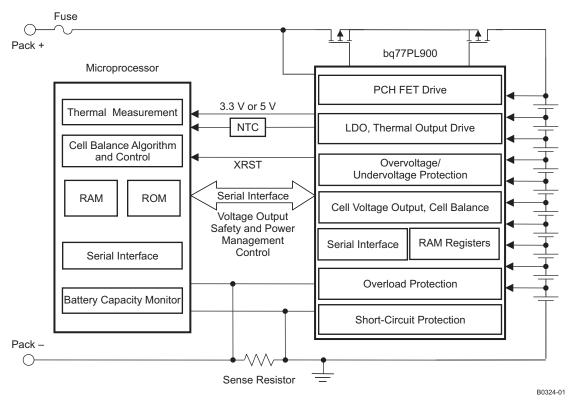

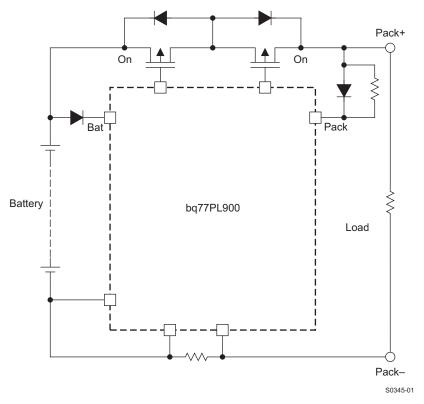

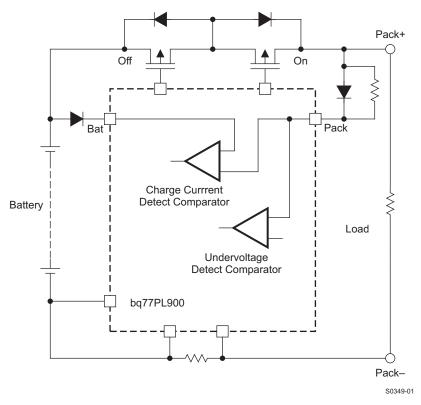

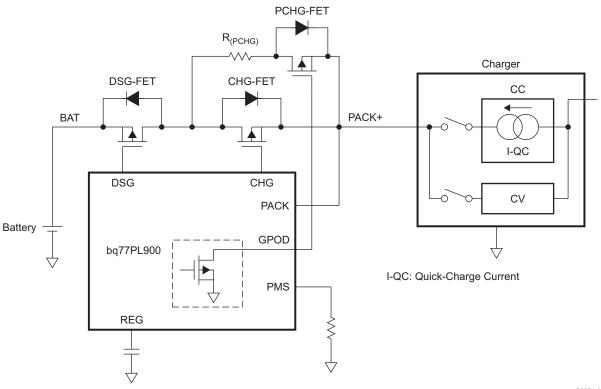

# **TYPICAL IMPLEMENTATION**

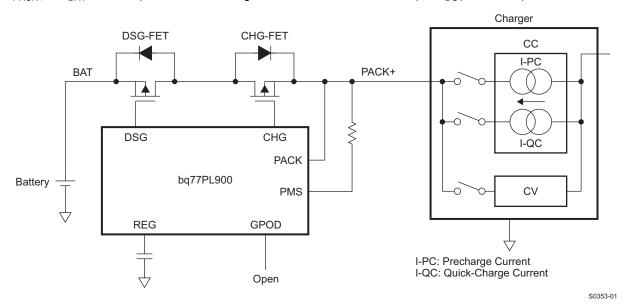

Figure 1. Stand-Alone Mode

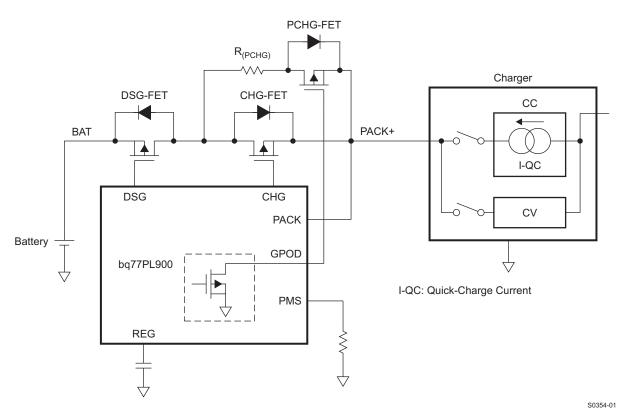

Figure 2. Host-Control Mode

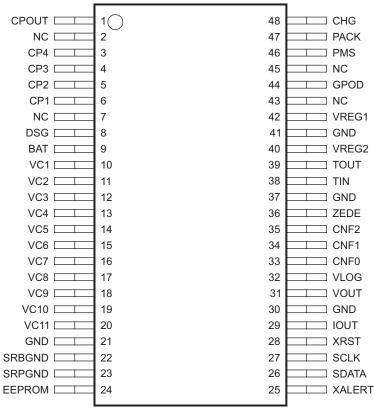

#### **PIN DETAILS**

#### **Pin Out Diagram**

# DL Package (Top View)

#### P0084-01

# **TERMINAL FUNCTIONS**

| NAME   | PIN#       | DESCRIPTION                                                                              |

|--------|------------|------------------------------------------------------------------------------------------|

| BAT    | 9          | Power supply voltage                                                                     |

| CHG    | 48         | Charge FET gate drive                                                                    |

| CNF0   | 33         | Used cell for number determination in combination with CNF1 and CNF2                     |

| CNF1   | 34         | Used cell for number determination in combination with CNF0 and CNF2                     |

| CNF2   | 35         | Used cell for number determination in combination with CNF0 and CNF1                     |

| CP1    | 6          | Charge pump capacitor 2 connection terminal                                              |

| CP2    | 5          | Charge pump capacitor 2 connection terminal                                              |

| CP3    | 4          | Charge pump capacitor 1 connection terminal                                              |

| CP4    | 3          | Charge pump capacitor 1 connection terminal (GND)                                        |

| CPOUT  | 1          | Charge pump output and internal power source.                                            |

| DSG    | 8          | Discharge FET gate drive                                                                 |

| EEPROM | 24         | Active-high EEPROM write-enable pin. During normal operation, should be connected to GND |

| GND    | 21, 30, 37 | Power-supply ground                                                                      |

| GPOD   | 44         | General-purpose N-CH FET open-drain output                                               |

| GND    | 41         | Should be connected to GND                                                               |

| IOUT   | 29         | Amplifier output for charge/discharge current measurement                                |

# **TERMINAL FUNCTIONS (continued)**

| NAME   | PIN#            | DESCRIPTION                                                                                                                                                                |

|--------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NC     | 2, 7, 43,<br>45 | No connect (not electrically connected)                                                                                                                                    |

| PACK   | 47              | PACK positive terminal and alternative power source                                                                                                                        |

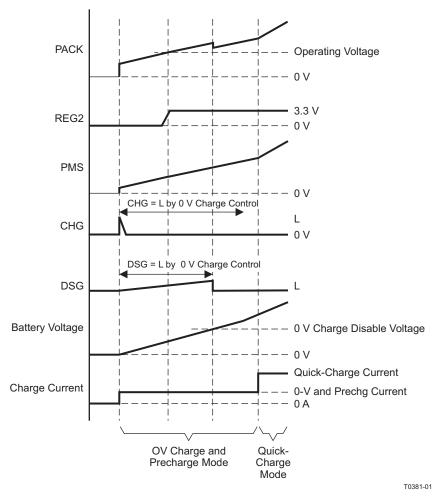

| PMS    | 46              | Determines CHG output state for zero-volt charge                                                                                                                           |

| SCLK   | 27              | Open-drain bidirectional serial interface clock with an internal 10-kΩ pullup to V <sub>LOG</sub>                                                                          |

| SDATA  | 26              | Open-drain bidirectional serial interface data with an internal 10-kΩ pullup to V <sub>LOG</sub>                                                                           |

| SRBGND | 22              | Current sense terminal (Connect Battery to cell's GND)                                                                                                                     |

| SRPGND | 23              | Current-sense positive terminal when discharging relative to SRNGND, current-sense negative terminal when charging relative to SRGND. (Connect to pack GND)                |

| TIN    | 38              | Temperature sensing input                                                                                                                                                  |

| TOUT   | 39              | Thermistor bias current source                                                                                                                                             |

| VC1    | 10              | Sense voltage input terminal for most positive cell, balance current input for most positive cell, and battery stack measurement input                                     |

| VC2    | 11              | Sense voltage input terminal for second-most positive cell, balance current input for second-most positive cell, and return balance current for most positive cell         |

| VC3    | 12              | Sense voltage input terminal for third-most positive cell, balance current input for third-most positive cell, and return balance current for second-most positive cell    |

| VC4    | 13              | Sense voltage input terminal for fourth-most positive cell, balance current input for fourth-most positive cell, and return balance current for third-most positive cell   |

| VC5    | 14              | Sense voltage input terminal for fifth-most positive cell, balance current input for fifth-most positive cell, and return balance current for fourth-most positive cell    |

| VC6    | 15              | Sense voltage input terminal for sixth-most positive cell, balance current input for sixth-most positive cell, and return balance current for fifth-most positive cell     |

| VC7    | 16              | Sense voltage input terminal for seventh-most positive cell, balance current input for seventh-most positive cell, and return balance current for sixth-most positive cell |

| VC8    | 17              | Sense voltage input terminal for eighth-most positive cell, balance current input for eighth-most positive cell, and return balance current for seventh-most positive cell |

| VC9    | 18              | Sense voltage input terminal for ninth-most positive cell, balance current input for ninth-most positive cell, and return balance current for eighth-most positive cell    |

| VC10   | 19              | Sense voltage input terminal for tenth-most positive cell, balance current input for tenth-most positive cell, and return balance current for ninth-most positive cell     |

| VC11   | 20              | Sense voltage input terminal for most negative cell, return balance current for least positive cell                                                                        |

| VLOG   | 32              | Data I/O voltage set by connecting either VREG1 or VREG2                                                                                                                   |

| VOUT   | 31              | Amplifier output for cell voltage measurement                                                                                                                              |

| VREG1  | 42              | Integrated 5-V regulator output                                                                                                                                            |

| VREG2  | 40              | Integrated 3.3-V regulator output                                                                                                                                          |

| XALERT | 25              | Open-drain output used to indicate status register change. (Includes an internal 100-kΩ pullup to V <sub>LOG</sub> .)                                                      |

| XRST   | 28              | Power-on-reset output. Active-low open-drain output with an internal 3-k $\Omega$ pullup to $V_{LOG}$                                                                      |

| ZEDE   | 36              | Protection delay test pin. Minimizes protection delay times when connected to V <sub>LOG</sub> . Programmed delay times used when pulled to GND, normal operation.         |

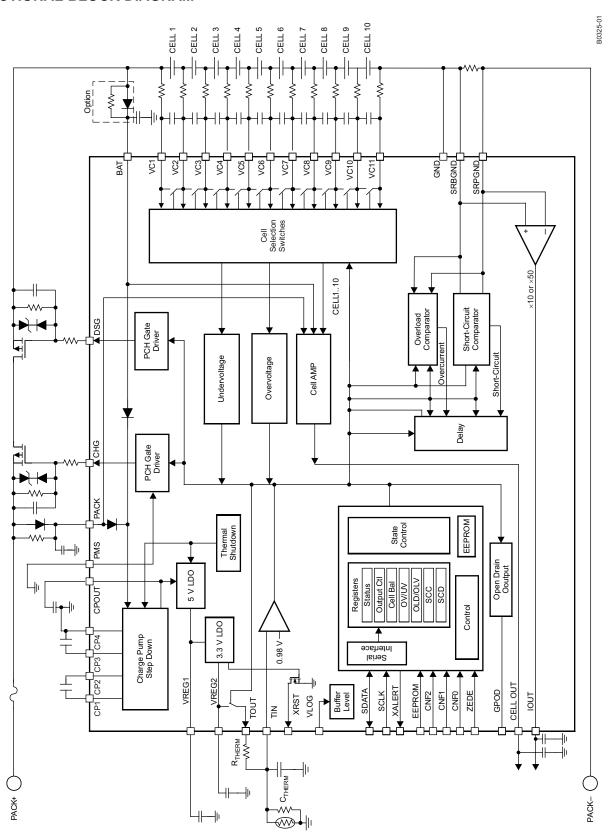

# **FUNCTIONAL BLOCK DIAGRAM**

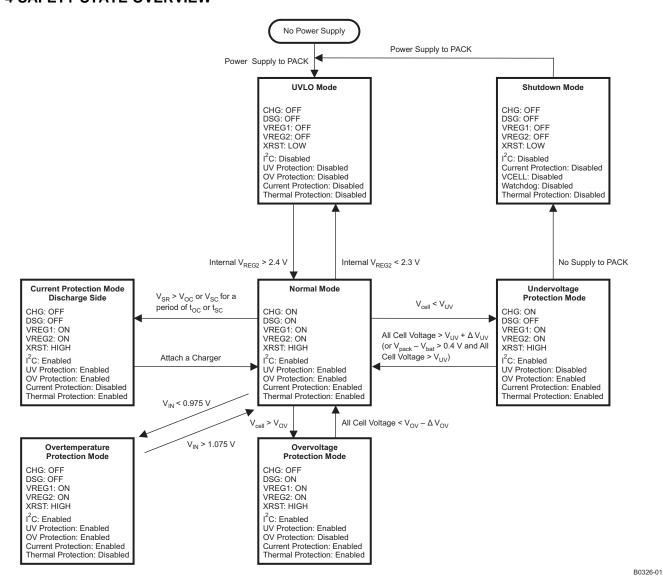

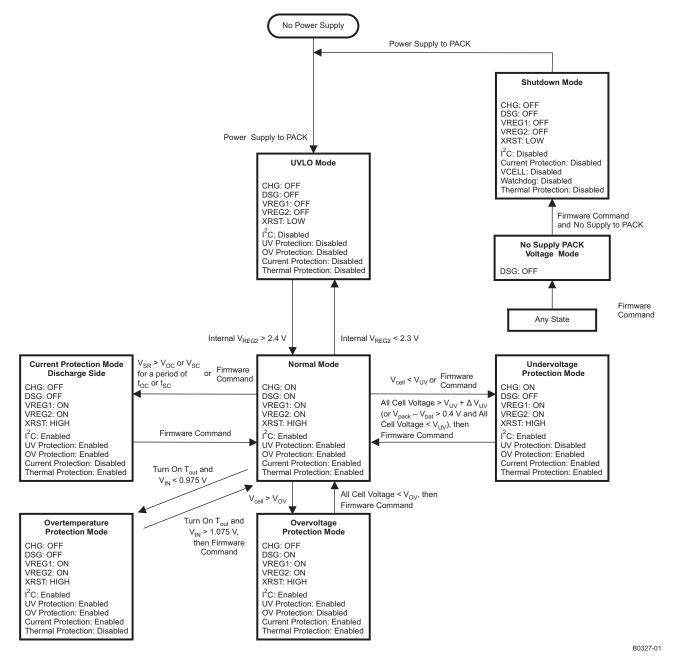

#### **4 SAFETY STATE OVERVIEW**

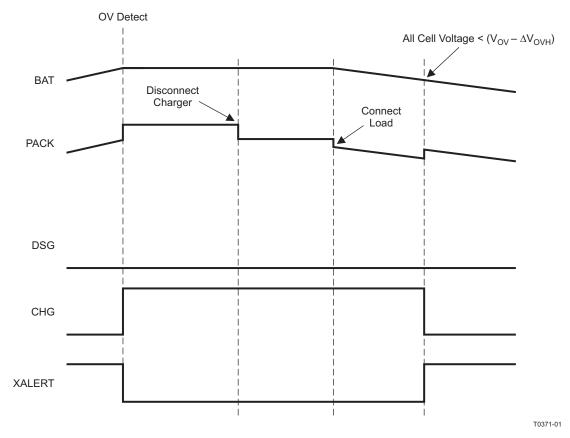

Figure 3. Stand-Alone Mode

Table 1. Stand-Alone STATUS Bit, XALERT and FET Transition Summary

| MODE TRANSITION                                                                        | STATUS BIT     | XALERT | FET ACTIVITY    |

|----------------------------------------------------------------------------------------|----------------|--------|-----------------|

| Normal to current protection                                                           | SCD or OCD = 1 | H to L | DSG and CHG off |

| Current protection to normal                                                           | SCD or OCD = 0 | L to H | DSG and CHG on  |

| Normal to overvoltage protection                                                       | OVP = 1        | H to L | CHG off         |

| Overvoltage protection to normal                                                       | OVP = 0        | L to H | CHG on          |

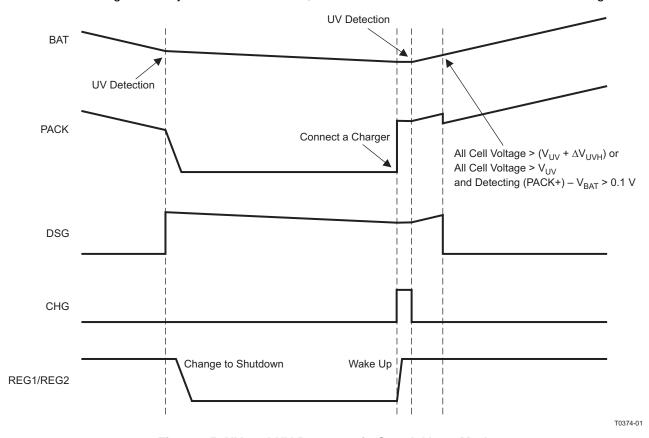

| Normal to undervoltage protection (when VPACK goes down to 0 V, move to shutdown mode) | UVP = 1        | H to L | DSG off         |

| Undervoltage protection to normal                                                      | UVP = 0        | L to H | DSG on          |

| Normal to overtemperature                                                              | OVT = 1        | H to L | DSG and CHG off |

| Overtemperature to normal                                                              | OVT = 0        | L to H | DSG and CHG on  |

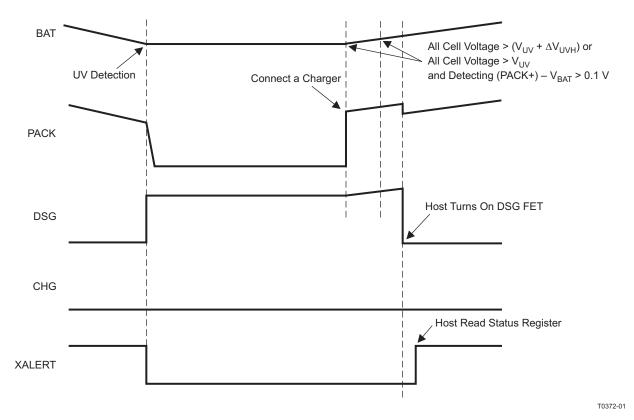

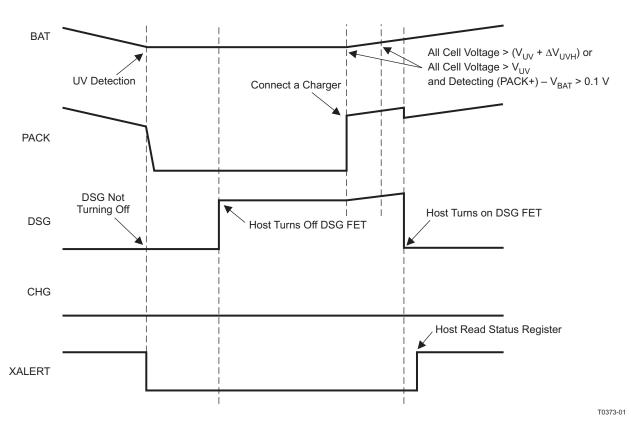

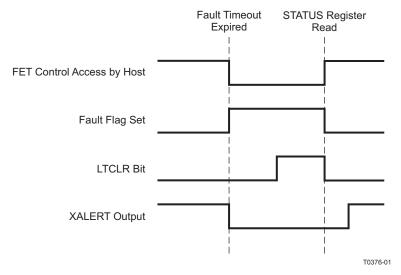

Figure 4. Host-Control Mode

# **Table 2. Host Control Summary**

| MODE TRAN                    | ISITION       | FUNCTION AND FIRMWARE PROCEDURE                                                                                               |  |  |

|------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------|--|--|

| Normal to current protection | on            | Vsr > Voc or Vsc for period of toc or tsc Automatically, DSG and CHG turn off, SCD or OCD status changes = 1, XALERT = L      |  |  |

| Current protection to norm   | nal           | 1. Send commands to transition LTCLR from 0 to 1 to 0                                                                         |  |  |

|                              |               | 2. Read status bit. XALERT would change to H.                                                                                 |  |  |

|                              |               | 3. Set CHG and DSG FET ON to enable normal operation                                                                          |  |  |

| Normal to overvoltage pro    | tection       | Vcell > Vov for period of tov<br>Automatically, CHG turns off, UV status changes = 1, XALERT = L                              |  |  |

| Overvoltage protection to    | normal        | Confirm the OVP protection status is cleared                                                                                  |  |  |

|                              |               | 2. Send command LTCLR from 1 to 0                                                                                             |  |  |

|                              |               | 3. Read status bit. XALERT changes to H.                                                                                      |  |  |

|                              |               | 4. Set CHG FET ON to enable normal operation                                                                                  |  |  |

| Normal to undervoltage       | UVFET_DIS = 0 | Vcell < Vuv for period of tuv<br>Automatically, DSG turns off, UV status changes = 1, XALERT = L                              |  |  |

| protection                   | UVFET_DIS = 1 | 1. Vcell < Vuv or for period of tuv, UV status changes = 1, XALERT = L                                                        |  |  |

|                              |               | 2. Send commands to turn off DSG.                                                                                             |  |  |

| Undervoltage protection      |               | Confirm the OVP protection status is cleared                                                                                  |  |  |

| to normal                    | UVFET DIS = X | 2. Send command LTCLR from 1 to 0                                                                                             |  |  |

|                              | UVFEI_DIS = X | 3. Set DSG FET ON to enable normal operation                                                                                  |  |  |

|                              |               | 4. Read status bit. XALERT changes to H.                                                                                      |  |  |

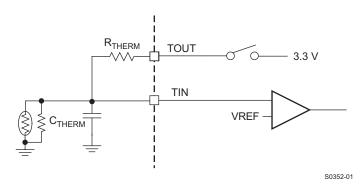

| Normal to overtemperatur     | е             | Send commands to turn on TOUT                                                                                                 |  |  |

|                              |               | 2. If TIN voltage < 0.975 V, DSG and CHG turn off, OVTEMP status changes = 1, XALERT = L                                      |  |  |

| Overtemperature to norma     | al            | <ol> <li>Send commands to turn on TOUT (To return to normal mode, bq77PL900 must<br/>acknowledge Vth &gt; 1.075 V)</li> </ol> |  |  |

|                              |               | 2. Send commands to transition LTCLR from 1 to 0                                                                              |  |  |

|                              |               | 3. Set CHG and DSG FET ON                                                                                                     |  |  |

|                              |               | 4. Read status bit. XALERT changes to H.                                                                                      |  |  |

| Any mode to shutdown         |               | 1. Set DSG FET OFF                                                                                                            |  |  |

|                              |               | 2. Wait until PACK voltage decreases to 0 V                                                                                   |  |  |

|                              |               | 3. SET shutdown bit to 1                                                                                                      |  |  |

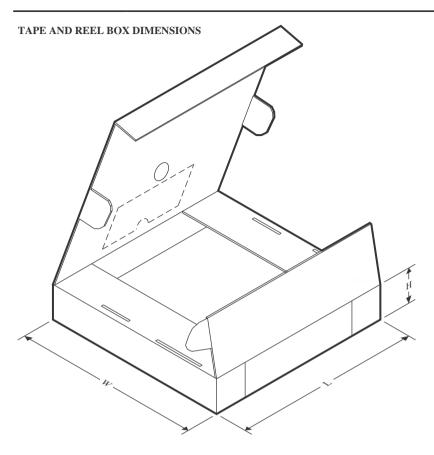

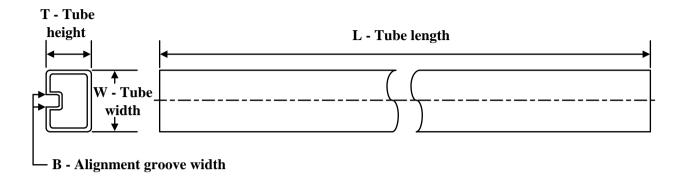

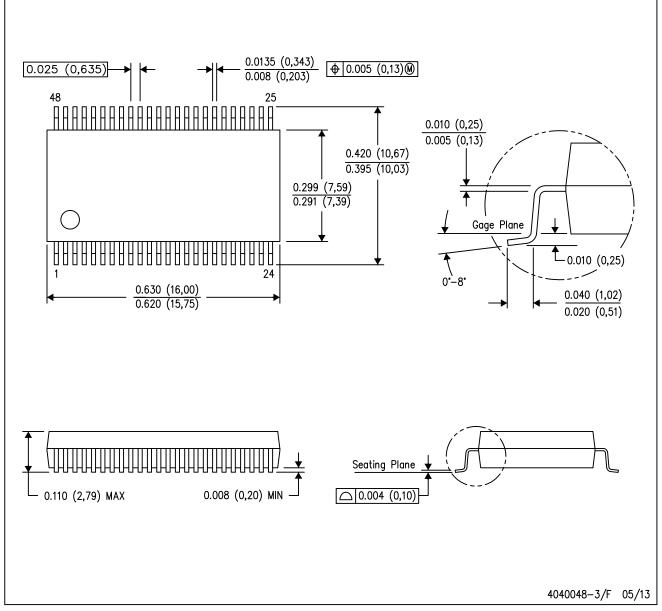

# **ORDERING INFORMATION**

| T <sub>A</sub> | PACKAGED<br>SSOP48         |

|----------------|----------------------------|

| -40°C to 100°C | bq77PL900DL <sup>(1)</sup> |

(1) The bq77PL900 can be ordered in tape and reel by adding the suffix R to the orderable part number, I.e., bq77PL900DLR.

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted) (1) (2)

|                     |                           |                                                        | VALUE           | UNIT |  |

|---------------------|---------------------------|--------------------------------------------------------|-----------------|------|--|

| V <sub>MAX</sub>    | Supply voltage range      | BAT, PACK                                              | -0.3 to 60      | V    |  |

|                     |                           | VC1-VC10                                               | -0.3 to 60      |      |  |

|                     |                           | VC11                                                   | -0.3 to 0.3     |      |  |

| V                   | Input voltage renge       | VCn to VCn + 1, n = 1 to 10                            | -0.3 to 8       | V    |  |

| V <sub>IN</sub>     | Input voltage range       | PMS                                                    | -0.3 to 60      | V    |  |

|                     |                           | SRP, SRN                                               | -0.5 to 1       |      |  |

|                     |                           | SDATA, SCLK, EEPROM, VLOG, ZEDE, CNF0, CNF1, CNF2, TIN | -0.3 to 7       |      |  |

|                     |                           | CHG                                                    | PACK – 20 to 60 |      |  |

|                     |                           | DSG                                                    | BAT – 20 to 60  |      |  |

| V                   | Output valtage renge      | TOUT, VOUT, IOUT, XRST, XALERT, SDATA, SCLK            | -0.3 to 7       | V    |  |

| Vo                  | Output voltage range      | CP1, CP2, CP3, CP4, CPOUT, GPOD                        | -0.3 to 60      | V    |  |

|                     |                           | VREG1                                                  | -0.3 to 8       |      |  |

|                     |                           | VREG2                                                  | -0.3 to 3.6     |      |  |

| I <sub>CB</sub>     | Current for cell balancin | Current for cell balancing                             |                 | mA   |  |

| T <sub>STG</sub>    | Storage temperature rar   | nge                                                    | -65 to 150      | °C   |  |

| T <sub>SOLDER</sub> | Lead temperature (solde   | ering, 10 s)                                           | 300             | °C   |  |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# **DISSIPATION RATINGS**

| PACKAGE | T <sub>A</sub> ≤ 25°C | DERATING FACTOR             | T <sub>A</sub> = 85°C | T <sub>A</sub> = 100°C |

|---------|-----------------------|-----------------------------|-----------------------|------------------------|

|         | POWER RATING          | ABOVE T <sub>A</sub> ≥ 70°C | POWER RATING          | POWER RATING           |

| DL      | 1388 mW               | 11.1 mW/°C                  | 720 mW                | 555 mW                 |

<sup>(2)</sup> All voltages are with respect to ground of this device except VCn - VC(n+1), where n=1 to 10 cell voltage.

www.ti.com

# RECOMMENDED OPERATING CONDITIONS

|                                     |                                |                    |               | MIN                     | NOM MAX                 | UNIT |

|-------------------------------------|--------------------------------|--------------------|---------------|-------------------------|-------------------------|------|

| Supply Voltag                       | ge                             | PACK, BAT          |               | 7                       | 50                      | V    |

| V <sub>I(STARTUP)</sub>             |                                | Start-up voltage P | ACK           | 7.5                     |                         | V    |

| $V_{LOG}$                           | Logic supply voltage           |                    |               | 0.8 × V <sub>REG2</sub> | 1.2 × V <sub>REG1</sub> | V    |

|                                     | Input voltage range            | VC1 to VC10        |               | 0                       | BAT                     |      |

|                                     |                                | VC11               |               | 0                       | 0.5                     |      |

| $V_{I}$                             |                                | SRP, SRN           |               | -0.3                    | 0.5                     | V    |

|                                     |                                | VCn - VC(n + 1),   | (n = 1 to 10) | 0                       | 7                       |      |

|                                     |                                | PACK, BAT          |               |                         | 50                      |      |

| V <sub>IH</sub>                     | Logic level input voltage high | SCLK, SDATA, EI    | EPROM, VLOG   | 0.8 × V <sub>LOG</sub>  | $V_{LOG}$               |      |

| V <sub>IL</sub>                     | Logic level input voltage low  | (VLOG = VREG1      | or VREG2)     | 0                       | 0.2 × V <sub>LOG</sub>  |      |

|                                     |                                | XALERT, SDATA      |               |                         | $V_{LOG}$               |      |

| M                                   | Output voltage range           | VOLIT              | VGAIN = High  |                         | 1.2                     | V    |

| Vo                                  | Output voltage range           | VOUT, IOUT         | VGAIN = Low   |                         | 0.975                   |      |

|                                     |                                | GPOD               |               |                         | 45                      | V    |

| R <sub>VCX</sub>                    |                                |                    |               |                         | 400                     | Ω    |

| I <sub>REGOUT</sub>                 |                                | I(reg1 + reg2)     |               |                         | 25                      | mA   |

| C <sub>REG1</sub>                   | External 5-V REG capacitor     |                    |               | 2.2                     |                         | μF   |

| C <sub>REG2</sub>                   | External 3.3-V REG capacitor   |                    |               | 2.2                     |                         | μF   |

| C <sub>CP1</sub> , C <sub>CP2</sub> | Charge pump flying capacitor   |                    |               | 1                       |                         | μF   |

| C <sub>CPOUT</sub>                  | Charge pump output capacitor   |                    |               | 4.7                     |                         | μF   |

| C <sub>VOUT</sub>                   | Output capacitance             |                    |               | 0.1                     |                         | μF   |

| C <sub>IOUT</sub>                   | Output capacitance             |                    |               | 0.1                     |                         | μF   |

| I <sub>OL</sub>                     |                                | GPOD, XRST         |               |                         | 1                       | mA   |

| f <sub>SCLK</sub>                   | Input frequency                | SCLK               |               |                         | 100                     | kHz  |

|                                     | EEPROM number of writes        |                    |               |                         | 3                       |      |

| T <sub>OPR</sub>                    | Operating temperature          |                    |               | -25                     | 85                      | °C   |

| T <sub>FUNC</sub>                   | Functional temperature         |                    |               | -40                     | 100                     | °C   |

# **ELECTRICAL CHARACTERISTICS**

BAT = PACK = 7 V to 50 V,  $T_A = -25$ °C to 85°C, typical values stated where  $T_A = 25$ °C and BAT = PACK = 36 V (unless otherwise noted)

|                          | PARAMETER                           | TEST CONDITIONS                                                                                                                                                                  |                                          | MIN  | TYP   | MAX        | UNIT |

|--------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------|-------|------------|------|

| SUPPLY CUP               | RRENT                               |                                                                                                                                                                                  |                                          |      |       |            |      |

|                          |                                     | No load at REG1, REG2, TOUT, SCLK, SDIN,                                                                                                                                         | T <sub>A</sub> = 25°C                    |      | 450   | 550        |      |

| I <sub>CC1</sub>         | Supply current 1                    | XALERT, CELLAMP, CURRENTAMP = off<br>CHG, DSG = on, cell balance = off,<br>I <sub>REG1</sub> = I <sub>REG2</sub> = 0 mA,<br>Charge pump = off <sup>(1)</sup> , BAT = PACK = 35 V | T <sub>A</sub> = -40°C to 100°C          |      |       | 600        | μΑ   |

| I <sub>CC2</sub>         | Supply current 2                    | No load at REG1, REG2, TOUT, SCLK, SDIN, XALERT, CELLAMP, CURRENTAMP = on, CHG, DSG = on, Cell balance = off, IREG1 = IREG2 = 0 mA, Charge pump = off, BAT = PACK = 35 V         | $T_A = 25$ °C $T_A = -40$ °C to $100$ °C |      | 650   | 750<br>800 | μΑ   |

|                          |                                     | OHO DOO " VDEOL VDEOL "                                                                                                                                                          | T <sub>A</sub> = 25°C                    |      | 0.1   | 1.2        |      |

| I <sub>SHUTDOWN</sub>    | Shutdown mode                       | CHG, DSG = off, VREG1 = VREG2 = off,<br>PACK = 0 V, BAT = 35 V                                                                                                                   | $T_A = -40$ °C to 100°C                  |      |       | 2          | μΑ   |

| VREG1, INTE              | GRATED 5-V LDO                      |                                                                                                                                                                                  | ·                                        |      |       |            |      |

|                          | 0 1 1                               | 8.5 V < PACK or BAT ≤ 50 V, I <sub>OUT</sub> ≤ 25 mA                                                                                                                             | $T_A = -40$ °C to                        | 4.55 | 5     | 5.45       |      |

| $V_{(REG1)}$             | Output voltage                      | 7 V < PACK or BAT ≤ 8.5 V, I <sub>OUT</sub> ≤ 3 mA                                                                                                                               | 100°C                                    | 4.55 | 5     | 5.45       | V    |

| $\Delta V_{(REG1)}$      | Output temperature drift            | PACK or BAT = 50 V, I <sub>OUT</sub> = 2 mA                                                                                                                                      | T <sub>A</sub> = 25°C                    |      | ±0.2% |            | 1    |

| ΔV <sub>(REG1LINE)</sub> | Line regulation                     | 10 V ≤ PACK or BAT ≤ 50 V, I <sub>OUT</sub> = 2 mA                                                                                                                               | T <sub>A</sub> = 25°C                    |      | 10    | 20         | mV   |

| , - ,                    | <del>-</del>                        | PACK or BAT = 36 V, 0.2 mA ≤ I <sub>OUT</sub> ≤ 2 mA                                                                                                                             |                                          |      | 7     | 15         |      |

| $\Delta V_{(REG1LOAD)}$  | Load regulation                     | PACK or BAT = 36 V, 0.2 mA ≤ I <sub>OUT</sub> ≤ 25 mA                                                                                                                            | $T_A = 25^{\circ}C$                      |      | 40    | 100        | mV   |

|                          |                                     | PACK or BAT = 36 V, VREG1 = 4.5 V                                                                                                                                                |                                          | 35   | 75    | 125        |      |

| IREG1MAX                 | Current limit                       | PACK or BAT = 36 V, VREG1 = 0 V                                                                                                                                                  | $T_A = 25^{\circ}C$                      | 5    | 20    | 35         | mA   |

| VREG2. INTE              | GRATED 3.3-V LDO                    |                                                                                                                                                                                  |                                          |      |       |            |      |

| - ,                      |                                     | 8.5 V < PACK or BAT ≤ 50 V, I <sub>OUT</sub> ≤ 25 mA                                                                                                                             |                                          | 3.05 | 3.3   | 3.55       |      |

| $V_{(REG2)}$             | Output voltage                      | 7 V < PACK or BAT ≤ 8.5 V, I <sub>OUT</sub> ≤ 10 mA                                                                                                                              | $T_A = -40$ °C to                        | 3.05 | 3.3   | 3.55       | V    |

| (KEG2)                   |                                     | 7 V < PACK or BAT ≤ 50 V, I <sub>OUT</sub> = 0.2 mA                                                                                                                              | 100°C                                    | -2%  | 3.3   | 2%         | 1    |

|                          | Output temperature drift            | PACK or BAT = 50 V, I <sub>OUT</sub> = 2 mA                                                                                                                                      | T <sub>A</sub> = -40°C to 100°C          |      | ±0.2% |            |      |

| $\Delta V_{(REG2)}$      | Line regulation                     | 7 V ≤ PACK or BAT ≤ 50 V, I <sub>OUT</sub> = 2 mA                                                                                                                                | T <sub>A</sub> = 25°C                    |      | 10    | 20         | mV   |

| △ v (REG2)               | 0                                   | PACK or BAT = 36 V, 0.2 mA ≤ I <sub>OUT</sub> ≤ 2 mA                                                                                                                             | n n                                      |      | 7     | 15         |      |

|                          | Load regulation                     | PACK or BAT = 36 V, 0.2 mA ≤ I <sub>OUT</sub> ≤ 25 mA                                                                                                                            | T <sub>A</sub> = 25°C                    |      | 40    | 100        | mV   |

|                          |                                     | PACK or BAT = 36 V, VREG2 = 3 V                                                                                                                                                  |                                          | 25   | 50    | 100        |      |

| I <sub>REG2MAX</sub>     | Current limit                       | PACK or BAT = 36 V, VREG2 = 0 V                                                                                                                                                  | T <sub>A</sub> = 25°C                    | 10   | 20    | 30         | mA   |

| TOUT, THER               | MISTOR POWER SUPPLY                 |                                                                                                                                                                                  |                                          |      |       |            |      |

| V <sub>TOUT</sub>        |                                     | I <sub>OUT</sub> = 0 mA                                                                                                                                                          | $T_A = -40$ °C to 100°C                  | 3.05 |       | 3.55       | V    |

| RDS <sub>(ON)</sub>      | Pass-element series resistance      | $I_{OUT} = -1$ mA at TOUT pin, $I_{reg2} = -0.2$ mA<br>RDS <sub>(ON)</sub> = $(V_{REG2} - V_{TOUT})/1$ mA                                                                        | $T_A = -40$ °C to 100°C                  |      | 50    | 100        | Ω    |

| V <sub>TINS</sub>        | Thermistor sense voltage            | $T_A = -40$ °C to 100°C                                                                                                                                                          |                                          | -5%  | 0.975 | 5%         | >    |

| V <sub>TINSHYS</sub>     | Thermistor sense hysteresis voltage | $T_A = -40^{\circ}\text{C to } 100^{\circ}\text{C}$                                                                                                                              |                                          | 50   | 100   | 150        | mV   |

| THERMAL SH               | IUTDOWN                             |                                                                                                                                                                                  |                                          |      |       |            |      |

| T <sub>therm</sub>       | Shutdown threshold                  | PACK or BAT = 36 V <sup>(2)</sup>                                                                                                                                                |                                          |      | 150   |            | °C   |

| PMS, PRECH               | ARGE MODE SELECT DISA               | BLE                                                                                                                                                                              |                                          |      |       |            |      |

| V <sub>PMSDISABLE</sub>  | PMS disable threshold of BAT        | PACK = PMS = 20 V, VREG2 = 0 V, CHG = ON -                                                                                                                                       | → OFF                                    | 8    | 13    | 16         | V    |

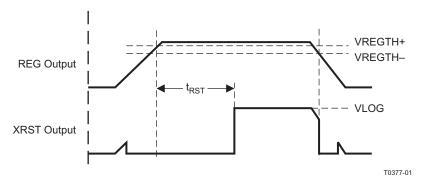

| POR, POWER               | R-ON RESET                          |                                                                                                                                                                                  |                                          |      |       |            |      |

| V                        | Negative-going voltage              | VLOG = VREG1(5 V) V                                                                                                                                                              |                                          | 3.85 | 4.05  | 4.25       | V    |

| $V_{POR-}$               | input                               | VLOG = VREG2(3.3 V) V                                                                                                                                                            |                                          | 2.45 | 2.65  | 2.8        | v    |

Charge pump starts working when ( $I_{REG33} + I_{REG5}$ ) > 3 mA. Not 100% tested, assured by design up to 125°C

<sup>(2)</sup>

# **ELECTRICAL CHARACTERISTICS (continued)**

BAT = PACK = 7 V to 50 V,  $T_A = -25$ °C to 85°C, typical values stated where  $T_A = 25$ °C and BAT = PACK = 36 V (unless otherwise noted)

| PARAMETER             |                                  | TEST CONDITIONS                                                                                                                |       | TYP     | MAX   | UNIT |

|-----------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------|---------|-------|------|

| M                     | Desition asian boots as          | VLOG = 3.3 V                                                                                                                   | 50    | 150     | 250   | \/   |

| $V_{POR\_HYS}$        | Positive-going hysteresis        | VLOG = 5 V                                                                                                                     | 100   | 250     | 400   | mV   |

| t <sub>RST</sub>      | Reset delay time                 |                                                                                                                                | 1     |         | 5     | ms   |

| CELL VOLTA            | AGE MONITOR                      |                                                                                                                                |       |         |       |      |

|                       |                                  | VCn − VCn + 1 = 0 V , 20 V ≤ BAT ≤ 50 V, VGAIN = Low                                                                           | 0.925 | 0.975   | 1.025 |      |

| V <sub>CELL OUT</sub> | CELL output                      | VCn − VCn + 1 = 0 V , 20 V ≤ BAT ≤ 50 V, VGAIN = High                                                                          | 1.12  | 1.2     | 1.28  | V    |

|                       |                                  | VCn − VCn + 1 = 4.5 V , 20 V ≤ BAT ≤ 50 V                                                                                      |       | 0.3     |       |      |

| REF 1                 | CELL output                      | $Mode^{(3)}$ , 20 V $\leq$ BAT or PACK $\leq$ 50 V, VGAIN = Low                                                                | -2%   | 0.975   | 2%    | V    |

| REF 2                 | CELL output                      | Mode <sup>(4)</sup> , 20 V ≤ BAT or PACK ≤ 50 V, VGAIN = High                                                                  | -2%   | 1.2     | 2%    | V    |

| PACK                  | CELL output                      | Mode <sup>(5)</sup>                                                                                                            | -5%   | PACK/50 | 5%    | V    |

| BAT                   | CELL output                      | Mode <sup>(6)</sup>                                                                                                            | -5%   | BAT/50  | 5%    | V    |

| CMRR                  | Common-mode rejection            | CELL max to CELL min, 20 V ≤ BAT ≤ 50 V                                                                                        | 40    |         |       | dB   |

|                       | CELL scale factor 1              | K = {CELL output (VC11 = 0 V, VC10 = 4.5 V) - CELL output (VC11 = VC10 = 0 V)} / 4.5 <sup>(7)</sup>                            | 0.147 | 0.15    | 0.153 |      |

| K1                    |                                  | K = {CELL output (VC2 = $40.5 \text{ V}$ , VC1 = $45 \text{ V}$ ) – CELL output (VC2 = VC1 = $40.5 \text{ V}$ )} / $4.5^{(7)}$ | 0.147 | 0.15    | 0.153 |      |

| 140                   |                                  | K = {CELL output (VC11 = 0 V, VC10 = $4.5 \text{ V}$ ) – CELL output (VC11 = VC10 = 0 V)} / $4.5^{(8)}$                        | 0.197 | 0.201   | 0.205 |      |

| K2                    | CELL scale factor 2              | K = {CELL output (VC2 = $40.5$ V, VC1 = $45$ V) – CELL output (VC2 = VC1 = $40.5$ V)} / $4.5$ <sup>(8)</sup>                   | 0.197 | 0.201   | 0.205 |      |

| I <sub>VCELLOUT</sub> | Drive current                    | VCn - VCn + 1= 0 V, Vcell = 0 V, T <sub>A</sub> = -40 to 100°C                                                                 | 12    | 18      |       | μΑ   |

| V <sub>ICR</sub>      | CELL output offset error         | CELL output (VC2 = 45 V, VC1 = 45 V) – CELL output (VC2 = VC1 = 0 V)                                                           |       | -1      |       | mV   |

| R <sub>BAL</sub>      | Cell balance internal resistance | RDS <sub>(ON)</sub> for internal FET switch at V <sub>DS</sub> = 2 V, BAT = PACK = 35 V                                        | -50%  | 400     | 50%   | Ω    |

| CURRENT M             | IONITOR                          |                                                                                                                                |       |         |       |      |

| V <sub>IOUT</sub>     | Output voltage                   | VSRP = VSRN = 0 V (9)                                                                                                          |       | 1.2     |       | V    |

| W                     | lanut offeet voltes a-           | VSRP = VSRN = 0 V <sup>(9)</sup> , T <sub>A</sub> = 25°C                                                                       | -3    |         | 3     | m) / |

| V <sub>OFFSET</sub>   | Input offset voltage             | VSRP = VSRN = 0 V <sup>(9)</sup> , T <sub>A</sub> = -40°C to 100°C                                                             | -4    |         | 4     | mV   |

|                       | DC gain, low                     | -100 mV < SRP < 100 mV (10)                                                                                                    | -2%   | 10      | 2%    |      |

|                       | DC gain, high                    | -20 mV < SRP < 20 mV <sup>(11)</sup>                                                                                           | -2%   | 50      | 2%    |      |

| I <sub>IOUT</sub>     | Drive current                    | $V_{IOUT} = 0 \text{ V}, T_A = -40^{\circ}\text{C} \text{ to } 100^{\circ}\text{C}$                                            | 12    | 18      |       | μΑ   |

- (3) STATE\_CONTROL [VGAIN] = 0, FUNCTION\_CONTROL [VAEN] = 1, CELL\_SEL[CAL2] = 0, [CAL0] = 1, [CAL0] = 1

(4) STATE\_CONTROL [VGAIN] = 1, FUNCTION\_CONTROL [VAEN] = 1, CELL\_SEL[CAL2] = 0, [CAL0] = 1, [CAL0] = 1

(5) STATE\_CONTROL [VGAIN] = X, FUNCTION\_CONTROL [PACK] = 1, [VAEN] = 1

(6) STATE\_CONTROL [VGAIN] = X, FUNCTION\_CONTROL [BAT] = 1, [VAEN] = 1

(7) STATE\_CONTROL [VGAIN] = 0, FUNCTION\_CONTROL [VAEN] = 1, CELL\_SEL[CAL2] = 0, [CAL0] = 0, [CAL0]

(8) STATE\_CONTROL [VGAIN] = 1, FUNCTION\_CONTROL [VAEN] = 1, CELL\_SEL[CAL2] = 0, [CAL0] = 0

(9) STATE\_CONTROL [IGAIN] = X, FUNCTION\_CONTROL [IAEN] = 1, [IACAL] = 1

(10) STATE\_CONTROL [IGAIN] = 0, FUNCTION\_CONTROL [IAEN] = 1, [IACAL] = 0

(11) STATE\_CONTROL [IGAIN] = 1, FUNCTION\_CONTROL [IAEN] = 1, [IACAL] = 0

# **ELECTRICAL CHARACTERISTICS (continued)**

BAT = PACK = 7 V to 50 V,  $T_A = -25$ °C to 85°C, typical values stated where  $T_A = 25$ °C and BAT = PACK = 36 V (unless otherwise noted)

|                         | PARAMETER                              | TEST CONDITIONS                        | MIN  | TYP | MAX  | UNIT |

|-------------------------|----------------------------------------|----------------------------------------|------|-----|------|------|

| BATTERY P               | PROTECTION THRESHOLDS                  |                                        | Ī    |     |      |      |

| V <sub>OV</sub>         | OV detection threshold range           | Default                                | 4.15 |     | 4.5  | V    |

| $\Delta V_{OV}$         | OV detection threshold<br>program step |                                        |      | 50  |      | mV   |

| $V_{\text{OVH}}$        | OV detection hysteresis voltage range  | Default                                | 0    |     | 0.3  | ٧    |

| $\Delta V_{OVH}$        | OV detection hysteresis program step   |                                        |      | 0.1 |      | ٧    |

| V <sub>UV</sub>         | UV detection threshold range           | Default                                | 1.4  |     | 2.9  | V    |

| $\Delta V_{UV}$         | UV detection threshold program step    |                                        |      | 100 |      | mV   |

| $V_{\text{UVH}}$        | UV detection hysteresis voltage        | Default                                | 0.2  |     | 1.2  | V    |

| $\Delta V_{\text{UVH}}$ | UV detection threshold program step    |                                        |      | 200 |      | mV   |

| V <sub>OCDT</sub>       | OCD detection threshold range          | Default                                | 10   |     | 85   | mV   |

| $\Delta V_{OCDT}$       | OCD detection threshold program step   |                                        |      | 5   |      | mV   |

| V <sub>SCDT</sub>       | SCD detection threshold range          | Default                                | 60   |     | 135  | mV   |

| ΔV <sub>SCDT</sub>      | SCD detection threshold program step   |                                        |      | 5   |      | mV   |

| V <sub>OV_acr</sub>     | OV detection threshold accuracy        | Default (T <sub>A</sub> = 0°C to 85°C) | -50  | 0   | 50   | mV   |

| V <sub>UV_acr</sub>     | UV detection threshold accuracy        | Default                                | -100 | 0   | 100  | mV   |

| V <sub>OCD_acr</sub>    | OCD detection threshold                | V <sub>OCD</sub> = 10 mV or 15 mV      | -4   | 0   | 4    | mV   |

| - OCD_acr               | accuracy                               | V <sub>OCD</sub> > 20 mV               | -20% | 0   | 20%  |      |

| V <sub>SCD_acr</sub>    | SCD detection threshold accuracy       | Default                                | -20% | 0   | 20%  |      |

| BATTERY P               | PROTECTION DELAY TIMES                 |                                        | Т    |     |      |      |

| t <sub>OV</sub>         | OV detection delay time range          | Default                                | 500  |     | 2250 | ms   |

| $\Delta t_{\text{OV}}$  | OV detection delay time step           |                                        |      | 250 |      | ms   |

| t <sub>UV</sub>         | UV detection delay time range          | Default                                | 0    |     | 8000 | ms   |

| $\Delta t_{\text{UV}}$  | UV detection delay time<br>step        |                                        | 1.25 |     | 1000 | ms   |

| t <sub>OCD</sub>        | OCD detection delay time range         | Default                                | 20   |     | 1600 | ms   |

| $\Delta t_{OCD}$        | OCD detection delay time step          |                                        | 20   |     | 100  | ms   |

| t <sub>SCD</sub>        | SCD detection delay time range         | Default                                | 0    |     | 900  | μs   |

| $\Delta t_{SCD}$        | SCD detection threshold program step   |                                        |      | 60  |      | μs   |

| t <sub>OV_acr</sub>     | OV detection delay time accuracy       | Default                                | -15% | 0%  | 15%  |      |

| t <sub>UV_acr</sub>     | UV detection delay time accuracy       | Default                                | -15% | 0%  | 15%  |      |

| t <sub>OC_acr</sub>     | OC detection delay time accuracy       | Default                                | -15% | 0%  | 15%  |      |

| V <sub>SCD_acr</sub>    | SC detection delay time accuracy       | t <sub>SCD</sub> Max                   | -15% | 0%  | 15%  |      |

|                         |                                        |                                        |      |     |      |      |

# **ELECTRICAL CHARACTERISTICS (continued)**

BAT = PACK = 7 V to 50 V,  $T_A = -25$ °C to 85°C, typical values stated where  $T_A = 25$ °C and BAT = PACK = 36 V (unless otherwise noted)

| PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                           | TEST CONDITIONS                                                                             |                               | MIN  | TYP    | MAX | UNIT  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------|------|--------|-----|-------|--|

| t <sub>SRC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | OC/SC recovery timing in stand-alone mode |                                                                                             |                               | -15% | 12.8 s | 15% |       |  |

| BATTERY P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ROTECTION RECOVERY                        |                                                                                             |                               |      |        |     |       |  |

| V <sub>RECSC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SC, OC recovery voltage                   |                                                                                             |                               | 1    | 1.4    | 2   | V     |  |

| V <sub>RECUV</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Undervoltage recover voltage              | $V_{RECUV} = V_{PACK-} V_{BAT},$<br>$V_{UV} + V_{UVH} > V_{CELL} > V_{UV}$                  |                               | 0.05 | 0.1    | 0.3 | ٧     |  |

| FET DRIVE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                           |                                                                                             |                               |      |        |     |       |  |

| Output voltage, charge $V_{(FETON)}$ Output voltage, charge and discharge FETs on an experiment of the properties of |                                           |                                                                                             |                               | 8    | 12     | 16  | V     |  |

| V(FETON)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | and discharge FETs on                     | $V_{O(FETONCHG)} = V_{(PACK)} - V_{(CHG)},$<br>VGS connect 1 M $\Omega$ , BAT = PACK = 35 V |                               | 8    | 12     | 16  | v<br> |  |

| V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Output voltage, charge                    | $V_{O(FETOFFDSG)} = V_{(PACK)} - V_{(DSG)}$ , BAT = PAC                                     | K = 35 V                      |      |        | 0.2 | V     |  |

| $V_{(FETOFF)}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | and discharge FETs off                    | $V_{O(FETOFFCHG)} = V_{(BAT)} - V_{(CHG)}$ , BAT = PACK = 35 V                              |                               |      |        | 0.2 | V<br> |  |

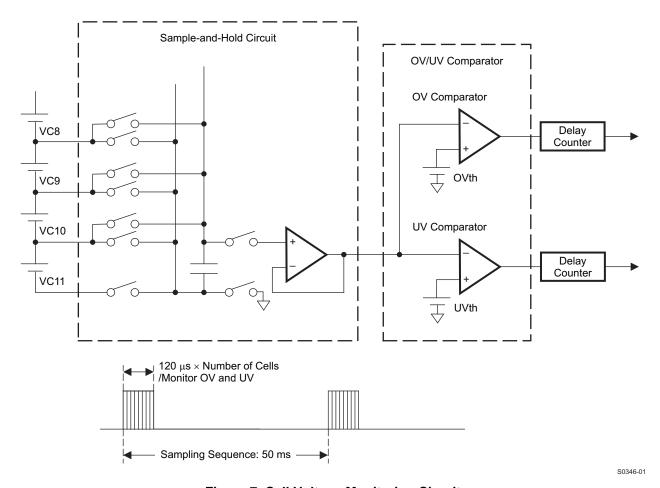

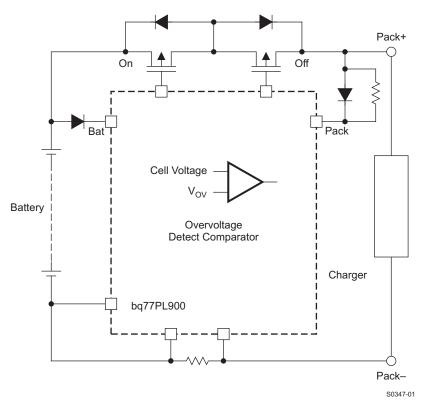

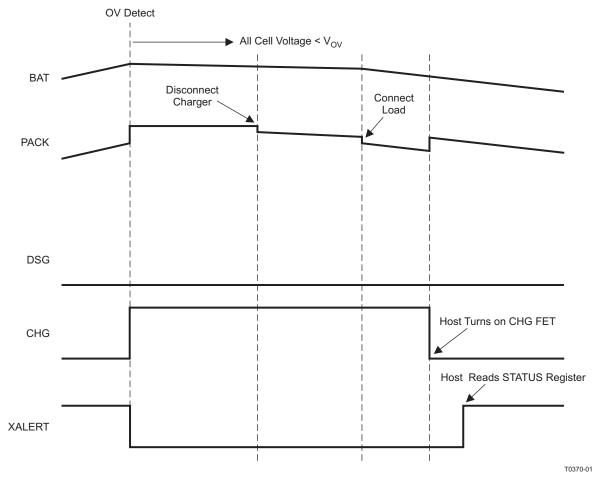

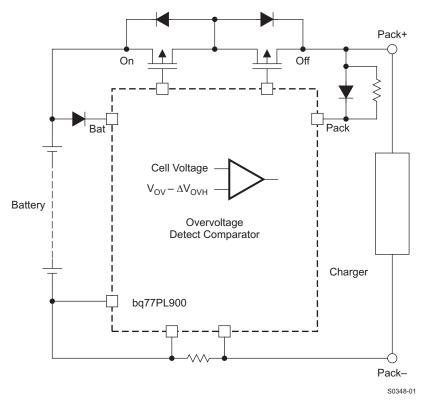

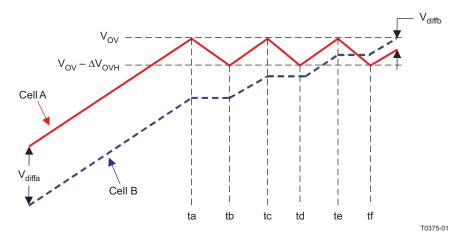

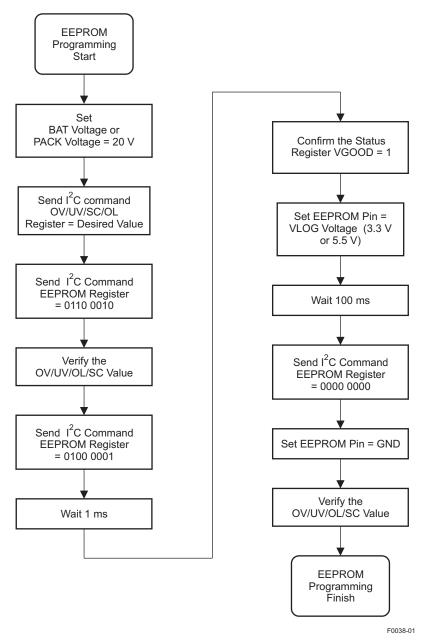

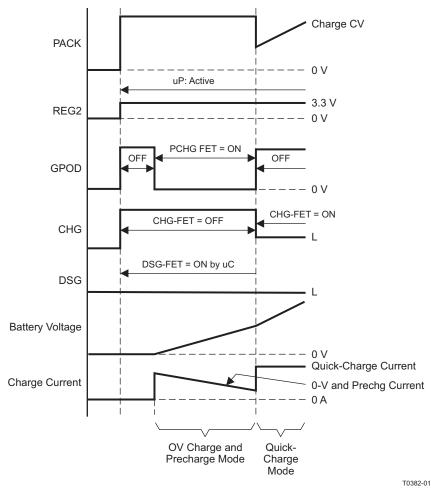

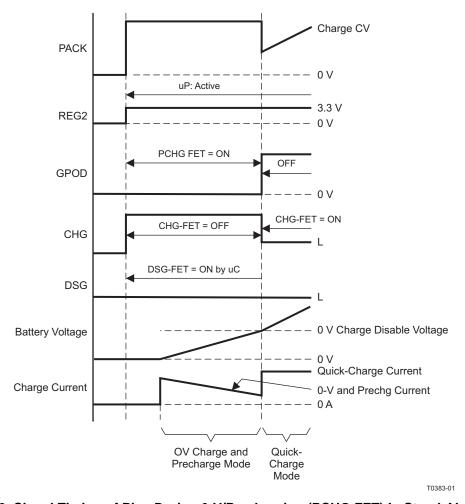

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Rise time                                 | C <sub>1</sub> = 20 nF. BAT = PACK = 35 V                                                   | V <sub>DSG</sub> : 10% to 90% |      | 5      | 15  |       |  |