SLVS550B-DECEMBER 2004-REVISED JANUARY 2013

# **16-CHANNEL LED DRIVER WITH DOT CORRECTION**

Check for Samples: TLC5923

## FEATURES

- 16 Channels

- Drive Capability

- 0 to 80 mA (Constant-Current Sink)

- Constant Current Accuracy: ±1% (typical)

- Serial Data Interface

- Fast Switching Output: T<sub>r</sub> / T<sub>f</sub> = 10ns (typical)

- CMOS Level Input/Output

- 30 MHz Data Transfer Rate

- V<sub>CC</sub> = 3.0 V to 5.5 V

- Operating Temperature = -40°C to 85°C

- LED Supply Voltage up to 17 V

- 32-pin HTSSOP( PowerPAD<sup>™</sup>) and QFN Packages

- Dot Correction

- 7 bit (128 Steps)

- individual adjustable for each channel

- Controlled In-Rush Current

- Error Information

- LOD: LED Open Detection

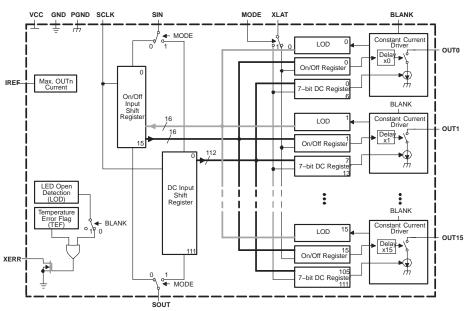

## FUNCTIONAL BLOCK DIAGRAM

- TEF: Thermal Error Flag

## **APPLICATIONS**

- Monocolor, Multicolor, Fullcolor LED Display

- Monocolor, Multicolor LED Signboard

- Display Backlighting

- Multicolor LED lighting applications

## DESCRIPTION

The TLC5923 is a 16 channel constant-current sink driver. Each channel has a On/Off state and a 128step adjustable constant current sink (dot correction). The dot correction adjusts the brightness variations between LED, LED channels and other LED drivers. Both dot correction and On/Off state are accessible via a serial data interface. A single external resistor sets the maximum current of all 16 channels.

The TLC5923 features two error information circuits. The LED open detection (LOD) indicates a broken or disconnected LED at an output terminal. The thermal error flag (TEF) indicates an overtemperature condition.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. PowerPAD is a trademark of Texas Instruments.

TEXAS INSTRUMENTS

#### SLVS550B-DECEMBER 2004-REVISED JANUARY 2013

www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

| ORDERING INFORMATION <sup>(1)</sup>               |                           |            |  |  |  |  |

|---------------------------------------------------|---------------------------|------------|--|--|--|--|

| T <sub>A</sub> Package Part Number <sup>(1)</sup> |                           |            |  |  |  |  |

| 10°C to 95°C                                      | 32-pin, HTSSOP, PowerPAD™ | TLC5923DAP |  |  |  |  |

| –40°C to 85°C                                     | 32-pin, 5 mm x 5 mm QFN   | TLC5923RHB |  |  |  |  |

For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

#### ABSOLUTE MAXIMUM RATINGS (1) (2)

|                  |                                                                  |                                                                                                                                   | TLC5923                       | UNIT  |

|------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------|

| $V_{CC}$         | Supply voltage <sup>(2)</sup>                                    |                                                                                                                                   | -0.3 to 6                     | V     |

| I <sub>O</sub>   | Output current (dc)                                              | I <sub>(OUT0)</sub> to I <sub>(OUT15)</sub>                                                                                       | 90                            | mA    |

| VI               | Input voltage range <sup>(2)</sup>                               | V <sub>(BLANK)</sub> , V <sub>(XLAT)</sub> , V <sub>(SCLK)</sub> , V <sub>(SIN)</sub> , V <sub>(MODE)</sub> , V <sub>(IREF)</sub> | -0.3 to V <sub>CC</sub> + 0.3 | V     |

| $\gamma$         | Output voltage range $\binom{2}{2}$                              | V <sub>(SOUT)</sub> , V <sub>(XERR)</sub>                                                                                         | -0.3 to V <sub>CC</sub> + 0.3 | V     |

| Vo               | Output voltage range <sup>(2)</sup>                              | V <sub>(OUT0)</sub> to V <sub>(OUT15)</sub>                                                                                       | -0.3 to 18                    | V     |

|                  |                                                                  | HBM (JEDEC JESD22-A114, Human Body Model)                                                                                         | 2                             | kV    |

|                  | ESD rating                                                       | CDM (JEDEC JESD22-C101, Charged Device Model)                                                                                     | 500                           | V     |

| T <sub>stg</sub> | Storage temperature range                                        |                                                                                                                                   | -40 to 150                    | °C    |

|                  | Power dissipation rating at (or                                  | HTSSOP (DAP)                                                                                                                      | 42.54                         | mW/°C |

|                  | Power dissipation rating at (or above) $T_A = 25^{\circ}C^{(3)}$ | QFN (RHB)                                                                                                                         | 27.86                         | mW/°C |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to network ground terminal.

(3) See SLMA002 for more information about PowerPAD<sup>™</sup>

#### **RECOMMENDED OPERATING CONDITIONS—DC Characteristics**

|                  |                                           |                                     | N      | IIN | NOM MAX | UNIT |

|------------------|-------------------------------------------|-------------------------------------|--------|-----|---------|------|

| $V_{CC}$         | Supply voltage                            |                                     |        | 3   | 5.5     | V    |

| Vo               | Voltage applied to output, (Out0 - Out15) |                                     |        |     | 17      | V    |

| $V_{\text{IH}}$  | High-level input voltage                  |                                     | 0.8 V0 | CC  | VCC     | V    |

| VIL              | Low-level input voltage                   |                                     | GI     | ١D  | 0.2 VCC | V    |

| I <sub>OH</sub>  | High-level output current                 | $V_{CC} = 5 V at SOUT$              |        |     | -1      | mA   |

| I <sub>OL</sub>  | Low-level output current                  | V <sub>CC</sub> = 5 V at SOUT, XERR |        |     | 1       | mA   |

| I <sub>OLC</sub> | Constant output current                   | OUT0 to OUT15                       |        |     | 80      | mA   |

| T <sub>A</sub>   | Operating free-air temperat               | ure range                           | -      | 40  | 85      | °C   |

#### SLVS550B – DECEMBER 2004 – REVISED JANUARY 2013

## **RECOMMENDED OPERATING CONDITIONS—AC Characteristics**

$V_{CC} = 3 \text{ V}$  to 5.5 V,  $T_A = -40^{\circ}\text{C}$  to 85°C (unless otherwise noted)

|                                    |                     |                                       | MIN | TYP | MAX | UNIT |

|------------------------------------|---------------------|---------------------------------------|-----|-----|-----|------|

| f <sub>SCLK</sub>                  | Clock frequency     | SCLK                                  |     |     | 30  | MHz  |

| t <sub>wh0,</sub> t <sub>wl0</sub> | CLK pulse duration  | SCLK=H/L                              | 16  |     |     | ns   |

| t <sub>wh1</sub>                   | XLAT pulse duration | XLAT=H                                | 20  |     |     | ns   |

| t <sub>su0</sub>                   |                     | SIN to SCLK↑ <sup>(1)</sup>           | 10  |     |     |      |

| t <sub>su1</sub>                   |                     | SLCK↑ to XLAT↓(dot correction data)   | 10  |     |     |      |

| t <sub>su1a</sub>                  | Setup time          | SCLK↑to XLAT↑ (ON/OFF data)           | 10  |     |     | ns   |

| t <sub>su2</sub>                   |                     | MODE↑↓ to SCLK↑                       | 10  |     |     |      |

| t <sub>su3</sub>                   |                     | MODE↑↓ to XLAT↑                       | 10  |     |     |      |

| t <sub>h0</sub>                    |                     | SCLK↑ to SIN                          | 10  |     |     |      |

| t <sub>h1</sub>                    |                     | XLAT ↓ to SCLK↑ (dot correction data) | 10  |     |     |      |

| t <sub>h1a</sub>                   | Hold time           | XLAT↑ to SCLK↑ (ON/OFF data)          | 10  |     |     | ns   |

| t <sub>h2</sub>                    |                     | SCLK↑to MODE↑↓                        | 10  |     |     |      |

| t <sub>h3</sub>                    | 1                   | XLAT↓ to MODE↑↓                       | 10  |     |     |      |

(1) " $\uparrow$ " and " $\downarrow$ " indicates a rising edge, and a falling edge respectively.

## **ELECTRICAL CHARACTERISTICS**

$V_{CC} = 3 V$  to 5.5 V,  $T_A = -40^{\circ}$ C to 85°C (unless otherwise noted)

|                                | PARAMETER                                                                                | TEST CONDITIONS                                                                                                         | MIN                  | TYP               | MAX   | UNIT |

|--------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------|-------|------|

| V <sub>OH</sub>                | High-level output voltage                                                                | I <sub>OH</sub> = -1 mA, SOUT                                                                                           | V <sub>CC</sub> –0.5 |                   |       | V    |

| V <sub>OL</sub>                | Low-level output voltage                                                                 | I <sub>OL</sub> = 1 mA, SOUT                                                                                            |                      |                   | 0.5   | V    |

| l <sub>l</sub>                 | Input current                                                                            | $V_I = V_{CC}$ or GND, BLANK, XLAT, SCLK, SIN, MODE                                                                     | -1                   |                   | 1     | μA   |

|                                |                                                                                          | No data transfer, All output OFF, $V_O = 1 V$ , $R_{(IREF)} = 10 k\Omega$                                               |                      |                   | 6     |      |

| I <sub>CC</sub> Supply current | No data transfer, All output OFF, $V_O$ = 1 V, $R_{(IREF)}$ = 1.3 $k\Omega$              |                                                                                                                         |                      | 15                |       |      |

|                                | Data transfer 30 MHz, All output ON, V <sub>O</sub> = 1 V, $R_{(IREF)}$ = 1.3 k $\Omega$ |                                                                                                                         |                      | 32                | mA    |      |

|                                | Data transfer 30 MHz, All output ON, V_O = 1 V, $R_{(IREF)}$ = 600 $\Omega$              |                                                                                                                         | 36                   | 65 <sup>(1)</sup> |       |      |

| I <sub>OLC</sub>               | Constant sink current                                                                    | All output ON, $V_O = 1 V$ , $R_{(IREF)} = 600 \Omega$                                                                  | 70                   | 80                | 90    | mA   |

| I <sub>LO0</sub>               | Leakage output current                                                                   | All output OFF, V <sub>O</sub> = 15 V, R <sub>(IREF)</sub> = 600 $\Omega$ , OUT0 to OUT15                               |                      |                   | 0.1   | μA   |

| I <sub>LO1</sub>               |                                                                                          | V <sub>XERR</sub> = 5.5 V, No TEF and LOD                                                                               |                      |                   | 10    | μA   |

| ∆I <sub>OLC0</sub>             | Constant sink current error                                                              | All output ON, $V_O = 1 V$ , $R_{(IREF)} = 600 \Omega$ , OUT0 to OUT15                                                  |                      | ±1%               | ±4%   |      |

| ∆l <sub>OLC1</sub>             | Constant sink current error                                                              | device to device, averaged current from OUT0 to OUT15, $R_{(IREF)}$ = 600 $\Omega$                                      |                      | ±4%               | ±8.5% |      |

| ∆l <sub>OLC2</sub>             | Line regulation                                                                          | All output ON, V <sub>O</sub> = 1 V, R <sub>(IREF)</sub> = 600 $\Omega$ , OUT0 to OUT15, V <sub>CC</sub> = 3 V to 5.5 V |                      | ±1                | ±4    | %/V  |

| ∆l <sub>OLC3</sub>             | Load regulation                                                                          | All output ON, V <sub>O</sub> = 1 V to 3 V, $R_{(IREF)}$ = 600 $\Omega$ , OUT0 to OUT15                                 |                      | ±2                | ±6    | %/V  |

| T <sub>(TEF)</sub>             | Thermal error flag threshold                                                             | Junction temperature, rising temperature <sup>(2)</sup>                                                                 | 150                  | 160               | 180   | °C   |

| V <sub>(LOD)</sub>             | LED open detection threshold                                                             |                                                                                                                         |                      | 0.3               | 0.4   | V    |

| V <sub>(IREF)</sub>            | Reference voltage output                                                                 | R <sub>(IREF)</sub> = 600 Ω                                                                                             | 1.20                 | 1.24              | 1.28  | V    |

Measured at device start-up temperature. Once the IC is operating (self heating), lower I<sub>CC</sub> values will be seen. See Figure 18.

Not tested. Specified by design.

SLVS550B-DECEMBER 2004-REVISED JANUARY 2013

www.ti.com

#### **DISSIPATION RATINGS**

| PACKAGE                                                  | POWER RATING<br>T <sub>A</sub> < 25°C | DERATING FACTOR<br>ABOVE TA = 25°C | POWER RATING<br>T <sub>A</sub> = 70°C | POWER RATING<br>T <sub>A</sub> = 85°C |

|----------------------------------------------------------|---------------------------------------|------------------------------------|---------------------------------------|---------------------------------------|

| 32-pin HTSSOP with PowerPAD <sup>(1)</sup><br>soldered   | 5318 mW                               | 42.54 mW/°C                        | 3403 mW                               | 2765 mW                               |

| 32-pin HTSSOP with PowerPAD <sup>(1)</sup><br>unsoldered | 2820 mW                               | 22.56 mW/°C                        | 1805 mW                               | 1466 mW                               |

| 32-pin QFN                                               | 3482 mW                               | 27.86 mW/°C                        | 2228 mW                               | 1811 mW                               |

(1) The PowerPAD is soldered to the PCB with a 2 oz. copper trace. See SLMA002 for further information.

## SWITCHING CHARACTERISTICS

|                  | PARAMETER              | TEST CONDITIONS                                                                                           | MIN | TYP | MAX  | UNIT |

|------------------|------------------------|-----------------------------------------------------------------------------------------------------------|-----|-----|------|------|

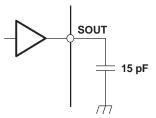

| t <sub>r0</sub>  | Rise time              | SOUT(see <sup>(1)</sup> )                                                                                 |     |     | 16   | 20   |

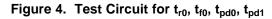

| t <sub>r1</sub>  | Rise lime              | OUTn, $V_{CC} = 5 \text{ V}$ , $T_A = 60^{\circ}\text{C}$ , DCx = 7F (see <sup>(2)</sup> )                |     | 10  | 30   | ns   |

| t <sub>f0</sub>  | Fall time              | SOUT (see <sup>(1)</sup> )                                                                                |     |     | 16   | 2    |

| t <sub>f1</sub>  | Fairtime               | OUTn, $V_{CC} = 5 \text{ V}$ , $T_A = 60^{\circ}\text{C}$ , DCx = 7F (see <sup>(2)</sup> )                |     | 10  | 30   | ns   |

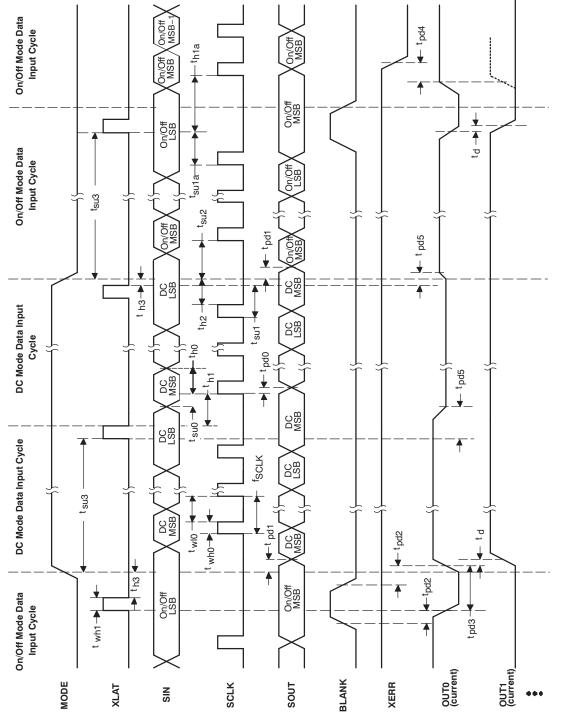

| t <sub>pd0</sub> |                        | SCLK $\uparrow$ to SOUT $\uparrow \downarrow$ (see <sup>(3) (4)</sup> )                                   |     |     | 30   |      |

| t <sub>pd1</sub> |                        | $MODE\uparrow\downarrow$ to $SOUT\uparrow\downarrow$ (see <sup>(3)</sup> )                                |     |     | 30   |      |

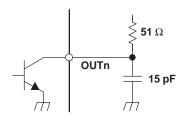

| t <sub>pd2</sub> | Drongation dology time | BLANK $\uparrow\downarrow$ to OUT0 $\uparrow\downarrow$ (see <sup>(5)</sup> ), Sink current On/Off        |     |     | 60   | ~~   |

| t <sub>pd3</sub> | Propagation delay time | XLAT $\uparrow$ to OUT0 $\uparrow\downarrow$ (see <sup>(5)</sup> )                                        |     |     | 60   | ns   |

| t <sub>pd4</sub> |                        | $OUTn\uparrow\downarrow$ to XERR $\uparrow\downarrow$ (see <sup>(6)</sup> )                               |     |     | 1000 |      |

| t <sub>pd5</sub> |                        | XLAT↑ to I <sub>OUT</sub> (dot-correction) (see <sup>(7)</sup> )                                          |     |     | 1000 |      |

| t <sub>d</sub>   | Output delay time      | OUTn $\uparrow$ to OUT(n+1) $\uparrow$ , OUTn $\downarrow$ to OUT(n+1) $\downarrow$ (see <sup>(5)</sup> ) | 14  | 22  | 30   | ns   |

(1) See Figure 4. Defined as from 10% to 90%

(2) See Figure 5. Defined as from 10% to 90%

(3) See Figure 4, Figure 14

(4) " $\uparrow$ " and " $\downarrow$ " indicates a rising edge, and a falling edge respectively.

(5) See Figure 5 and Figure 14

(6) See Figure 5, Figure 6, and Figure 14

(7) See Figure 5

4 Submit Documentation Feedback

#### SLVS550B-DECEMBER 2004-REVISED JANUARY 2013

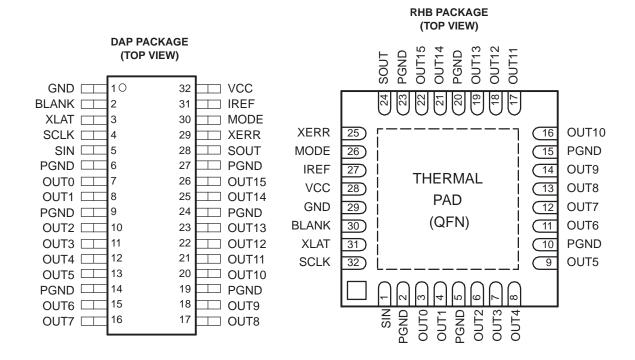

#### **Terminal Functions**

| TERMINAL |                         | TERMINAL                |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|-------------------------|-------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | N                       | 0.                      | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| NAME     | TSSOP                   | QFN                     |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| BLANK    | 2                       | 30                      | I   | Blank (Light OFF). When BLANK=H, All OUTn outputs are forced OFF. When BLANK=L, ON/OFF of OUTn outputs are controlled by input data.                                                                                                                                                                                                                                                                                                                                                                         |

| GND      | 1                       | 29                      |     | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| IREF     | 31                      | 27                      | I/O | Reference current terminal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| MODE     | 30                      | 26                      | I   | Mode select. When MODE=L, SIN, SOUT, SCLK, XLAT are connected to ON/OFF control logic. When MODE=H, SIN, SOUT, SCLK, XLAT are connected to dot-correction logic.                                                                                                                                                                                                                                                                                                                                             |

| OUT0     | 7                       | 3                       | 0   | Constant current output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT1     | 8                       | 4                       | 0   | Constant current output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT2     | 10                      | 6                       | 0   | Constant current output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT3     | 11                      | 7                       | 0   | Constant current output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT4     | 12                      | 8                       | 0   | Constant current output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT5     | 13                      | 9                       | 0   | Constant current output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT6     | 15                      | 11                      | 0   | Constant current output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT7     | 16                      | 12                      | 0   | Constant current output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT8     | 17                      | 13                      | 0   | Constant current output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT9     | 18                      | 14                      | 0   | Constant current output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT10    | 20                      | 16                      | 0   | Constant current output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT11    | 21                      | 17                      | 0   | Constant current output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT12    | 22                      | 18                      | 0   | Constant current output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT13    | 23                      | 19                      | 0   | Constant current output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT14    | 25                      | 21                      | 0   | Constant current output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT15    | 26                      | 22                      | 0   | Constant current output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PGND     | 6, 9, 14,<br>19, 24, 27 | 2, 5, 10,<br>15, 20, 23 |     | Power ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SCLK     | 4                       | 32                      | I   | Data shift clock. Note that the internal connections are switched by MODE (pin #30). At SCLK↑, the shift-registers selected by MODE shift the data.                                                                                                                                                                                                                                                                                                                                                          |

| SIN      | 5                       | 1                       | Ι   | Data input of serial I/F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SOUT     | 28                      | 24                      | 0   | Data output of serial I/F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VCC      | 32                      | 28                      |     | Power supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

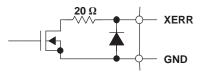

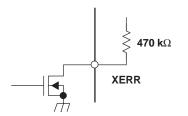

| XERR     | 29                      | 25                      | 0   | Error output. XERR is open drain terminal. XERR transistions from H to L when LOD or TEF detected.                                                                                                                                                                                                                                                                                                                                                                                                           |

| XLAT     | 3                       | 31                      | I   | Data latch signal. When MODE = L (ON/OFF data mode), XLAT is an edge-triggered latch signal of ON/OFF registers. The serial data in ON/OFF input shift registers is latched into the ON/OFF registers at the rising edge of XLAT. When MODE = H (DC data mode), XLAT is a level-triggered latch signal of dot correction registers. The serial data in DC input shift registers is written into dot correction registers when XLAT = H. The data in dot correction registers is held constant when XLAT = L. |

SLVS550B-DECEMBER 2004-REVISED JANUARY 2013

www.ti.com

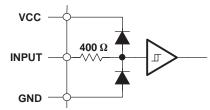

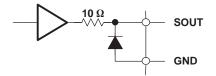

## PIN EQUIVALENT INPUT AND OUTPUT SCHEMATIC DIAGRAMS

(Note: Resistor values are equivalent resistance and not tested).

Figure 1. Input Equivalent Circuit (BLANK, XLAT, SCLK, SIN, MODE)

Figure 2. Output Equivalent Circuit

Figure 3. Output Equivalent Circuit (XERR)

## PARAMETER MEASUREMENT INFORMATION

Figure 5. Test Circuit for  $t_{r1},\,t_{f1},\,t_{pd2},\,t_{pd3},\,t_{pd5},\,t_d$

## PARAMETER MEASUREMENT INFORMATION (continued)

Figure 6. Test Circuit for  $t_{pd4}$

SLVS550B-DECEMBER 2004-REVISED JANUARY 2013

## PRINCIPLES OF OPERATION

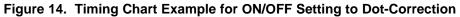

## Setting Maximum Channel Current

The maximum output current per channel is set by a single external resistor, R<sub>(IREF)</sub>, which is placed between IREF and GND. The voltage on IREF is set by an internal band gap V(IREF) with a typical value of 1.24V. The maximum channel current is equivalent to the current flowing through R<sub>(IRFE)</sub> multiplied by a factor of 40. The maximum output current per channel can be calculated by Equation 1:

$$I_{MAX} = \frac{V_{IREF}}{R_{IREF}} \times 40$$

(1)

where:

$V_{IREF} = 1.24V$  typ.

$R_{IREF}$  = User selected external resistor ( $R_{IREF}$  should not be smaller than 600  $\Omega$ )

Figure 15 shows the maximum output current, I<sub>OLC</sub>, versus R<sub>(IREF)</sub>. In Figure 15, R<sub>(IREF)</sub> is the value of the resistor between IREF terminal to ground, and IOLC is the constant output current of OUT0,.....OUT15. A variable power supply may be connected to the IREF pin through a resistor to change the maximum output current per channel. The maximum output per channel is 40 times the current flowing out of the IREF pin. The maximum current from IREF equals  $1.24V/600\Omega$ .

## Setting Dot-Correction

The TLC5923 has the capability to fine adjust the current of each channel, OUT0 to OUT15 independently. This is also called dot correction. This feature is used to adjust the brightness deviations of LED connected to the output channels OUT0 to OUT15. Each of the 16 channels can be programmed with a 7-bit word. The channel output can be adjusted in 128 steps from 0% to 100% of the maximum output current IMAX. Dot correction for all channels must be entered at the same time. Equation 2 determines the output current for each OUTn:

$$I_{Outn} = \frac{I_{MAX} \times DC_n}{127}$$

(2)

where:

$I_{Max}$  = the maximum programmable current of each output

DCn = the programmed dot-correction value for output n ( $DCn = 0, 1, 2 \dots 127$ )

n = 0, 1, 2 ... 15

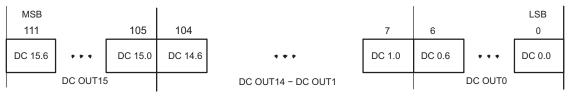

Dot correction data are entered for all channels at the same time. The complete dot correction data format consists of 16 x 7-bit words, which forms a 112-bit wide serial data packet. The channel data is put one after another. All data is clocked in with MSB first. Figure 7 shows the DC data format. The DC15.6 in Figure 7 stands for the 6<sup>th</sup> most significant bit for output 15.

Figure 7. DC Data Format

To input data into dot correction register, MODE must be set to high. The internal input shift register is then set to 112 bit width. After all serial data is clocked in, a high level pulse of XLAT signal connects the serial data to the dot correction register. The dot correction registers are level-triggered latches of XLAT signal. The serial data is latched into the dot correction registers when XLAT goes low. The data in dot correction registers is held constant when XLAT is low. BLANK signal does not need to be high to latch in new data. Since XLAT is a leveltriggered signal when MODE is high, SCLK and SIN must not be changed while XLAT is high. (Figure 14).

**ISTRUMENTS**

FXAS

Copyright © 2004–2013, Texas Instruments Incorporated

#### **Output Enable**

All OUTn channels of TLC5923 can switched off with one signal. When BLANK signal is set to high, all OUTn are disabled, regardless of On/Off status of each OUTn. When BLANK is set to low, all OUTn work under normal conditions.

| BLANK | OUT0 - OUT15     |  |  |

|-------|------------------|--|--|

| LOW   | Normal condition |  |  |

| HIGH  | Disabled         |  |  |

#### Table 1. BLANK Signal Truth Table

#### Setting Channel On/Off Status

All OUTn channels of TLC5923 can be switched on or off independently. Each of the channels can be programmed with a 1-bit word. On/Off data are entered for all channels at the same time. The complete On/Off data format consists of 16 x 1-bit words, which form a 16-bit wide data packet. The channel data is put one after another. All data is clocked in with MSB first. Figure 8 shows the On/Off data format.

#### Figure 8. On/Off Data Format

To input On/Off data into On/Off register MODE must be set to low. The internal input shift register is then set to 16 bit width. After all serial data is clocked in, a rising edge of XLAT is used to latch data into the On/Off register. The ON/OFF register is an edge-triggered latch of XLAT signal. BLANK signal does not need to be high to latch in new data. Figure 14 shows the On/Off data input timing chart.

#### **Delay Between Outputs**

The TLC5923 has graduated delay circuits between outputs. These delay circuits can be found in the constant current block of the device (see Functional Block Diagram). The fixed delay time is 20 ns (typical), OUT0 has no delay, OUT1 has 20 ns delay, OUT2 has 40 ns delay, etc. This delay prevents large inrush currents, which reduce power supply bypass capacitor requirements when the outputs turn on. The delay works during switch on and switch off of each output channel. LEDs that have not turned on before BLANK is pulled high will still turn on and off at the determined delayed time regardless of the state of BLANK. Therefore, every LED will be illuminated for the amount of time BLANK is low.

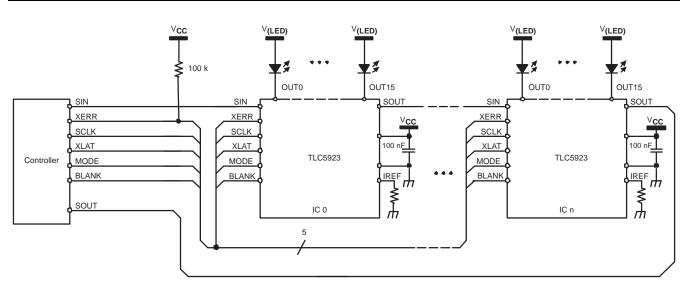

#### Serial Interface Data Transfer Rate

The TLC5923 includes a flexible serial interface, which can be connected to microcontroller or digital signal processor. Only 3 pins are in required to input data into the device. The rising edge of SCLK signal shifts the data from SIN pin to internal shift register. After all data is clocked in, a rising edge of XLAT latches the serial data to the internal registers. All data is clocked in with MSB first. Multiple TLC5923 devices can be cascaded by connecting SOUT pin of one device with SIN pin of following device. The SOUT pin can also be connected to controller to receive LOD information from TLC5923.

(3)

SLVS550B-DECEMBER 2004-REVISED JANUARY 2013

Figure 9. Cascading Devices

Figure 9 shows a example application with n cascaded TLC5923 devices connected to a controller. The maximum number of cascaded TLC5923 devices depends on application system and data transfer rate. Equation 3 calculates the minimum data input frequency needed.

$$f_(SCLK) = 112 \times f_(update) \times n$$

where:

f\_(SCLK): The minimum data input frequency for SCLK and SIN.

f\_(update): The update rate of the whole cascaded system.

n: The number of cascaded TLC5923 devices.

#### **Operating Modes**

The TLC5923 has different operating modes depending on MODE signal. Table 2 shows the available operating modes. The values in the input shift registers, DC register and On/Off register are unknown just after power on. The DC and On/Off register values should be properly stored through the serial interface before starting the operation.

| MODE SIGNAL | INPUT SHIFT REGISTER | MODE                           |

|-------------|----------------------|--------------------------------|

| LOW         | 16 bit               | On/Off Mode                    |

| HIGH        | 112 bit              | Dot Correction Data Input Mode |

| Table 2. | TLC5923         | Operating | Modes | Truth | Table |

|----------|-----------------|-----------|-------|-------|-------|

|          | 1 2 0 0 0 2 2 0 | operating | Moucs | mun   | Table |

#### **Error Information Output**

The open-drain output XERR is used to report both of the TLC5923 error flags, TEF and LOD. During normal operating conditions, the internal transistor connected to the XERR pin is turned off. The voltage on XERR is pulled up to  $V_{CC}$  through a external pullup resistor. If TEF or LOD is detected, the internal transistor is turned on, and XERR is pulled to GND. Since XERR is an open-drain output, multiple ICs can be OR'ed together and pulled up to  $V_{CC}$  with a single pullup resistor. This reduces the number of signals needed to report a system error.

To differentiate LOD and TEF signal from XERR pin, LOD can be masked out with BLANK = HIGH.

|                   | CONDITION |                           | ERROR INFORMATION |      | XERR                  |

|-------------------|-----------|---------------------------|-------------------|------|-----------------------|

| TEMPERATURE       | BLANK     | OUTn VOLTAGE              | TEF               | LODn | _                     |

| $T_J < T_{(TEF)}$ | Н         | Don't Care                | L                 | L    | High-Z <sup>(1)</sup> |

| $T_J > T_{(TEF)}$ |           |                           | Н                 |      | L                     |

| $T_J < T_{(TEF)}$ | L         | $OUTn > V_{(LOD)}$        | L                 | L    | High-Z                |

|                   |           | OUTn < V <sub>(LOD)</sub> |                   | Н    | L                     |

| $T_J > T_{(TEF)}$ |           | OUTn > V <sub>(LOD)</sub> | Н                 | L    | L                     |

|                   |           | OUTn < V <sub>(LOD)</sub> |                   | Н    | L                     |

Table 3. XERR Truth Table

(1) Note: High-Z indicates high impedance

#### **TEF: Thermal Error Flag**

The TLC5923 provides a temperature error flag (TEF) circuit to indicate an overtemperature condition of the IC. If the junction temperature exceeds the threshold temperature  $T_{(TEF)}$  (160°C typical), TEF becomes H and XERR pin goes to low level. When the junction temperature becomes lower than the threshold temperature, TEF becomes L and XERR pin becomes high impedance.

#### LOD: LED-Open Detection

The TLC5923 has an LED-open detector to detect broken or disconnected LEDs, which should be connected to the output. The LED-open detector pulls the XERR pin down to GND when the LED open is detected. An open LED is detected when the following three conditions are met:

- 1. BLANK is low

- 2. On/Off data is high

- 3. The voltage of OUTn is less than 0.3 V (typical)

The LOD status of each output can also be read out from the SOUT pin. Figure 10 shows the LOD data format. Table 4 shows the LOD truth table.

| MSB          |              |              |          |             |             | LSB         |

|--------------|--------------|--------------|----------|-------------|-------------|-------------|

| 15           |              |              |          |             |             | 0           |

| LOD<br>OUT15 | LOD<br>OUT14 | LOD<br>OUT13 | * * *    | LOD<br>OUT2 | LOD<br>OUT1 | LOD<br>OUT0 |

|              |              |              | LOD Data |             |             |             |

Figure 10. LOD Data Format

SLVS550B - DECEMBER 2004 - REVISED JANUARY 2013

www.ti.com

| Table 4 |       | Data | Truth | Table |

|---------|-------|------|-------|-------|

|         | . LOD | σαια | mun   | Table |

| LED  | ON/OFF | LOD BIT |

|------|--------|---------|

| Good | On     | 0       |

| Good | Off    | 0       |

| Bad  | On     | 1       |

| Bad  | Off    | 0       |

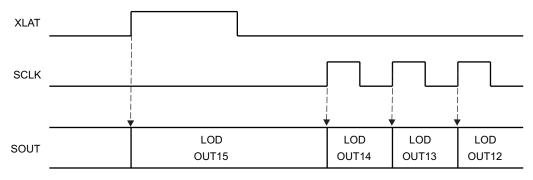

#### Key Timing Requirements to Reading LOD

LOD status flag

The LOD status flag becomes active if the output voltage is <0.3 V (typical) when the output sink current turns on. There is a 1- $\mu$ s time delay from the time the output sink current turns on until the time the LOD status flag becomes valid. The timing for each channel's LOD status to become valid is shifted by the 30 ns channel-to-channel turn-on time. After BLANK goes low, OUT0 LOD status is valid when tpd2 + tpd4 = 60 ns + 1  $\mu$ s = 1.06  $\mu$ s. OUT1 LOD status is valid when tpd2 + tpd4 + td = 60 ns + 1  $\mu$ s + 30 ns = 1.09  $\mu$ s. OUT3 LOD status is valid when tpd2 + tpd4 + 2\*td = 1.12  $\mu$ s, and so on.

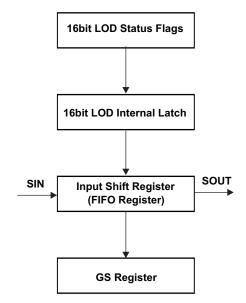

LOD internal latch

The TLC5923 has an internal latch to hold each channel's LOD status flag information, as shown in Figure 11. When MODE is low, the LOD status information is latched into this latch on the rising edge of XLAT. This is an edge-triggered latch. To ensure that a valid LOD status flag is latched, BLANK must be low when XLAT goes high. After the rising edge of XLAT, changes in the status flags do not affect the values in the LOD latch.

· Loading LOD data to the input shift register

The LOD data must be transferred to the input shift register before it is available to be clocked out of SOUT. The internal shift register has a set/reset function that is controlled by the LOD internal latch. While XLAT is high, the LOD internal latch holds the input shift register in either set or reset, depending on the value in the latch. This effectively puts the LOD data into the input shift register where it remains as long as XLAT is high. The values in the input shift register are unaffected by any other signals, including SIN and SCLK while XLAT is high. During this time, the status of OUT15 is present on SOUT.

Latching LOD data into the internal shift register

While XLAT is high, the status of OUT15 is present on SOUT. When XLAT transitions low, all data is latched into the Input shift register, and the LOD internal latch is disconnected from the internal shift register.

Clocking LOD data out of SOUT

While XLAT is low and SCLK is low, the status of OUT15 is on SOUT. On the next rising edge of SCLK, the status of OUT14 shifts to SOUT. Each subsequent rising edge of SCLK shifts the LOD data out of SOUT. XLAT must stay low until all LOD data is clocked out of SOUT. See *Shifting the LOD Data Out* section for more details.

SLVS550B-DECEMBER 2004-REVISED JANUARY 2013

Figure 11. LOD Flags and Latches

#### Shifting the LOD Data Out

SOUT outputs the LOD data as shown in Figure 12, where:

- XLAT rising edge

- Holds the LOD status flag. SOUT outputs LOD OUT15 data. BLANK must be low.

- XLAT = H

Sets or resets the input shift register depending on each LOD data.

Set/Reset function is higher priority than shifting the register value. If XLAT is high and the SCLK pin is pulsed, all LOD data are kept in the shift register and SOUT keeps the LOD OUT15 data.

• XLAT = L

Ready to shift out LOD data by SCLK. SOUT contains LOD OUT15 data at this time. BLANK can be high or low during this time.

SCLK rising edge

SOUT outputs LOD OUT14 at the first SCLK rising edge. SOUT outputs LOD OUT13 at the second SCLK rising edge, and continues to output the next LOD data at each SCLK rising edge.

Figure 12. The LOD Data of SOUT

Figure 13 shows the timing chart of reading LOD data.

# TLC5923

SLVS550B-DECEMBER 2004-REVISED JANUARY 2013

| MODE  |                           | At the rising edge of XLAT while BLANK=L, LOD status is latched into the internal edgetriggered register. |       |

|-------|---------------------------|-----------------------------------------------------------------------------------------------------------|-------|

| XLAT  |                           | When XLAT=H, the internal edge-triggered register<br>sets or resets the input shift register              | _     |

| SCLK  |                           |                                                                                                           |       |

| SIN   |                           |                                                                                                           | _     |

| SOUT  |                           |                                                                                                           | _     |

| BLANK | 1510ns max                | 1510ns max                                                                                                | _     |

| Ουτο  | tpd2: 60ns max            | tpd2: 60ns max                                                                                            |       |

| OUT15 | LED open                  |                                                                                                           | ····· |

| XERR  | td x 15 = 450ns max       | td x 15 = 450ns max                                                                                       | _     |

|       | <b>4</b> tpd4: 1000ns max | tpd4: 1000ns max                                                                                          |       |

|       | >1000ns                   | >1000ns                                                                                                   |       |

Figure 13. Timing Chart of Reading LOD Data

.

**EXAS** STRUMENTS

www.ti.com

SLVS550B – DECEMBER 2004 – REVISED JANUARY 2013

TEXAS INSTRUMENTS

www.ti.com

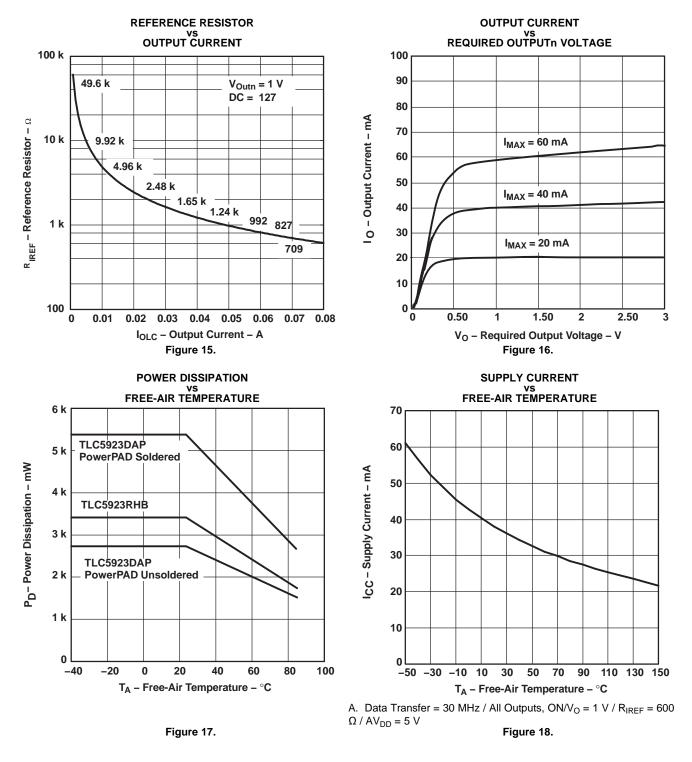

## **TYPICAL CHARACTERISTICS**

## Power Rating – Free-Air Temperature

Figure 17 shows total power dissipation. Figure 18 shows supply current versus free-air temperature.

SLVS550B-DECEMBER 2004-REVISED JANUARY 2013

#### **REVISION HISTORY**

NOTE: Page numbers of previous versions may differ from current version.

| Cł | anges from Revision A (November 2005) to Revision B                               | Page |

|----|-----------------------------------------------------------------------------------|------|

| •  | Corrected device number from "TLC4923RHB" to "TLC5923RHB" in Ordering Info table. | 2    |

## PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty |              | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing            |      | Gly            | (2)          | (6)                           | (3)                 |              | (4/5)          |         |

| TLC5923DAP       | ACTIVE | HTSSOP       | DAP                | 32   | 46             | RoHS & Green | NIPDAU                        | Level-3-260C-168 HR | -40 to 85    | TLC5923        | Samples |

| TLC5923DAPG4     | ACTIVE | HTSSOP       | DAP                | 32   | 46             | RoHS & Green | NIPDAU                        | Level-3-260C-168 HR | -40 to 85    | TLC5923        | Samples |

| TLC5923DAPR      | ACTIVE | HTSSOP       | DAP                | 32   | 2000           | RoHS & Green | NIPDAU                        | Level-3-260C-168 HR | -40 to 85    | TLC5923        | Samples |

| TLC5923RHBR      | ACTIVE | VQFN         | RHB                | 32   | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | TLC<br>5923    | Samples |

| TLC5923RHBT      | ACTIVE | VQFN         | RHB                | 32   | 250            | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | TLC<br>5923    | Samples |

| TLC5923RHBTG4    | ACTIVE | VQFN         | RHB                | 32   | 250            | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | TLC<br>5923    | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

## PACKAGE OPTION ADDENDUM

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

Texas

STRUMENTS

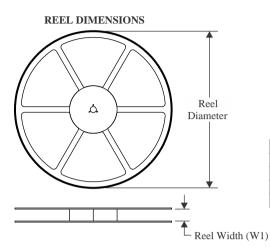

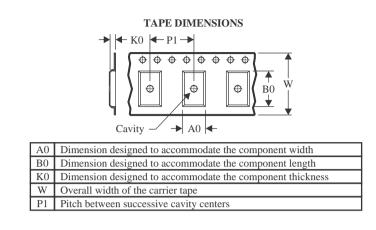

## TAPE AND REEL INFORMATION

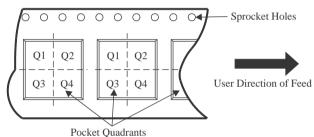

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| TLC5923DAPR                 | HTSSOP          | DAP                | 32 | 2000 | 330.0                    | 24.4                     | 8.6        | 11.5       | 1.6        | 12.0       | 24.0      | Q1               |

| TLC5923RHBR                 | VQFN            | RHB                | 32 | 3000 | 330.0                    | 12.4                     | 5.3        | 5.3        | 1.5        | 8.0        | 12.0      | Q2               |

| TLC5923RHBT                 | VQFN            | RHB                | 32 | 250  | 180.0                    | 12.4                     | 5.3        | 5.3        | 1.5        | 8.0        | 12.0      | Q2               |

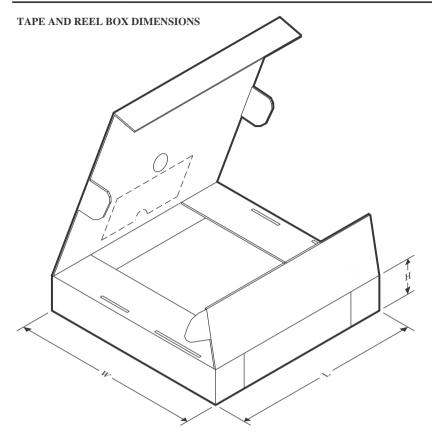

# PACKAGE MATERIALS INFORMATION

5-Dec-2023

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TLC5923DAPR | HTSSOP       | DAP             | 32   | 2000 | 350.0       | 350.0      | 43.0        |

| TLC5923RHBR | VQFN         | RHB             | 32   | 3000 | 356.0       | 356.0      | 35.0        |

| TLC5923RHBT | VQFN         | RHB             | 32   | 250  | 210.0       | 185.0      | 35.0        |

## TEXAS INSTRUMENTS

www.ti.com

5-Dec-2023

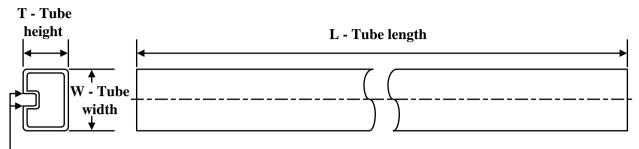

## TUBE

## - B - Alignment groove width

\*All dimensions are nominal

| Device       | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | Τ (μm) | B (mm) |

|--------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| TLC5923DAP   | DAP          | HTSSOP       | 32   | 46  | 530    | 11.89  | 3600   | 4.9    |

| TLC5923DAPG4 | DAP          | HTSSOP       | 32   | 46  | 530    | 11.89  | 3600   | 4.9    |

# **DAP 32**

# **GENERIC PACKAGE VIEW**

# PowerPAD<sup>™</sup> TSSOP - 1.2 mm max height

8.1 x 11, 0.65 mm pitch

PLASTIC SMALL OUTLINE

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

- This drawing is subject to change without notice. Β.

- Body dimensions do not include mold flash or protrusion. Mold flash and protrusion shall not exceed 0.15 per side. C.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad

- Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>. Falls within JEDEC MO-153 Variation DCT.

PowerPAD is a trademark of Texas Instruments.

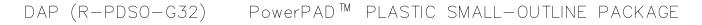

# DAP (R-PDSO-G32)

# PowerPAD<sup>™</sup> PLASTIC SMALL OUTLINE

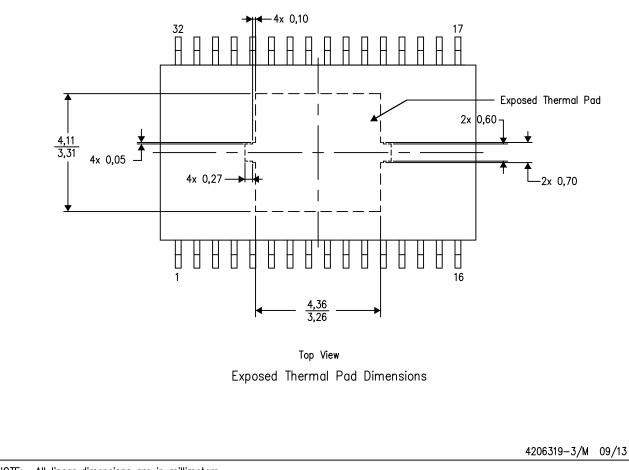

#### THERMAL INFORMATION

This PowerPAD<sup> $\mathbb{M}$ </sup> package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

NOTE: All linear dimensions are in millimeters

PowerPAD is a trademark of Texas Instruments.

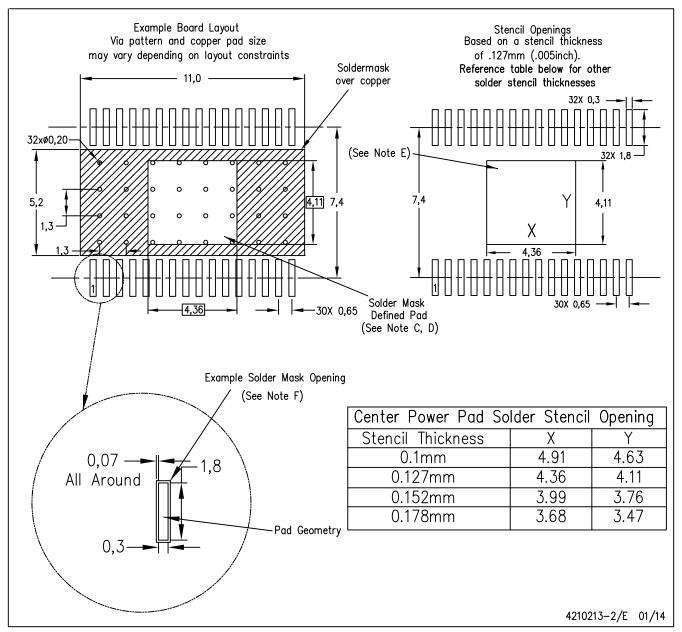

DAP (R-PDSO-G32) PowerPAD™ PLASTIC SMALL OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <http://www.ti.com>. Publication IPC-7351 is recommended for alternate designs.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

- F. Contact the board fabrication site for recommended soldermask tolerances.

PowerPAD is a trademark of Texas Instruments

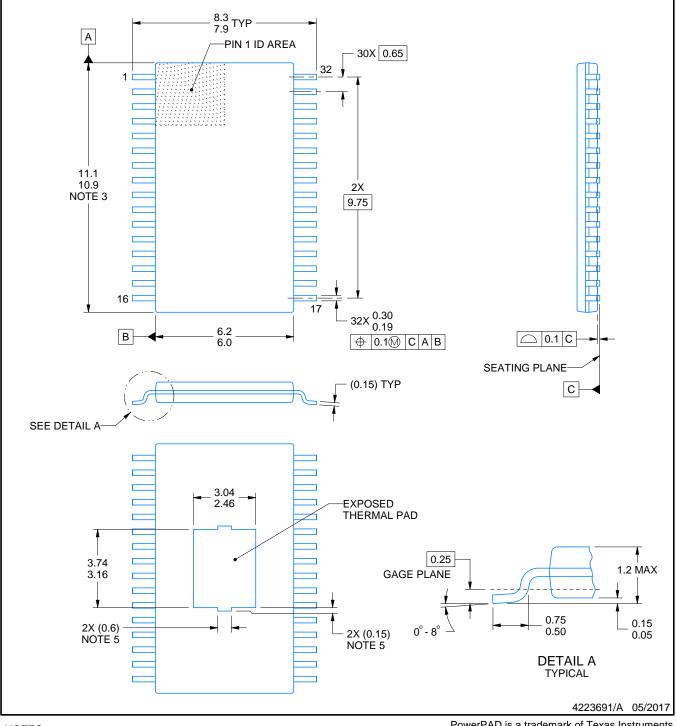

# **PACKAGE OUTLINE**

# **DAP0032C**

## PowerPAD<sup>™</sup> TSSOP - 1.2 mm max height

PLASTIC SMALL OUTLINE

NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

- 4. Reference JEDEC registration MO-153.

- 5. Features may differ and may not be present.

# **DAP0032C**

# **EXAMPLE BOARD LAYOUT**

## PowerPAD<sup>™</sup> TSSOP - 1.2 mm max height

PLASTIC SMALL OUTLINE

NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.

- Solder mask tolerances between and around signal pads can vary based on board fabrication site.

This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 (www.ti.com/lit/slma002) and SLMA004 (www.ti.com/lit/slma004).

- 9. Size of metal pad may vary due to creepage requirement.

# DAP0032C

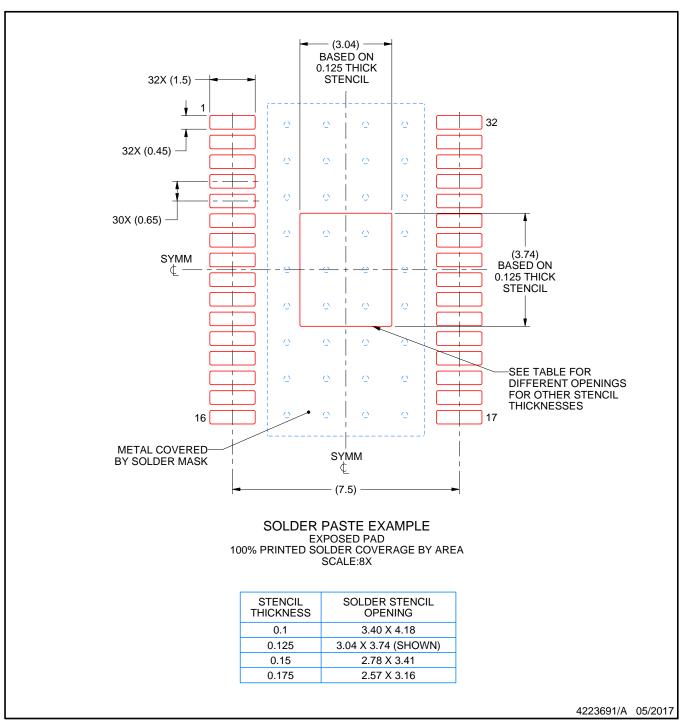

# **EXAMPLE STENCIL DESIGN**

## PowerPAD<sup>™</sup> TSSOP - 1.2 mm max height

PLASTIC SMALL OUTLINE

NOTES: (continued)

10. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

11. Board assembly site may have different recommendations for stencil design.

# **RHB 32**

5 x 5, 0.5 mm pitch

# **GENERIC PACKAGE VIEW**

## VQFN - 1 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

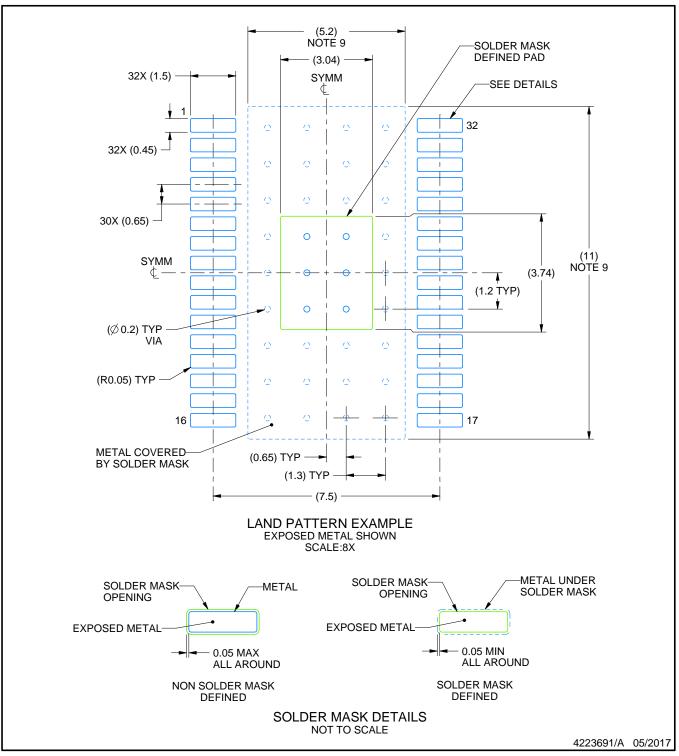

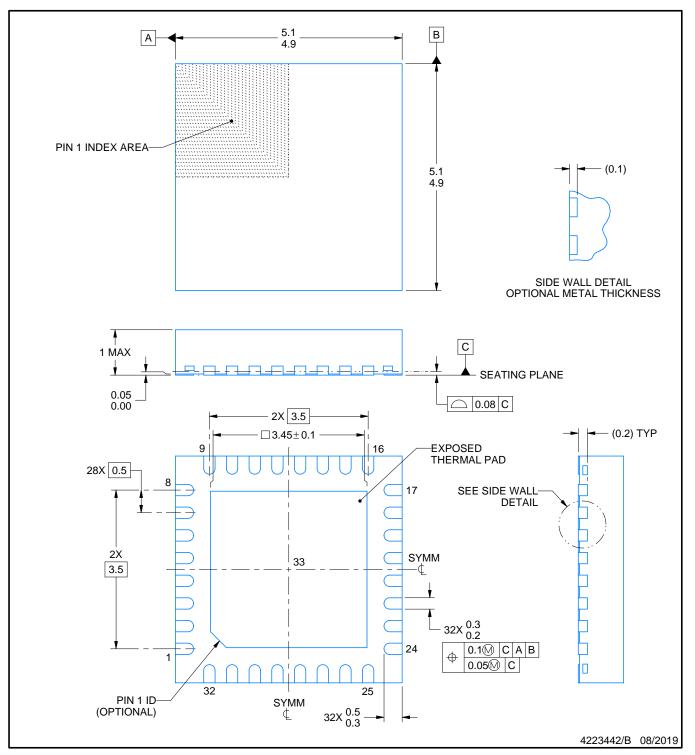

# **RHB0032E**

# **PACKAGE OUTLINE**

## VQFN - 1 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

# **RHB0032E**

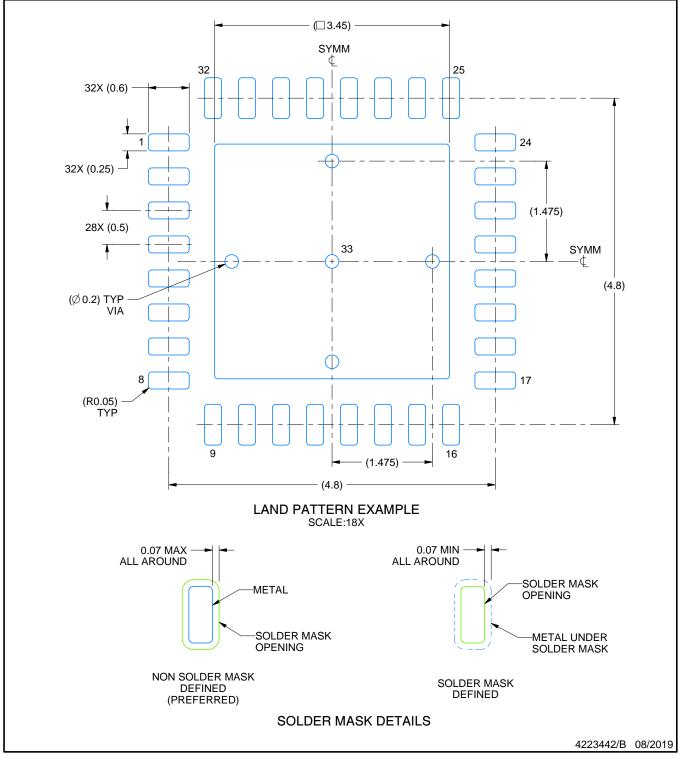

# **EXAMPLE BOARD LAYOUT**

## VQFN - 1 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

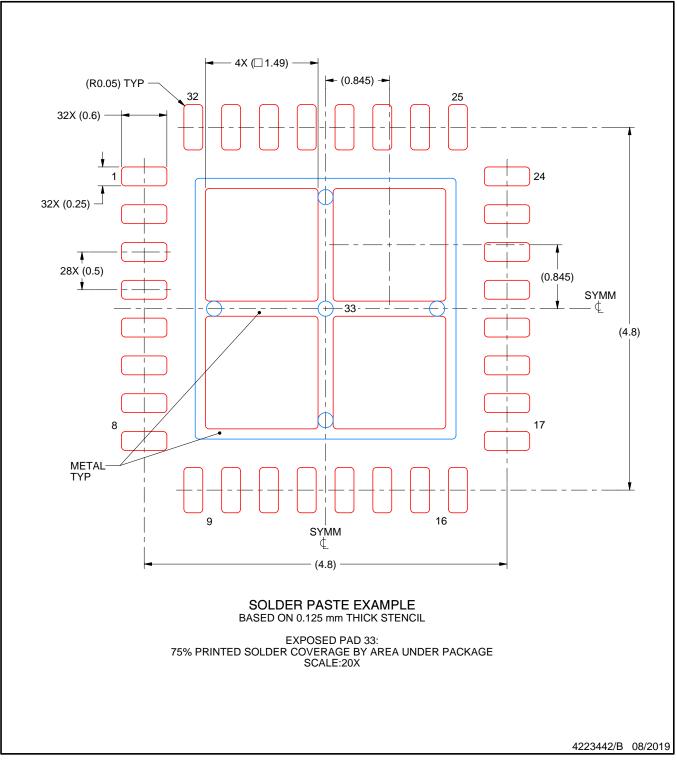

# **RHB0032E**

# **EXAMPLE STENCIL DESIGN**

## VQFN - 1 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated