Sample &

Buy

TEXAS INSTRUMENTS

TPS65735

SLVSAI6A - JUNE 2011 - REVISED JANUARY 2016

# **TPS65735 PMU for Active Shutter 3D Glasses**

# 1 Device Overview

# 1.1 Features

Linear Charger

•

- Three Charger Phases: Pre-Charge, Fast Charge, and Charge Termination

- Externally Set Charge Current Which Supports up to 100 mA

- LED Current Sinks for Power Good and Charger Status Indication

- Low-Dropout Regulator (LDO) Supply for External Modules (Microcontroller, RF Module, IR Module)

- LDO Continuous Output Current up to 30 mA

# 1.2 Applications

Active Shutter 3D Glasses

# 1.3 Description

- Boost Converter

- Adjustable Output Voltage: 8 V to 16 V

- Boost Output Internally Connected to H-Bridge Analog Switches

- Full H-Bridge Analog Switches

- Controlled by an External Microcontroller for System Operation

- Output Pin for Divided Down Battery Voltage

Useful for ADC or Comparator Input of an MCU

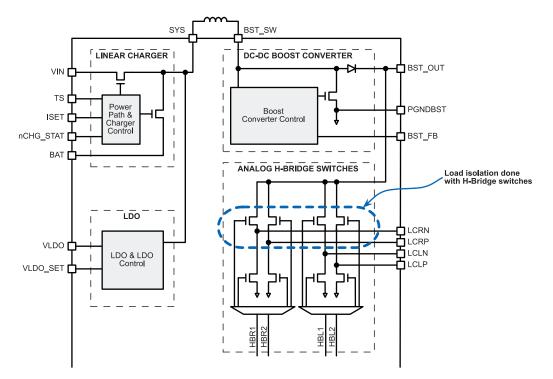

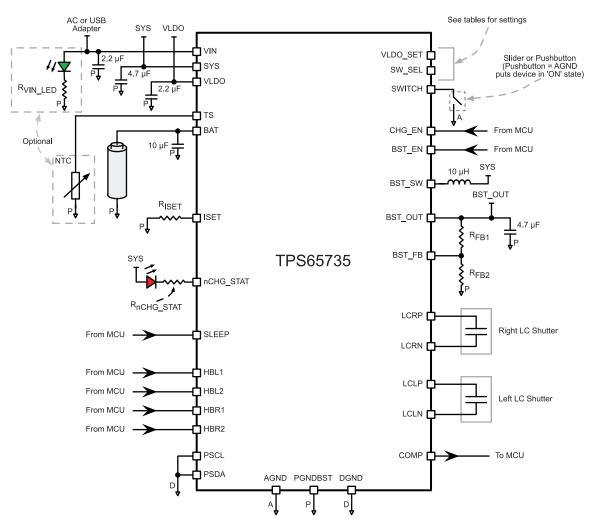

The TPS65735 device is a power management unit (PMU) for active shutter 3D glasses consisting of an integrated power path, linear charger, LDO, boost converter, and full H-bridge analog switches for left and right shutter operation in a pair of active shutter 3D glasses. In addition to the power devices, a typical 3D glasses system contains both a microcontroller and a communications front end (IR, RF, or other) in order to handle the communication and synchronous operation along with a 3D television.

# Device Information<sup>(1)</sup>

| Device information |           |                   |  |  |  |

|--------------------|-----------|-------------------|--|--|--|

| PART NUMBER        | PACKAGE   | BODY SIZE (NOM)   |  |  |  |

| TPS65735           | VSON (32) | 4.00 mm x 4.00 mm |  |  |  |

(1) For more information, see Section 10, Mechanical Packaging and Orderable Information.

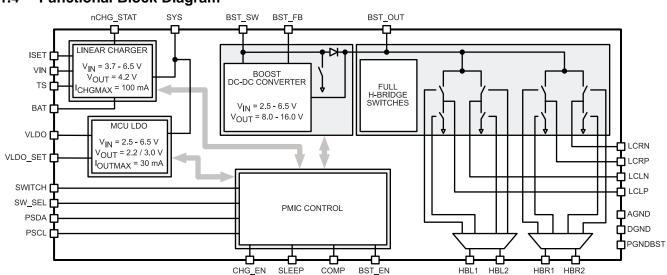

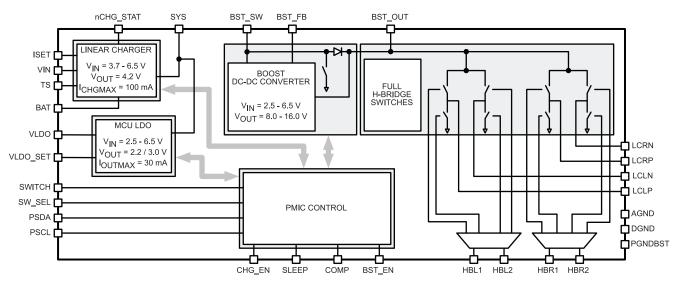

# 1.4 Functional Block Diagram

# **Table of Contents**

| 1 | Devi | ce Overview <u>1</u>              |

|---|------|-----------------------------------|

|   | 1.1  | Features 1                        |

|   | 1.2  | Applications 1                    |

|   | 1.3  | Description <u>1</u>              |

|   | 1.4  | Functional Block Diagram 1        |

| 2 | Revi | sion History 2                    |

| 3 | Term | ninal Configuration and Functions |

|   | 3.1  | Pin Diagram 3                     |

|   | 3.2  | Pin Functions <u>4</u>            |

| 4 | Spec | ifications <u>5</u>               |

|   | 4.1  | Absolute Maximum Ratings 5        |

|   | 4.2  | ESD Ratings                       |

|   | 4.3  | Power-On Hours (POH) 5            |

|   | 4.4  | Recommended Operating Conditions  |

|   | 4.5  | Thermal Information6              |

|   | 4.6  | Electrical Characteristics 7      |

|   | 4.7  | Quiescent Current 10              |

|   | 4.8  | Typical Characteristics 10        |

| 5 | Deta | iled Description 11               |

|   | 5.1  | Overview                          |

|    | 5.2   | Functional Block Diagram          | <u>11</u> |

|----|-------|-----------------------------------|-----------|

|    | 5.3   | Feature Description               | <u>11</u> |

|    | 5.4   | Device Functional Modes           | 24        |

| 6  | Appl  | ication and Implementation        | 25        |

|    | 6.1   | Application Information           | 25        |

|    | 6.2   | Typical Application               | 25        |

| 7  | Powe  | er Supply Recommendations         | 30        |

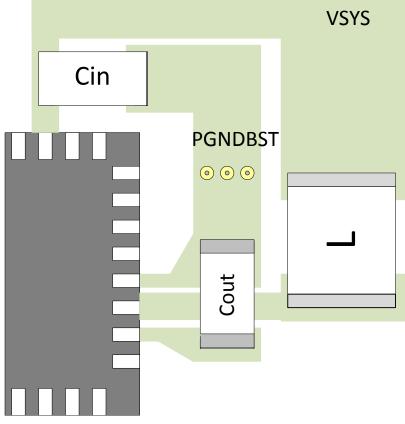

| 8  | Layo  | ut                                | 30        |

|    | 8.1   | Layout Guidelines                 | <u>30</u> |

|    | 8.2   | Layout Example                    | 30        |

| 9  | Devi  | ce and Documentation Support      | 31        |

|    | 9.1   | Device Support                    | 31        |

|    | 9.2   | Community Resources               | 31        |

|    | 9.3   | Trademarks                        | 31        |

|    | 9.4   | Electrostatic Discharge Caution   | 31        |

|    | 9.5   | Glossary                          | 31        |

| 10 |       | nanical, Packaging, and Orderable |           |

|    | Infor | mation                            | <u>31</u> |

|    | 10.1  | Packaging Information             | <u>31</u> |

|    |       |                                   |           |

# 2 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Original (June 2011) to Revision A                                                                                                                                                                                                                                                                                                                | Page |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| <ul> <li>Added ESD Ratings table, Typical Characteristics section, Detailed Description section, Device Functional<br/>Modes section, Application and Implementation section, Power Supply Recommendations section, Layout<br/>section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information<br/>section.</li> </ul> | 1    |

# **3** Terminal Configuration and Functions

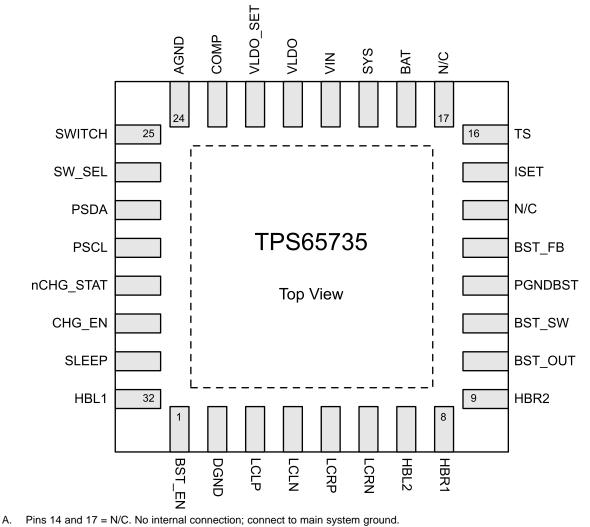

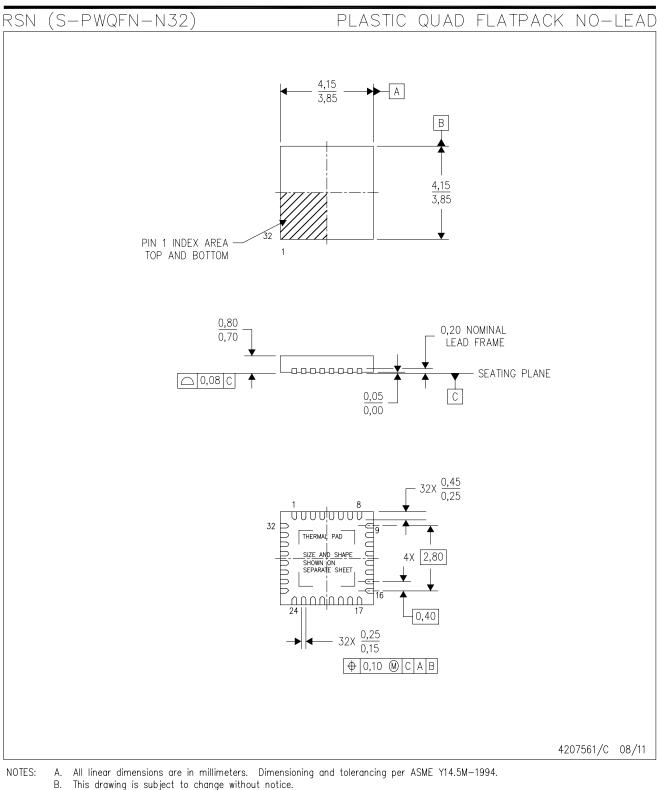

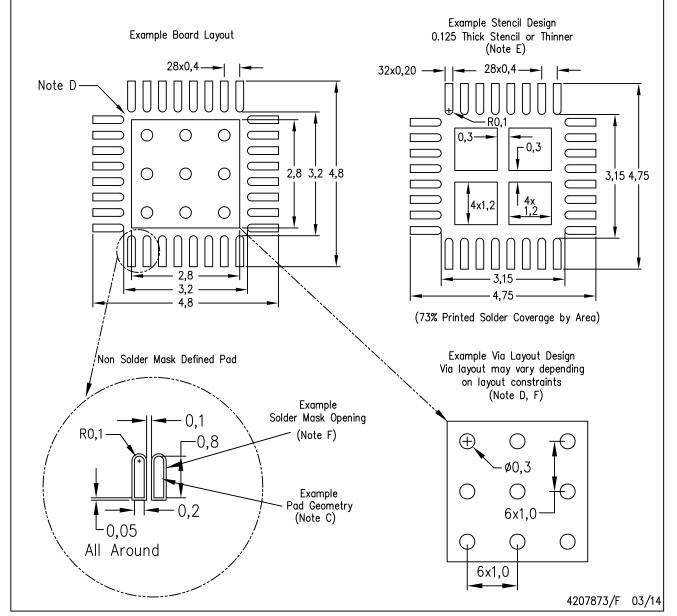

# 3.1 Pin Diagram

Figure 3-1. 32-Pin RSN WQFN (Top View)

# 3.2 Pin Functions

## Table 3-1. Pin Functions

| PIN       |                  |      |                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|-----------|------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NO.       | NAME             | I/O  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| POWER MA  | NAGEMENT CORE (P | MIC) |                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 1         | BST_EN           | I    | Boost Enable Input from an MCU, High = Boost Enabled                                                                                                                                                                                                                                                                                              |  |  |  |

| 2         | DGND             | _    | Digital Ground                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 3         | LCLP             | 0    | H-Bridge Output for Left LC Shutter, Positive Terminal                                                                                                                                                                                                                                                                                            |  |  |  |

| 4         | LCLN             | 0    | H-Bridge Output for Left LC Shutter, Negative Terminal                                                                                                                                                                                                                                                                                            |  |  |  |

| 5         | LCRP             | 0    | H-Bridge Output for Right LC Shutter, Positive Terminal                                                                                                                                                                                                                                                                                           |  |  |  |

| 6         | LCRN             | 0    | H-Bridge Output for Right LC Shutter, Negative Terminal                                                                                                                                                                                                                                                                                           |  |  |  |

| 7         | HBL2             | I    | H-Bridge Input 2 for Left LC Shutter                                                                                                                                                                                                                                                                                                              |  |  |  |

| 8         | HBR1             | I    | H-Bridge Input 1 for Right LC Shutter                                                                                                                                                                                                                                                                                                             |  |  |  |

| 9         | HBR2             | I    | H-Bridge Input 2 for Right LC Shutter                                                                                                                                                                                                                                                                                                             |  |  |  |

| 10        | BST_OUT          | 0    | Boost Output                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 11        | BST_SW           | 0    | Boost Switch Node                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 12        | PGNDBST          | _    | Boost Power Ground                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 13        | BST_FB           | I    | Boost Feedback Node                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 15        | ISET             | I/O  | Fast-Charge Current Setting Resistor                                                                                                                                                                                                                                                                                                              |  |  |  |

| 16        | TS               | I    | Pin for 10-kΩ NTC Thermistor Connection<br>FLOAT IF THERMISTOR / TS FUNCTION IS NOT USED                                                                                                                                                                                                                                                          |  |  |  |

| 18        | BAT              | I/O  | Charger Power Stage Output and Battery Voltage Sense Input                                                                                                                                                                                                                                                                                        |  |  |  |

| 19        | SYS              | 0    | Output Terminal to System                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 20        | VIN              | I    | AC or USB Adapter Input                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 21        | VLDO             | 0    | LDO Output                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 22        | VLDO_SET         | I    | Sets LDO Output Voltage (see Table 5-2)                                                                                                                                                                                                                                                                                                           |  |  |  |

| 23        | COMP             | 0    | Scaled Battery Voltage for MCU Comparator or ADC Input (Battery Voltage Monitoring)<br>DO NOT CONNECT IF COMP FUNCTION IS NOT USED                                                                                                                                                                                                                |  |  |  |

| 24        | AGND             | -    | Analog Ground                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 25        | SWITCH           | I    | Switch Input for Device Power On/Off                                                                                                                                                                                                                                                                                                              |  |  |  |

| 26        | SW_SEL           | I    | Selects Type of Switch Connected to SWITCH Pin (see Table 5-6)                                                                                                                                                                                                                                                                                    |  |  |  |

| 27        | PSDA             | I/O  | I <sup>2</sup> C Data Pin (only used for TI debug and test)<br>GROUND PIN IN APPLICATION                                                                                                                                                                                                                                                          |  |  |  |

| 28        | PSCL             | I/O  | I <sup>2</sup> C Clock Pin (only used for TI debug and test)<br>GROUND PIN IN APPLICATION                                                                                                                                                                                                                                                         |  |  |  |

| 29        | nCHG_STAT        | 0    | Open-drain Output, Charge Status Indication<br>CONNECT TO GROUND IF FUNCTION IS NOT USED                                                                                                                                                                                                                                                          |  |  |  |

| 30        | CHG_EN           | I    | Charger Enable Input from an MCU, High = Boost Enabled                                                                                                                                                                                                                                                                                            |  |  |  |

| 31        | SLEEP            | I/O  | Sleep Enable Input from an MCU (edge triggered, only for system shutdown)                                                                                                                                                                                                                                                                         |  |  |  |

| 32        | HBL1             | I    | H-Bridge Input 1 for Left LC Shutter                                                                                                                                                                                                                                                                                                              |  |  |  |

| MISCELLAN | EOUS AND PACKAG  | E    |                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 14, 17    | N/C              | —    | All N/C should be connected to the main system ground.                                                                                                                                                                                                                                                                                            |  |  |  |

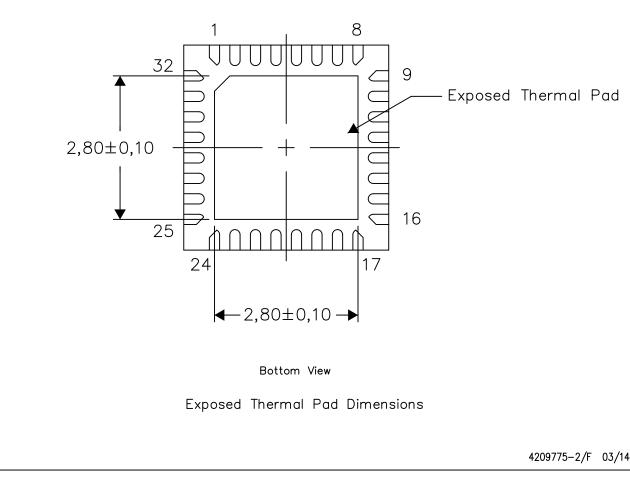

| 33        | Thermal PAD      | _    | There is an internal electrical connection between the exposed thermal pad and the AGND ground pin of the device. The thermal pad must be connected to the same potential as the AGND pin on the printed circuit board. Do not use the thermal pad as the primary ground input for the device. AGND pin must be connected to ground at all times. |  |  |  |

www.ti.com

# 4 Specifications

## 4.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)(2)</sup>

|                  |                            |                                                                                                | MIN  | MAX | UNIT |

|------------------|----------------------------|------------------------------------------------------------------------------------------------|------|-----|------|

|                  |                            | xcept for VIN, BST_OUT, BST_SW, BST_FB, VLDO, LCLP, D, DGND, and PGNDBST) with respect to AGND | -0.3 | 7   | V    |

|                  | VIN with respect to AGND   |                                                                                                | -0.3 | 28  | V    |

|                  | BST_OUT, BST_SW, LCL       | P, LCLN, LCRP, and LCRN with respect to PGNDBST                                                | -0.3 | 18  | V    |

|                  | BST_FB with respect to PO  | GNDBST, VLDO with respect to DGND                                                              | -0.3 | 3.6 | V    |

| T <sub>A</sub>   | Operating free-air tempera | ture                                                                                           | 0    | 60  | °C   |

| -                |                            | Electrical characteristics ensured                                                             | 0    | 85  | - °C |

| IJ               | Junction temperature       | Functionality ensured <sup>(3)</sup>                                                           | 0    | 105 |      |

| T <sub>stg</sub> | Storage temperature        |                                                                                                | -55  | 150 | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to V<sub>SS</sub>, unless otherwise noted.

(3) Device has a thermal shutdown feature implemented that shuts down at 105°C

# 4.2 ESD Ratings

|                  |                         |                                                                  | VALUE | UNIT |

|------------------|-------------------------|------------------------------------------------------------------|-------|------|

|                  |                         | Human Body Model (HBM), per ANSI/ESDA/JEDEC JS001 <sup>(1)</sup> | ±1000 |      |

| V <sub>ESD</sub> | Electrostatic discharge | Charged Device Model (CDM),<br>per JESD22-C101 <sup>(2)</sup>    | ±250  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 4.3 Power-On Hours (POH)

See (1)(2)(3)(4)

| OPERATING<br>CONDITION | NOMINAL CVDD VOLTAGE (V) | JUNCTION TEMPERATURE (T <sub>j</sub> ) | LIFETIME POH <sup>(5)</sup> |

|------------------------|--------------------------|----------------------------------------|-----------------------------|

| 100% OPP               | 1.1                      | –40 to 105 °C                          | 100 K                       |

| 120% OPP               | 1.2                      | –40 to 105 °C                          | 100 K                       |

| 166% OPP               | 1.35                     | –40 to 105 °C                          | 49 K                        |

(1) This information is provided solely for your convenience and does not extend or modify the warranty provided under TI's standard terms and conditions for TI semiconductor products.

(2) To avoid significant degradation, the device power-on hours (POH) must be limited to those specified in this table.

(3) Logic functions and parameter values are not assured out of the range specified in the recommended operating conditions.

(4) Notations in this table cannot be deemed a warranty or deemed to extend or modify the warranty under TI's standard terms and conditions for TI semiconductor products.

(5) POH represent device operation under the specified nominal conditions continuously for the duration of the calculated lifetime.

## 4.4 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                    |                                                                                                      | MIN | NOM | MAX               | UNIT |

|------------------------------------|------------------------------------------------------------------------------------------------------|-----|-----|-------------------|------|

| CHARGER / POV                      | VER PATH                                                                                             |     |     |                   |      |

| V <sub>VIN</sub>                   | Voltage at charger input pin                                                                         | 3.7 |     | 28 <sup>(1)</sup> | V    |

| I <sub>VIN</sub>                   | Input current at VIN pin                                                                             |     |     | 200               | mA   |

| C <sub>VIN</sub>                   | Capacitor on VIN pin                                                                                 | 0.1 | 2.2 | 10                | μF   |

| L <sub>VIN</sub>                   | Inductance at VIN pin                                                                                | 0   |     | 2                 | μH   |

| V <sub>SYS</sub>                   | Voltage at SYS pin                                                                                   | 2.5 |     | 6.4               | V    |

| I <sub>SYS(OUT)</sub>              | Output current at SYS pin                                                                            |     |     | 100               | mA   |

| C <sub>SYS</sub>                   | Capacitor on SYS pin                                                                                 | 0.1 | 4.7 | 10                | μF   |

| V <sub>BAT</sub>                   | Voltage at BAT pin                                                                                   | 2.5 |     | 6.4               | V    |

| C <sub>BAT</sub>                   | Capacitor on BAT pin                                                                                 | 4.7 |     | 10                | μF   |

| R <sub>EXT(nCHG_STAT)</sub>        | Resistor connected to nCHG_STAT pin to limit current into pin                                        | 320 |     |                   | Ω    |

| BOOST CONVER                       | TER / H-BRIDGE SWITCHES                                                                              |     |     | ·                 |      |

| V <sub>IN(BST_SW)</sub>            | Input voltage for boost converter                                                                    | 2.5 |     | 6.5               | V    |

| V <sub>BST_OUT</sub>               | Output voltage for boost converter                                                                   | 8   |     | 16                | V    |

| C <sub>BST_OUT</sub>               | Boost output capacitor                                                                               | 3.3 | 4.7 | 10                | μF   |

| L <sub>BST_SW</sub> <sup>(2)</sup> | Inductor connected between SYS and BST_SW pins                                                       | 4.7 |     | 10 <sup>(3)</sup> | μH   |

| LDO                                |                                                                                                      |     |     | ·                 |      |

| C <sub>VLDO</sub>                  | External decoupling cap on pin VLDO                                                                  | 1   |     | 10                | μF   |

| POWER MANAG                        | EMENT CORE CONTROL (LOGIC LEVELS FOR GPIOS)                                                          |     |     |                   |      |

| V <sub>IL(PMIC)</sub>              | GPIO low level (BST_EN, CHG_EN, SW_SEL, VLDO_SET and to switch H-Bridge inputs to a low, 0, level)   |     |     | 0.4               | V    |

| V <sub>IH(PMIC)</sub>              | GPIO high level (BST_EN, CHG_EN, SW_SEL, VLDO_SET and to switch H-Bridge inputs to a high, 1, level) | 1.2 |     |                   | V    |

(1) VIN pin has 28 V ESD protection

(2) See Section 5.3.4 for information on boost converter inductor selection.

(3) Design optimized for boost operation with 10 µH inductor

#### 4.5 Thermal Information

|                       |                                                             | TPS65735   |      |

|-----------------------|-------------------------------------------------------------|------------|------|

|                       | THERMAL METRIC                                              | RSN (WQFN) | UNIT |

|                       |                                                             | 32 PINS    |      |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance <sup>(1)</sup>       | 38.9       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance <sup>(2)</sup>    | 26.5       | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance <sup>(3)</sup>         | 9.8        | °C/W |

| ΨJT                   | Junction-to-top characterization parameter <sup>(4)</sup>   | 0.3        | °C/W |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter <sup>(5)</sup> | 9.8        | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance <sup>(6)</sup> | 3.5        | °C/W |

(1) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

(2) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDECstandard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

(3) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

(4) The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining R<sub>0JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

(5) The junction-to-board characterization parameter,  $\psi_{JB}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining R<sub>0JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

(6) The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

# 4.6 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                            | PARAMETER                                                                                             | TEST CONDITIONS                                                                                                                 | MIN                        | TYP                                                 | MAX                        | UNIT |

|----------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------|----------------------------|------|

| BATTERY CHAP               | RGER POWER PATH                                                                                       |                                                                                                                                 |                            |                                                     |                            |      |

| V <sub>UVLO(VIN)</sub>     | Undervoltage lockout at power path input, VIN pin                                                     | $V_{VIN}: 0 V \rightarrow 4 V$                                                                                                  | 3.2                        | 3.3                                                 | 3.45                       | V    |

| V <sub>HYS-UVLO(VIN)</sub> | Hysteresis on UVLO at power<br>path input, VIN pin                                                    | $V_{VIN}$ : 4 V $\rightarrow$ 0 V                                                                                               | 200                        |                                                     | 300                        | mV   |

| V <sub>IN-DT</sub>         | Input power detection threshold                                                                       | Input power detected if: $(V_{VIN} > V_{BAT} + V_{IN-DT})$ ;<br>$V_{BAT} = 3.6 V$<br>$V_{VIN}$ : 3.5 V $\rightarrow$ 4 V        | 40                         |                                                     | 140                        | mV   |

| V <sub>HYS-INDT</sub>      | Hysteresis on V <sub>IN-DT</sub>                                                                      | $V_{BAT} = 3.6 V$<br>$V_{VIN}$ : 4 V $\rightarrow$ 3.5 V                                                                        | 20                         |                                                     |                            | mV   |

| V <sub>OVP</sub>           | Input over-voltage protection threshold                                                               | $V_{VIN}$ : 5 V $\rightarrow$ 7 V                                                                                               | 6.4                        | 6.6                                                 | 6.8                        | V    |

| V <sub>HYS-OVP</sub>       | Hysteresis on OVP                                                                                     | $V_{VIN}$ : 11 V $\rightarrow$ 5 V                                                                                              |                            | 105                                                 |                            | mV   |

| V <sub>DO(VIN-SYS)</sub>   | VIN pin to SYS pin dropout<br>voltage<br>V <sub>VIN</sub> – V <sub>SYS</sub>                          | $\begin{array}{l} I_{SYS} = 150 \text{ mA} \mbox{ (including } I_{BAT}) \\ V_{VIN} = 4.35 \ V \\ V_{BAT} = 3.6 \ V \end{array}$ |                            |                                                     | 350                        | mV   |

| V <sub>DO(BAT-SYS)</sub>   | BAT pin to SYS pin dropout<br>voltage<br>V <sub>BAT</sub> – V <sub>SYS</sub>                          | I <sub>SYS</sub> = 100 mA<br>V <sub>VIN</sub> = 0 V<br>V <sub>BAT</sub> > 3 V                                                   |                            |                                                     | 150                        | mV   |

| I <sub>VIN(MAX)</sub>      | Maximum power path input<br>current at pin VIN                                                        | $V_{VIN} = 5 V$                                                                                                                 |                            | 200                                                 |                            | mA   |

| V <sub>SUP(ENT)</sub>      | Enter battery supplement mode                                                                         |                                                                                                                                 |                            | V <sub>SYS</sub> ≤<br>(V <sub>BAT</sub> - 40<br>mV) |                            | V    |

| V <sub>SUP(EXIT)</sub>     | Exit battery supplement mode                                                                          |                                                                                                                                 |                            | V <sub>SYS</sub> ≥<br>(V <sub>BAT</sub> - 20<br>mV) |                            | V    |

| V <sub>SUP(SC)</sub>       | Output short-circuit limit in<br>supplement mode                                                      |                                                                                                                                 |                            | 250                                                 |                            | mV   |

| V <sub>O(SC)</sub>         | Output short-circuit detection threshold, power-on                                                    |                                                                                                                                 |                            | 0.9                                                 |                            | V    |

| BATTERY CHAP               | RGER                                                                                                  |                                                                                                                                 |                            |                                                     |                            |      |

| I <sub>CC</sub>            | Active supply current into VIN pin                                                                    | $V_{VIN} = 5 V$<br>No load on SYS pin<br>$V_{BAT} > V_{BAT(REG)}$                                                               |                            |                                                     | 2                          | mA   |

| I <sub>BAT(SC)</sub>       | Source current for BAT pin<br>short-circuit detection                                                 |                                                                                                                                 |                            | 1                                                   |                            | mA   |

| V <sub>BAT(SC)</sub>       | BAT pin short-circuit detection threshold                                                             |                                                                                                                                 | 1.6                        | 1.8                                                 | 2.0                        | V    |

| V <sub>BAT(REG)</sub>      | Battery charger output voltage                                                                        |                                                                                                                                 | -1%                        | 4.20                                                | 1%                         | V    |

| V <sub>LOWV</sub>          | Pre-charge to fast-charge transition threshold                                                        |                                                                                                                                 | 2.9                        | 3.0                                                 | 3.1                        | V    |

| I <sub>СНG</sub>           | Charger fast charge current<br>range<br>I <sub>CHG</sub> = K <sub>ISET</sub> / R <sub>ISET</sub>      | $V_{VIN} = 5 V$<br>$V_{BAT(REG)} > V_{BAT} > V_{LOWV}$                                                                          | 5                          |                                                     | 100                        | mA   |

| K <sub>ISET</sub>          | Battery fast charge current set<br>factor<br>I <sub>CHG</sub> = K <sub>ISET</sub> / R <sub>ISET</sub> |                                                                                                                                 | -20%                       | 450                                                 | 20%                        | AΩ   |

| I <sub>PRECHG</sub>        | Pre-charge current                                                                                    |                                                                                                                                 | 0.07 ×<br>І <sub>СНG</sub> | 0.10 ×<br>I <sub>CHG</sub>                          | 0.15 ×<br>І <sub>СНG</sub> | mA   |

| I <sub>TERM</sub>          | Charge current value for termination detection threshold                                              | I <sub>CHG</sub> = 100 mA                                                                                                       | 7                          | 10                                                  | 15                         | mA   |

# **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted)

|                           | PARAMETER                                                    | TEST CONDITIONS                                                                                                                                      | MIN  | TYP                          | MAX  | UNIT |

|---------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------|------|------|

| V <sub>RCH</sub>          | Recharge detection threshold                                 | $V_{\text{BAT}}$ below nominal charger voltage, $V_{\text{BAT}(\text{REG})}$                                                                         | 55   | 100                          | 170  | mV   |

| BAT(DET)                  | Sink current for battery detection                           |                                                                                                                                                      |      | 1                            |      | mA   |

| t <sub>CHG</sub>          | Charge safety timer<br>(18000 seconds = 5 hours)             |                                                                                                                                                      |      | 18000                        |      | S    |

| t <sub>PRECHG</sub>       | Pre-charge timer<br>(1800 seconds = 30 minutes)              |                                                                                                                                                      |      | 1800                         |      | S    |

| V <sub>DPPM</sub>         | DPPM threshold                                               |                                                                                                                                                      |      | V <sub>BAT</sub> +<br>100 mV |      | V    |

| LEAK(nCHG)                | Leakage current for<br>nCHG_STAT pin                         | $V_{nCHG\_STAT} = 4.2 V$<br>CHG_EN = LOW (Charger disabled)                                                                                          |      |                              | 100  | nA   |

| R <sub>DSON(nCHG)</sub>   | On resistance for<br>nCHG_STAT MOSFET switch                 |                                                                                                                                                      |      | 20                           | 60   | Ω    |

| MAX(nCHG)                 | Maximum input current to<br>nCHG_STAT pin                    |                                                                                                                                                      |      |                              | 50   | mA   |

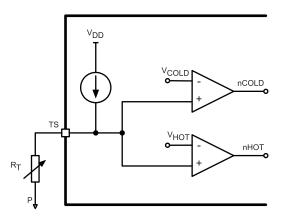

| BATTERY CHA               | RGER NTC MONITOR                                             |                                                                                                                                                      |      |                              |      |      |

| I <sub>TSBIAS</sub>       | TS pin bias current                                          |                                                                                                                                                      |      | 75                           |      | μA   |

| V <sub>COLD</sub>         | 0°C charge threshold for 10-<br>kΩ NTC<br>( $\beta$ = 3490)  |                                                                                                                                                      |      | 2100                         |      | mV   |

| V <sub>HYS(COLD)</sub>    | Low temperature threshold hysteresis                         | Battery charging and battery / NTC temperature increasing                                                                                            |      | 300                          |      | mV   |

| V <sub>HOT</sub>          | 50°C charge threshold for 10-<br>kΩ NTC<br>( $\beta$ = 3490) |                                                                                                                                                      |      | 300                          |      | mV   |

| V <sub>HYS(HOT)</sub>     | High temperature threshold<br>hysteresis                     | Battery charging and battery / NTC temperature decreasing                                                                                            |      | 30                           |      | mV   |

| BATTERY CHA               | RGER THERMAL REGULATION                                      |                                                                                                                                                      |      |                              | ·    |      |

| T <sub>J(REG_LOWER)</sub> | Charger lower thermal regulation limit                       |                                                                                                                                                      |      | 75                           |      | °C   |

| $T_{J(REG_UPPER)}$        | Charger upper thermal<br>regulation limit                    |                                                                                                                                                      |      | 95                           |      | °C   |

| T <sub>J(OFF)</sub>       | Charger thermal shutdown temperature                         |                                                                                                                                                      |      | 105                          |      | °C   |

| T <sub>J(OFF-HYS)</sub>   | Charger thermal shutdown<br>hysteresis                       |                                                                                                                                                      |      | 20                           |      | °C   |

| LDO                       |                                                              |                                                                                                                                                      |      |                              |      |      |

| I <sub>MAX(LDO)</sub>     | Maximum LDO output current, $V_{VLDO} = 2.2 V$               | V <sub>SYS</sub> = 4.2 V<br>V <sub>VIN</sub> = 0 V<br>VLDO_SET = 0 V                                                                                 | 30   |                              |      | mA   |

|                           | Maximum LDO output current, $V_{VLDO} = 3.0 V$               | V <sub>SYS</sub> = 4.2 V<br>V <sub>VIN</sub> = 0 V<br>VLDO_SET = V <sub>SYS</sub>                                                                    | 30   |                              |      | mA   |

| I <sub>SC(LDO)</sub>      | Short circuit current limit                                  |                                                                                                                                                      | 30   |                              | 100  | mA   |

| V <sub>VLDO</sub>         | LDO output voltage                                           | $VLDO\_SET = LOW$ $(VLDO\_SET pin connected to DGND)$ $3.7 V \le V_{VIN} \le 6.5 V$ $I_{LOAD(LDO)} = -10 mA$                                         | 2.13 | 2.2                          | 2.27 | V    |

| V <sub>VLDO</sub>         | LDO output voltage                                           | $\begin{array}{l} VLDO\_SET = HIGH \\ (V_{VLDO\_SET} = V_{SYS}) \\ 3.7 \ V \leq V_{VIN} \leq 6.5 \ V \\ I_{LOAD(LDO)} = -10 \ \text{mA} \end{array}$ | 2.91 | 3.0                          | 3.09 | V    |

| V <sub>DO(LDO)</sub>      | LDO Dropout voltage                                          | $V_{VIN}$ - $V_{LDO}$ when in dropout<br>$I_{LOAD(LDO)} = -10 \text{ mA}$                                                                            |      |                              | 200  | mV   |

Copyright © 2011–2016, Texas Instruments Incorporated

# **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted)

|                            | PARAMETER                                                                                                              | TEST CONDITIONS                                                                                                        | MIN  | TYP  | MAX  | UNIT |

|----------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

|                            | Line regulation                                                                                                        | $3.7 \text{ V} \le V_{VIN} \le 6.5 \text{ V}$<br>$I_{LOAD(LDO)} = -10 \text{ mA}$                                      | -1%  |      | 1%   |      |

|                            | Load regulation                                                                                                        | $V_{VIN} = 3.5 V$<br>0.1 mA ≤ I <sub>LOAD(LDO)</sub> ≤ -10 mA                                                          | -2%  |      | 2%   |      |

| PSRR                       | Power supply rejection ratio                                                                                           | at 20 KHz, $I_{LOAD(LDO)}$ = 10 mA $V_{DO(LDO)}$ = 0.5 V $C_{VLDO}$ = 10 $\mu F$                                       |      | 45   |      | dB   |

| BOOST CONVE                | RTER                                                                                                                   |                                                                                                                        |      |      |      |      |

| I <sub>Q(BST)</sub>        | Boost operating quiescent current                                                                                      | Boost Enabled, BST_EN = High<br>$I_{OUT(BST)} = 0 \text{ mA}$<br>(boost is not switching)<br>$V_{BAT} = 3.6 \text{ V}$ |      | 2    | 4.5  | μA   |

| R <sub>DSON(BST)</sub>     | Boost MOSFET switch on-<br>resistance                                                                                  | $V_{IN(BST)} = 2.5 V$<br>$I_{SW(MAIN)} = 200 mA$                                                                       |      | 0.8  | 1.2  | Ω    |

| I <sub>LKG(BST_SW)</sub>   | Leakage into BST_SW pin<br>(includes leakage into analog<br>h-bridge switches)                                         | BST_EN signal = LOW (Boost<br>disabled)<br>V <sub>BST_SW</sub> = 4.2 V<br>No load on BST_OUT pin                       |      |      | 90   | nA   |

| I <sub>SWLIM(BST)</sub>    | Boost MOSFET switch current<br>limit                                                                                   |                                                                                                                        | 100  | 150  | 200  | mA   |

| V <sub>DIODE(BST)</sub>    | Voltage across integrated<br>boost diode during normal<br>operation                                                    | BST_EN signal = HIGH<br>V <sub>BST_SW</sub> = 16.0 V<br>I <sub>BST_OUT</sub> = -2 mA                                   |      |      | 1.0  | V    |

| V <sub>REF(BST)</sub>      | Boost reference voltage on<br>BST_FB pin                                                                               |                                                                                                                        | 1.17 | 1.2  | 1.23 | V    |

| V <sub>REFHYS(BST)</sub>   | Boost reference voltage<br>hysteresis on BST_FB pin                                                                    |                                                                                                                        | 2%   | 2.5% | 3.2% |      |

| T <sub>ON(BST)</sub>       | Maximum on time detection threshold                                                                                    |                                                                                                                        | 5    | 6.5  | 8    | μs   |

| T <sub>OFF(BST)</sub>      | Minimum off time detection threshold                                                                                   |                                                                                                                        | 1.4  | 1.75 | 2.1  | μs   |

| T <sub>SHUT(BST)</sub>     | Boost thermal shutdown threshold                                                                                       |                                                                                                                        |      | 105  |      | °C   |

| T <sub>SHUT-HYS(BST)</sub> | Boost thermal shutdown threshold hysteresis                                                                            |                                                                                                                        |      | 20   |      | °C   |

| FULL H-BRIDGE              | E ANALOG SWITCHES                                                                                                      |                                                                                                                        | 1    |      |      |      |

| I <sub>Q(HSW)</sub>        | Operating quiescent current<br>for h-bridge switches                                                                   |                                                                                                                        |      |      | 5    | μΑ   |

| R <sub>DSON(HSW)</sub>     | H-bridge switches on resistance                                                                                        |                                                                                                                        |      | 20   | 40   | Ω    |

| T <sub>DELAY(HSW-H)</sub>  | H-bridge switch propagation<br>delay, input switched from low<br>to high state.                                        | $V_{HBxy} = 0 \ V \rightarrow V_{VLDO}$                                                                                |      | 100  |      | ns   |

| T <sub>DELAY(HSW-L)</sub>  | H-bridge switch propagation<br>delay, input switched from<br>high to low state.                                        | $V_{HBxy} = V_{VLDO} \rightarrow 0 \ V$                                                                                |      | 100  |      | ns   |

| POWER MANAG                | GEMENT CORE CONTROLLER                                                                                                 |                                                                                                                        | ·    |      |      |      |

| V <sub>IL(PMIC)</sub>      | Low logic level for logic<br>signals on power management<br>core<br>(BST_EN, CHG_EN, SLEEP,<br>HBR1, HBR2, HBL1, HBL2) | IO logic level decreasing: $V_{SYS} \rightarrow 0 V$<br>$I_{IN} = 1 mA$                                                |      |      | 0.4  | V    |

| VIH(PMIC)                  | High logic level for signals on<br>power management core<br>(BST_EN, CHG_EN, SLEEP,<br>HBR1, HBR2, HBL1, HBL2)         | IO logic level increasing:<br>0 V $\rightarrow$ V <sub>SYS</sub><br>I <sub>IN</sub> = 1 mA                             | 1.2  |      |      | V    |

Copyright © 2011–2016, Texas Instruments Incorporated

## **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted)

|                            | PARAMETER                                      | TEST CONDITIONS                                       | MIN | TYP  | MAX  | UNIT |

|----------------------------|------------------------------------------------|-------------------------------------------------------|-----|------|------|------|

| V <sub>GOOD(LDO)</sub>     | Power fault detection threshold                | V <sub>VLDO</sub> decreasing                          |     |      | 1.96 | V    |

| V <sub>GOOD_HYS(LDO)</sub> | Power fault detection<br>hysteresis            | V <sub>VLDO</sub> increasing                          |     | 50   |      | mV   |

| VBATCOMP                   | COMP pin voltage (scaled down battery voltage) | V <sub>BAT</sub> = 4.2 V<br>V <sub>VLDO</sub> = 2.2 V |     | 1.85 |      |      |

|                            |                                                | V <sub>BAT</sub> = 2.5 V<br>V <sub>VLDO</sub> = 2.2 V |     | 1.10 |      | V    |

|                            |                                                | V <sub>BAT</sub> = 4.2 V<br>V <sub>VLDO</sub> = 3.0 V |     | 1.90 |      | v    |

|                            |                                                | V <sub>BAT</sub> = 3.3 V<br>V <sub>VLDO</sub> = 3.0 V |     | 1.50 |      |      |

## 4.7 Quiescent Current

over operating free-air temperature range (unless otherwise noted)

|                        | PARAMETER                                              | TEST CONDITIONS                                                                                                                                                                  | MIN | TYP | MAX  | UNIT |

|------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| I <sub>Q(SLEEP)</sub>  | Power management core quiescent current in sleep mode  | at 25° C<br>$V_{BAT} = 3.6 V$<br>$V_{VIN} = 0 V$<br>No load on LDO<br>CHG_EN, BST_EN grounded<br>BST_FB = 300 mV<br>Power management core in sleep<br>mode / device 'off'        |     | 8.6 | 10.5 | μA   |

| I <sub>Q(ACTIVE)</sub> | Power management core quiescent current in active mode | at 25° C<br>$V_{BAT} = 3.6 V$<br>$V_{VIN} = 0 V$<br>Boost enabled but not switching, H-<br>bridge in grounded state<br>No load on LDO<br>Power management core in active<br>mode |     | 39  | 53.5 | μA   |

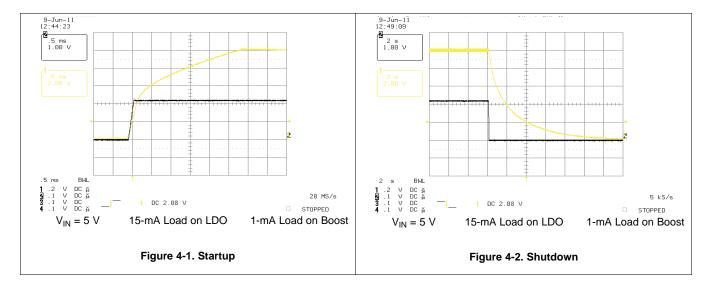

## 4.8 Typical Characteristics

## 5 Detailed Description

#### 5.1 Overview

The TPS65735 integrates a linear charger and a Boost Converter to create a PMIC for active shutter 3D glasses.

## 5.2 Functional Block Diagram

Figure 5-1. TPS65735 Simplified Functional Block Diagram

## 5.3 Feature Description

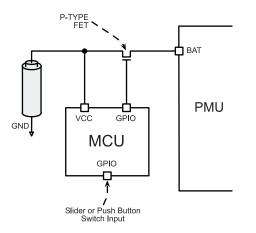

#### 5.3.1 System Operation

The system must complete the power up routine before it enters normal operating mode. The specific system operation depends on the setting defined by the state of the SW\_SEL pin. The details of the system operation for each configuration of the SW\_SEL pin are contained in this section.

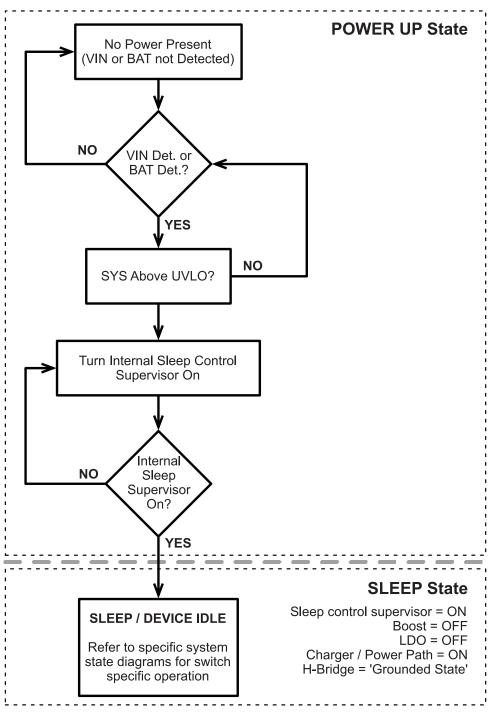

#### 5.3.1.1 System Power Up

Figure 5-2. System Power Up State Diagram

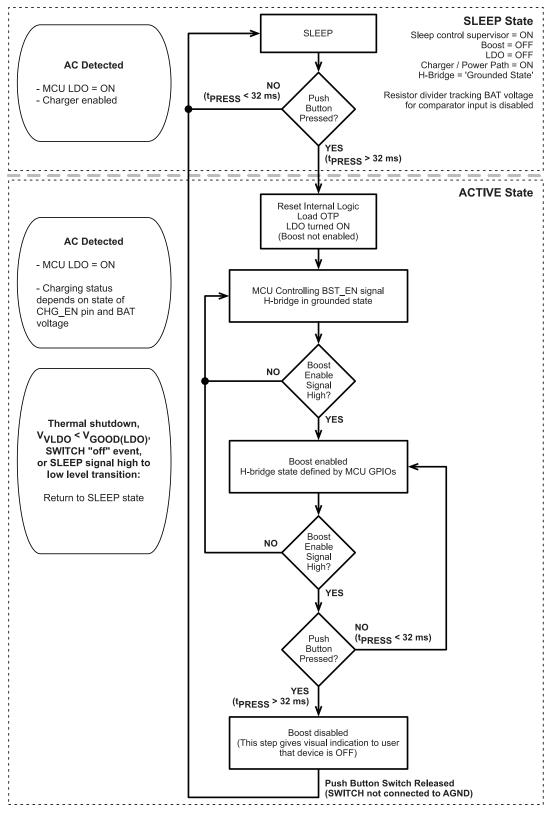

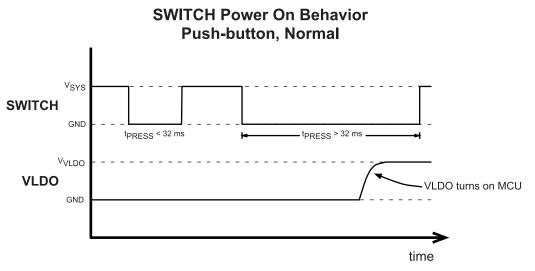

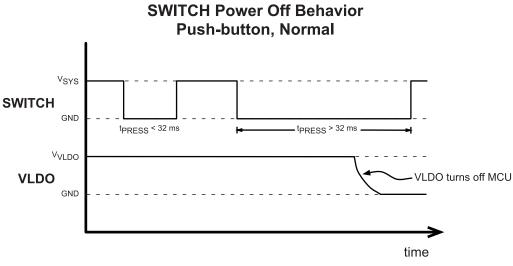

#### 5.3.1.2 System Operation Using Push Button Switch

Figure 5-3. Push Button State Diagram

NSTRUMENTS www.ti.com

ÈXAS

## 5.3.2 Linear Charger Operation

This device has an integrated Li-Ion battery charger and system power path management feature targeted at space-limited portable applications. The architecture powers the system while simultaneously and independently charging the battery. This feature reduces the number of charge and discharge cycles on the battery, allows for proper charge termination, and enables the system to run with a defective or absent battery pack. It also allows instant system turn-on even with a totally discharged battery.

The input power source for charging the battery and running the system can be an AC adapter or USB port connected to the VIN pin as long as the input meets the device operating conditions outlined in this datasheet. The power-path management feature automatically reduces the charging current if the system load increases. Note that the charger input, VIN, has voltage protection up to 28 V.

#### 5.3.2.1 Battery and TS Detection

To detect and determine between a good or damaged battery, the device checks for a short circuit on the BAT pin by sourcing  $I_{BAT(SC)}$  to the battery and monitoring the voltage on the BAT pin. While sourcing this current if the BAT pin voltage exceeds  $V_{BAT(SC)}$ , a battery has been detected. If the voltage stays below the  $V_{BAT(SC)}$  level, the battery is presumed to be damaged and not safe to charge.

The device will also check for the presence of a 10-k $\Omega$  NTC thermistor attached to the TS pin of the device. The check for the NTC thermistor on the TS pin is done much like the battery detection feature described previously. The voltage on the TS pin is compared against a defined level and if it is found to be above the threshold, the NTC thermistor is assumed to be disconnected or not used in the system. To reduce the system quiescent current, the NTC thermistor temperature sensing function is only enabled when the device is charging and when the thermistor has been detected.

Figure 5-5. Thermistor Detection and Circuit

#### 5.3.2.2 Battery Charging

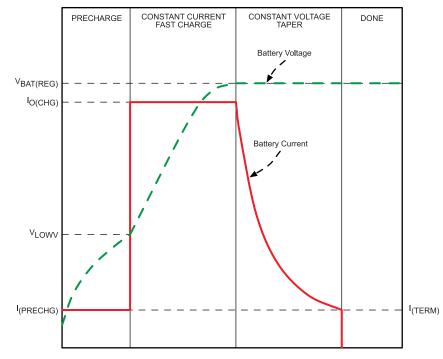

The battery is charged in three phases: conditioning pre-charge, constant-current fast charge (current regulation), and a constant-voltage tapering (voltage regulation). In all charge phases, an internal control loop monitors the IC junction temperature and reduces the charge current if an internal temperature threshold is exceeded. Figure 5-6 shows what happens in each of the three charge phases:

Figure 5-6. Battery Charge Phases

In the pre-charge phase, the battery is charged with the pre-charge current that is scaled to be 10% of the fast-charge current set by the resistor connected to the ISET pin. Once the battery voltage crosses the  $V_{LOWV}$  threshold, the battery is charged with the fast-charge current ( $I_{CHG}$ ). As the battery voltage reaches  $V_{BAT(REG)}$ , the battery is held at a constant voltage of  $V_{BAT(REG)}$  and the charge current tapers off as the battery approaches full charge. When the battery current reaches  $I_{TERM}$ , the charger indicates charging is done by making the nCHG\_STAT pin high impedance. Note that termination detection is disabled whenever the charge rate is reduced from the set point because of the actions of the thermal loop, the DPM loop, or the  $V_{IN(LOWV)}$  loop.

#### 5.3.2.2.1 Pre-charge

The value for the pre-charge current is set to be 10% of the charge current that is set by the external resistor,  $R_{ISET}$ . Pre-charge current is scaled to lower currents when the charger is in thermal regulation.

#### 5.3.2.2.2 Charge Termination

In the fast charge state, once  $V_{BAT} \ge V_{BAT(REG)}$ , the charger enters constant voltage mode. In constant voltage mode, the charge current will taper until termination when the charge current falls below the  $I_{(TERM)}$  threshold (typically 10% of the programmed fast charge current). Termination current is not scaled when the charger is in thermal regulation. When the charging is terminated, the nCHG\_STAT pin will be high impedance (effectively turning off any LED that is connected to this pin).

## 5.3.2.2.3 Recharge

Once a charge cycle is complete and termination is reached, the battery voltage is monitored. If  $V_{BAT} < V_{BAT(REG)} - V_{RCH}$ , the device determines if the battery has been removed. If the battery is still present, then the recharge cycle begins and will end when  $V_{BAT} \ge V_{BAT(REG)}$ .

#### 5.3.2.2.4 Charge Timers

The charger in this device has internal safety timers for the pre-charge and fast charge phases to prevent potential damage to either the battery or the system. The default values for these timers are found as follows: Pre-charge timer = 0.5 hours (30 minutes) and Fast charge timer = 5 hours (300 minutes).

During the fast charge phase, the following events may increase the timer durations:

- 1. The system load current activates the DPM loop which reduces the available charging current

- 2. The input current is reduced because the input voltage has fallen to VIN(LOW)

- 3. The device has entered thermal regulation because the IC junction temperature has exceeded T<sub>J(REG)</sub>

During each of these events, the internal timers are slowed down proportionately to the reduction in charging current.

If the pre-charge timer expires before the battery voltage reaches  $V_{\text{LOWV}}$ , the charger indicates a fault condition.

#### 5.3.2.3 Charger Status (nCHG\_STAT Pin)

The nCHG\_STAT pin is used to indicate the charger status by an externally connected resistor and LED circuit. The pin is an open drain input and the internal switch is controlled by the logic inside of the charger. This pin may also be connected to a GPIO of the system MCU to indicate charging status. The table below details the status of the nCHG\_STAT pin for various operating states of the charger.

| CHARGING STATUS                               | nCHG_STAT FET / LED |

|-----------------------------------------------|---------------------|

| Pre-charge / Fast Charge / Charge Termination | ON                  |

| Recharge                                      | OFF                 |

| OVP                                           | OFF                 |

| SLEEP                                         | OFF                 |

#### Table 5-1. nCHG\_STAT Functionality

#### 5.3.3 LDO Operation

The power management core has a low dropout linear regulator (LDO) with variable output voltage capability. This LDO is used for supplying the microcontroller and may be used to supply either an external IR or RF module, depending on system requirements. The LDO can supply a continuous current of up to 30 mA.

The output voltage ( $V_{VLDO}$ ) of the LDO is set by the state of the VLDO\_SET pin. See Table 5-2 for details on setting the LDO output voltage.

| VLDO_SET STATE                    | VLDO OUTPUT VOLTAGE<br>(V <sub>VLDO</sub> ) |

|-----------------------------------|---------------------------------------------|

| Low (VLDO_SET < $V_{IL(PMIC)}$ )  | 2.2 V                                       |

| High (VLDO_SET > $V_{IH(PMIC)}$ ) | 3.0 V                                       |

#### Table 5-2. VLDO\_SET Functionality

#### 5.3.3.1 LDO Internal Current Limit

The internal current limit feature helps protect the LDO regulator during fault conditions. During current limit, the output sources a fixed amount of current, defined in the Electrical Characteristics table. The voltage on the output in this stage can not be regulated and will be  $V_{OUT} = I_{LIMIT} \times R_{LOAD}$ . The pass transistor integrated into the LDO will dissipate power,  $(V_{IN} - V_{OUT}) \times I_{LIMIT}$ , until the device enters thermal shutdown. In thermal shutdown the device will enter the *SLEEP / POWER OFF* state which means that the LDO will then be disabled and shut off.

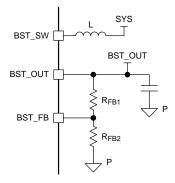

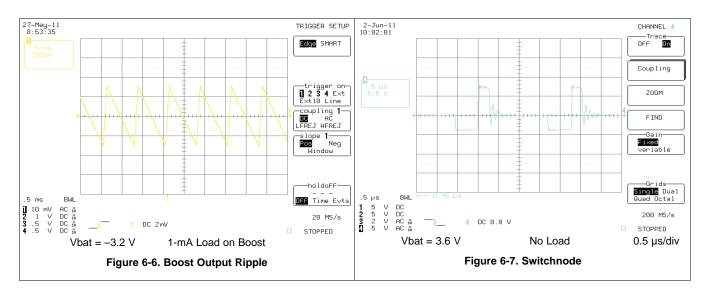

## 5.3.4 Boost Converter Operation

The boost converter in this device is designed for active shutter 3D glasses. This load is typically a light load where the average current is 2 mA or lower and the peak current out of a battery is limited in operation. This asynchronous boost converter operates with a minimum off time / maximum on time for the integrated low side switch, these values are specified in the Electrical Characteristics table of this datasheet.

The peak output voltage from the boost converter is adjustable and set by using an external resistor divider connected between BST\_OUT pin, BST\_FB pin, and ground. The peak output voltage is set by choosing resistors for the feedback network such that the voltage on the BST\_FB pin is  $V_{\text{REF(BST)}} = 1.2 \text{ V}$ . See Section 6.2.1.2.2 for more information on calculating resistance values for this feedback network.

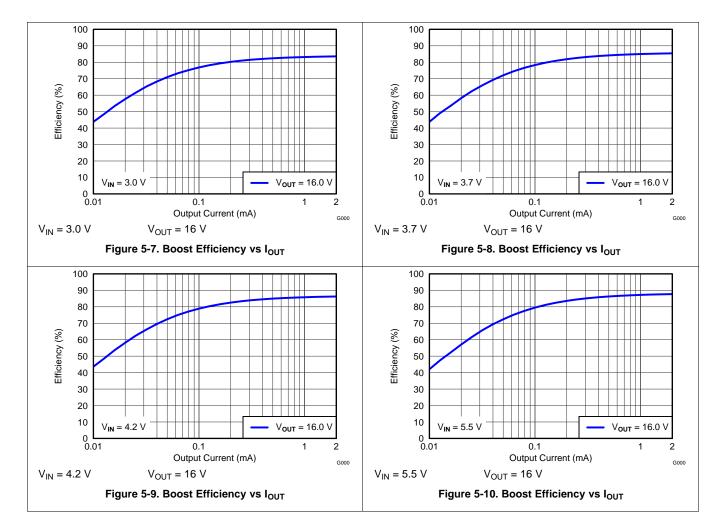

The efficiency curves for various input voltages over the typical 3D glasses load range (2 mA and lower) are shown below. All curves are for a target  $V_{OUT}$  of 16 V. For output voltages less than 16 V, a higher efficiency at each operating input voltage should be expected. Note that efficiency is dependent upon the external boost feedback network resistance, the inductor used, and the type of load connected.

#### 5.3.4.1 Boost Thermal Shutdown

An internal thermal shutdown mode is implemented in the boost converter that shuts down the device if the typical junction temperature of  $105^{\circ}$ C is exceeded. If the device is in thermal shutdown mode, the main switch of the boost is open and the device enters the *SLEEP / POWER OFF* state.

#### 5.3.4.2 Boost Load Disconnect

When the boost is disabled (BST\_EN = LOW), the H-bridge is automatically placed into the OFF state. In the OFF state the high side H-bridge switches are open and the low side switches of the H-bridge are closed. The OFF state grounds and discharges the load, potentially prolonging the life of the LC shutters by eliminating any DC content (see Section 5.3.5.1 for more information regarding the H-bridge states). The disconnection of the load is done with the H-Bridge and can be seen in the next figure (Figure 5-11).

Figure 5-11. Boost Load Disconnect

An advantage to this topology for disconnecting the load is that the boost output capacitor is charged to approximately the SYS voltage level, specifically  $V_{SYS}$  -  $V_{DIODE(BST)}$ , when the boost is disabled. This design ensures that there is not a large in-rush current into the boost output capacitor when the boost is enabled. The boost operation efficiency is also increased because there is no load disconnect switch in the boost output path. A load disconnect switch would decrease efficiency because of the resistance that it would introduce.

#### 5.3.5 Full H-Bridge Analog Switches

The TPS65735 has two integrated full H-bridge analog switches that can be connected to GPIOs of a host microcontroller. There is an internal level shifter that manages the input signals to the H-Bridge switches.

#### 5.3.5.1 H-Bridge Switch Control

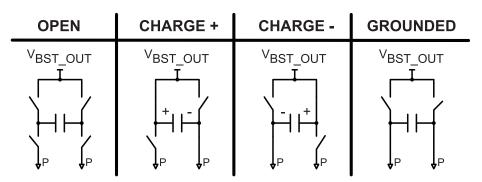

The H-Bridge switches are controlled by an external microcontroller for system operation - specifically to control charge polarity on the LCD shutters. Depending on the state of the signals from the microcontroller, the H-Bridge will be put into 4 different states. These states are:

- **OPEN**: All Switches Opened

- CHARGE+: Boost Output Voltage Present on Pins LCLP or LCRP

- CHARGE-: Boost Output Voltage Present on Pins LCLN or LCRN

- **GROUNDED**: High Side Switches are Opened and Low Side Switches are Closed

If CHARGE+ state is followed by the CHARGE- state, the voltage across the capacitor connected to the H-Bridge output terminals will be reversed. The system automatically switches to the GROUNDED state when the boost is disabled by the BST\_EN pin - for more details see Section 5.3.1.

| HBx2 [HBL2 & HBR2] | HBx1 [HBL1 & HBR1] | H-Bridge<br>STATE |

|--------------------|--------------------|-------------------|

| 0                  | 0                  | OPEN              |

| 0                  | 1                  | CHARGE +          |

| 1                  | 0                  | CHARGE -          |

| 1                  | 1                  | GROUNDED          |

Table 5-3. H-Bridge States from Inputs

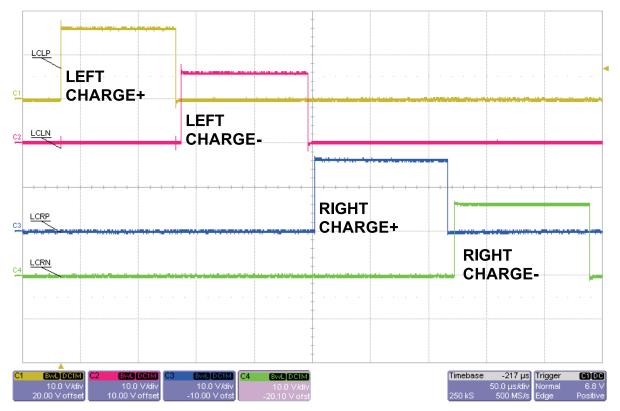

Figure 5-12. H-Bridge States

Figure 5-13. H-Bridge States from Oscilloscope

## 5.3.6 Power Management Core Control

Various functions of the power management core can be controlled by GPIOs of an external MCU or by setting the default state by connecting these function pins to a logic high or low level on the PCB.

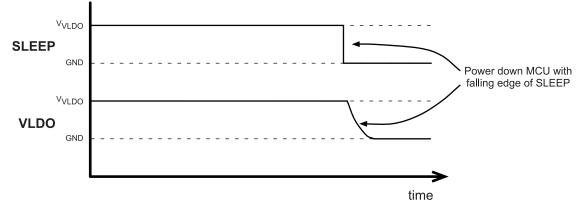

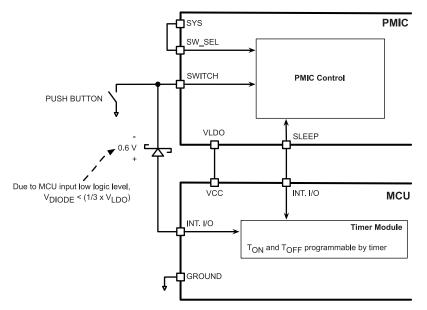

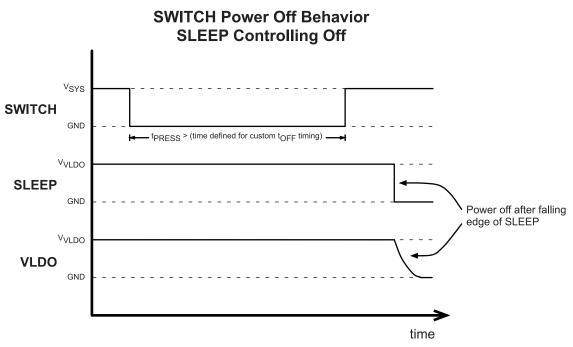

#### 5.3.6.1 SLEEP / Power Control Pin Function

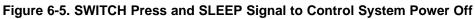

The internal SLEEP signal between the power management device and the MSP430 can be used to control the power down behavior of the device. This has multiple practical applications such as a watchdog implementation for the communication between the sender (TV) and the receiver (3D glasses) or different required system on and off times; typically when the push-button press timing for an off event is a few seconds in length, programmable by software in the system MCU.

If there is a requirement that the push-button press for system on and off events are different, the SLEEP signal must be set to a logic high value ( $V_{SLEEP} > V_{IH(PMIC)}$ ) upon system startup. This implementation allows the device to power down the system on the falling edge of the SLEEP signal (when:  $V_{SLEEP} < V_{IL(PMIC)}$ ).

Figure 5-14. SLEEP Signal to Force System Power Off

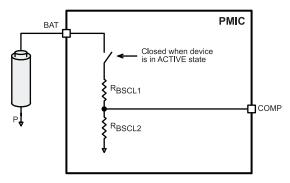

## 5.3.6.2 COMP Pin Functionality

The COMP pin is used to output a scaled down voltage level related to the battery voltage for input to a comparator of a microcontroller. Applications for this COMP feature could be to generate an interrupt on the microcontroller when battery voltage drops under a threshold and the device can then be shut down or indicate to the end user with an LED that the battery requires charging.

Figure 5-15. COMP Pin Internal Connection

# Table 5-4. Scaling Resistors for COMP Pin Function $(V_{VLDO} = 2.2 \text{ V})$

| SCALING RESISTORS FOR<br>COMP PIN FUNCTION | VALUE   |

|--------------------------------------------|---------|

| R <sub>BSCL1</sub>                         | 3.0 MΩ  |

| R <sub>BSCL2</sub>                         | 2.36 ΜΩ |

# Table 5-5. Scaling Resistors for COMP Pin Function ( $V_{VLDO} = 3.0 \text{ V}$ )

| SCALING RESISTORS FOR<br>COMP PIN FUNCTION | VALUE   |

|--------------------------------------------|---------|

| R <sub>BSCL1</sub>                         | 3.0 ΜΩ  |

| R <sub>BSCL2</sub>                         | 2.48 ΜΩ |

Using the designed values in Table 5-4 or Table 5-5, the voltage on the COMP pin will be:  $V_{COMP} = 0.5 \times V_{VLDO} + 300 \text{ mV}$ . This ensures that the COMP pin voltage will be close to half of the LDO output voltage plus the LDO dropout voltage of the device. The COMP pin can also be used as the input to an ADC channel of an external microcontroller if additional accuracy or functionality is desired over a simple comparison.

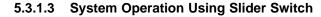

## 5.3.6.3 SW\_SEL Pin Functionality

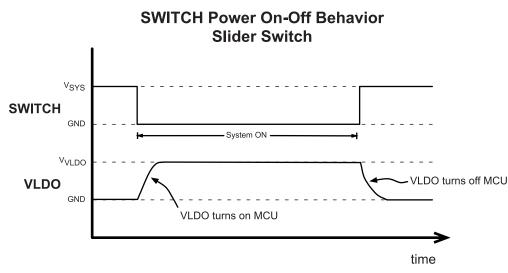

The SW\_SEL pin is used to select what type of switch is connected to the SWITCH pin of the device. Selection between a push-button and a slider switch can be made based on the state of this pin.

# SW\_SEL STATE TYPE OF SWITCH SELECTED Low (V<sub>SW\_SEL</sub> < V<sub>IL(PMIC)</sub>) Slider Switch High (V<sub>SW\_SEL</sub> > V<sub>IH(PMIC)</sub>) Push-button

Table 5-6. SW SEL Settings

When the push button switch type is selected, the device will debounce the SWITCH input with a 32-ms timer for both the ON and OFF events and either power on or off the device. Using the push-button switch function, the ON and OFF timings are equal;  $t_{ON} = t_{OFF}$ . If the system requirements are such that the on and off timings should be different,  $t_{ON} \neq t_{OFF}$ , then refer to the following section for the correct system setup: Section 6.2.1.2.3.When the slider switch operation is selected, the SWITCH pin must be externally pulled up to the SYS voltage with a resistor and the output connected to the slider switch. When the SWITCH pin is pulled to ground, the device will turn on and enter the power up sequence.

## 5.3.6.4 SWITCH Pin

The SWITCH pin behavior is defined by the SW\_SEL pin (Section 5.3.6.3) which defines the type of switch that is connected to the system; either a slider switch or push-button.

## 5.3.6.5 Slider Switch Behavior