Sample &

Buy

# TLC6C5712-Q1

SLVSCO9A - AUGUST 2015 - REVISED AUGUST 2015

TLC6C5712-Q1 12-Channel, Full-Diagnostic, Constant-Current-Sink LED Driver With 8-Bit Dot Correction

Technical

Documents

# 1 Features

- Qualified for Automotive Applications

- AEC-Q100 Qualified

- Device Temperature Grade 1: –40°C to 125°C Ambient Operating Temperature Range

- Device HBM ESD Classification Level H3A

- Device CDM ESD Classification Level C4B

- 12 Power DMOS-Transistor Output Channels

- Maximum Constant Current up to 75 mA, Programmable through External Resistor

- Maximum Output Voltage up to 7 V

- Maximum Dropout Voltage:

- 0.75 V at 50 mA per Channel

- 1.2 V at 75 mA per Channel

- Excellent Output Constant-Current Accuracy:

- Channel-Channel Difference: < ±3% (Max.)</li>

- Device-Device Difference: < ±3% (Max.)

- 8-Bit, 256-Step Linear Dot Correction for Each Channel

- Flexible External PWM Dimming Support

- 6 PWM Inputs With Frequency Supervision

- Programmable Channel Mapping Capability through SPI

- Protection and Diagnostics

- Adjacent-Pin Short Detection

- Open-Load, Short-to-GND, Shorted-LED, Detection for Both Activated and Deactivated State

- Thermal Prewarning and Shutdown

- Open-Drain Error Retorting

- LED Weak Supply Diagnostics

- Reference Resistor Open or Short Detection and Protection

- SPI Register Lock for Content Protection

- Force Error for SPI Integrity Diagnostics

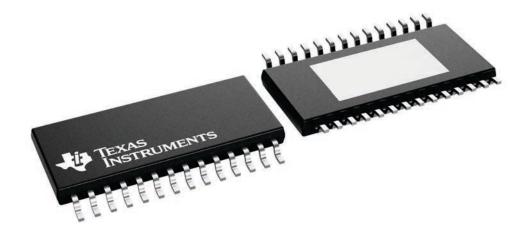

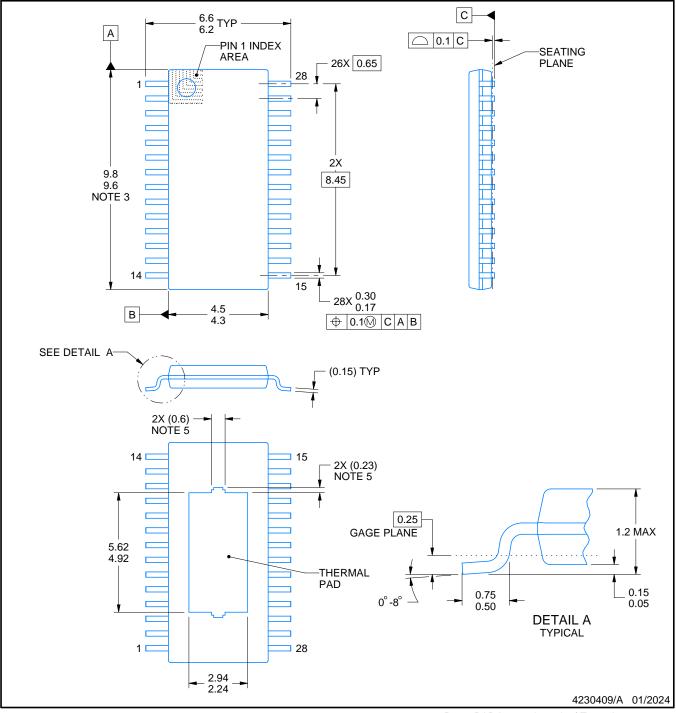

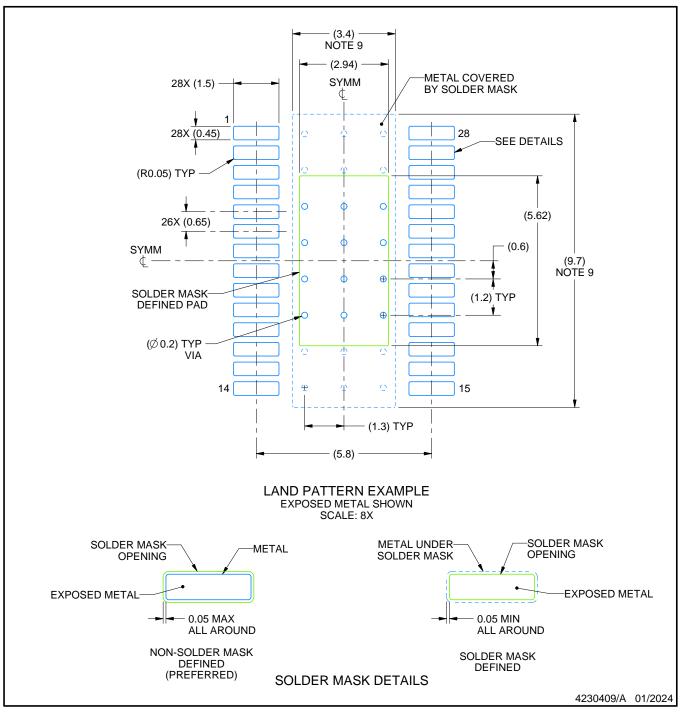

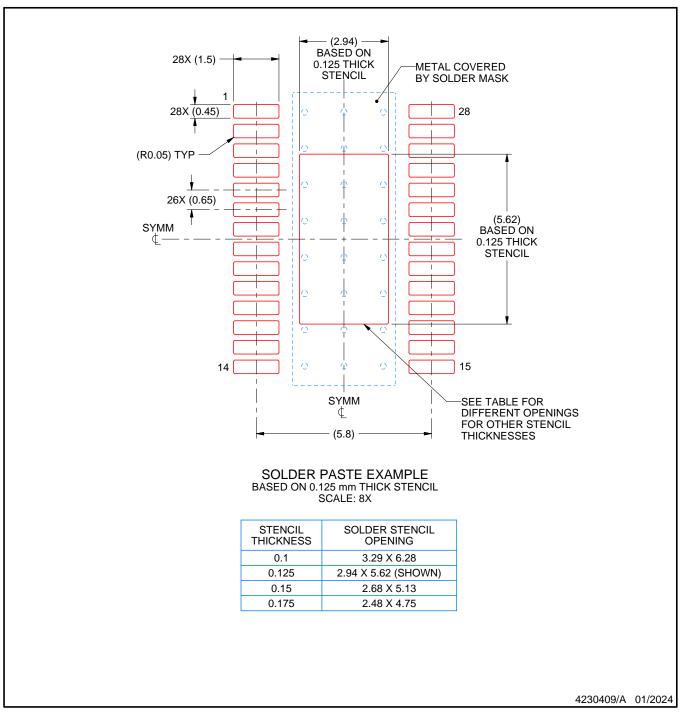

- Small and Thermally Effective 28-Pin HTSSOP PowerPAD<sup>™</sup> Package

# 2 Applications

- Cluster Tell-Tale Indicators

- Panel and Button Backlighting

- Bar-Graph LEDs

- Shifter PRNDL Indicators

- Sequential Turn Indicators

## 3 Description

Tools &

Software

In automotive cluster and other safety-critical LED driver applications, the performance demand for multi-channel LED is increasing to achieve consistency of LED brightness and color temperature. System-level safety considerations require detection capability for various fault scenarios and thus increase system complexity.

Support &

Community

**.**...

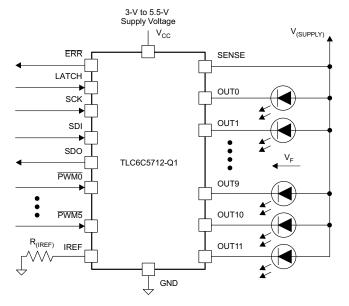

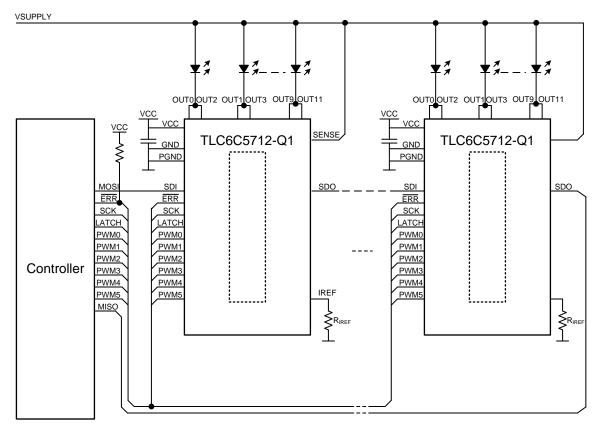

The TLC6C5712-Q1 device is a 12-channel constantcurrent-sink LED driver. The precision output current with 8-bit dot correction makes the TLC6C5712-Q1 device a perfect solution to correct LED brightness and color temperature variation. Advanced protection and diagnostics for each component improve systemlevel robustness and ease safety-oriented design. Six PWM inputs with programmable mapping support different LED color-dimming configurations and provide a high dimming ratio. A 16-bit serialperipheral interface (SPI with diagnostics supports multiple devices in a daisy chain and eases the system-level design.

### **Device Information**<sup>(1)</sup>

| PART NUMBER  | PACKAGE     | BODY SIZE (NOM)   |

|--------------|-------------|-------------------|

| TLC6C5712-Q1 | HTSSOP (28) | 4.40 mm × 9.70 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

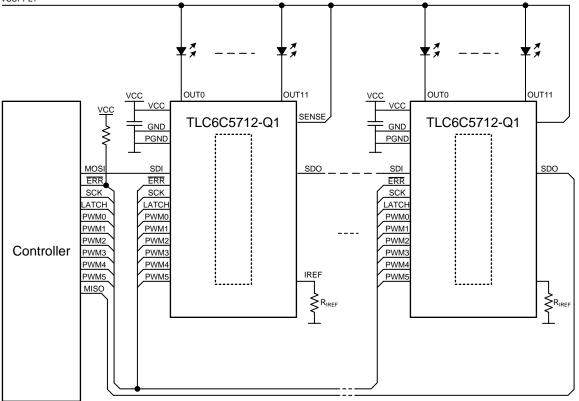

### **Typical Application Schematic**

TEXAS INSTRUMENTS

www.ti.com

Page

# **Table of Contents**

| 1 | Feat | tures 1                            |

|---|------|------------------------------------|

| 2 | Арр  | lications 1                        |

| 3 | Des  | cription 1                         |

| 4 | Rev  | ision History 2                    |

| 5 | Pin  | Configuration and Functions 3      |

| 6 | Spe  | cifications 4                      |

|   | 6.1  | Absolute Maximum Ratings 4         |

|   | 6.2  | ESD Ratings 4                      |

|   | 6.3  | Recommended Operating Conditions 4 |

|   | 6.4  | Thermal Information 5              |

|   | 6.5  | Electrical Characteristics 5       |

|   | 6.6  | Timing Requirements 7              |

|   | 6.7  | Switching Characteristics 7        |

|   | 6.8  | Typical Characteristics 9          |

| 7 | Deta | ailed Description 11               |

|   | 7.1  | Overview 11                        |

|   | 7.2  | Functional Block Diagram 11        |

|   |      |                                    |

|    | 7.3  | Feature Description                         | 12              |

|----|------|---------------------------------------------|-----------------|

|    | 7.4  | Device Functional Modes                     | 21              |

|    | 7.5  | Register Maps                               | 22              |

| 8  | App  | lication and Implementation                 | 55              |

|    | 8.1  | Application Information                     | <mark>55</mark> |

|    | 8.2  | Typical Applications                        | <mark>55</mark> |

| 9  | Pow  | er Supply Recommendations                   | 58              |

| 10 | Laye | out                                         | 58              |

|    | 10.1 | Layout Guidelines                           | <mark>58</mark> |

|    | 10.2 | Layout Example                              | <mark>59</mark> |

| 11 | Dev  | ice and Documentation Support               | 60              |

|    | 11.1 | Documentation Support                       | <mark>60</mark> |

|    | 11.2 | Community Resource                          | <mark>60</mark> |

|    | 11.3 | Trademarks                                  | <mark>60</mark> |

|    | 11.4 | Electrostatic Discharge Caution             | <mark>60</mark> |

|    | 11.5 | Glossary                                    | <mark>60</mark> |

| 12 |      | hanical, Packaging, and Orderable<br>mation | 60              |

## **4** Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

### Changes from Original (December 2014) to Revision A

| Released the full version of the data sheet | 1 |

|---------------------------------------------|---|

|                                             |   |

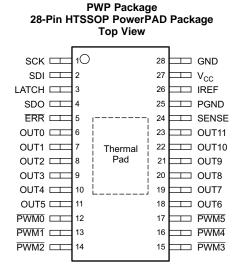

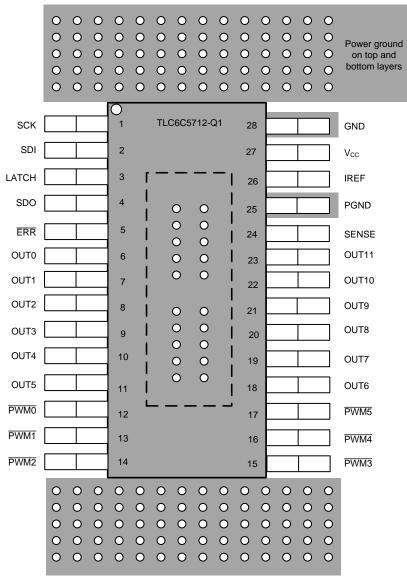

# 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN I/O         |     | 1/0 | DECODIDATION                                                            |

|-----------------|-----|-----|-------------------------------------------------------------------------|

| NAME            | NO. | 1/0 | DESCRIPTION                                                             |

| ERR             | 5   | 0   | Error output, open-drain output, active-low                             |

| GND             | 28  | —   | Device ground                                                           |

| IREF            | 26  | I   | Connect an external resistor to GND for setting the full-scale current. |

| LATCH           | 3   | I   | Latch enable                                                            |

| OUT0            | 6   | 0   | Open-drain output                                                       |

| OUT1            | 7   | 0   | Open-drain output                                                       |

| OUT2            | 8   | 0   | Open-drain output                                                       |

| OUT3            | 9   | 0   | Open-drain output                                                       |

| OUT4            | 10  | 0   | Open-drain output                                                       |

| OUT5            | 11  | 0   | Open-drain output                                                       |

| OUT6            | 18  | 0   | Open-drain output                                                       |

| OUT7            | 19  | 0   | Open-drain output                                                       |

| OUT8            | 20  | 0   | Open-drain output                                                       |

| OUT9            | 21  | 0   | Open-drain output                                                       |

| OUT10           | 22  | 0   | Open-drain output                                                       |

| OUT11           | 23  | 0   | Open-drain output                                                       |

| PGND            | 25  |     | Ground for output power                                                 |

| PWM0            | 12  | I   | PWM dimming input 0                                                     |

| PWM1            | 13  | I   | PWM dimming input 1                                                     |

| PWM2            | 14  | I   | PWM dimming input 2                                                     |

| PWM3            | 15  | I   | PWM dimming input 3                                                     |

| PWM4            | 16  | I   | PWM dimming input 4                                                     |

| PWM5            | 17  | I   | PWM dimming input 5                                                     |

| SCK             | 1   | I   | SPI clock                                                               |

| SDI             | 2   | I   | Serial-data input                                                       |

| SDO             | 4   | 0   | Serial-data output                                                      |

| SENSE           | 24  | I   | Sense input (LED supply-voltage monitor)                                |

| V <sub>CC</sub> | 27  | I   | Power supply                                                            |

# 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating ambient temperature range. Voltages referenced with respect to GND (unless otherwise noted)<sup>(1)(2)</sup>

|                       |                                               |  | MIN  | MAX             | UNIT |

|-----------------------|-----------------------------------------------|--|------|-----------------|------|

|                       | V <sub>cc</sub>                               |  | -0.3 | 7               |      |

| Input voltage         | IREF, LATCH, PWMx, SCK, SDI                   |  | -0.3 | V <sub>CC</sub> | V    |

|                       | SENSE                                         |  | -0.3 | 10              |      |

|                       | ERR open-drain output                         |  | -0.3 | 7               |      |

| Output voltage        | OUTx power DMOS drain-to-source voltage       |  | -0.3 | 10              | V    |

| 1 0                   | SDO                                           |  | -0.3 | V <sub>CC</sub> |      |

| Ground                | PGND                                          |  | -0.3 | 0.3             | V    |

| Operating ambient t   | emperature, T <sub>A</sub>                    |  | -40  | 125             | °C   |

| Operating junction to | perating junction temperature, T <sub>J</sub> |  | -40  | 150             | °C   |

| Storage temperature   | e range, T <sub>stg</sub>                     |  | -55  | 150             | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are measured relative to GND.

### 6.2 ESD Ratings

|                    |                            |                                                         |                                 | VALUE | UNIT |

|--------------------|----------------------------|---------------------------------------------------------|---------------------------------|-------|------|

|                    |                            | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup> |                                 | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic<br>discharge | Charged device model (CDM) per AEC 0100 011             | All pins                        | ±500  | V    |

|                    | aleellargo                 | Charged device model (CDM), per AEC Q100-011            | Corner pins (1, 14, 15, and 28) | ±750  | v    |

(1) AEC Q100-002 indicates HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                 |                                |                            | MIN                  | NOM                 | MAX                  | UNIT |

|-----------------|--------------------------------|----------------------------|----------------------|---------------------|----------------------|------|

| V <sub>CC</sub> | Supply input voltage           |                            | 3                    |                     | 5.5                  | V    |

| V               |                                | LATCH, PWMx, SCK, SDI, SDO | 0                    |                     | 5.5                  | V    |

| VI              | Input voltage                  | ERR, SENSE                 | 0                    |                     | 7                    | v    |

| Vo              | Output voltage                 | OUTx for $x = 0$ to 11     | 0.5                  |                     | 7                    | V    |

| V <sub>IL</sub> | Input logic-low voltage        | LATCH, PWMx, SCK, SDI      | 0.28 V <sub>CC</sub> | 0.3 V <sub>CC</sub> | 0.33 V <sub>CC</sub> | V    |

| VIH             | Input logic-high voltage       | LATCH, PWMx, SCK, SDI      | 0.38 V <sub>CC</sub> | $0.4 V_{CC}$        | 0.43 V <sub>CC</sub> | V    |

| T <sub>A</sub>  | Ambient operating temperature  |                            | -40                  |                     | 125                  | °C   |

| TJ              | Junction operating temperature |                            | -40                  |                     | 150                  | °C   |

## 6.4 Thermal Information

|                       |                                              | TLC6C5712-Q1 |      |

|-----------------------|----------------------------------------------|--------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PWP (HTSSOP) | UNIT |

|                       |                                              | 28 PINS      |      |

| $R_{	extsf{	heta}JA}$ | Junction-to-ambient thermal resistance       | 39           | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 19.5         | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 16.1         | °C/W |

| Ψ <sub>JT</sub>       | Junction-to-top characterization parameter   | 0.5          | °C/W |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 15.9         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.7          | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

## 6.5 Electrical Characteristics

$T_A = 25^{\circ}C$ , over recommended operating conditions (unless otherwise specified)

|                             | PARAMETER                           | TEST CONDITIONS                                                                                              | MIN                 | TYP                 | MAX                 | UNIT |

|-----------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------|---------------------|---------------------|------|

| POWER SUP                   | PLIES (V <sub>CC</sub> , PGND, GND) |                                                                                                              |                     |                     |                     |      |

| 1                           | Supply ourrent                      | $V_{CC}$ = 5 V, PWM = H, R <sub>REF</sub> = 20.5 k $\Omega$                                                  | 3                   |                     | 4.5                 | mA   |

| I <sub>CC</sub>             | Supply current                      | V <sub>CC</sub> = 3.3 V                                                                                      | 2.5                 |                     | 4                   | mA   |

| V(POR-rising)               | Power-on reset voltage, rising      | Rising threshold                                                                                             | 2.6                 | 2.7                 | 2.8                 | V    |

| V <sub>(POR-falling)</sub>  | Power-on reset voltage, falling     | Falling threshold                                                                                            | 2.4                 | 2.5                 | 2.6                 | V    |

| V <sub>(POR-hyst)</sub>     | POR threshold hysteresis            |                                                                                                              |                     | 0.2                 |                     | V    |

|                             | S (PWMx, SDI, LATCH, SCK)           |                                                                                                              |                     |                     |                     |      |

| V <sub>(HYS)</sub>          | Input logic hysterisis              | V <sub>CC</sub> = 5 V or 3.3 V                                                                               |                     | 0.1 V <sub>CC</sub> |                     | V    |

| l <sub>lkg</sub>            | Input leakage current               | $V_I = V_{CC}$                                                                                               | -1                  |                     | 1                   | μA   |

| R <sub>PU</sub>             | PWM pullup resistance               |                                                                                                              | 105                 | 150                 | 230                 | kΩ   |

| CONTROL OU                  | JTPUTS (ERR, IREF, SDO)             |                                                                                                              |                     |                     |                     |      |

| V <sub>(ERR)</sub>          | ERR pin open-drain voltage drop     | I <sub>(ERR)</sub> = 4 mA, V <sub>CC</sub> = 3.3 V–5 V                                                       |                     |                     | 0.1 V <sub>CC</sub> | V    |

| IIkg(ERR)                   | ERR leakage current                 | V <sub>(ERR)</sub> = 5 V                                                                                     |                     |                     | 3                   | μA   |

| V <sub>(IREF)</sub>         | IREF voltage                        | R <sub>(IREF)</sub> = 20.5 kΩ                                                                                | 1.204               | 1.229               | 1.254               | V    |

| V <sub>OH(SDO)</sub>        | SDO output-high voltage             | $I_{(SDO)} = -4 \text{ mA}$                                                                                  | 0.9 V <sub>CC</sub> |                     |                     | V    |

| V <sub>OL(SDO)</sub>        | SDO output-low voltage              | I <sub>(SDO)</sub> = 4 mA                                                                                    |                     |                     | 0.1 V <sub>CC</sub> | V    |

| OUTPUT STA                  | GE (OUTx)                           |                                                                                                              |                     |                     |                     |      |

|                             |                                     | $V_{(OUTx)} = 0.75 \text{ V}, R_{(IREF)} = 12.2 \text{ k}\Omega,$<br>Dot correction = 255                    |                     | 50                  |                     |      |

| I <sub>(OUTx,max)</sub>     | Constant output current             | $V_{(OUTx)} = 1.2 \text{ V}, \text{ R}_{(IREF)} = 8.13 \text{ k}\Omega,$<br>Dot correction = 255             |                     | 75                  |                     | mA   |

| I <sub>(OUTx,min)</sub>     | Minimum current-sink capability     | $V_{(OUTx)} = 0.75 \text{ V},  \text{R}_{\text{REF}} = 12.2 \text{ k}\Omega, \\ \text{dot correction} = 255$ | 0.15                | 0.165               | 0.18                | mA   |

| I <sub>(OUTx,default)</sub> | Constant output current             | $V_{(OUTx)} = 0.75$ V, reference fault detected,<br>Dot correction = 255                                     | 7.5                 | 10                  | 14                  | mA   |

|                             |                                     | $V_{CC}$ = 3.3 V, $R_{(IREF)}$ = 12.2 k $\Omega,$ dot correction = 255                                       |                     |                     | 0.75                |      |

| V <sub>(OUT,min)</sub>      | Minimum output voltage              | $V_{CC} = 5 \text{ V}, \text{ R}_{(IREF)} = 12.2 \text{ k}\Omega, \text{ dot correction} = 255$              |                     |                     | 0.5                 | V    |

|                             |                                     | $V_{CC} = 5 \text{ V}, \text{ R}_{(IREF)} = 8.13 \text{ k}\Omega, \text{ dot correction} = 255$              |                     |                     | 1.2                 |      |

|                             | Output-current dot-correction       | $V_{CC}$ = 5 V, $R_{(IREF)}$ = 12.2 kΩ, (50-mA maximum output current)                                       | -0.6                |                     | 0.6                 |      |

| DNL                         | differential nonlinearity           | $V_{CC}$ = 5 V, $R_{(IREF)}$ = 61 kΩ, (10-mA maximum output current)                                         | -0.08               |                     | 0.08                | mA   |

|                             |                                     | $V_{(OUTx)}$ = 0.75 V, $R_{(IREF)}$ = 12.2 k $\Omega$ (50 mA), dot correction = 255                          | -3%                 |                     | 3%                  |      |

| A1                          | Output current absolute error       | $V_{(OUTx)}$ = 0.75 V, $R_{(IREF)}$ = 20.5 k $\Omega$ (30 mA), dot correction = 255                          | -3%                 |                     | 3%                  |      |

| ΔI <sub>(OUTx)</sub>        | percentage                          | $V_{(OUTx)}$ = 0.75 V, $R_{(IREF)}$ = 61 k $\Omega$ (10 mA), dot correction = 255                            | -7.5%               |                     | 7.5%                |      |

|                             |                                     | $V_{(OUTx)}$ = 1.2 V, $R_{(IREF)}$ = 8.13 k $\Omega$ (75 mA), dot correction = 255                           | -3%                 |                     | 3%                  |      |

Copyright © 2015, Texas Instruments Incorporated

NSTRUMENTS

Texas

# **Electrical Characteristics (continued)**

| $T_A = 25^{\circ}C$ , over recommended operating conditions (unless otherwise spec | $_{A} = 25^{\circ}C$ , over | er recommended | operating c | onditions ( | (unless c | otherwise s | pecified |

|------------------------------------------------------------------------------------|-----------------------------|----------------|-------------|-------------|-----------|-------------|----------|

|------------------------------------------------------------------------------------|-----------------------------|----------------|-------------|-------------|-----------|-------------|----------|

|                             | PARAMETER                                                                                                        | TEST CONDITIONS                                  | MIN   | TYP  | MAX  | UNIT  |

|-----------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-------|------|------|-------|

| ΔI <sub>(OUT_VOUT)</sub>    | Output current dependency on OUTx voltage                                                                        |                                                  | -0.5% |      | 0.5% |       |

| K <sub>(OUT)</sub>          | Ratio of output current to IREF current, $K = I_{(OUTx)} / I_{(IREF)}$                                           | Dot correction = 255                             |       | 500  |      | mA/mA |

| I <sub>lkg(OUTx)</sub>      | Output leakage current                                                                                           |                                                  |       |      | 0.5  | μA    |

| I <sub>lkg(SENSE)</sub>     | Leakage current at SENSE pin                                                                                     | $V_{CC} = 0, V_{(SENSE)} = 5 V$                  |       |      | 10   | μA    |

| I(IREF_octh)                | IREF resistor open-circuit detection threshold                                                                   | $V_{CC} = 5 V$                                   | 4.5   |      | 15   | μA    |

| I(IREF_octh,hyst)           | IREF resistor open-circuit detection-<br>threshold hysteresis                                                    | $V_{CC} = 5 V$                                   |       | 2    |      | μA    |

| I(IREF_scth)                | IREF resistor short-circuit detection threshold                                                                  | V <sub>CC</sub> = 5 V                            | 160   |      | 260  | μA    |

| I(IREF_scth,hyst)           | IREF resistor short-circuit detection-<br>threshold hysteresis                                                   | V <sub>CC</sub> = 5 V                            |       | 20   |      | μA    |

| I <sub>(OUT_PULLUP)</sub>   | Channel pullup current during<br>deactivated state                                                               | V <sub>CC</sub> = 5 V, V <sub>(OUTx)</sub> = 1 V |       | 50   |      | μA    |

| PROTECTION                  | CIRCUITS                                                                                                         |                                                  |       |      |      |       |

| V <sub>(WLS)</sub>          | Weak LED supply-detection threshold voltage                                                                      | [WLS_TH] = 0                                     | 4.1   | 4.2  | 4.3  | V     |

| V <sub>(WLS_hyst)</sub>     | Weak LED supply hysteresis                                                                                       | [WLS_TH] = 0                                     |       | 0.1  |      | V     |

| V <sub>(WLS_OPT)</sub>      | Weak LED supply detection-threshold voltage                                                                      | [WLS_TH] = 1                                     | 2.7   | 2.77 | 2.85 | V     |

| V <sub>(WLS_hyst_OPT)</sub> | Weak LED supply hysteresis                                                                                       | [WLS_TH] = 1                                     |       | 0.1  |      | V     |

| V <sub>(SC_th)</sub>        | Short circuit-to-V <sub>(SENSE)</sub> detection<br>threshold, voltage difference between<br>V(SENSE) and V(OUTx) |                                                  | 0.5   | 0.7  | 0.9  | V     |

| V <sub>(SC_hyst)</sub>      | Short circuit-to-V <sub>(SENSE)</sub> detection hysteresis                                                       |                                                  |       | 0.1  |      | V     |

| V <sub>(OC_th)</sub>        | Open-circuit detection threshold                                                                                 |                                                  | 0.1   | 0.2  | 0.3  | V     |

| V <sub>(OC_hyst)</sub>      | Open-circuit-detection hysteresis                                                                                |                                                  |       | 0.05 |      | V     |

| T <sub>(TSD)</sub>          | Thermal-shutdown junction temperature                                                                            |                                                  | 150   | 165  |      | °C    |

| T <sub>(HYS)</sub>          | Thermal shutdown or warning junction temperature hysteresis                                                      |                                                  |       | 15   |      | ٥C    |

| T <sub>(PTW)</sub>          | Pre-thermal warning junction-<br>temperature threshold                                                           |                                                  | 125   | 135  | 150  | °C    |

6

## 6.6 Timing Requirements

|                                            |                                    | MIN | NOM | MAX | UNIT |

|--------------------------------------------|------------------------------------|-----|-----|-----|------|

| f <sub>(SCK)</sub>                         | Clock frequency, cascade operation |     | 1   | 10  | MHz  |

| t <sub>c(SCK)</sub>                        | SCK cycle time                     | 100 |     |     | ns   |

| t <sub>w(LAH)</sub> , t <sub>w(WLAH)</sub> | Pulse duration, LATCH              | 380 |     |     | ns   |

| t <sub>w(CKH)</sub> , t <sub>w(WCKH)</sub> | SCK high pulse duration            | 50  |     |     | ns   |

| t <sub>w(CKL)</sub> , t <sub>w(WCKL)</sub> | SCK low pulse duration             | 50  |     |     | ns   |

| t <sub>w(SEW)</sub> , t <sub>w(WDI)</sub>  | SDI high and low pulse duration    | 150 |     |     | ns   |

| t <sub>su(SEST)</sub>                      | SDI setup time prior to SCK rise   | 75  |     |     | ns   |

| t <sub>h(SEHD)</sub>                       | SDI hold time after SCK rise       | 75  |     |     | ns   |

| t <sub>r</sub>                             | Output rise time (SCK)             |     |     | 50  | ns   |

| t <sub>f</sub>                             | Output fall time (SCK)             |     |     | 50  | ns   |

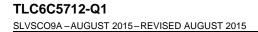

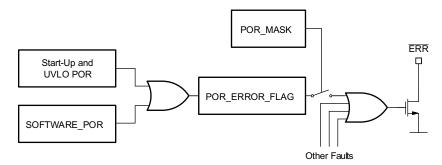

# 6.7 Switching Characteristics

$T_{\rm A}$  = –40°C to 105°C,  $V_{\rm CC}$  = 3 V to 5.5 V

|                         | PARAMETER                                          | TEST CONDITIONS                                                                                          | MIN  | TYP  | MAX  | UNIT |

|-------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------|------|------|------|------|

| f <sub>(SCK)</sub>      | Clock frequency                                    | Cascade operation                                                                                        |      |      | 10   | MHz  |

| t <sub>d(LAH)</sub>     | Latch switching delay                              |                                                                                                          |      |      | 3000 | ns   |

| t <sub>pd(SOH)</sub>    | SDO propagation delay time (L to H)                |                                                                                                          |      |      | 1000 | ns   |

| t <sub>pd(SOL)</sub>    | SDO propagation delay (H to L)                     |                                                                                                          |      |      | 3000 | ns   |

| t <sub>pd(LAOL)</sub>   | High to low propagation delay time (LATCH – OUT)   |                                                                                                          |      | 750  | 3000 | ns   |

| t <sub>pd(CKLAH)</sub>  | Low-to-high propagation delay time (SCK – LATCH)   |                                                                                                          | 200  |      |      | ns   |

| t <sub>pd(CKDOH)</sub>  | Low-to-high propagation delay time (SCK – SDO)     |                                                                                                          |      | 30   | 75   | ns   |

| t <sub>pd(CKDOHL)</sub> | High-to-low propagation delay time (SCK – SDO)     |                                                                                                          |      | 30   | 75   | ns   |

| t <sub>r(o)</sub>       | Rise time, outputs (OFF) SDO                       |                                                                                                          |      |      | 50   | ns   |

| t <sub>f(0)</sub>       | Fall time, outputs (ON) SDO                        |                                                                                                          |      |      | 50   | ns   |

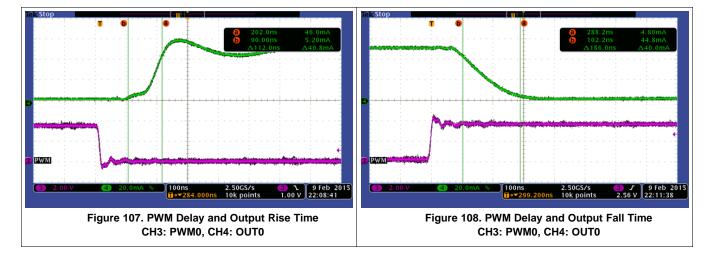

| t <sub>d(PWM_ON)</sub>  | Output delay time from PWMx to $I_{(\text{OUT}x)}$ | PWMx falling threshold from 0.4 V <sub>CC</sub> to $I_{(OUTx)}$ rising threshold 10% of $I_{(OUTx,max)}$ | 0.09 | 0.13 | 0.2  | μs   |

| t <sub>d(PWM_OFF)</sub> | Output delay time PWMx to $I_{\mbox{OUTx}}$        | PWMx rising threshold from 0.4 $V_{CC}$ to $I_{(OUTx)}$ falling threshold 90% of $I_{(OUTx,max)}$        | 0.09 | 0.13 | 0.2  | μs   |

|                         | Output rise time                                   | Default slew rate, rise time from<br>10% to 90% current, 30-pF loading<br>capacitance                    |      |      | 0.3  |      |

| t <sub>r</sub>          | Output rise time                                   | With slow-slew-rate register option,<br>rise time from 10% to 90% current,<br>30-pF loading capacitance  |      |      | 0.8  | μs   |

|                         |                                                    | Default slew rate, fall time from 90%<br>to 10% current, 30-pF loading<br>capacitance                    |      |      | 0.3  |      |

| t <sub>f</sub>          | Output fall time                                   | With slow-slew-rate register option,<br>fall time from 90% to 10% current,<br>30-pF loading capacitance  |      |      | 0.8  | μs   |

| t <sub>(DEG)</sub>      | Output open or short degllitch time                |                                                                                                          | 1    | 2    | 3    | μs   |

| t <sub>(REF_DEG)</sub>  | Reference open or short deglitch time              |                                                                                                          |      | 100  |      | μs   |

| t <sub>(PWM)</sub>      | PWM edge detection timer                           | Timer length for PWM edge detection                                                                      | 17   | 20   | 23   | ms   |

|                         |                                                    |                                                                                                          |      |      |      |      |

Texas Instruments

www.ti.com

0 V

V<sub>(supply)</sub>

0.5 V

$V_{CC}$

0 V

$V_{CC}$

0 V

t<sub>d(LAH)</sub> -

50%

OUTPUT

OUT0-OUT11

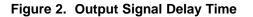

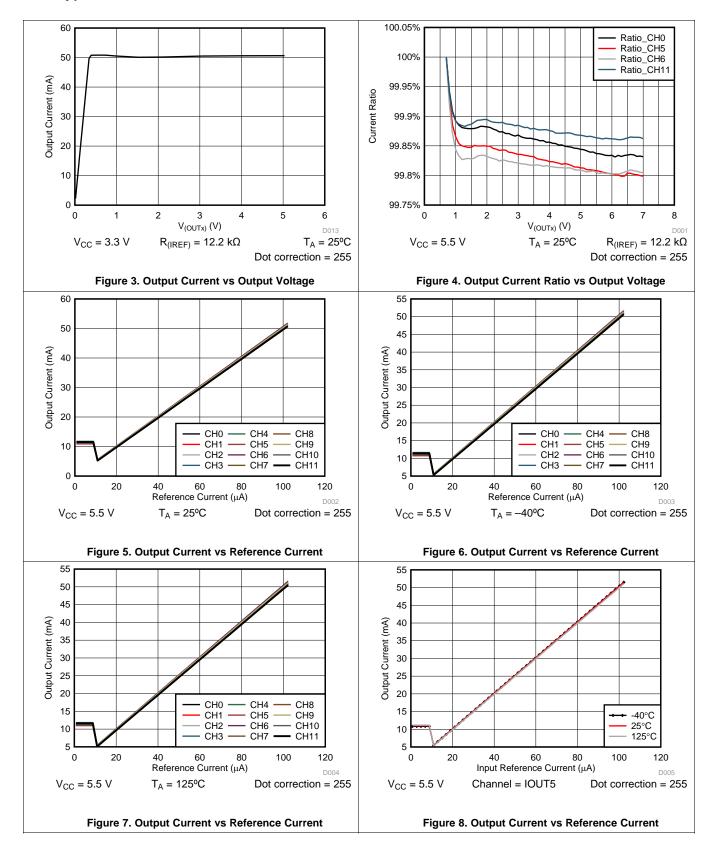

## 6.8 Typical Characteristics

SLVSCO9A - AUGUST 2015 - REVISED AUGUST 2015

www.ti.com

### **Typical Characteristics (continued)**

## 7 Detailed Description

### 7.1 Overview

The TLC6C5712-Q1 device is a 12-channel constant-current-sink LED driver. At the TLC6C5712-Q1 output stage, 12 regulated current channels provide uniform and constant current for driving LEDs within a wide range of forward-voltage variations.

Users can adjust output current from 10 mA to 75 mA through an external resistor,  $R_{(IREF)}$ , which provides flexibility in controlling the light intensity of the LEDs. The maximum constant-current value (full-scale range) of all 12 channels is set by a single external resistor. The current of each individual output can be programmed in 256 linear steps, allowing further calibration. The design of the TLC6C5712-Q1 device supports up to 7 V at the output ports. The serial communication interface is designed for high-throughput data transmission with cascaded devices. The device has six PWM input channels and 12 output channels that can be mapped arbitrarily to any of the 6 PWM inputs.

The TLC6C5712-Q1 device has advanced diagnostics, LED open-load detection, shorted-LED detection, shortcircuit to ground detection, reference resistor open and short protection, PWM input-frequency supervision, adjacent-pin short diagnostics, thermal pre-warning and thermal protection. LED open-and-short and output short-to-ground detection is available even when an LED channel is off. The diagnostic functions and errors can be activated or de-activated individually by functions or channels. Users can configure the open-drain error output to signalize various types of errors.

#### OUT1 OUTO OUT10 OUT11 V<sub>CC</sub> IREF IO Regulator SENSE PWM0 Output Driver and PWM Error Detection MUX . 12 12 12 PWM5 12-Bit Output Latch Configuration Open-Drain LATCH ERR Latches Error Output SPI and Control SCK /12 Logic 16-Bit Shift SDI SDO Register GND PGND

### 7.2 Functional Block Diagram

### 7.3 Feature Description

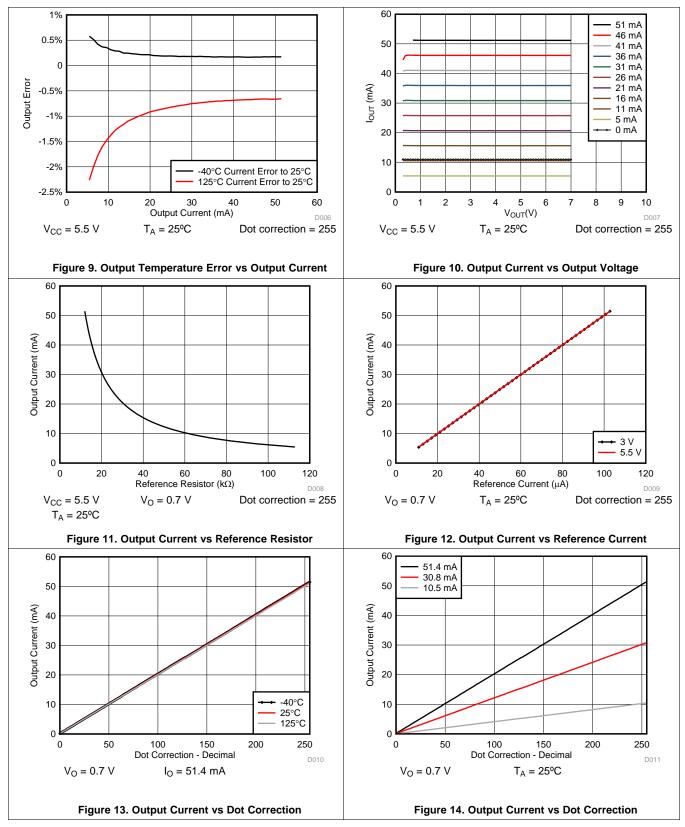

### 7.3.1 Power-On Reset (POR)

The device supports two types of POR, start-up or UVLO POR and software POR, with software reset capability.

### 7.3.1.1 Start-Up or UVLO POR

When power is applied to  $V_{CC}$ , or when  $V_{CC}$  is undervoltage ( $V_{CC} < V_{(POR)}$ ), an internal power-on reset (POR) holds the TLC6C5712-Q1 device in a reset condition with the following conditions until  $V_{CC}$  reaches VPOR. During RESET:

- The device cannot receive data.

- The SDO pin is held LOW, so the device cannot transmit data.

- The ERR open-drain output is pulled down.

During POR, communication between the controller and the device is lost. Any data transmitted during this period is lost. The state machine inside the device is undefined. After POR, the reset status is released, the TLC6C5712-Q1 registers and SPI state machine are re-initialized to default states (see the *Default* column in Table 2). [POR\_ERR\_FLAG] is set to HIGH during start-up or UVLO POR.

### 7.3.1.2 Software POR

A software reset command (*SOFTWARE\_POR*>) resets all internal register settings to default values. The command executes on a LATCH rising edge. All fault bits and diagnostic status are cleared and set to their default values. The *SOFTWARE\_POR*> command also executes the RESET\_STATUS] command. The [POR\_ERR\_FLAG] bit in the *READ\_STATUSO*> register is set to HIGH on a software POR.

### 7.3.1.3 Reset POR

Either start-up or a UVLO POR or a software POR sets [POR\_ERR\_FLAG] to HIGH. when the device enters POR status, the [POR\_ERR\_FLAG] bit is latched HIGH. To clear the [POR\_ERR\_FLAG], a *RESET\_POR* command must be issued.

If [POR\_ERR\_FLAG] is set either by start-up, UVLO, or software, and the device is not in any UVLO state, [POR\_ERR\_FLAG] is latched and does not block any operation.

### 7.3.1.4 POR Masking

[POR\_ERR\_FLAG] reporting to the ERR output can be masked by the [POR\_MASK] bit. If a POR event happens when [POR\_MASK] is set HIGH, POR events do not trigger the ERR output, and [POR\_ERR\_FLAG] is set HIGH.

Figure 15. POR Error Report Topology

See the following addresses in Table 2: 61h, 62h, 63h, and A2h.

### 7.3.2 Error Feedback

The TLC6C5712-Q1 device supports an active-low open-drain output for error information through the ERR pin for the MCU error-monitor interrupt. If any FLAG bit is set to HIGH in the <READ\_STATUS0> register, and is not masked by a corresponding mask bit in the <WRITE\_ERROR\_MASK> register, the ERR pin pulls low to indicate an ERROR scenario. The MCU should immediately execute the error monitor routine.

### Feature Description (continued)

#### 7.3.2.1 Recovery From Error

When any fault occurs, all FAULT information can be read in separate FAULT registers, for example, <<u>READ\_OPEN\_FAULTO></u>. When the error condition recovers, the register information is still latched and the ERR pin remains low until the fault is masked or the *RESET\_STATUS* command has been issued. However, if the error condition still exists after issuing the *RESET\_STATUS* command, the ERR pin pulls low again and the corresponding FAULT register is set HIGH.

### 7.3.2.2 RESET\_STATUS Command

The *RESET\_STATUS* command clears all flags in the following registers:

<READ\_ADJSHORT0> <READ\_ADJSHORT1> <READ\_SHORT\_FAULT0> <READ\_SHORT\_GND\_FAULT0> <READ\_SHORT\_GND\_FAULT0> <READ\_OPEN\_FAULT0> <READ\_OPEN\_FAULT0> <READ\_OPEN\_FAULT1> <READ\_OPEN\_FAULT1> <READ\_PWM\_FAULT> <READ\_STATUS0>, **excluding** the [POR\_ERR\_FLAG] bit.

As mentioned in the POR section, only the RESET\_POR command can clear the [POR\_ERR\_FLAG] bit.

[POR\_ERR\_FLAG] bit: Read only (R) bit. HIGH: A POR error has occurred. To reset this flag, issue a *RESET\_POR* command.

[POR\_MASK] bit: Read and write (R/W) bit. HIGH: A POR error is stored in the [POR\_ERR\_FLAG] bit and is not reported to ERR.

*RESET\_POR*: A command to reset [POR\_ERR\_FLAG].

SOFTWARE\_POR: A command to generate a POR. It also clears STATUS flags.

See the following addresses in Table 2: 62h, 9Ah through A2h, A8h, and A9h.

### 7.3.3 PWM Input

The TLC6C5712-Q1 device has six PWM inputs with independently configurable mapping to modulate any of the 12 channels for external PWM dimming. A PWM monitor can be used to supervise PWM input-signal integrity.

### 7.3.3.1 PWM Dimming

PWM dimming is supported on all 12 channels by six PWM inputs. The input PWMx signal is active-low. Due to the minimal pulse duration needed for diagnostics, at 200 Hz the minimum achievable duty cycle is 0.1%, or 5 µs minimal on-time. Similarly, the maximum achievable duty cycle is 99.2%, or 40 µs minimum off-time. The setting of this boundary allows enough time for diagnostic functions. In the case of 0% or 100% PWM, diagnostics are not reported.

### 7.3.3.2 PWM Monitor

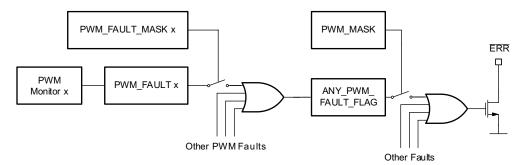

Independent **rising-edge** triggered timers are implemented as PWM monitors for each PWMx input channel. when the timer length reaches the threshold t<sub>PWM</sub>, [PWM\_FAULTx] is set to HIGH. If the corresponding masking register [PWM\_FAULT\_MASKx] is also set HIGH, the fault is stored in [PWM\_FAULTx] and is not reported to the [ANY\_PWM\_FAULT\_FLAG] register. [ANY\_PWM\_FAULT\_FLAG] is set to HIGH and the ERR pin is pulled LOW if any of the PWM monitors reported a fault and the mask register [PWM\_MASK] is disabled. The PWM rising edge resets the timer and restarts counting from 0. For 0% or 100% PWM, the [PWM\_FAULTx] registers should be independently masked for each PWMx input via the [PWM\_FAULT\_MASKx] registers.

### Feature Description (continued)

Figure 16. PWM Fault Report Topology

After being set HIGH, [PWM\_FAULTx] FAULT\_PWMx is latched even if the corresponding PWM input toggling has recovered. The *RESET\_STATUS* command must be issued to clear the [ANY\_PWM\_FAULT\_FLAG] bit.

### 7.3.3.3 PWM Mapping

Each of the 12 output channels has a 3-bit [PWM\_MAP\_CH] field to assign to one PWMx input. All output channels are assigned to PWM0 by default. Table 1 lists the mapping for each PWMx input..

| PWMx<br>PWM0 |

|--------------|

| PWM0         |

|              |

| PWM1         |

| PWM2         |

| PWM3         |

| PWM4         |

| PWM5         |

| PWM0         |

| PWM0         |

|              |

### Table 1. PWMx Mapping

### 7.3.3.4 PWM MAP Register Lock

To avoid unintended modification of the <PWM MAPx> registers, the <PWM MAPx> registers can be locked via the *LOCK\_MAP* command and unlocked via the *UNLOCK\_MAP* command. For details, see the *Register Protection* feature.

See the following addresses in Table 2: 40h through 45h, 60h, 62h, 66h through 68h, 6Ch, A0h through A3h, A6h, and A7h.

| [PWM_MAP_CH] field:       | R/W. 3 bits. Mapping output channel PWM source to PWMx input.                      |

|---------------------------|------------------------------------------------------------------------------------|

| [PWM_FAULT_MASKx] bit:    | R/W. Active-high. Mask the PWM fault flag PWMx.                                    |

| [PWM_MASK] bit:           | R/W. Active-high. Disable the ANY_PWM_FAULT_FLAG from reporting to ERR.            |

| [PWM_FAULTx] bit:         | R only. Active-high. HIGH: PWM monitor timer has triggered for $\overline{PWMx}$ . |

| [ANY_PWM_FAULT_FLAG] bit: | R only. Active-high. HIGH: One or more PWMx inputs have triggered the PWM monitor. |

| [SLOW_SLEW_RATE] bit:     | R/W. Active-high. HIGH: Slow slew rate.                                            |

#### 7.3.4 Constant-Current Output

(1)

The TLC6C5712-Q1 device has 12 constant-current output channels. An external resistor, R<sub>(IREF)</sub>, sets the maximum current of all channels globally. The current of each channel is individually configurable by independent 8-bit current digital-to-analog converters to support dot-correction capability, also known as calibration capability. Dot correction can be used to calibrate out brightness differences introduced by LED bin-to-bin differences or plastic transmittance variation by software instead of manually selecting matching resistors.

### 7.3.4.1 Global Current Reference

Maximum channel output current (dot-correction register [OUTPUT\_DC\_CHx] is set at full range, FFh) is globally set by reference resistor  $R_{(IREF)}$ . The  $V_{(IREF)}$  voltage biases external reference resistor  $R_{(IREF)}$ , generating reference current  $I_{(IREF)}$ .  $I_{(IREF)}$  is sensed and amplified by the ratio of  $K_{(OUT)}$  as the maximum output current. Choose the external resistor  $R_{(IREF)}$  value using Equation 1, based on maximum current  $I_{(OUT,MAXIDC=255)}$ .

$$\mathsf{R}_{(\mathsf{IREF})} = \frac{\mathsf{V}_{(\mathsf{IREF})}}{\mathsf{I}_{(\mathsf{OUT})\mathsf{max}\,|\,\mathsf{Dot\,Correction\,=\,255}}} \times \mathsf{K}_{(\mathsf{OUT})}$$

#### 7.3.4.2 Current Reference Monitor and Protection

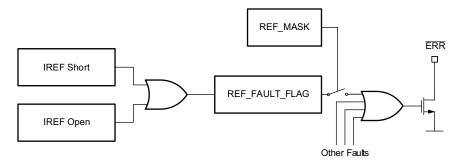

The TLC6C5712-Q1 device implements a current-reference monitor for current-reference resistor open-and-short diagnostic and protection. The device monitors the current  $I_{(IREF)}$  flowing out of the IREF pin. If  $I_{(IREF)}$  is higher than  $I_{(IREF_scth)}$ , a reference-short condition is asserted, limiting the  $I_{(IREF)}$  output current for short protection. If the  $I_{(IREF)}$  current is smaller than  $I_{(IREF_scth)}$ , a reference-open condition is asserted.

To maintain output function when the IREF resistor is in a short or open condition, device switches to a fail-safe current source. In fail-safe mode, the maximum output current is defined as  $I_{(OUTx\_default)}$ . when the external fault condition is removed, the external resistor sets the  $I_{(IREF)}$  current.

$$I_{(IREF)} = \frac{V_{(IREF)}}{R_{(IREF)}}$$

(2)

To avoid switching into default current unintentionally, the device implements a digital deglitch filter on the reference open and short diagnostics. The filter length is defined as  $t_{(REF\_deg)}$ . On assertion of the reference open-or-short fault, the [REF\_FAULT\_FLAG] bit is set. The [REF\_MASK] bit can be used to mask the reference fault output to the ERR pin. If [REF\_MASK] is enabled, a reference fault is not reported to the ERR output. If [REF\_MASK] is enabled, a reference fault is not reported to the ERR output. If [REF\_MASK] is enabled, a reference fault is not reported to the ERR output. Clearing the [REF\_FAULT\_FLAG] bit requires issuing the *RESET\_STATUS* command.

Figure 17. Reference Fault Report Topology

### 7.3.4.3 Channel Activation Control

[CH\_ON\_MASKx] are the channel activation mask bits which control each channel output ACTIVATED-DEACTIVATED. Logic LOW stands for channel ACTIVATED status.

DEACTIVTING a channel output does not clear the diagnostics registers.

SLVSCO9A - AUGUST 2015 - REVISED AUGUST 2015

**NSTRUMENTS**

**EXAS**

### 7.3.4.4 Individual Dot Correction Control

Each channel has an internal 8-bit linear-current digital-to-analog converter for individual dot correction control. The 8-bit [OUTPUT\_DC\_CHx] fields are used to control DAC output current according to Equation 3. Note that the minimum current is 1 / 256 of  $I_{OUT,MAX}$ . If absolutely zero current is required in some scenarios, the channel can be disabled by setting the corresponding channel-enable [CH\_ON\_MASKx] bit HIGH.

$$I_{(OUT)} = I_{(OUT)} max \times \frac{Dot Correction + 1}{256}$$

(3)

### 7.3.4.5 Output Slew-Rate Adjustment

To accommodate different slew rate requirements for EMC optimization, the [SLOW\_SLEW\_RATE] bit is provided. Setting [SLOW\_SLEW\_RATE] HIGH makes both the rising and falling times, t<sub>r</sub> and t<sub>f</sub>, longer.

### 7.3.4.6 Register Lock

To avoid unintended modification of registers, the [OUTPUT\_DC\_CHx] fields can be locked with the *LOCK\_CORR* command and unlocked with the *UNLOCK\_CORR* command. The [CH\_ON\_MASKx] bits can be locked with the *LOCK\_MASK* command and unlocked with the *UNLOCK\_MASK* command. For details, see the *Register Protection* section.

### 7.3.4.7 Deactivated-Channel Internal Pullup

To avoid floating outputs on a deactivated channel, optional pullup current to the SENSE node  $I_{(OUT_PULLUP)}$  is provided. The pullup current is disabled by default and can be enabled by setting the [DIS\_PULL\_UP\_CHx] bit HIGH.

See the following addresses in Table 2: 46h through 43h, 69h, 6Ah, 6Dh, 6Eh, and 86h through 93h.

[OUTPUT\_DC\_CHx] field:R/W. 8-bit. Dot correction current DAC setting register for channel x.[CH\_ON\_MASKx]:R/W. HIGH: Channel output disabled; LOW: Channel output enabled

## 7.3.5 Advanced Diagnostics

The TLC6C5712-Q1 device supports a variety of diagnostic features, including:

- Pre-thermal warning and thermal shutdown protection

- LED short-to-supply detection

- LED short-to-GND detection

- LED open-load detection

- Deactivated-channel LED-open or -short detection

- Weak-LED-supply detection

- Adjacent-pin short detection

- Reference resistor open or short detection and protection

- PWM frequency monitor

### 7.3.5.1 Pre-Thermal Warning and Thermal Shutdown Protection

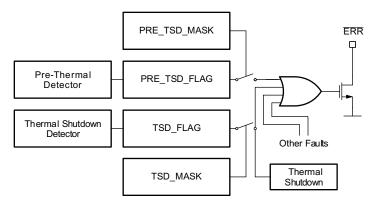

When the junction temperature exceeds the pre-thermal-warning threshold  $T_{(PTW), }[PRE_TSD_FLAG]$  in the <READ\_STATUS0> register is set HIGH to signal the pre-thermal warning. The ERR open-drain output is also pulled down. The microcontroller should respond to the fault warning and take actions to prevent junction temperature rising.

If junction temperature continues to rise and exceeds thermal-shutdown threshold  $T_{(TSD)}$ , the overt<u>emp</u>erature fault bit [TSD\_FLAG] in the <READ\_STATUS0> register is set HIGH to signal thermal shutdown, the ERR opendrain output is also pulled down, and all output channels are turned off for protection.

[PRE\_TSD\_FLAG] and [TSD\_FLAG] are latched when triggered. To clear either of the flags, issue the *RESET\_STATUS* command.

[TSD\_FLAG] is latched after having been set. After the die temperature falls below  $T_{(TSD)} - T_{(HYS)}$ , the LED outputs are activated using the previous settings without re-initializing.

The <u>flag</u> bits can be individually masked by [PRE\_TSD\_MASK] and [TSD\_MASK]. [PRE\_TSD\_MASK] prevents the ERR open-drain output. [TSD\_MASK] prevents the ERR open-drain output and thermal shutdown of all channels. Even if the faults are masked, the fault status can still be read in the registers.

Figure 18. Thermal Fault Report Topology

### 7.3.5.2 LED Short-to-Supply Detection

The device has independent LED short-to-supply detection for each channel. Whether the channel PWM source is HIGH or LOW, the voltage difference between the SENSE and OUTx pins is monitored.

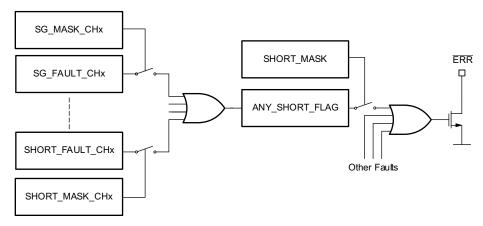

If an LED short to the supply is detected, the [SHORT\_FAULT\_CHx] bit of the channel is set HIGH and the [ANY\_SHORT\_FLAG] bit is set HIGH The [ANY\_SHORT\_FLAG] also pulls down the ERR open-drain output.

The LED short-to-supply fault does not disable the corresponding channel output. when the fault condition is removed, the LED should resume normal operation. Fault conditions are latched in the [SHORT\_FAULT\_CHx] bits. To clear the [SHORT\_FAULT\_CHx] bits, issue the *RESET\_STATUS* command.

The [SHORT\_FAULT\_CHx] bits can be masked independently for each channel by the [SHORT\_MASK\_CHx] bits. when the [SHORT\_MASK\_CHx] bit of any channel is set HIGH, the short-to-supply fault on the specific channel is not reported to [ANY\_SHORT\_FLAG].

### 7.3.5.3 LED Short-to-GND Detection

The TLC6C5712-Q1 device is able to distinguish an LED short-to-GND condition from an LED open-detection condition by having an internal pullup current to the SENSE node. The pullup is enabled during the PWM OFF state or channel-deactivated state.

If an LED short-to-GND is detected, the [SG\_FAULT\_CHx] bit for the channel is set HIGH, and the [ANY\_SHORT\_FLAG] bit is also set HIGH. [ANY\_SHORT\_FLAG] also pulls down the ERR open-drain output.

An LED short-to-GND fault does not disable the corresponding channel output. when a fault condition is removed, the LED should resume normal operation. Fault conditions are latched in the [SG\_FAULT\_CHx] fault bits. Issue a *RESET\_STATUS* command to clear the [SG\_FAULT\_CHx] fault bits.

The [SG\_FAULT\_CHx] channel-fault bits can be masked independently by [SG\_MASK\_CHx]. when the [SG\_MASK\_CHx] bit of any channel is set HIGH, the short-to-GND fault on the specific channel is not reported to [ANY\_SHORT\_FLAG].

Figure 19. Short Fault Report Topology

### 7.3.5.4 LED Open-Load Detection

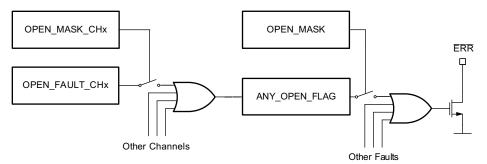

The device has independent LED open-load detection for each channel. If an LED open-load condition is detected, the [OPEN\_FAULT\_CHx] bit for the channel is set HIGH, and the [ANY\_OPEN\_FLAG] bit also is set HIGH. [ANY\_OPEN\_FLAG] also pulls down the ERR open-drain output.

An LED open-load fault does not disable the corresponding channel output. when a fault condition is removed, the LED should resume normal operation. Fault conditions are latched in the [OPEN\_FAULT\_CHx] fault bits. Issue a *RESET\_STATUS* command to clear the [OPEN\_FAULT\_CHx] fault bits.

The [OPEN\_FAULT\_CHx] channel-fault bits can be masked independently by the [OPEN\_MASK\_CHx] bits. when the [OPEN\_MASK\_CHx] bit of any channel is set HIGH, the open-load fault on the specific channel is not reported to the [ANY\_OPEN\_FLAG] bit.

[ANY\_OPEN\_FLAG] is the indicator for open-load detectors. [ANY\_OPEN\_FLAG] can be masked by [OPEN\_MASK] to avoid pulling down the ERR open-drain output.

Figure 20. Open Fault Report Topology

### 7.3.5.5 Deactivated-Channel LED Open or Short Detection

Deactivating a channel by setting [CH\_ON\_MASKx] automatically enables detection of an off-state LED open load, short to the supply, or short to GND. If a fault is detected when the pullup is enabled, the respective fault register is set and the ERR open-drain output is pulled down.

To clear the fault, issue the *RESET\_STATUS* command, the same as for activated-state diagnostics. The faultmasking mechanism is also the same as for activated-state diagnostics.

If an application allows absolutely no current during the channel disabled state, disable the off-state LED openor-short detection feature using the [DIS\_OFF\_FAULT\_DIAG] bit.

There is a provision for pulling each channel up to SENSE to avoid a floating node during off-state. This function can be enabled by setting the [DIS\_PULL\_UP\_CHx] bit to HIGH. If any [DIS\_PULL\_UP\_CHx] bit is set HIGH, the [DIS\_PULL\_UP\_FLAG] bit is also set HIGH.

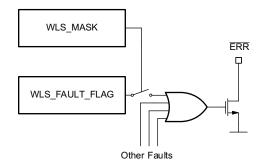

### 7.3.5.6 Weak LED Supply (WLS) Detection

The TLC6C5712-Q1 device provides weak-LED-supply detection to avoid reporting false faults due to supply failure. Implementation of weak-LED-supply detection is by monitoring the  $V_{(SENSE)}$  voltage using the internal threshold voltage  $V_{(WLS)}$  as a reference.

The default threshold  $V_{(WLS)}$  is set for a 5-V supply. If a 3.3-V LED supply is needed, the threshold voltage can be tuned to  $V_{(WLS OPT)}$  by setting the [WLS\_TH] bit HIGH.

when a fault is detected, the [WLS\_FAULT\_FLAG] bit is set if the [WLS\_MASK] masking bit is not active. The [WLS\_FAULT\_FLAG] bit remains latched even if the voltage recovers. To clear the fault, issue the *RESET\_STATUS* command.

Figure 21. Weak-LED-Supply Fault-Report Topology

#### 7.3.5.6.1 Adjacent-Pin Short Detection

On-demand adjacent-pin short detection is provided. This feature requires off-line diagnostics when the outputs are disabled. Otherwise, interruptions in normal operation and visual brightness glitches may result.

To start adjacent-pin short detection, set the [ADJ\_DIAG\_START] bit to HIGH. This bit automatically returns to LOW when the adjacent pin diagnostic procedure is finished.

After [ADJ\_DIAG\_START] has been set to HIGH and back to LOW, if any two adjacent pins are shorted, the [ADJ\_FLAG\_CHx] bit for the faulty channel is set HIGH. The microcontroller can read [ADJ\_FLAG\_CHx] to determine which two adjacent pins are shorted.

Deactivating all the channels by using the [CH\_ON\_MASKx] bits is suggested before starting adjacent-pin diagnostics.

when the [ADJ\_FLAG\_CHx] bit is set, it can only be cleared by issuing the RESET\_STATUS command.

#### 7.3.5.6.2 Force Error

To validate the ERR pulldown feedback without a real fault, the [FORCE\_ERR] <u>bit is</u> provided to enable an ERR force-down to simulate a faulty scenario. When [FORCE\_ERR] is HIGH, the ERR open-drain output is pulled down. To clear the fault, issue the *RESET\_STATUS* command.

#### 7.3.5.6.3 Reference Resistor Open and Short Detection

See the *Constant-Current Output* section.

#### 7.3.5.6.4 PWM Monitor

See the *PWM Input* section.

# TLC6C5712-Q1

SLVSCO9A - AUGUST 2015-REVISED AUGUST 2015

www.ti.com

### 7.3.6 Register Protection

To avoid an unintended change of critical registers, register locking and unlocking functions are provided. when the registers are locked, they cannot be overwritten until an unlock command is issued. When the registers are locked, they are still available for reading. Critical registers include:

| Dot correction register | <write_corrx>, x = 0–11</write_corrx>                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PWM mapping register    | <write_mapx>, x = 0–5</write_mapx>                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Masking registers       | <pre><write_ch_on_mask0> <write_ch_on_mask1> <write_short_mask0> <write_short_mask1> <write_short_gnd_mask0> <write_short_gnd_mask1> <write_open_mask0> <write_open_mask1> <write_open_mask1> <write_pwm_fault_mask> <write_error_mask></write_error_mask></write_pwm_fault_mask></write_open_mask1></write_open_mask1></write_open_mask0></write_short_gnd_mask1></write_short_gnd_mask0></write_short_mask1></write_short_mask0></write_ch_on_mask1></write_ch_on_mask0></pre> |

Miscellaneous register

### 7.3.6.1 Dot Correction Register Lock and Unlock

The <WRITE\_CORRx> dot correction register can be locked via the *LOCK\_CORR*command. When it is locked, no data in the <WRITE\_CORRx> registers can be altered. To unlock, issue the *UNLOCK\_CORR* command.

### 7.3.6.2 PWM Mapping Register Lock and Unlock

The <WRITE\_MAPx> dot correction register can be locked via the *LOCK\_MAP* command. When it is locked, no data in the <WRITE\_MAPx> registers can be altered. To unlock, issue the *UNLOCK\_MAP* command.

### 7.3.6.3 Masking Register Lock and Unlock

Masking registers can be locked via *LOCK\_MASK* command. When it is locked, no data in the masking registers listed in the *Register Protection* section can be altered. To unlock, issue the *UNLOCK\_MASK* command.

### 7.3.6.4 Miscellaneous Register Lock and Unlock

Miscellaneous registers can be locked via the *LOCK\_MISC* command. When it is locked, no data in the miscellaneous register listed in the *Register Protection* section can be altered. To unlock, issue the *UNLOCK\_MISC* command.

### 7.3.6.5 Lock Flag Indication

The status of all lock registers is stored in the [LOCK\_CORR\_FLAG], [LOCK\_MASK\_FLAG], [LOCK\_MAP\_FLAG] and [LOCK\_MISC\_FLAG] bits of the <READ\_STATUS1> register.

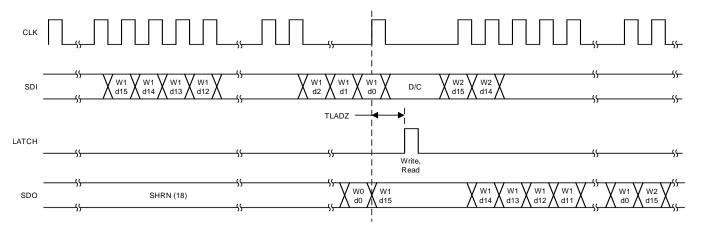

### 7.3.7 Serial Interface – SPI

The serial port is used to write data to, read diagnostic status from and configure settings of the TLC6C5712-Q1 device by transferring the input data to the desired address. During normal operation, an 8-bit serial address and 8-bit serial data are written into the 16-bit shift register. On an SCK rising-edge input, data is sampled. Data is shifted on a SCK falling edge and the shift registers advance, converting the 16 most-recent inputs to parallel signals on the LATCH rising edge.

At the rising edge on the LATCH input, a decoder which controls data transfer between shift and storage registers interprets the addresses. Depending on the address, valid data is conveyed from or to the appropriate latch or a command is interpreted. On latching a read address, data is read out from a storage register and shifted out of SDO to the microcontroller or daisy chained TLC6C5712-Q1 device.

Because for each address the TLC6C5712-Q1 device shifts out a fixed amount of data at the end of a write-read cycle, it is possible to send different address codes to each IC in a daisy chain.

For a number N of daisy-chained devices, a communication cycle comprises  $16 \times N$  SCK cycles with the corresponding data, transferred from shift registers to latches or from latches to shift registers on the rising edge of LATCH. The falling edge of LATCH indicates the end of a communication cycle.

The TLC6C5712-Q1 device supports multiple devices in cascaded daisy-chain mode. Each communication sequence must only have one LATCH rising edge, and therefore cannot be split into multiple smaller sequences.

Figure 22. Write-Access Data for a Typical Use Case

### 7.3.8 Thermal Information

TLC6C5712-Q1 has internal thermal shutdown (TSD) protection from device overheating. For continuous operation, the junction temperature should not exceed thermal-shutdown threshold. If TSD is not disabled by register and junction temperature exceeds thermal shutdown threshold, all outputs are turned off for protection. When the junction temperature falls below the thermal threshold minus hysteresis, outputs resume.

Use Equation 4 to estimate the device power.

$$P_{D(tot)} = V_{CC} \times I_{CC} + \sum_{x=0}^{11} \left( V_{(OUTx)} \times I_{(OUTx)} \right) - \frac{V_{(IREF)}}{R_{(IREF)}^2}$$

where

- P<sub>D(tot)</sub> = Total power dissipation of the device

- V<sub>(OUTx)</sub> = Voltage drop for channel x

- I<sub>(OUTx)</sub> = Average LED current for channel x

- V<sub>(IREF)</sub> = Reference voltage

- R<sub>(IREF)</sub> = Reference resistor

### 7.4 Device Functional Modes

### 7.4.1 Operation With V<sub>CC</sub> < 2.8 V (Power-On-Reset Threshold)

The TLC6C5712-Q1 device might not work properly with  $V_{CC}$  below 2.8 V. When POR is triggered, the device latches a POR fault and reports it through the ERR output. If  $V_{CC}$  continuous to drop, the content of the registers could be reset to their default value, with all outputs shutting down by default.

### 7.4.2 Operation With $V_{CC} \ge 2.8 V$ (Power-On-Reset Threshold)

The TLC6C5712-Q1 device is fully functional with  $V_{CC}$  at or above 2.8 V. The output current depends on the channel output voltage,  $V_{(OUTx)}$ . Given enough headroom for output transistors, the device should sink current as programmed. If the headroom voltage is not enough, the output current could be lower than programmed.

Copyright © 2015, Texas Instruments Incorporated

# 7.5 Register Maps

Table 2. Register Map

| Register Name         | Addr        | D7       | D6                  | D5               | D4                      | D3                        | D2              | D1                | D0              | Default |

|-----------------------|-------------|----------|---------------------|------------------|-------------------------|---------------------------|-----------------|-------------------|-----------------|---------|

| WRITE_MAP0            | 40h         | RESER    | VED                 |                  | PWM_MAP_CH1[2:0]        | I                         |                 | PWM_MAP_CH0[2:0]  |                 | 00h     |

| WRITE_MAP1            | 41h         | RESER    | VED                 |                  | PWM_MAP_CH3[2:0]        |                           |                 | PWM_MAP_CH2[2:0]  |                 | 00h     |

| WRITE_MAP2            | 42h         | RESER    | VED                 |                  | PWM_MAP_CH5[2:0]        |                           |                 | PWM_MAP_CH4[2:0]  |                 | 00h     |

| WRITE_MAP3            | 43h         | RESER    | VED                 |                  | PWM_MAP_CH7[2:0]        |                           |                 | PWM_MAP_CH6[2:0]  |                 | 00h     |

| WRITE_MAP4            | 44h         | RESER    | VED                 |                  | PWM_MAP_CH9[2:0]        |                           |                 | PWM_MAP_CH8[2:0]  |                 | 00h     |

| WRITE_MAP5            | 45h         | RESER    | VED                 |                  | PWM_MAP_CH11[2:0]       |                           |                 | PWM_MAP_CH10[2:0] |                 | 00h     |

| WRITE_CORR0           | 46h         |          |                     |                  | OU                      | FPUT_DC_CH0[7:0]          |                 |                   |                 | 00h     |

| WRITE_CORR1           | 47h         |          |                     |                  | OU                      | FPUT_DC_CH1[7:0]          |                 |                   |                 | 00h     |

| WRITE_CORR2           | 48h         |          |                     |                  | OU                      | FPUT_DC_CH2[7:0]          |                 |                   |                 | 00h     |

| WRITE_CORR3           | 49h         |          |                     |                  | OU                      | FPUT_DC_CH3[7:0]          |                 |                   |                 | 00h     |

| WRITE_CORR4           | 4Ah         |          |                     |                  | OU                      | FPUT_DC_CH4[7:0]          |                 |                   |                 | 00h     |

| WRITE_CORR5           | 4Bh         |          |                     |                  | OU                      | FPUT_DC_CH5[7:0]          |                 |                   |                 | 00h     |

| WRITE_CORR6           | 4Ch         |          |                     |                  | OU                      | FPUT_DC_CH6[7:0]          |                 |                   |                 | 00h     |

| WRITE_CORR7           | 4Dh         |          |                     |                  | OU                      | FPUT_DC_CH7[7:0]          |                 |                   |                 | 00h     |

| WRITE_CORR8           | 4Eh         |          | OUTPUT_DC_CH8[7:0]  |                  |                         |                           |                 |                   |                 | 00h     |

| WRITE_CORR9           | 4Fh         |          | OUTPUT_DC_CH9[7:0]  |                  |                         |                           |                 |                   |                 | 00h     |

| WRITE_CORR10          | 50h         |          | OUTPUT_DC_CH10[7:0] |                  |                         |                           |                 |                   |                 | 00h     |

| WRITE_CORR11          | 51h         |          |                     |                  | OUT                     | PUT_DC_CH11[7:0]          |                 |                   |                 |         |

| WRITE_CH_ON_MASK0     | 52h         | RESER    | VED                 | CH_ON_MASK5      | CH_ON_MASK4             | CH_ON_MASK3               | CH_ON_MASK2     | CH_ON_MASK1       | CH_ON_MASK0     | 3Fh     |

| WRITE_CH_ON_MASK1     | 53h         | RESER    | VED                 | CH_ON_MASK11     | CH_ON_MASK10            | CH_ON_MASK9               | CH_ON_MASK8     | CH_ON_MASK7       | CH_ON_MASK6     | 3Fh     |

| WRITE_SHORT_MASK0     | 54h         | RESER    | VED                 | SHORT_MASK_CH5   | SHORT_MASK_CH4          | SHORT_MASK_CH3            | SHORT_MASK_CH2  | SHORT_MASK_CH1    | SHORT_MASK_CH0  | 3Fh     |

| WRITE_SHORT_MASK1     | 55h         | RESER    | VED                 | SHORT_MASK_CH11  | SHORT_MASK_CH10         | SHORT_MASK_CH9            | SHORT_MASK_CH8  | SHORT_MASK_CH7    | SHORT_MASK_CH6  | 3Fh     |

| WRITE_SHORT_GND_MASK0 | 56h         | RESER    | VED                 | SG_MASK_CH5      | SG_MASK_CH4             | SG_MASK_CH3               | SG_MASK_CH2     | SG_MASK_CH1       | SG_MASK_CH0     | 3Fh     |

| WRITE_SHORT_GND_MASK1 | 57h         | RESER    | VED                 | SG_MASK_CH11     | SG_MASK_CH10            | SG_MASK_CH9               | SG_MASK_CH8     | SG_MASK_CH7       | SG_MASK_CH6     | 3Fh     |

| WRITE_OPEN_MASK0      | 58h         | RESER    | VED                 | OPEN_MASK_CH5    | OPEN_MASK_CH4           | OPEN_MASK_CH3             | OPEN_MASK_CH2   | OPEN_MASK_CH1     | OPEN_MASK_CH0   | 3Fh     |

| WRITE_OPEN_MASK1      | 59h         | RESER    | VED                 | OPEN_MASK_CH11   | OPEN_MASK_CH10          | OPEN_MASK_CH9             | OPEN_MASK_CH8   | OPEN_MASK_CH7     | OPEN_MASK_CH6   | 3Fh     |

| _                     | 5Ah–<br>5Fh |          |                     |                  |                         | RESERVED                  |                 |                   |                 | 00h     |

| WRITE_PWM_FAULT_MASK  | 60h         | RESER    | VED                 | PWM_FAULT_MASK5  | PWM_FAULT_MASK4         | PWM_FAULT_MASK3           | PWM_FAULT_MASK2 | PWM_FAULT_MASK1   | PWM_FAULT_MASK0 | 3Fh     |

| RESET_POR             | 61h         |          |                     |                  | RESET_POR c             | ommand is issued if data  | = 69h           |                   |                 | 00h     |

| RESET_STATUS          | 62h         |          |                     |                  | RESET_STATUS            | command is issued if dat  | a = 66h         |                   |                 | 00h     |

| SOFTWARE_POR          | 63h         |          |                     |                  | SOFTWARE_POF            | R command is issued if da | ta = 99h        |                   |                 | 00h     |

| WRITE_DIS_PULL_UP_0   | 64h         | RESER    | VED                 | DIS_PULL_UP_CH5  | DIS_PULL_UP_CH4         | DIS_PULL_UP_CH3           | DIS_PULL_UP_CH2 | DIS_PULL_UP_CH1   | DIS_PULL_UP_CH0 | 00h     |

| WRITE_DIS_PULL_UP_1   | 65h         | RESER    | VED                 | DIS_PULL_UP_CH11 | DIS_PULL_UP_CH10        | DIS_PULL_UP_CH9           | DIS_PULL_UP_CH8 | DIS_PULL_UP_CH7   | DIS_PULL_UP_CH6 | 00h     |

| WRITE_ERROR_MASK      | 66h         | REF_MASK | POR_MASK            | OPEN_MASK        | SHORT_MASK              | PWM_MASK                  | WLS_MASK        | PRE_TSD_MASK      | TSD_MASK        | 00h     |

| WRITE_MISC_CMD        | 67h         |          | RESERVE             | Ð                | DIS_OFF_FAULT_<br>DI AG | ADJ_DIAG_START            | SLOW_SLEW_RAT E | FORCE_ERR         | WLS_TH          | 00h     |

| LOCK_MAP              | 68h         |          |                     |                  | LOCK_MAP co             | mmand is issued if data = | = A5h           |                   |                 | 00h     |

| LOCK_CORR             | 69h         |          |                     |                  | LOCK_CORR of            | ommand is issued if data  | = 55h           |                   |                 | 00h     |

# Register Maps (continued)

|                       |             |      |                                             | Table            | 2. Register Ma    | o (continued)             |                 |                   |                 |         |  |  |

|-----------------------|-------------|------|---------------------------------------------|------------------|-------------------|---------------------------|-----------------|-------------------|-----------------|---------|--|--|

| Register Name         | Addr        | D7   | D6                                          | D5               | D4                | D3                        | D2              | D1                | D0              | Default |  |  |

| LOCK_MASK             | 6Ah         |      |                                             |                  | LOCK_MASK c       | ommand is issued if data  | = AAh           | L                 |                 | 00h     |  |  |

| LOCK_MISC             | 6Bh         |      |                                             |                  | UNLOCK_MISC       | command is issued if data | a = 5Ah         |                   |                 | 00h     |  |  |

| UNLOCK_MAP            | 6Ch         |      |                                             |                  | UNLOCK_MAP        | command is issued if data | = CCh           |                   |                 | 00h     |  |  |

| UNLOCK_CORR           | 6Dh         |      | UNLOCK_CORR command is issued if data = 33h |                  |                   |                           |                 |                   |                 |         |  |  |

| UNLOCK_MASK           | 6Eh         |      |                                             |                  | UNLOCK_MASK       | command is issued if data | a = 3Ch         |                   |                 | 00h     |  |  |

| UNLOCK_MISC           | 6Fh         |      |                                             |                  | UNLOCK_MISC       | command is issued if data | a = C3h         |                   |                 | 00h     |  |  |

| _                     | 70h–<br>7Fh |      | RESERVED                                    |                  |                   |                           |                 |                   |                 |         |  |  |

| READ_MAP0             | 80h         | RESE | RVED                                        |                  | PWM_MAP_CH1[2:0]  |                           |                 | PWM_MAP_CH0[2:0]  |                 | 00h     |  |  |

| READ_MAP1             | 81h         | RESE | RESERVED                                    |                  |                   |                           |                 | PWM_MAP_CH2[2:0]  |                 | 00h     |  |  |

| READ_MAP2             | 82h         | RESE | RVED                                        |                  | PWM_MAP_CH5[2:0]  |                           |                 | PWM_MAP_CH4[2:0]  |                 | 00h     |  |  |

| READ_MAP3             | 83h         | RESE | RVED                                        |                  | PWM_MAP_CH7[2:0]  |                           |                 | PWM_MAP_CH6[2:0]  |                 | 00h     |  |  |

| READ_MAP4             | 84h         | RESE | RVED                                        |                  | PWM_MAP_CH9[2:0]  |                           |                 | PWM_MAP_CH8[2:0]  |                 | 00h     |  |  |