TPS65381A-Q1

SLVSDJ1A-JULY 2016-REVISED MAY 2017

# TPS65381A-Q1 Multirail Power Supply for Microcontrollers in Safety-Relevant **Applications**

#### **Device Overview**

#### 1.1 **Features**

- Qualified for Automotive Applications

- AEC-Q100 Qualified With the Following Results:

- Device Temperature Grade 1: –40°C to +125°C **Ambient Operating Temperature**

- Device HBM ESD Classification Level H2

- Device CDM ESD Classification Level C3B

#### Multirail Power Supply Supporting Among **Others**

TI Hercules™ TMS570, C2000™, and Various Functional-Safety Architecture Microcontrollers

#### Supply Rails

- Input voltage range:

- 5.8 V to 36 V (CAN, I/O, MCU Core, and Sensor-Supply Regulators Functional)

- 4.5 V to 5.8 V (3.3 V I/O and MCU Core Regulators Functional)

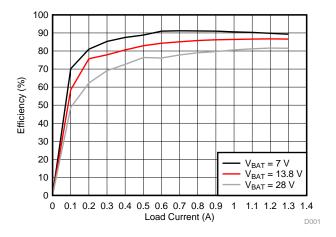

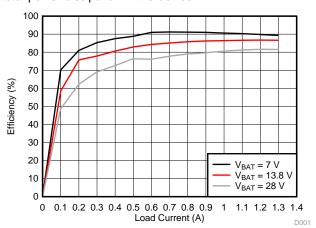

- 6-V Asynchronous Switch Mode Preregulator With Internal FET, 1.3-A Output Current

- 5-V (CAN) Supply Voltage, Linear Regulator With Internal FET, 300-mA Output Current

- 3.3-V or 5-V (MCU I/O) Voltage, Linear Regulator With Internal FET, 300-mA Output Current

- 0.8-V to 3.3-V Adjustable (MCU Core Voltage), Linear Regulator Controller With External FET

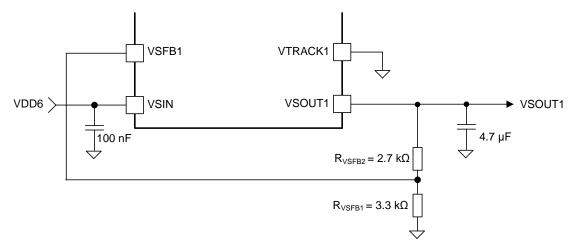

- 3.3-V to 9.5-V Adjustable Sensor Supply: Linear Tracking Regulator With Internal FET, 100-mA Output Current, and Protection Against Short-to-Supply and Short-to-Ground

- Charge Pump: Typically 12 V Above Battery Voltage

#### Power Supply and System Monitoring

- Independent Undervoltage and Overvoltage Monitoring on All Regulator Outputs, Battery Voltage, and Internal Supplies

- Independent Voltage References for Regulator References and Voltage Monitoring. Voltage-Monitoring Circuitry With Independent Bandgap Reference and Separate Supply Input Pin

- Self-Check on all Voltage Monitoring (Automatic During Power-Up and After Power-Up Initiated by External MCU)

- All Supplies With Internal FETs Protected With Current-Limit and Overtemperature Shutdown

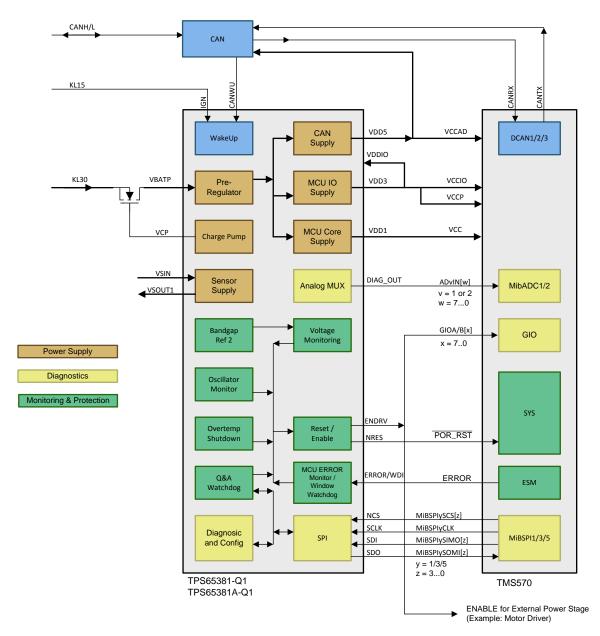

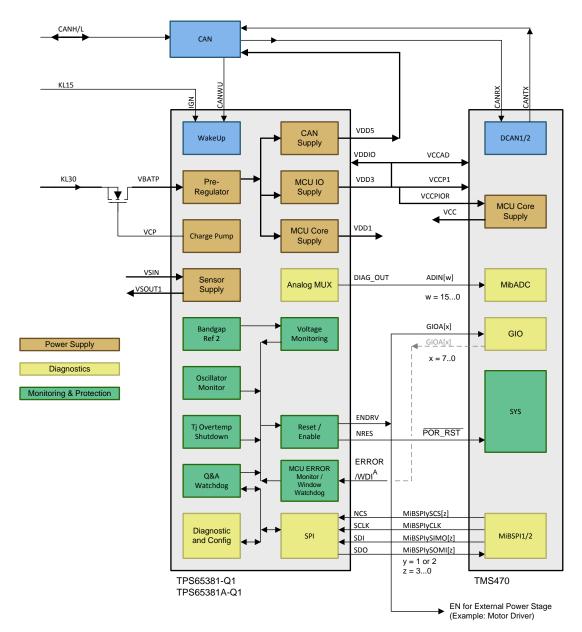

#### Microcontroller (MCU) Interface

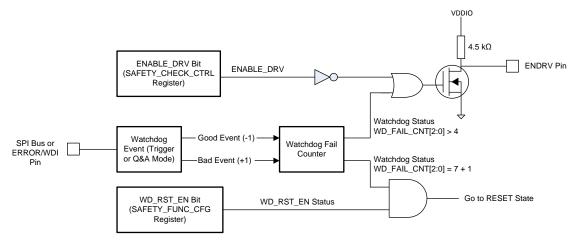

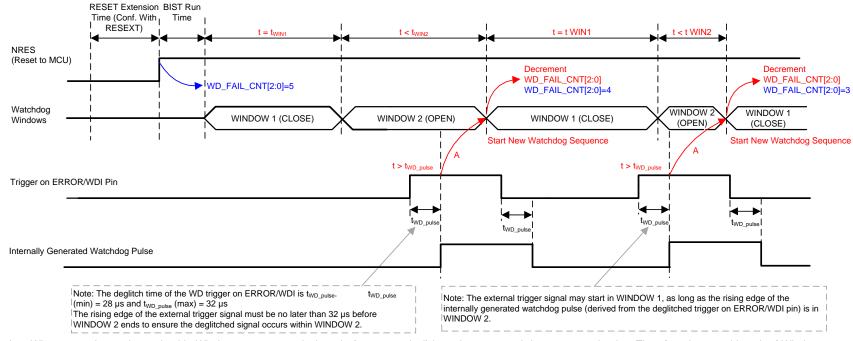

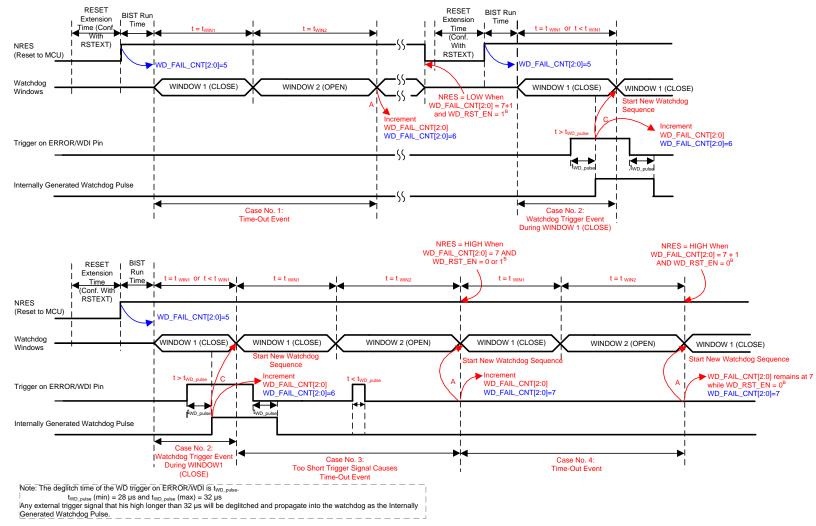

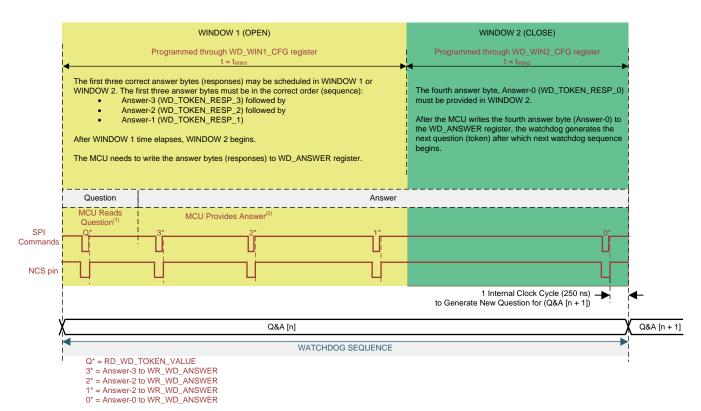

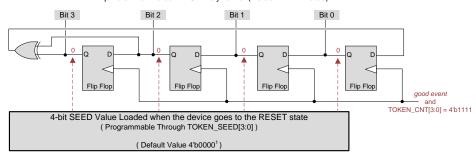

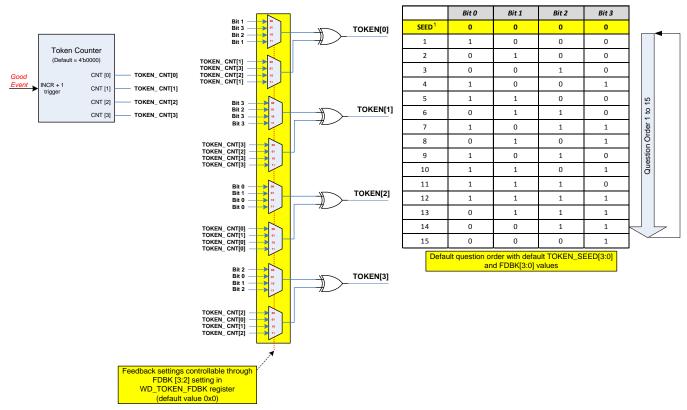

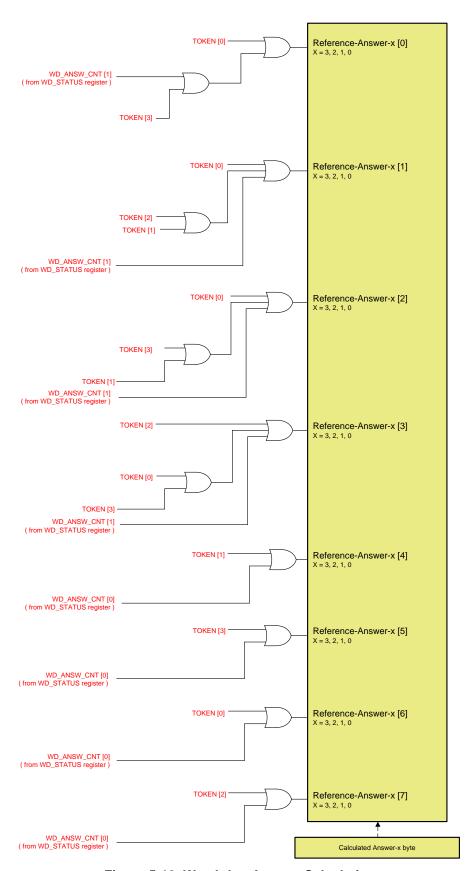

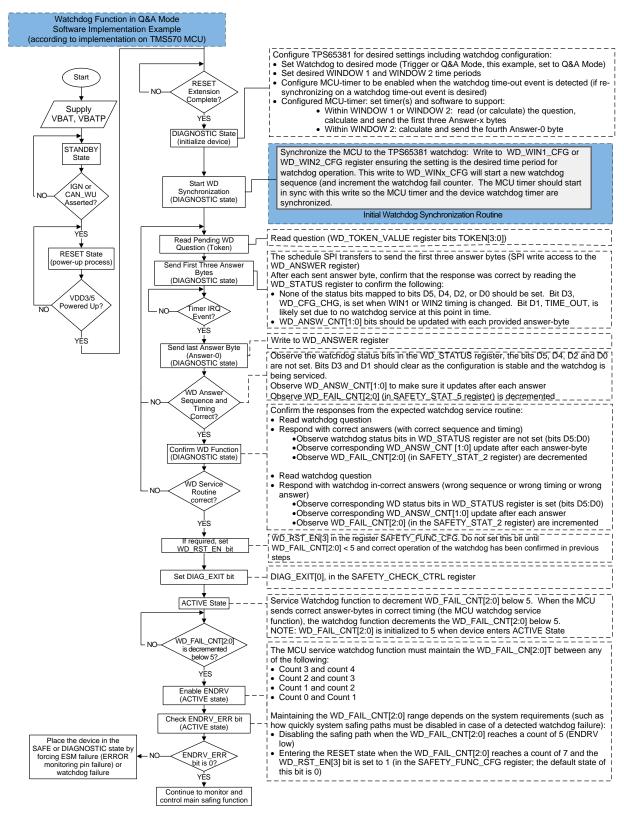

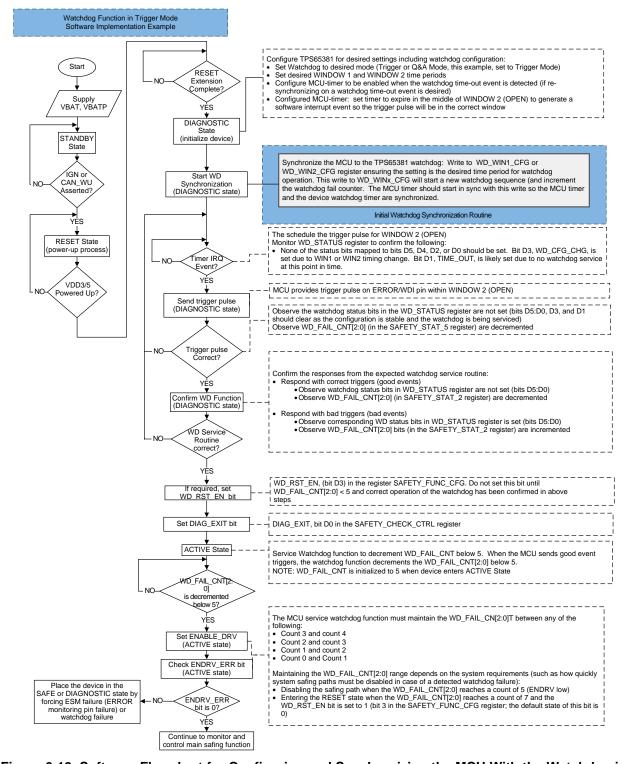

- Watchdog: Trigger Mode (OPEN/CLOSE) Window) or Question and Answer Mode

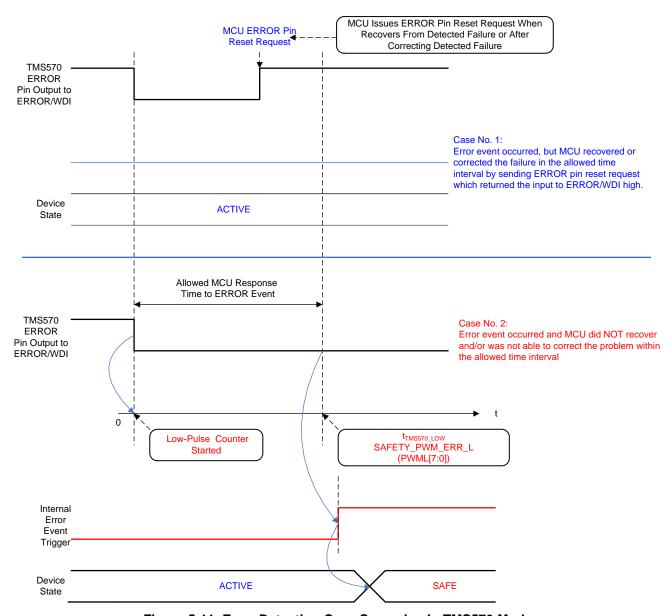

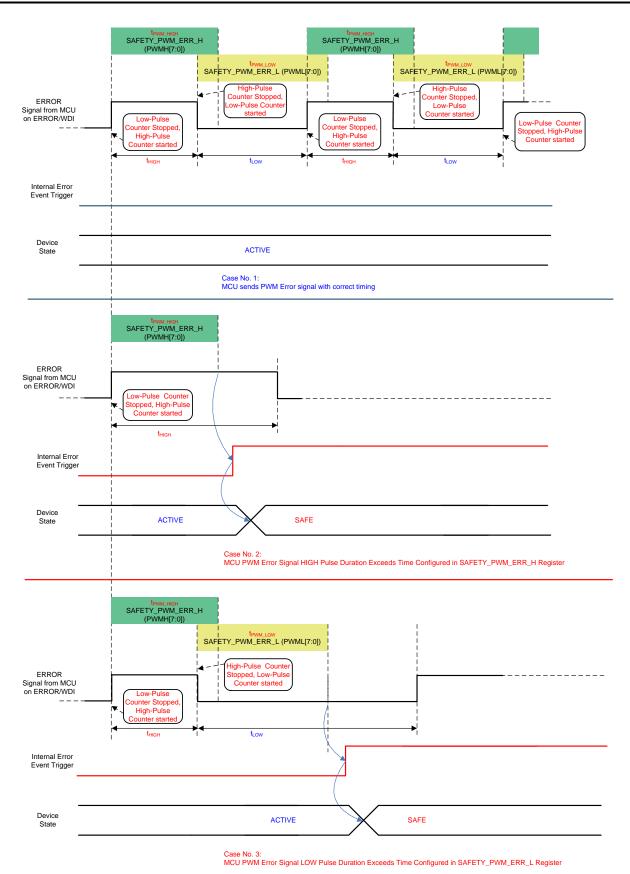

- MCU Error-Signal Monitor For Lock-Step Dual-Core MCUs Including Hercules™ TMS570, C2000™, and Various Functional-Safety Architecture MCUs Using Pulse-Width Modulation (PWM) Error Output

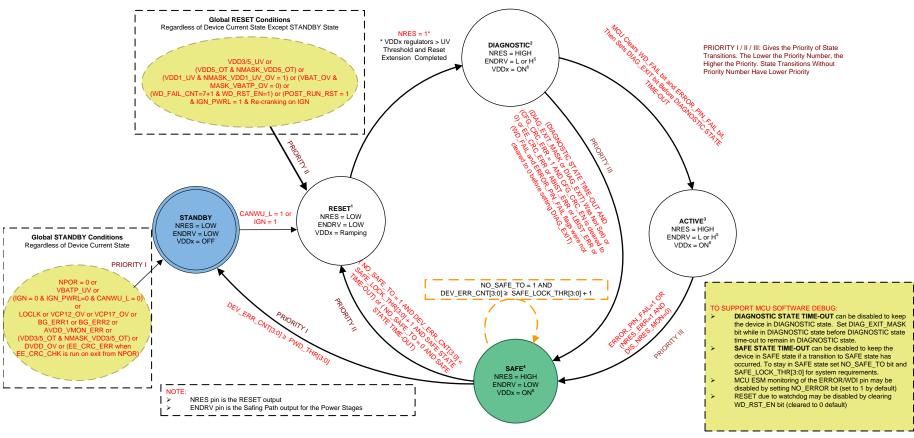

- DIAGNOSTIC State for Performing Device Self-Tests, Diagnostics, and External Interconnect Checks

- SAFE State for Device and System Protection on Error Event Detection

- Clock Monitor for Internal Oscillator

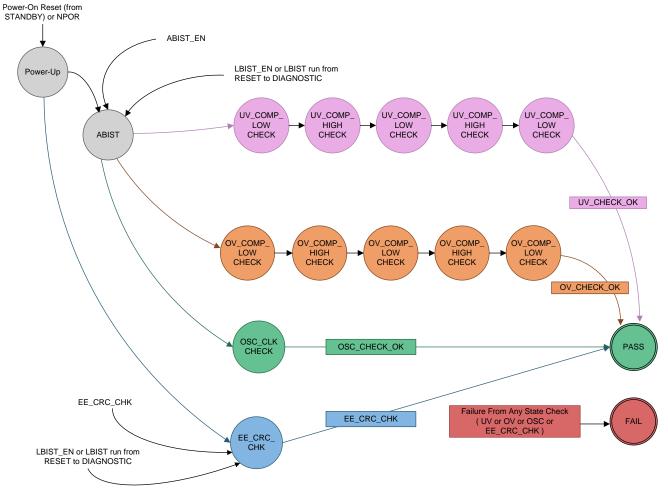

- Self-Tests for Analog- and Digital-Critical Circuits Executed With Every Device Power Up or Activated by MCU in DIAGNOSTIC State

- CRC on Nonvolatile Memory, Device and Configuration Registers

- Reset Circuit and Output Pin for MCU

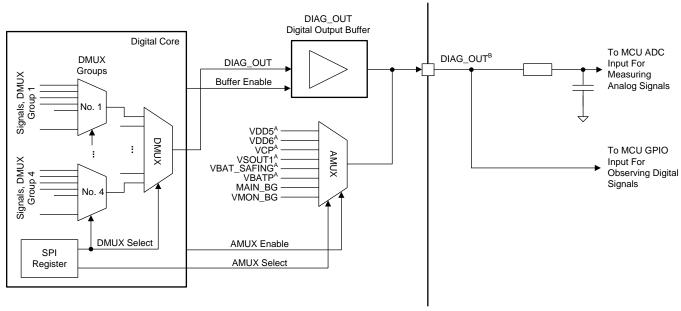

- Diagnostic Output Pin Allowing MCU to Observe Through a Multiplexer Internal Analog and Digital Signals of the Device

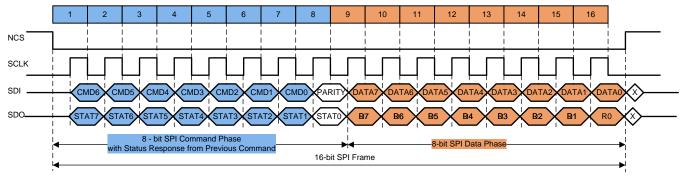

#### Serial Peripheral Interface (SPI)

- Configuration Registers

- Watchdog Question and Answers

- Diagnostic Status Readout

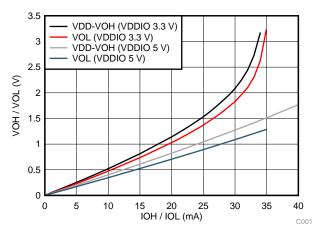

- Compliant With 3.3-V and 5-V Logic Levels

- Enable Drive Output for Disabling Safing-Path or External Power-Stages on Detected System-Failure

- Wakeup Through IGNITION Pin or CAN **WAKEUP Pin**

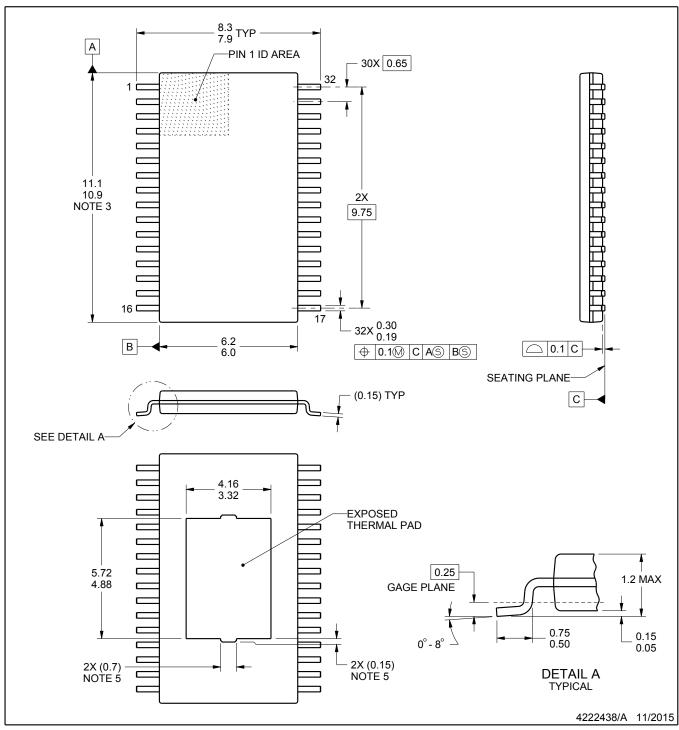

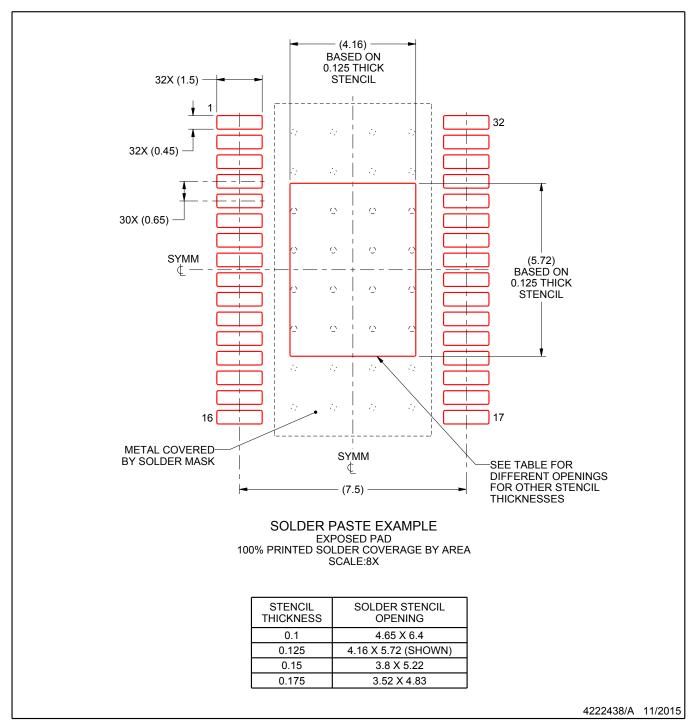

- Package: 32-Pin HTSSOP PowerPAD™ IC **Package**

# 1.2 Applications

#### Safety Automotive Applications

- Power Steering: Electrical Power Steering (EPS) and Electro Hydraulic Power Steering (EHPS)

- Braking: Anti-Lock Brake System (ABS),

Electronic Stability Control (ESC), and Electric

Parking Brake

- Advanced Driver Assistance Systems (ADAS)

- Suspension

#### Industrial Safety Applications

- Safety Programmable-Logic Controllers (PLCs)

- Safety I/O Control Modules

- Test and Measurement

- Railway and Subway Signal Control and Safety Modules

- Elevator and Escalator Safety Control

- Wind Turbine Control

#### 1.3 Description

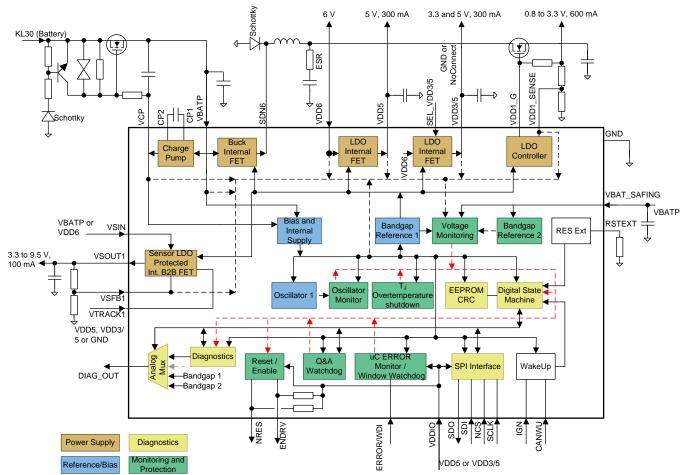

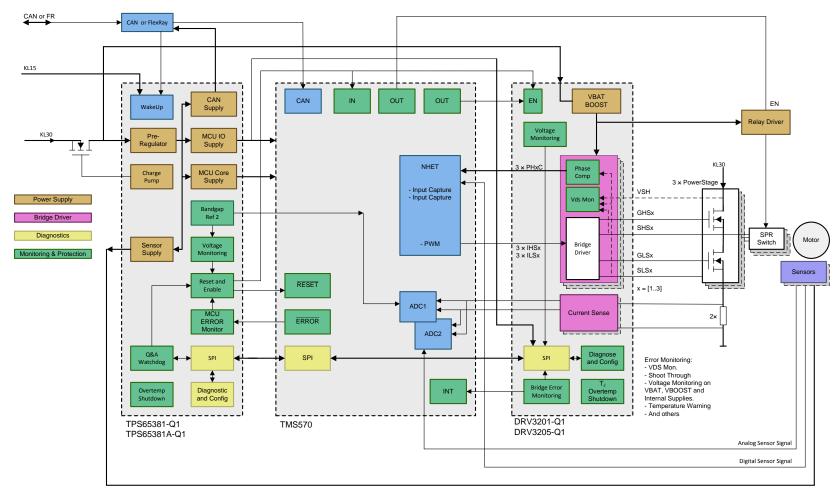

The TPS65381A-Q1 device is a multirail power supply designed to supply microcontrollers (MCUs) in safety-relevant applications, such as those found in automotive and industrial markets. The device supports Texas Instruments' Hercules™ TMS570 MCU and C2000™ MCU families, and various other MCUs with dual-core lockstep (LS) or loosely-coupled architectures (LC).

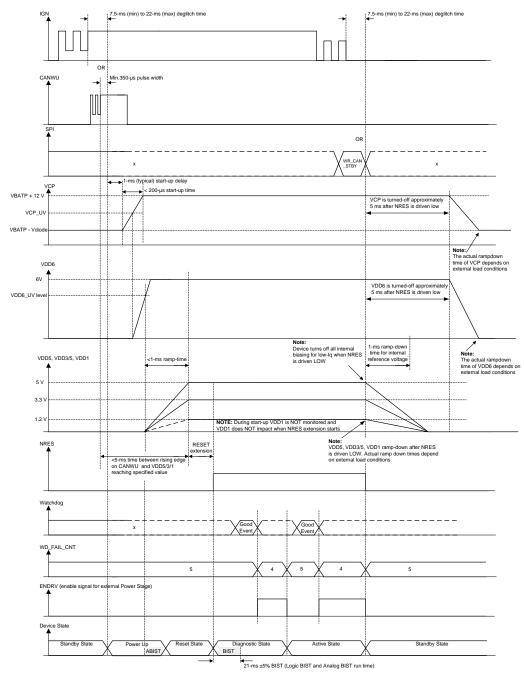

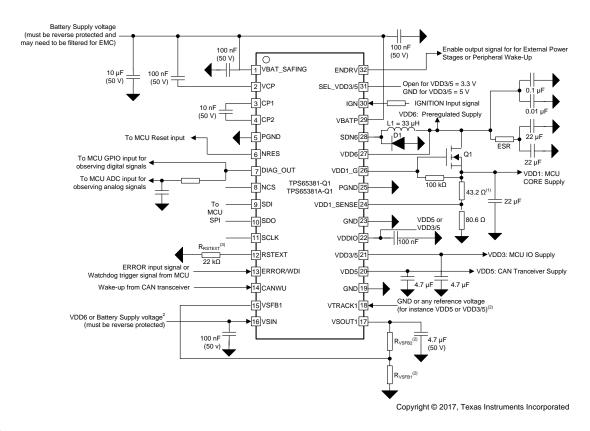

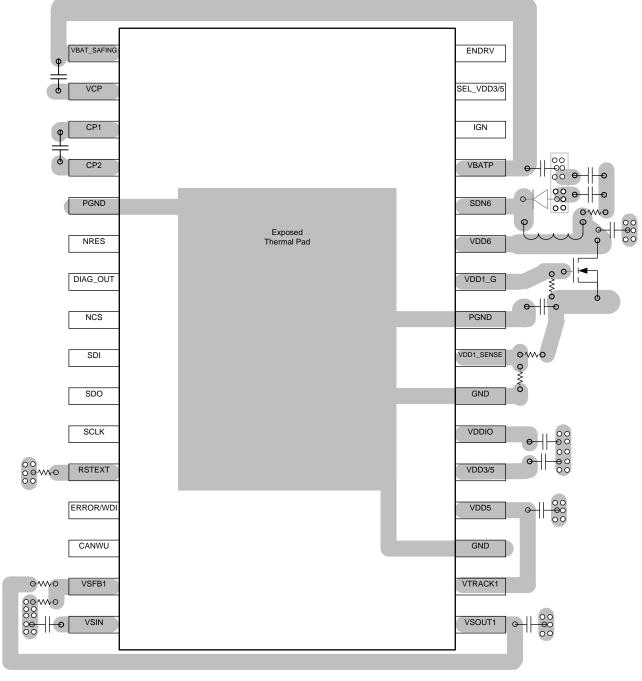

The TPS65381A-Q1 device integrates multiple supply rails to power the MCU, controller area network (CAN), or FlexRay, and an external sensor. An asynchronous-buck switch-mode power-supply converter with an internal FET converts the input supply (battery) voltage to a 6-V preregulator output. This 6-V preregulator supplies the other regulators. The device supports wakeup from IGNITION or wakeup from the CAN transceiver.

The integrated, fixed 5-V linear regulator with internal FET can be used for a CAN or FlexRay transceiver supply for example. A second linear regulator, also with an internal FET, regulates to a selectable 5-V or 3.3-V output which, for example, can be use for the MCU I/O voltage.

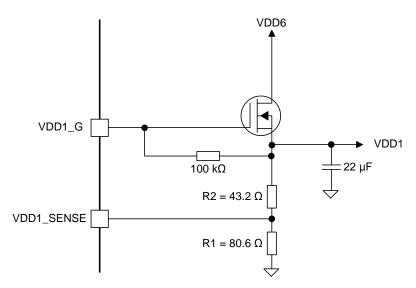

The TPS65381A-Q1 device includes an adjustable linear-regulator controller, requiring an external FET and resistor divider, that regulates to an adjustable voltage of between 0.8 V and 3.3 V which may be used for the MCU core supply.

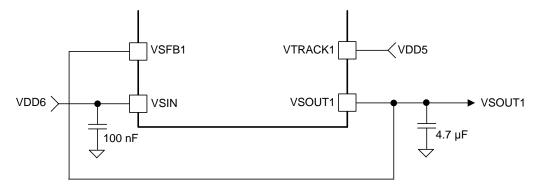

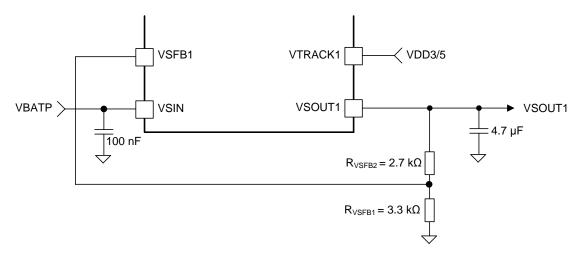

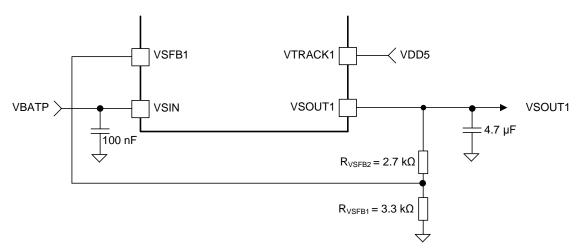

The integrated sensor supply can be run in tracking mode or adjustable output mode and includes short-to-ground and short-to-battery protection. Therefore, this regulator can power a sensor outside the module or electronic control unit (ECU).

The integrated charge pump provides overdrive voltage for the internal regulators. The charge pump can also be used in a reverse-battery protection circuit by using the charge-pump output to control an external NMOS transistor. This solution allows for a lower minimum-battery-voltage operation compared to a traditional reverse-battery blocking diode when the device must be operational at the lowest possible supply voltages.

The device monitors undervoltage and overvoltage on all regulator outputs, battery voltage, and internal supply rails. A second bandgap reference, independent from the main bandgap reference, is used for the undervoltage and overvoltage monitoring, to avoid any drifts in the main bandgap reference from being undetected. In addition, regulator current-limits and temperature protections are implemented.

The TPS65381A-Q1 device has monitoring and protection functions, which include the following: watchdog with trigger and *question and answer* modes, MCU error-signal monitor, clock monitoring on internal oscillators, self-check on the clock monitor, cyclic redundancy check (CRC) on nonvolatile memory, a diagnostic output pin allowing the MCU to observe internal analog and digital signals of the device, a reset circuit and output pin for the MCU, and an enable drive output to disable the safing-path or external-power stages on detected faults. A built-in self-test (BIST) monitors the device functionality automatically at power-up. A dedicated DIAGNOSTIC state allows the MCU to check TPS65381A-Q1 monitoring and protection functions.

The TPS65381A-Q1 device is offered in a 32-pin HTSSOP PowerPAD package.

## Device Information<sup>(1)</sup>

| PART NUMBER  | PACKAGE     | BODY SIZE (NOM)    |

|--------------|-------------|--------------------|

| TPS65381A-Q1 | HTSSOP (32) | 11.00 mm × 6.20 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

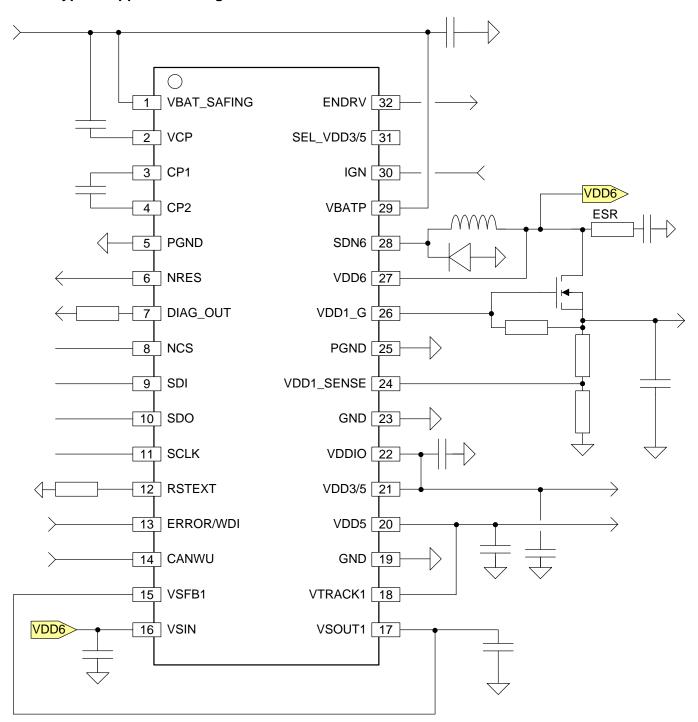

## 1.4 Typical Application Diagram

Copyright © 2016, Texas Instruments Incorporated

Figure 1-1. Typical Application Diagram

www.ti.com

# 2 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Chang | ges from Original (July 2016) to Revision A | Page |

|-------|---------------------------------------------|------|

| •     | Released the full version of the data sheet | 2    |

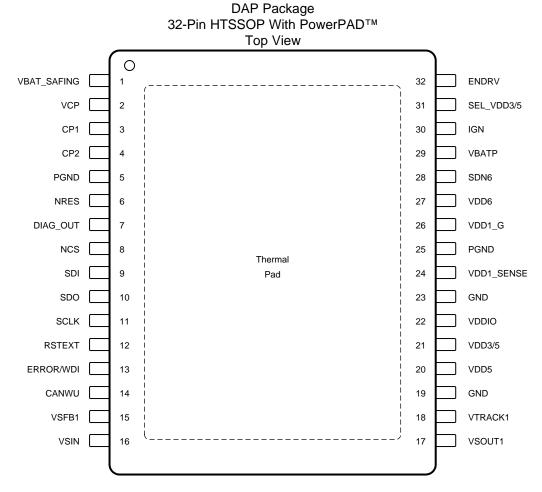

# **Pin Configuration and Functions**

**TRUMENTS**

The pin configuration drawing in this section is not to scale. For package dimensions, see the mechanical data in Section 10.

**Pin Functions**

|     | PIN         | TVDE | DECORIDEION                                                                                                                     |

|-----|-------------|------|---------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME        | TYPE | DESCRIPTION                                                                                                                     |

| 1   | VBAT_SAFING | PWR  | Battery (supply) input for monitoring (VMON) and BG2 functions (must be reverse protected), should be connected to VBATP        |

| 2   | VCP         | PWR  | Charge-pump output voltage                                                                                                      |

| 3   | CP1         | PWR  | Charge-pump external capacitor, high-voltage side                                                                               |

| 4   | CP2         | PWR  | Charge-pump external capacitor, low-voltage side                                                                                |

| 5   | PGND        | GND  | Ground (power)                                                                                                                  |

| 6   | NRES        | 0    | Cold reset output signal for the microcontroller (MCU) (active-low, internal pullup, open drain output)                         |

| 7   | DIAG_OUT    | 0    | Diagnostic output pin for diagnostic MUX. Internal analog (AMUX) and digital (DMUX) signal connection to MCU ADC and digital IO |

| 8   | NCS         | I    | SPI chip select (active-low, internal pullup)                                                                                   |

| 9   | SDI         | I    | SPI serial data IN (internal pulldown)                                                                                          |

| 10  | SDO         | 0    | SPI serial data OUT                                                                                                             |

| 11  | SCLK        | I    | SPI clock (internal pull down)                                                                                                  |

| 12  | RSTEXT      | I    | Configuration pin to set reset extension time through a resistor to GND                                                         |

# Pin Functions (continued)

|     | PIN         |     | DECODIONION                                                                                                                                                                             |

|-----|-------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME        |     | DESCRIPTION                                                                                                                                                                             |

| 13  | ERROR/WDI   | I   | Error input signal from the MCU while using the MCU ESM (with the watchdog in Q&A Mode), trigger input for the watchdog in trigger mode (MCU ESM not used). This pin is edge triggered. |

| 14  | CANWU       | I   | Wake-up input from CAN transceiver, other transceiver or other source. Wake-up request latched with CANWU_L. (internal pulldown)                                                        |

| 15  | VSFB1       | 1   | Feedback input reference for sensor supply regulator (VSOUT1)                                                                                                                           |

| 16  | VSIN        | PWR | Input supply voltage for the sensor-supply regulator (VSOUT1)                                                                                                                           |

| 17  | VSOUT1      | PWR | Output voltage for the VSOUT1 sensor-supply regulator                                                                                                                                   |

| 18  | VTRACK1     | I   | Tracking input reference for sensor-supply regulator (VSOUT1) (internal pulldown)                                                                                                       |

| 19  | GND         | GND | Ground (analog)                                                                                                                                                                         |

| 23  | GND         | GND | Ground (analog)                                                                                                                                                                         |

| 20  | VDD5        | PWR | VDD5 regulator output voltage                                                                                                                                                           |

| 21  | VDD3/5      | PWR | VDD3/5 regulator output voltage                                                                                                                                                         |

| 22  | VDDIO       | PWR | I/O supply input for pins to and from the MCU                                                                                                                                           |

| 24  | VDD1_SENSE  | I   | Reference input for VDD1 regulator (feedback) and input for UV/OV monitoring of VDD1 regulator                                                                                          |

| 25  | PGND        | GND | Ground (power)                                                                                                                                                                          |

| 26  | VDD1_G      | 0   | Gate drive of external FET for VDD1 regulator                                                                                                                                           |

| 27  | VDD6        | PWR | VDD6 switch mode regulator feedback input and supply input for integrated VDD5 and VDD3/5 regulators                                                                                    |

| 28  | SDN6        | PWR | Switching node for VDD6 switch mode regulator                                                                                                                                           |

| 29  | VBATP       | PWR | Battery (supply) voltage (must be reverse protected), main power supply input for device                                                                                                |

| 30  | IGN         | 1   | Wake-up input from ignition (key) or other source (internal pulldown)                                                                                                                   |

| 31  | SEL_VDD3/5  | I   | Input selects voltage level for VDD3/5 regulator (SEL_VDD3/5 pin open: 3.3-V regulation from VDD3/5; SEL_VDD3/5 pin to GND: 5-V regulation from VDD3/5)                                 |

| 32  | ENDRV       | 0   | Enable output signal for peripherals (for example, motor-driver IC), safing path output (internal pullup, open drain output)                                                            |

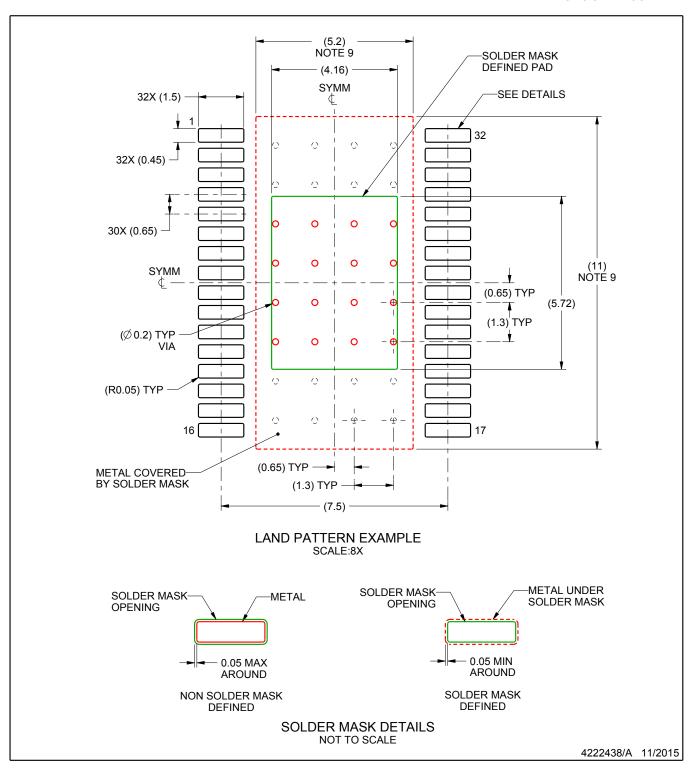

|     | Thermal pad |     | Place thermal vias to large ground plane and connect to GND and PGND pins.                                                                                                              |

## 4 Specifications

## 4.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)(1)(2)

| POS   |                                                                                                                                                         |                                                            | MIN  | MAX                                    | UNIT |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------|----------------------------------------|------|

| M1.1  | Protected-battery voltage                                                                                                                               | VBATP, VBAT_SAFING, VSIN                                   | -0.3 | 40                                     | V    |

| M1.2  | Charge-pump voltage                                                                                                                                     | VCP, CP1 <sup>(3)</sup>                                    | -0.3 | lesser<br>of<br>VBATP<br>+ 16 or<br>52 | V    |

| M1.3  | Charge-pump pumping capacitor voltage                                                                                                                   | CP2                                                        | -0.3 | -0.3 40                                |      |

| M1.3a | Charge-pump overdrive voltage                                                                                                                           | VCP <sup>(3)</sup> -VBATP                                  | -0.3 | 16                                     | V    |

| M1.4  | VDD6 switching-node voltage                                                                                                                             | SDN6                                                       | -0.3 | 40                                     | V    |

| M1.5  | VDD6 output voltage                                                                                                                                     | VDD6                                                       | -0.3 | 40                                     | V    |

| M1.6  | VDD5 output voltage                                                                                                                                     | VDD5                                                       | -0.3 | 7                                      | V    |

| M1.7  | VDD3/5 output voltage                                                                                                                                   | VDD3/5                                                     | -0.3 | 7                                      | V    |

| M1.8  | VDD1_G voltage                                                                                                                                          | VDD1_G                                                     | -0.3 | 15                                     | V    |

| M1.10 | VDD1_SENSE voltage                                                                                                                                      | VDD1_SENSE                                                 | -0.3 | 7                                      | V    |

| M1.11 | Sensor supply tracking voltage                                                                                                                          | VTRACK1                                                    | -0.3 | 40                                     | V    |

| M1.12 | Sensor supply output and feedback voltage                                                                                                               | VSOUT1, VSFB1 <sup>(4)</sup>                               | -2   | 18                                     | ٧    |

| M1.14 | Analog/digital reference output voltage                                                                                                                 | DIAG_OUT                                                   | -0.3 | 7                                      | ٧    |

| M1.15 | Logic I/O voltage                                                                                                                                       | VDDIO, ERROR/WDI, ENDRV, NRES, NCS, SDI, SDO, SCLK, RSTEXT | -0.3 | 7                                      | V    |

| M1.16 | tensor supply tracking voltage VTRA sensor supply output and bedback voltage VSOU canalog/digital reference output oltage VDDIG SCLK SEL_VGN wakeup IGN | SEL_VDD3/5                                                 | -0.3 | 40                                     | V    |

| M1.17 | IGN wakeup                                                                                                                                              | IGN                                                        | -7   | 40                                     | V    |

| M1.18 | CAN wakeup                                                                                                                                              | CANWU                                                      | -0.3 | 40                                     | V    |

| M1.19 | Operating virtual junction temperate                                                                                                                    | ure, T <sub>J</sub>                                        |      | 150                                    | °C   |

|       | Storage temperature, T <sub>stg</sub>                                                                                                                   |                                                            | -65  | 150                                    | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 4.2 ESD Ratings

| POS.  |                                            |                                              |                                                         |                                            |       |  |  |

|-------|--------------------------------------------|----------------------------------------------|---------------------------------------------------------|--------------------------------------------|-------|--|--|

| M1.21 | V <sub>(ESD)</sub> Electrostatic discharge |                                              | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup> | All pins except VSOUT1 (17) and VSFB1 (15) | ±2000 |  |  |

| M1.20 |                                            | numan body model (nbw), per AEC Q100-002     | On sensor supply pins VSOUT1 (17) and VSFB1 (15)        | ±4000                                      | V     |  |  |

| M1.22 |                                            |                                              | Observed devices are del (ODM), and AEO 0400 044        | Corner pins (1, 16, 17, and 32)            | ±750  |  |  |

| M1.23 |                                            | Charged device model (CDM), per AEC Q100-011 | All pins                                                | ±500                                       |       |  |  |

(1) AEC Q100-002 indicates that HBM stressing is done in accordance with the ANSI/ESDA/JEDEC JS-001 Specification.

<sup>(2)</sup> All voltage values are with respect to the network ground pin unless otherwise noted.

<sup>(3)</sup> VCP and CP1 are output pins, no external voltage should be applied to these pins. Absolute Maximum ratings for these pins are what may appear on the pins.

<sup>(4)</sup> VSOUT1 is connected to VSFB1 directly (for unity gain) or through resistor divider (tracking mode gain or non-tracking mode output voltage adjusting). In case of a short to supply fault, the voltage on VSOUT1 is equal to the supply to the device (VBATP, VBAT\_SAFING, and VSIN where VSIN is connected to VBATP as it's supply instead of VDD6) and VSFB1 voltage will follow VSOUT1 based on the use case, directly (for unity gain) or via resistor divider (tracking mode gain or non-tracking mode output voltage adjusting).

## 4.3 Recommended Operating Conditions

Over operating temperature range and with respect to the GND and PGND (GND = PGND) pins (unless otherwise noted)

| POS    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | MIN | MAX                | UNIT |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|------|

| M1.20a | Operating ambient temperature, T <sub>A</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -40 | 125                | °C   |

| R1.1   | Minimum input supply voltage on VBATP for initial power up (POS 6.2, VBATP_UV <sub>on</sub> ) <sup>(1)(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     | 5.8 <sup>(3)</sup> | V    |

| R1.2   | <ul> <li>Input supply voltage on VBATP (1)(2)(4)</li> <li>To support operation when VBATP is between 5.8 V and 7 V, the device remains functional. Some rails can be in dropout or undervoltage depending on actual input supply and the configuration of the specific regulator.</li> <li>VDD6 can be in dropout mode (100% duty cycle)</li> <li>VDD3/5 configured for 5-V output can be in dropout. If the output reaches VDD3/5_UV threshold, the device transitions to the RESET state because of a VDD3/5 undervoltage event. If VDD3/5 is configured for 3.3-V output it remains functional.</li> <li>VDD5 can be in dropout. If output reaches the VDD5_UV threshold, the device indicates the undervoltage event through the VDD5_UV status bit.</li> <li>VSOUT1 can be in dropout depending on configuration. If output reaches VSOUT1_UV threshold, the device indicates the undervoltage event through the VSOUT1_UV status bit.</li> </ul>                                                                  | 5.8 | 34 <sup>(5)</sup>  | ٧    |

| R1.3   | <ul> <li>Input supply voltage on VBATP after initial power up, functional operation during low input supply voltage events, (POS 6.1, VBATP_UV<sub>off</sub>):<sup>(1)(6)</sup></li> <li>The device remains functional. Some rails can be in dropout or undervoltage depending on actual input supply and the configuration of the specific regulator.</li> <li>VDD6 is in dropout mode (100% duty cycle).</li> <li>VDD3/5 configured for 5-V output can be in dropout. If the output reaches VDD3/5_UV threshold, the device transitions to the RESET state because of a VDD3/5 undervoltage event. If VDD3/5 is configured for 3.3-V output it remains functional.</li> <li>VDD5 can be in dropout. If the output reaches VDD5_UV threshold, the device indicates the undervoltage event through the VDD5_UV status bit.</li> <li>VSOUT1 may be in dropout depending on configuration, if output reaches VSOUT1_UV threshold the device indicates the undervoltage event through the VSOUT1_UV status bit.</li> </ul> | 4.5 | 5.8                | V    |

| R1.4   | VDDIO supply-voltage range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3.3 | 5                  | ٧    |

| R1.5   | Current consumption in standby mode (all regulator outputs disabled) IGN = 0 V, CANWU = 0 V, 5.8 V $\leq$ VBAT $\leq$ 20 V for T <sub>J</sub> $<$ 85°C or 5.8 V $\leq$ VBAT $\leq$ 14 V tor T <sub>J</sub> = 125°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     | 75                 | μΑ   |

- (1) VBATP should be connected to VBAT\_SAFING.

- (2) VBAT\_SAFING has a supply high enough to power the VMON block and internal rail AVDD\_VMON above AVDD\_VMON\_UV.

- (3) The device may power up when VBATP is less than 5.8 V, but it will always power up when VBATP is 5.8V or greater, while VBAT\_SAFING has a supply high enough to power the VMON block and internal rail AVDD\_VMON above AVDD\_VMON\_UV.

- (4) Under slow VBAT ramp-down and when VDD3/5 rail is configured as a 5-V rail, the NRES output can be pulled low when VBAT is at approximately 6.3 V. This occurs because of an undervoltage transient on the VDD3/5 rail.

Under slow VBAT ramp-up and when VDD3/5 rail is configured as a 5-V rail, the NRES output can be pulled low when VBAT is at approximately 6.6 V. This occurs because of an undervoltage transient on VDD3/5 rail. Under similar conditions, undervoltage transients are observed on VDD5 and VSOUT1 rails (refer to Device Behavior Under Slow VBAT Ramp-Up and Ramp-Down).

- (5) The recommended maximum operating voltage for VBATP and VBAT\_SAFING is listed as 34 V, just below the overvoltage detection thresholds for VBATP, VBATP\_OV<sub>rise</sub> and VBATP\_OV<sub>fall</sub>. TI recommends enabling overvoltage detection on VBATP (default is enabled, MASK\_VBATP\_OV = 0). TI also recommends evaluating the thermal and power dissipation of the device in the application and ensure the design has adequate thermal management for operation at the necessary supply voltage level.

- (6) The device will remain on if VBATP drops from 5.8V down to VBATP\_UV<sub>off</sub> threshold or another voltage monitor detects an undervottage on a specific rail and changes the device state. VBAT\_UV<sub>off</sub> can be detected at 4.5 V but could be detected as low as 4.2 V. VBAT\_SAFING has a supply high enough to power the VMON block and internal rail AVDD\_VMON above AVDD\_VMON\_UV.

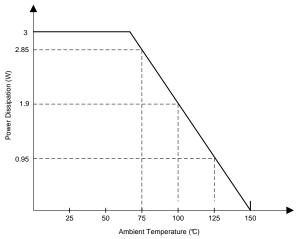

#### 4.4 Thermal Information

|                        | THERMAL METRIC <sup>(1)</sup>                | TPS65381A-Q1 DAP (HTSSOP) | UNIT |

|------------------------|----------------------------------------------|---------------------------|------|

|                        |                                              | 32 PINS                   |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 26.3                      | °C/W |

| $R_{\theta JC(top)}$   | Junction-to-case (top) thermal resistance    | 14.1                      | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 6                         | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 0.2                       | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 6.2                       | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 0.5                       | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

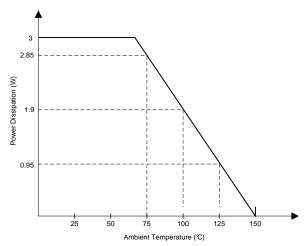

- (1) In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature (T<sub>A</sub>max) is dependent on the maximum-operating junction temperature (T<sub>J</sub>max), the maximum power dissipation of the device in the application (P<sub>D</sub>max), and the junction-to-ambient thermal resistance of the part/package in the application (R<sub>0JA</sub>), as given by the following equation: T<sub>A</sub>max = T<sub>J</sub>max (R<sub>0JA</sub> × P<sub>D</sub>max).

- (2) Maximum power dissipation is a function of  $T_J$ max,  $R_{\theta JA}$ , and  $T_A$ . The maximum-allowable power dissipation at any allowable ambient temperature is  $P_D = (T_J$ max  $T_A) / R_{\theta JA}$ .

Figure 4-1. Derating Profile for Power Dissipation Based on High-K JEDEC PCB

#### 4.5 Electrical Characteristics

Over operating ambient temperature  $T_A = -40^{\circ}\text{C}$  to the maximum-operating junction temperature  $T_J = 150^{\circ}\text{C}$ , and with VBATP = VBAT\_SAFING in the recommended operating range (see R1.2 in Section 4.3) (unless otherwise noted)

| POS   |                         | PARAMETER                                                                                                 | TEST CONDITIONS                                                                                                                                                                                                                             | MIN               | TYP  | MAX  | UNIT |

|-------|-------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|------|------|

| VDD6- | BUCK WITH INT           | FERNAL FET                                                                                                |                                                                                                                                                                                                                                             |                   |      |      |      |

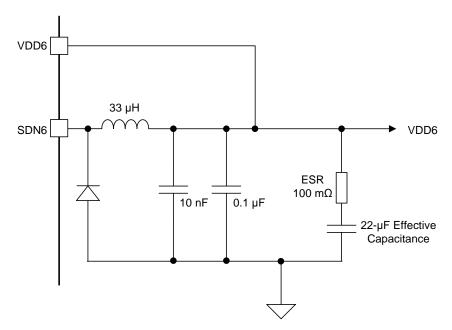

| AN    | C <sub>VDD6</sub>       | Value of output ceramic capacitor <sup>(1)</sup>                                                          | ESR range 100 m $\Omega$ to 300 m $\Omega^{(2)}$                                                                                                                                                                                            | 22                |      | 47   | μF   |

| AN    | L <sub>VDD6</sub>       | Value of inductor                                                                                         |                                                                                                                                                                                                                                             | 22                | 33   |      | μH   |

| 1.1   | VDD6                    | VDD6 output voltage                                                                                       | Average DC value excluding ripple and load transients, VBAT > $7 \text{ V}$ , $0 < \text{I}_{\text{VDD6}} < 1.3 \text{ A}$ , including dc line and load regulation, temperature drift, and long-term drift where VBAT = VBATP = VBAT_SAFING | 5.4               | 6    | 6.6  | V    |

| 1.1a  | VDD6 <sub>ripple</sub>  | VDD6 ripple voltage                                                                                       | Peak-to-peak, ensured by design<br>VBATP = VBAT_SAFING = 14 V, L = 33 μH, C = 22 μF                                                                                                                                                         |                   | 200  |      | mV   |

| 1.2   | I <sub>VDD6</sub>       | VDD6 output current I <sub>VDD5</sub> + I <sub>VDD3/5</sub> + I <sub>VDD1</sub> + I <sub>VSOUT1</sub> (3) |                                                                                                                                                                                                                                             |                   |      | 1.3  | Α    |

| 1.3   | V <sub>dropout6</sub>   | VDD6 output dropout voltage V <sub>dropout6</sub> = (VBATP – SDN6)                                        | $I_{VDD6}$ = 1.3 A (example: R <sub>DS(on)</sub> = 0.46 Ω)                                                                                                                                                                                  |                   |      | 0.6  | ٧    |

| 1.4   | I <sub>VDD6_limit</sub> | Peak current out of SDN6 pin <sup>(4)</sup>                                                               |                                                                                                                                                                                                                                             | 1.5               |      | 2.5  | Α    |

| 1.5   | $f_{ m clk\_VDD6}$      | Clock Frequency (5)                                                                                       |                                                                                                                                                                                                                                             | 396               | 440  | 484  | kHz  |

| 1.6   | DC <sub>VDD6</sub>      | t <sub>on</sub> /t <sub>period</sub>                                                                      | 0 < I <sub>VDD6</sub> < 1.3 A<br>VDD6 enters dropout mode (100% duty cycle) for VBATP < 7<br>V                                                                                                                                              | 7% <sup>(6)</sup> |      | 100% |      |

| 1.7   | Tprot <sub>VDD6</sub>   | Temperature protection threshold <sup>(7)</sup>                                                           |                                                                                                                                                                                                                                             | 175               |      | 210  | °C   |

| VDD5  | - LDO WITH INT          | FERNAL FET                                                                                                |                                                                                                                                                                                                                                             |                   |      |      |      |

| AN    | C <sub>VDD5</sub>       | Value of output ceramic capacitor                                                                         | ESR range 0 m $\Omega$ to 100 m $\Omega$                                                                                                                                                                                                    | 1                 |      | 5    | μF   |

| 2.1   | VDD5                    | VDD5 output voltage <sup>(8)</sup>                                                                        | 0 < I <sub>VDD</sub> 5 < 300 mA                                                                                                                                                                                                             | 4.9               | 5    | 5.1  | ٧    |

| 2.2   | I <sub>VDD5</sub>       | VDD5 output current, including load from the internal resistor of 660 $\Omega$ (typical)                  |                                                                                                                                                                                                                                             |                   |      | 300  | mA   |

| 2.3   | VDD5 <sub>dyn</sub>     | VDD5 output voltage dynamic                                                                               | Load step 20% to 80% in 5 $\mu$ s, with $C_{VDD5}$ = 5 $\mu$ F                                                                                                                                                                              | 4.85              | 5    | 5.15 | V    |

| 2.4   | VDD5 <sub>max</sub>     | Maximum VDD5 output voltage during VBATP step from 5.5 V to 13.5 V within 10 $\mu s$                      | $C_{VDDS} = 5 \mu F$ , $I_{VDDS} < 300 \text{ mA}$                                                                                                                                                                                          |                   |      | 5.5  | ٧    |

| 2.5   | V <sub>dropout5</sub>   | VDD5 output dropout voltage V <sub>dropout5</sub> = (VDD6 – VDD5)                                         | I <sub>VDDS</sub> < 300 mA                                                                                                                                                                                                                  |                   |      | 0.3  | ٧    |

| 2.6   | PSRR <sub>VDD5</sub>    | Power supply rejection ratio                                                                              | $\begin{array}{l} 50 < f < 20 \text{ kHz}, \text{ VBATP} = 10 \text{ V}, \text{ U} = 4 \text{ Vpp}, \\ C_{\text{VDD5}} = 5  \mu\text{F}, \text{ 0} < I_{\text{VDD5}} < 300 \text{ mA} \end{array}$                                          |                   | > 40 |      | dB   |

| 2.7   | LnReg <sub>VDD5</sub>   | Line regulation (I <sub>VDD5</sub> constant)                                                              | 0 < I <sub>VDDS</sub> < 300 mA,<br>8 V < VBATP < 19 V                                                                                                                                                                                       | -25               |      | 25   | mV   |

| 2.8   | LdReg <sub>VDD5</sub>   | Load regulation (VDD6 constant)                                                                           | 0 < I <sub>VDD5</sub> < 300 mA,<br>8 V < VBATP < 19 V                                                                                                                                                                                       | -25               |      | 25   | mV   |

| 2.9   | TmpCo <sub>VDD5</sub>   | Temperature drift                                                                                         | Normalized to 25°C value                                                                                                                                                                                                                    | -0.5%             |      | 0.5% |      |

| 2.11  | dVDD5/dt                | dV/dt at VDD5 at startup                                                                                  | Between 10% and 90% of VDD5 end-value                                                                                                                                                                                                       | 5                 |      | 50   | V/ms |

| 2.13  | Tprot <sub>VDD5</sub>   | Temperature protection threshold <sup>(9)</sup>                                                           |                                                                                                                                                                                                                                             | 175               |      | 210  | °C   |

| 2.14  | I <sub>VDD5_limit</sub> | Current-limit <sup>(10)</sup>                                                                             |                                                                                                                                                                                                                                             | 350               |      | 650  | mA   |

- (1) Capacitance is effective capacitance after derating for operating voltage, temperature, and lifetime.

- (2) ESR is total effective series resistance of the capacitors and if necessary added series resistor.

- (3) I<sub>VDD6</sub> is the load current from VDD5, VDD3/5, VDD1 and VSOUT1 on VDD6 regulator; VDD6 is not recommended to be loaded directly for applications or peripherals that cannot operate with wider tolerance and ripple since VDD6 is a pre-regulator. However, LDOs or DC-DC converters may be connected directly as along as the total load current on VDD6, I<sub>VDD6</sub>, does not exceed the specification for VDD6 load current.

- (4) VDD6 current limit is based on the peak current through SDN6 switch, it will not directly correspond to an average current limit.

- (5) Actual switching on SND6 depends on whether output voltage on VDD6 is above or below hysteretic PWM comparator threshold at the moment of the rising edge of the F<sub>clk\_VDD6</sub> clock. If no switching is needed when the risking edge of the F<sub>clk\_VDD6</sub> clock occurs, SDN6 will not switch on. SDN6 turn off is determined by the hysteretic PWM comparator threshold, when the actual VDD6 voltage is above the threshold SDN6 will turn off.

- (6) When the VDD6 control loop turns the SDN6 switch on at the rising edge of a fclk\_VDD6 clock cycle, SDN6 will remain on with a minimum duty cycle of 7%. However, if the control loop skips a clock cycle the duty cycle will be 0% for that fclk\_VDD6 clock cycle.

- (7) Protection of VDD6, shared with VDD3/5 overtemperature protection.

- (8) VDD5 output regulation includes line and load regulation, temperature drift.

- 9) Protection of VDD5. In case of detected overtemperature, only VDD5 will be switched off.

- (10) I<sub>VDD5\_limit</sub> current limit has snap back behavior. During a short circuit condition, a transient current higher than the maximum will occur until the current limit snaps back into the specified range.

Over operating ambient temperature  $T_A = -40^{\circ}C$  to the maximum-operating junction temperature  $T_J = 150^{\circ}C$ , and with VBATP = VBAT\_SAFING in the recommended operating range (see R1.2 in Section 4.3) (unless otherwise noted)

| VBA    | IP = VBAI_                 | SAFING in the recommended operating                                                                                                                        | g range (see R1.2 in Sect                                                                                  | ion 4.3) (unless of           | herwise i | noted) |       |                                         |

|--------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-------------------------------|-----------|--------|-------|-----------------------------------------|

| POS    |                            | PARAMETER                                                                                                                                                  | TEST CONDIT                                                                                                | TEST CONDITIONS               |           | TYP    | MAX   | UNIT                                    |

| VDD3/  | 5 – LDO WITH INT           | TERNAL FET                                                                                                                                                 |                                                                                                            |                               |           |        |       |                                         |

| AN     | C <sub>VDD3/5</sub>        | Value of output ceramic capacitor                                                                                                                          | ESR range 0 m $\Omega$ to 100 m $\Omega$                                                                   |                               | 1         |        | 5     | μF                                      |

| 3.1a   | VDD3/5                     | VDD3/5 output voltage, SEL_VDD3/5 pin: open = 3.3 V                                                                                                        | 0 < I <sub>VDD3/5</sub> < 300 mA                                                                           | 3.3-V Setting                 | 3.234     | 3.3    | 3.366 | V                                       |

| 3.1b   | VDD3/3                     | setting, ground = 5 V setting                                                                                                                              | 0 < I <sub>VDD3/5</sub> < 300 IIIA                                                                         | 5-V Setting                   | 4.9       | 5      | 5.1   | V                                       |

| 3.2    | I <sub>VDD3/5</sub>        | VDD3/5 output current, including load from the internal resistor of 440 $\Omega$ (typ.) for 3.3 V setting or 660 $\Omega$ (typ.) for 5 V setting $^{(11)}$ |                                                                                                            |                               |           |        | 300   | mA                                      |

| 3.3a   | VDD2/F                     | VDD2/F autout valtage dunamin                                                                                                                              | Load step 20% to 80% in 5 µs, with                                                                         | 3.3-V Setting                 | 3.15      | 3.3    | 3.43  | V                                       |

| 3.3b   | VDD3/5 <sub>dyn</sub>      | VDD3/5 output voltage dynamic                                                                                                                              | $C_{VDD3/5} = 5 \mu F$                                                                                     | 5-V Setting                   | 4.85      | 5      | 5.15  | V                                       |

| 2.4    | VDD2/F                     | Maximum VDD3/5 output voltage during VBATP step                                                                                                            | C 5E. 1 . 200 mA                                                                                           | 3.3-V Setting                 |           |        | 3.6   | V                                       |

| 3.4    | VDD3/5 <sub>max</sub>      | from 5.5 V to 13.5 V within 10 μs                                                                                                                          | $C_{VDD3/5} = 5 \mu F$ , $I_{VDD3/5} < 300 \text{ mA}$                                                     | 5-V Setting                   |           |        | 5.5   | V                                       |

| 3.5    | Vdropout3/5                | VDD3/5 output dropout voltage Vdropout3/5 = (VDD6-VDD3/5)                                                                                                  | I <sub>VDD3/5</sub> < 300 mA                                                                               |                               |           |        | 0.3   | V                                       |

| 3.6    | PSRR <sub>VDD3/5</sub>     | Power-supply rejection ratio                                                                                                                               | $50 < f < 20$ kHz, VBATP = 10 V, U = $C_{VDD3/5} = 5$ μF, $0 < I_{VDD3/5} < 300$ mA                        | 4 Vpp                         |           | > 40   |       | dB                                      |

| 3.7    | LnReg <sub>VDD3/5</sub>    | Line regulation (I <sub>VDD3</sub> constant)                                                                                                               | 0 < I <sub>VDD3/5</sub> < 300 mA,<br>8 V < VBATP < 19 V                                                    |                               | -25       |        | 25    | mV                                      |

| 3.8    | LdReg <sub>VDD3/5</sub>    | Load regulation (VDD6 constant)                                                                                                                            | 0 < I <sub>VDD3/5</sub> < 300 mA<br>8 V < VBATP < 19 V                                                     |                               | -25       |        | 25    | mV                                      |

| 3.9    | TmpCo <sub>VDD3/5</sub>    | Temperature drift                                                                                                                                          | Normalized to 25°C value                                                                                   | I                             | -0.5%     |        | 0.5%  |                                         |

| 3.11   | dVDD35/dt                  | dV/dt at VDD3/5 at start-up                                                                                                                                | Between 10% and 90% of VDD3/5                                                                              | 3.3-V Setting                 | 3         |        | 30    | V/ms                                    |

| 0      | a 1 2 2 0 0 / at           | aviat at 75550 at start up                                                                                                                                 | end-value                                                                                                  | 5-V Setting                   | 5         |        | 50    | *************************************** |

| 3.13   | Tprot <sub>VDD3/5</sub>    | Temperature protection threshold <sup>(12)</sup>                                                                                                           |                                                                                                            |                               | 175       |        | 210   | °C                                      |

| 3.14   | I <sub>VDD3/5_limit</sub>  | Current-limit <sup>(13)</sup>                                                                                                                              |                                                                                                            |                               | 350       |        | 650   | mA                                      |

| 3.15   | I <sub>pu_SEL_VDD3/5</sub> | Pullup current on SEL_VDD3/5 pin                                                                                                                           |                                                                                                            |                               |           |        | 20    | μA                                      |

| VDD1 - | - LDO WITH EXTE            | ERNAL FET                                                                                                                                                  | 1                                                                                                          |                               | ı         |        |       |                                         |

| AN     | Vgs(th)                    | Gate threshold voltage, external FET                                                                                                                       | ID = 1 mA                                                                                                  |                               | 0.3       |        | 3     | V                                       |

| AN     | Ciss                       | Gate capacitance, external FET                                                                                                                             | VGS = 0 V                                                                                                  |                               |           |        | 3200  | pF                                      |

| AN     | Qgate                      | Gate Charge, external FET                                                                                                                                  | VGS = 0 V to 10 V                                                                                          |                               |           |        | 70    | nC                                      |

| AN     | gfs                        | Forward transconductance, external FET                                                                                                                     | ID = 50 mA                                                                                                 |                               | 0.4       |        |       | S                                       |

| AN     | C <sub>VDD1</sub>          | Value of output ceramic capacitor                                                                                                                          | ESR range 0 m $\Omega$ to 100 m $\Omega$                                                                   |                               | 5         |        | 40    | μF                                      |

| 4.1    | VDD1                       | VDD1 output voltage, depends on external resistive divider                                                                                                 |                                                                                                            |                               | 0.8       |        | 3.3   | V                                       |

| 4.2    | VDD1 <sub>SENSE</sub>      | VDD1 reference voltage <sup>(14)</sup>                                                                                                                     | 10 mA < I <sub>VDD1</sub> < 600 mA                                                                         |                               | 0.792     | 0.8    | 0.808 | V                                       |

| 4.2a   | VDD1 <sub>SENSE_BIAS</sub> | Bias current of VDD1 <sub>SENSE</sub>                                                                                                                      |                                                                                                            |                               | -6.6      |        | -10   | μΑ                                      |

| 4.3    | I <sub>VDD1</sub>          | VDD1 output current                                                                                                                                        | Minimum current realized with extern                                                                       | nal resistive divider         | 10        |        | 600   | mA                                      |

| 4.4    | VDD1 <sub>G</sub>          | VDD1_G output voltage                                                                                                                                      | Referenced to GND                                                                                          |                               |           |        | 15    | V                                       |

| 4.5    | VDD1 <sub>G_off</sub>      | VDD1_G voltage in OFF condition                                                                                                                            | 20 μA into VDD1_G pin                                                                                      |                               |           |        | 0.3   | V                                       |

| 4.6    | I_VDD1 <sub>G</sub>        | VDD1_G DC load current                                                                                                                                     |                                                                                                            |                               |           |        | 200   | μΑ                                      |

| 4.7    | VDD1 <sub>dyn</sub>        | VDD1 output voltage dynamic                                                                                                                                | Load step 10% to 90% in 1 µs, with                                                                         | CVDD1 = 40 μF <sup>(15)</sup> |           | ± 4%   |       |                                         |

|        |                            |                                                                                                                                                            |                                                                                                            | VDD1 = 0.8-V output           |           |        | 0.898 |                                         |

| 4.8    |                            | Maximum VDD1 output voltage during VBATP step from 5.5 V to 13.5 V within 10 μs                                                                            | $C_{VDD1} > 6 \mu F$ , $I_{VDD1} < 600 \text{ mA}$                                                         | VDD1 = 1.23-V output          |           |        | 1.287 | V                                       |

|        |                            | monrolo v to vote v mamir ve pe                                                                                                                            | VDD1 = 3.3-V output                                                                                        |                               |           |        | 3.435 |                                         |

| 4.9    | PSRR <sub>VDD1</sub>       | Power-supply rejection ratio                                                                                                                               | 50 < f < 20 kHz, VBATP = 10 V, U = 4 Vpp,<br>C <sub>VDD1</sub> = 10 μF, 10 mA < I <sub>VDD1</sub> < 600 mA |                               |           | > 40   |       | dB                                      |

| 4.10   | LnReg <sub>VDD1</sub>      | Line regulation on VDD1_SENSE ( $I_{VDD1}$ constant)                                                                                                       | 10 mA < <sub>IVDD1</sub> < 600 mA, 8 V < VBATP < 19 V                                                      |                               | -7        |        | 7     | mV                                      |

| 4.11   | LdReg <sub>VDD1</sub>      | Load regulation on VDD1_SENSE (VDD6 constant)                                                                                                              | 10 mA < I <sub>VDD</sub> 1 < 600 mA, 8 V < VBA                                                             | TP < 19 V                     | -7        |        | 7     | mV                                      |

| 4.12   | TmpCo <sub>VDD1</sub>      | Temperature drift                                                                                                                                          | Normalized to 25°C value                                                                                   |                               | -0.5%     |        | 0.5%  |                                         |

| 4.14   | dVDD1/dt                   | dV/dt at VDD1_SENSE at start-up                                                                                                                            | Between 10% and 90% of VDD1 end                                                                            | d-value                       | 0.8       |        | 8     | V/ms                                    |

| vsou   | T1 – LDO WITH PI           | ROTECTED INTERNAL FET                                                                                                                                      |                                                                                                            |                               |           |        |       |                                         |

<sup>(11)</sup> Less than 50% of maximum loading of I<sub>VDD3/5</sub> should be placed on the VDD3/5 regulator before NRES goes high during device power

<sup>(12)</sup> Protection of VDD3/5, treated as global overtemperature (shutdown for all regulators).

(13) I<sub>VDD3/5\_limit</sub> current limit has snap back behavior. During a short circuit condition, a transient current higher than the maximum will occur until the current limit snaps back into the specified range.

<sup>(14)</sup> VDD1 regulation including line and load regulation, temperature drift and long-term drift. Does not include tolerance of resistor divider to set VDD1 output voltage.

<sup>(15)</sup> VDD1<sub>dyn</sub> will depend on external FET choice

Over operating ambient temperature  $T_A = -40$ °C to the maximum-operating junction temperature  $T_J = 150$ °C, and with VBATP = VBAT\_SAFING in the recommended operating range (see R1.2 in Section 4.3) (unless otherwise noted)

| POS   |                           | PARAMETER                                                                                                                                                             | TEST COND                                                                                                                  | DITIONS                    | MIN   | TYP  | MAX  | UNIT |

|-------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------|-------|------|------|------|

| AN    | C <sub>VSOUT1</sub>       | Value of output ceramic capacitor                                                                                                                                     | ESR range 0 m $\Omega$ to 100 m $\Omega$                                                                                   |                            | 0.5   |      | 10   | μF   |

| 5.1   | VSOUT1                    | VSOUT1 output voltage, depends on external resistive divider and tracking or non-tracking mode                                                                        |                                                                                                                            |                            | 3.3   |      | 9.5  | V    |

| 5.2   | MV <sub>VSOUT1</sub>      | For tracking mode:<br>Matching output error MV <sub>VSOUT1</sub> =<br>(VTRACK1 – VSFB1) <sup>(16)</sup>                                                               | 0 < I <sub>VSOUT1</sub> < 100 mA                                                                                           |                            | -35   |      | 35   | mV   |

| 5.3   | VSFB1                     | For non-tracking mode: VSOUT1 reference voltage(17)                                                                                                                   | 10 mA < I <sub>VSOUT1</sub> < 100 mA                                                                                       |                            | 2.45  | 2.5  | 2.55 | V    |

| 5.3a  | VTRACK1 <sub>th</sub>     | Threshold for selecting tracking/non-tracking mode (VTRACK1 > VTRACK1 <sub>th_max</sub> V for tracking mode, VTRACK1 < VTRACK1 <sub>th_min</sub> V non-tracking mode) |                                                                                                                            |                            | 1.1   | 1.2  | 1.3  | V    |

| 5.3b  | VTRACK1 <sub>pd</sub>     | Internal pulldown resistance on VTRACK1 pin                                                                                                                           |                                                                                                                            |                            |       | 100  |      | kΩ   |

| 5.4   | I <sub>VSOUT1</sub>       | VSOUT1 output current, including internal resistor to dissipate minimum current <sup>(18)</sup>                                                                       |                                                                                                                            |                            |       |      | 100  | mA   |

| 5.5   | VdrS1                     | VSOUT1 dropout voltage VdrS1 = (VSIN-VSOUT1)                                                                                                                          | 0 < I <sub>VSOUT1</sub> < 100 mA                                                                                           |                            |       |      | 0.75 | V    |

| 5.6   | PSRR <sub>VSOUT1</sub>    | Power-supply rejection ratio                                                                                                                                          | With VTRACK1 = GND, VSOUT1 50 < f < 20 kHz, VSIN = 10 V, U = $C_{VSOUT1}$ = 1 $\mu$ F, 0 < $I_{VSOUT1}$ < 100 $I_{VSOUT1}$ | : 4 Vpp                    |       | > 40 |      | dB   |

| 5.7   | LnReg <sub>VSOUT1</sub>   | Line regulation (I <sub>VSOUT1</sub> constant)                                                                                                                        | 0 < I <sub>VSOUT1</sub> < 100 mA, 8 V < VSIN                                                                               | < 19 V                     | -25   |      | 25   | mV   |

| 5.8   | LdReg <sub>VSOUT1</sub>   | Load regulation (VSIN constant)                                                                                                                                       | 0 < I <sub>VSOUT1</sub> < 100 mA, 8 V < VSIN                                                                               | < 19 V                     | -35   |      | 35   | mV   |

| 5.9   | TmpCo <sub>VSOUT1</sub>   | Temperature drift                                                                                                                                                     | Normalized to 25°C value                                                                                                   |                            | -0.5% |      | 0.5% |      |

| 5.11  | VSOUT1 <sub>SH</sub>      | Output short circuit voltage range                                                                                                                                    | VSOUT1 (VSFB1 configured for re                                                                                            | egulation) <sup>(19)</sup> | -2    |      | 18   | V    |

| 5.12  | -I <sub>VSIN</sub>        | Output reverse current                                                                                                                                                | VSOUT1 = 14 V and VBATP = 0 V                                                                                              | /, regulator switched off  |       |      | 20   | mA   |

| 5.13  | Tprot <sub>VSOUT1</sub>   | Temperature protection threshold <sup>(20)</sup>                                                                                                                      |                                                                                                                            |                            | 175   |      | 210  | °C   |

| 5.14  | I <sub>VSOUT1_limit</sub> | Current-limit                                                                                                                                                         |                                                                                                                            |                            | 120   |      | 500  | mA   |

| VOLTA | AGE MONITORING            |                                                                                                                                                                       | 1                                                                                                                          |                            |       |      | ı    |      |

| 6.1   | VBATP_UV <sub>off</sub>   | VBATP and VBAT_SAFING level for indication by VBAT_UV comparitor <sup>(21)</sup>                                                                                      | VBATP = VBAT_SAFING                                                                                                        |                            | 4.2   |      | 4.5  | V    |

| 6.2   | VBATP_UV <sub>on</sub>    | VBATP and VBAT_SAFING level for indication by VBAT_UV comparitor <sup>(21)</sup>                                                                                      | VBATP = VBAT_SAFING                                                                                                        |                            | 5.4   |      | 5.8  | V    |

| 6.3   | VBATP_UV <sub>hys</sub>   | Undervoltage hysteresis                                                                                                                                               | VBATP = VBAT_SAFING                                                                                                        |                            | 1.1   |      | 1.4  | V    |