# LMH6586 32x16 Video Crosspoint Switch

Check for Samples: LMH6586

### **FEATURES**

- 32 Inputs and 16 Outputs

- AC-Coupled Inputs with Integrated DC Restore Clamp

- Individually Addressable Outputs

- Pin-Selectable Output Buffer Gain (1 V/V or 2 V/V)

- –3 dB Bandwidth = 66 MHz

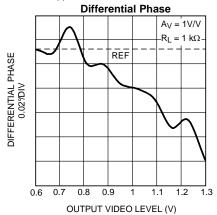

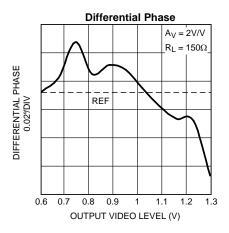

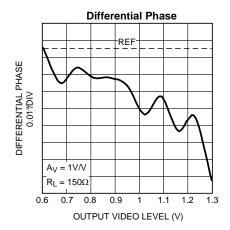

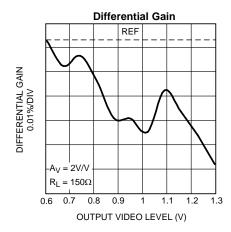

- DG = 0.05%, DP = 0.05° @  $R_L$  = 150 $\Omega$ ,  $A_V$  = 2V/V

- -70 dB Off-Isolation @ 6 MHz

- Individual Input and Output Shutdown Modes

- Device Power Down Mode

- Video Detection with Programmable Threshold (8 Levels)

- Sync Detection with Pin-Configurable Threshold

- 100 kHz I<sup>2</sup>C Interface with 2-Bit Configurable Slave Address

- Single 5V Supply Operation

- Extra Video Output (VOUT\_16) for External Video Sync Separator

#### **APPLICATIONS**

- CCTV Security and Surveillance Systems

- Analog Video Routing

#### DESCRIPTION

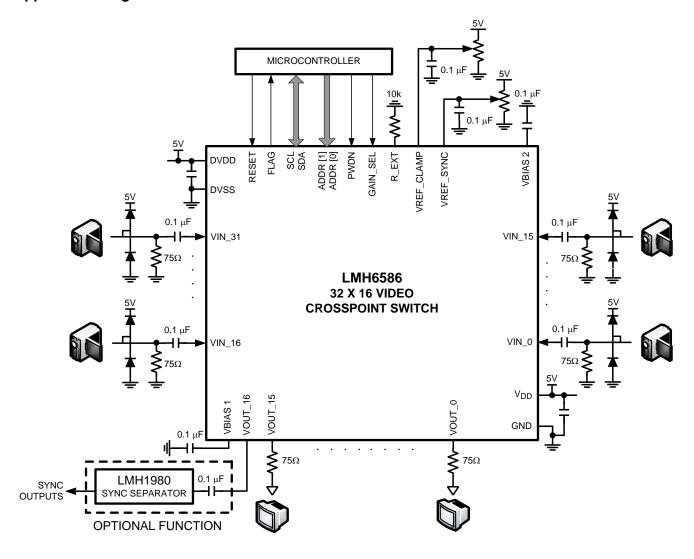

The LMH6586 is a non-blocking analog video crosspoint switch designed for routing standard NTSC or PAL composite video signals. The non-blocking architecture allows any of the 32 inputs to be connected to any of the 16 outputs, including any input that is already connected. Each input has an integrated DC restore clamp for biasing of the AC-coupled video signal. The output buffers have a common selectable gain setting of 1X or 2X and can drive loads of 150 $\Omega$ .

The LMH6586 features two types of input signal detection for convenient monitoring of activity on any input channel. Video detection can be configured to indicate when either "presence of video" or "loss of video" is detected across the video threshold level controlled by a programmable register. Additionally, sync detection can be configured to indicate when "loss of sync" is detected across the sync threshold level controlled by a DC voltage input.

The switch configuration and other parameters are programmable via the  $I^2C$  bus interface. The slave device address is configurable via two external pins allowing up to four LMH6586 devices, each with a unique address, on a common  $I^2C$  bus. This helps facilitate expansion of the crosspoint matrix array size (e.g. 64 x 16). The LMH6586 operates from a common single 5V supply for its analog sections as well as its control logic and  $I^2C$  interface. The LMH6586 is offered in a space-saving 80-pin TQFP.

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

# **Application Diagram**

### **Functional Diagram**

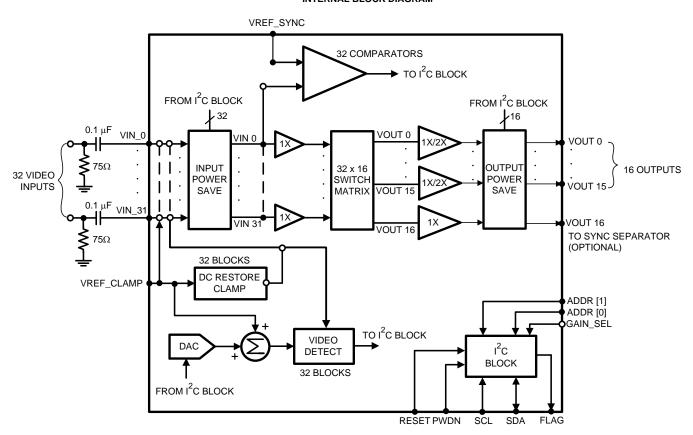

#### INTERNAL BLOCK DIAGRAM

Figure 1. Functional Diagram

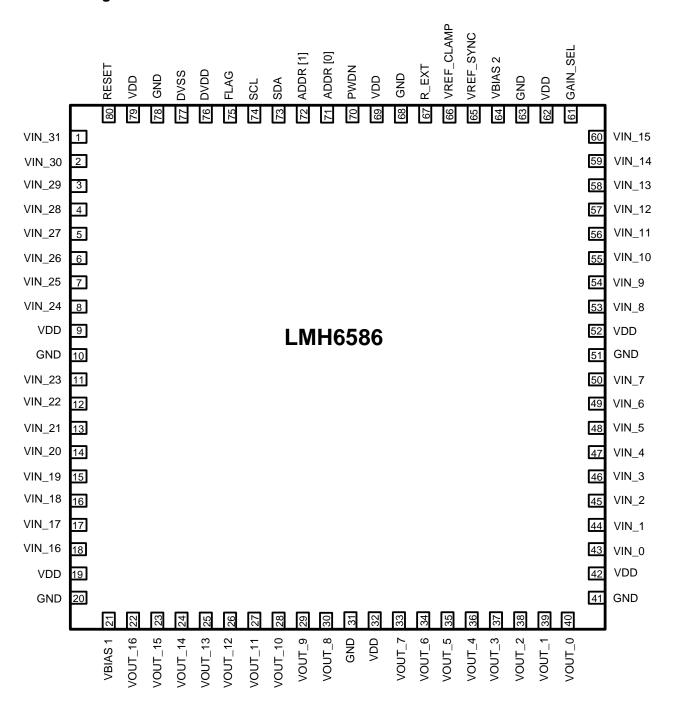

### **Connection Diagram**

### **PIN DESCRIPTIONS**

| PIN DESCRIPTIONS  Din # Bin Name Bin Description |             |                                                |  |  |  |  |  |  |  |

|--------------------------------------------------|-------------|------------------------------------------------|--|--|--|--|--|--|--|

| Pin #                                            | Pin Name    | Pin Description                                |  |  |  |  |  |  |  |

| 1                                                | VIN_31      | VIDEO INPUT 31                                 |  |  |  |  |  |  |  |

| 2                                                | VIN_30      | VIDEO INPUT 30                                 |  |  |  |  |  |  |  |

| 3                                                | VIN_29      | VIDEO INPUT 29                                 |  |  |  |  |  |  |  |

| 4                                                | VIN_28      | VIDEO INPUT 28                                 |  |  |  |  |  |  |  |

| 5                                                | VIN_27      | VIDEO INPUT 27                                 |  |  |  |  |  |  |  |

| 6                                                | VIN-26      | VIDEO INPUT 26                                 |  |  |  |  |  |  |  |

| 7                                                | VIN_25      | VIDEO INPUT 25                                 |  |  |  |  |  |  |  |

| 8                                                | VIN_24      | VIDEO INPUT 24                                 |  |  |  |  |  |  |  |

| 9                                                | VDD         | VDD (connect to 5V supply)                     |  |  |  |  |  |  |  |

| 10                                               | GND         | GND                                            |  |  |  |  |  |  |  |

| 11                                               | VIN_23      | VIDEO INPUT 23                                 |  |  |  |  |  |  |  |

| 12                                               | VIN_22      | VIDEO INPUT 22                                 |  |  |  |  |  |  |  |

| 13                                               | VIN_21      | VIDEO INPUT 21                                 |  |  |  |  |  |  |  |

| 14                                               | VIN_20      | VIDEO INPUT 20                                 |  |  |  |  |  |  |  |

| 15                                               | VIN_19      | VIDEO INPUT 19                                 |  |  |  |  |  |  |  |

| 16                                               | VIN_18      | VIDEO INPUT 18                                 |  |  |  |  |  |  |  |

| 17                                               | VIN_17      | VIDEO INPUT 17                                 |  |  |  |  |  |  |  |

| 18                                               | VIN_16      | VIDEO INPUT 16                                 |  |  |  |  |  |  |  |

| 19                                               | VDD         | VDD (connect to 5V supply)                     |  |  |  |  |  |  |  |

| 20                                               | GND         | GND                                            |  |  |  |  |  |  |  |

| 21                                               | VBIAS 1     | VBIAS 1 (connect to external 0.1 μF capacitor) |  |  |  |  |  |  |  |

| 22                                               | VOUT_16     | VIDEO OUTPUT 16                                |  |  |  |  |  |  |  |

| 23                                               | VOUT_15     | VIDEO OUTPUT 15                                |  |  |  |  |  |  |  |

| 24                                               | VOUT_14     | VIDEO OUTPUT 14                                |  |  |  |  |  |  |  |

| 25                                               | VOUT_13     | VIDEO OUTPUT 13                                |  |  |  |  |  |  |  |

| 26                                               | VOUT_12     | VIDEO OUTPUT 12                                |  |  |  |  |  |  |  |

| 27                                               | VOUT_11     | VIDEO OUTPUT 11                                |  |  |  |  |  |  |  |

| 28                                               | VOUT_10     | VIDEO OUTPUT 10                                |  |  |  |  |  |  |  |

| 29                                               | VOUT_9      | VIDEO OUTPUT 9                                 |  |  |  |  |  |  |  |

| 30                                               | VOUT_8      | VIDEO OUTPUT 8                                 |  |  |  |  |  |  |  |

| 31                                               | GND         | GND                                            |  |  |  |  |  |  |  |

| 32                                               | VDD         | VDD (connect to 5V supply)                     |  |  |  |  |  |  |  |

| 33                                               | VOUT_7      | VIDEO OUTPUT 7                                 |  |  |  |  |  |  |  |

| 34                                               | VOUT_6      | VIDEO OUTPUT 6                                 |  |  |  |  |  |  |  |

| 35                                               | VOUT_5      | VIDEO OUTPUT 5                                 |  |  |  |  |  |  |  |

| 36                                               | VOUT_4      | VIDEO OUTPUT 4                                 |  |  |  |  |  |  |  |

| 37                                               | VOUT_3      | VIDEO OUTPUT 3                                 |  |  |  |  |  |  |  |

| 38                                               | VOUT_2      | VIDEO OUTPUT 2                                 |  |  |  |  |  |  |  |

| 39                                               | VOUT_1      | VIDEO OUTPUT 1                                 |  |  |  |  |  |  |  |

| 40                                               | VOUT_0      | VIDEO OUTPUT 0                                 |  |  |  |  |  |  |  |

| 41                                               | GND         | GND                                            |  |  |  |  |  |  |  |

| 42                                               | VDD         | VDD (connect to 5V supply)                     |  |  |  |  |  |  |  |

| 43                                               | VIN_0       | VIDEO INPUT 0                                  |  |  |  |  |  |  |  |

| 44                                               | VIN_1       | VIDEO INPUT 1                                  |  |  |  |  |  |  |  |

| 45                                               | VIN_2       | VIDEO INPUT 2                                  |  |  |  |  |  |  |  |

| 46                                               | VIN_3       | VIDEO INPUT 3                                  |  |  |  |  |  |  |  |

| 47                                               | VIN_4       | VIDEO INPUT 4                                  |  |  |  |  |  |  |  |

| L                                                | · · · · - · | · = • ·· · · ·                                 |  |  |  |  |  |  |  |

# PIN DESCRIPTIONS (continued)

| Pin # | Pin Name   | Pin Description                                                                                                             |

|-------|------------|-----------------------------------------------------------------------------------------------------------------------------|

| 48    | VIN_5      | VIDEO INPUT 5                                                                                                               |

| 49    | VIN_6      | VIDEO INPUT 6                                                                                                               |

| 50    | VIN_7      | VIDEO INPUT 7                                                                                                               |

| 51    | GND        | GND                                                                                                                         |

| 52    | VDD        | VDD (connect to 5V supply)                                                                                                  |

| 53    | VIN_8      | VIDEO INPUT 8                                                                                                               |

| 54    | VIN_9      | VIDEO INPUT 9                                                                                                               |

| 55    | VIN_10     | VIDEO INPUT 10                                                                                                              |

| 56    | VIN_11     | VIDEO INPUT 11                                                                                                              |

| 57    | VIN_12     | VIDEO INPUT 12                                                                                                              |

| 58    | VIN_13     | VIDEO INPUT 13                                                                                                              |

| 59    | VIN_14     | VIDEO INPUT 14                                                                                                              |

| 60    | VIN_15     | VIDEO INPUT 15                                                                                                              |

| 61    | GAIN       | GAIN SELECT INPUT (set low for 1X gain, or set high for 2X gain)                                                            |

| 62    | VDD        | VDD (connect to 5V supply)                                                                                                  |

| 63    | GND        | GND                                                                                                                         |

| 64    | VBIAS 2    | VBIAS 2 (connect to external 0.1 μF capacitor)                                                                              |

| 65    | VREF_SYNC  | SYNC DETECTION THRESHOLD VOLTAGE INPUT (bias to 350 mV <sub>DC</sub> , recommended)                                         |

| 66    | VREF_CLAMP | DC RESTORE CLAMP VOLTAGE INPUT (bias to 300 mV <sub>DC</sub> , recommended)                                                 |

| 67    | R_EXT      | R_EXT BIAS RESISTOR (connect to external 10 kΩ 1% resistor)                                                                 |

| 68    | GND        | GND                                                                                                                         |

| 69    | VDD        | VDD (connect to 5V supply)                                                                                                  |

| 70    | PWDN       | POWER DOWN INPUT (set low for normal operation, set high to power down all video I/O blocks and I <sup>2</sup> C interface) |

| 71    | ADDR [0]   | I <sup>2</sup> C SLAVE ADDRESS BIT 0 INPUT (set low for bit0 = 0, or set low for bit0 = 1)                                  |

| 72    | ADDR [1]   | I <sup>2</sup> C SLAVE ADDRESS BIT 1 INPUT (set low for bit1 = 0, or set low for bit1 = 1)                                  |

| 73    | SDA        | I <sup>2</sup> C DATA IN/OUT (requires external pull-up resistor to DVDD supply)                                            |

| 74    | SCL        | I <sup>2</sup> C CLOCK INPUT (requires external pull-up resistor to DVDD supply)                                            |

| 75    | FLAG       | DETECTION FLAG OUTPUT (active high)                                                                                         |

| 76    | DVDD       | DIGITAL VDD (connect to 5V supply)                                                                                          |

| 77    | DVSS       | DIGITAL GND                                                                                                                 |

| 78    | GND        | GND                                                                                                                         |

| 79    | VDD        | VDD (connect to 5V supply)                                                                                                  |

| 80    | RESET      | RESET INPUT (set low for normal operation, set high to reset device registers to default settings)                          |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

Absolute Maximum Ratings (1)(2)

| Human Body Model | 2500V                          |

|------------------|--------------------------------|

| Machine Model    | 250V                           |

|                  | 5V                             |

|                  | -0.3V to V <sub>DD</sub> +0.3V |

|                  | −65°C to +150°C                |

|                  | 300°C                          |

|                  | +150°C                         |

|                  | •                              |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured. For ensured specifications, see the Electrical Characteristics tables.

- (2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

- (3) Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22-A115-A (ESD MM std. of JEDEC)Field-Induced Charge-Device Model, applicable std. JESD22-C101-C (ESD FICDM std. of JEDEC).

# Operating Ratings<sup>(1)(2)</sup>

| Supply Voltage (V <sub>DD</sub> ) | 5V ± 10%                      |

|-----------------------------------|-------------------------------|

| Ambient Temperature Range         | -40°C ≤ T <sub>A</sub> ≤ 85°C |

| $\theta_{JA}$                     | 25°C/W                        |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured. For ensured specifications, see the Electrical Characteristics tables.

- (2) The maximum power dissipation is a function of T<sub>J(MAX)</sub> and θ<sub>JA</sub>. The maximum allowable power dissipation at any ambient temperature is P<sub>D</sub> = (T<sub>J(MAX)</sub> T<sub>A</sub>)/ θ<sub>JA</sub>. All numbers apply for packages soldered directly onto a PC Board.

# Electrical Characteristics(1)

Unless otherwise specified, all limits ensured for  $T_A$  = 25°C,  $V_{DD}$  = 5V,  $R_{EXT}$  = 10 k $\Omega$  1%, VREF\_CLAMP = 300 mV,  $R_L$  = 150 $\Omega$ ,  $C_L$  = 12 pF.

| Symbol                         | Parameter                        | Conditions                                                                                | Min  | Тур  | Max  | Units |

|--------------------------------|----------------------------------|-------------------------------------------------------------------------------------------|------|------|------|-------|

| DC Specifi                     | cations                          |                                                                                           |      |      |      |       |

| $V_{DD}$                       | Operating Supply Voltage         |                                                                                           | 4.5  |      | 5.5  | V     |

| I <sub>DD</sub>                | Supply Current                   | No Load, A <sub>V</sub> = 1 V/V                                                           |      | 300  | 360  | mA    |

|                                | Power Save Supply Current        | No Load, A <sub>V</sub> = 1 V/V, SCL= SDA= PWDN= DVDD                                     |      | 1.5  |      | mA    |

| A <sub>V</sub>                 | Gain                             | 2x Gain Buffer                                                                            | 1.92 | 2.00 | 2.07 | V/V   |

|                                |                                  | 1x Gain Buffer                                                                            | 0.95 | 0.99 | 1.03 | V/V   |

| ΔA <sub>V_CH-CH</sub>          | Gain Matching (Ch to Ch)         | A <sub>V</sub> = 1 V/V                                                                    |      | 1.2  | 3    | %     |

| Vos                            | Output Offset Voltage            | A <sub>V</sub> = 1 V/V, No Load (referenced to DC restored input)                         |      | 60   |      | mV    |

| V <sub>DET_LSB</sub>           | Video Detection Threshold LSB    |                                                                                           | 85   | 95   | 105  | mV    |

| V <sub>DET</sub>               | Video Detection Threshold Offset | Video detection threshold offset<br>measured above sync tip level of DC<br>restored input |      | ±50  |      | mV    |

| AC Specifi                     | cations                          |                                                                                           |      |      |      |       |

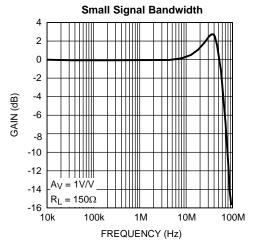

| BW <sub>SS</sub>               | Small Signal Bandwidth (-3 dB)   | V <sub>OUT</sub> = 20 mV <sub>PP</sub>                                                    |      | 66   |      | MHz   |

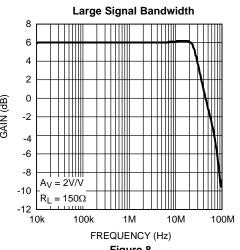

| BW <sub>LS</sub>               | Large Signal Bandwidth (-3 dB)   | $V_{OUT} = 1.5 V_{PP}$                                                                    |      | 29   |      | MHz   |

| t <sub>r</sub> /t <sub>f</sub> | Rise/Fall Time                   | 10% to 90%, V <sub>OUT</sub> = 2 V <sub>PP</sub>                                          |      | 35   |      | ns    |

| tp                             | Propagation Delay                | 50% to 50%, V <sub>OUT</sub> = 2 V <sub>PP</sub>                                          |      | 5    |      | ns    |

| t <sub>pCh-Ch</sub>            | Ch-Ch Propagation Delay          | 50% to 50%, V <sub>OUT</sub> = 2 V <sub>PP</sub>                                          |      | 5    |      | ns    |

(1) All voltages are measured with respect to GND, unless otherwise specified.

# Electrical Characteristics<sup>(1)</sup> (continued)

Unless otherwise specified, all limits ensured for  $T_A$  = 25°C,  $V_{DD}$  = 5V,  $R_{EXT}$  = 10 k $\Omega$  1%, VREF\_CLAMP = 300 mV,  $R_L$  = 150 $\Omega$ ,  $C_L$  = 12 pF.

| Symbol                    | Parameter                         | Conditions                        | Min | Тур  | Max | Units |

|---------------------------|-----------------------------------|-----------------------------------|-----|------|-----|-------|

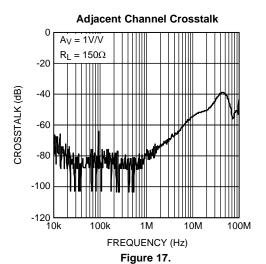

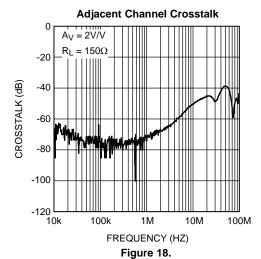

| СТ                        | Adjacent CH Crosstalk             | f = 6 MHz, A <sub>V</sub> = 2 V/V |     | -58  |     | dB    |

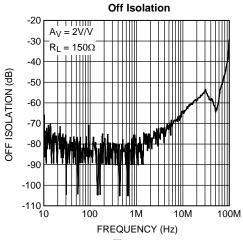

| Off Iso                   | Input-Output Off-Isolation        | f = 6 MHz, A <sub>V</sub> = 2 V/V |     | -70  |     | dB    |

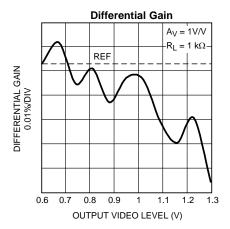

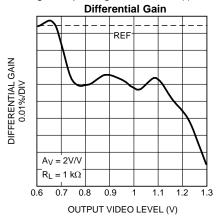

| DG                        | Differential Gain Error for NTSC  | A <sub>V</sub> = 2 V/V, 3.5 MHz   |     | 0.05 |     | %     |

| DP                        | Differential Phase Error for NTSC | A <sub>V</sub> = 2 V/V, 3.5 MHz   |     | 0.05 |     | deg   |

| I <sup>2</sup> C Interfac | ce and Digital Pin Logic Levels   | •                                 |     |      |     |       |

| $V_{IL}$                  | Low Input Voltage                 |                                   |     |      | 1.5 | V     |

| V <sub>IH</sub>           | High Input Voltage                |                                   | 3.3 |      |     | V     |

| I <sub>IN</sub>           | Input Current                     |                                   |     | ±1   |     | μΑ    |

| V <sub>OL</sub>           | Low Output Voltage                | I <sub>OL</sub> = 3 mA            |     | 0.5  |     | V     |

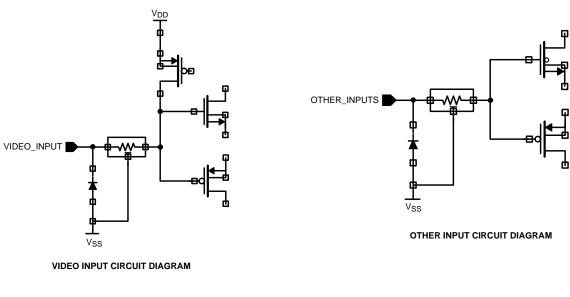

VIDEO\_SYNC\_DETECT

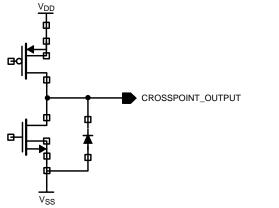

VIDEO OUTPUT CIRCUIT DIAGRAM

VIDEO SYNC DETECT CIRCUIT DIAGRAM

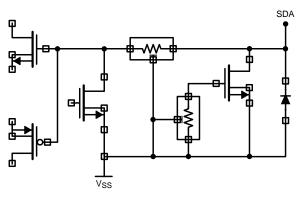

12C DATA CIRCUIT DIAGRAM

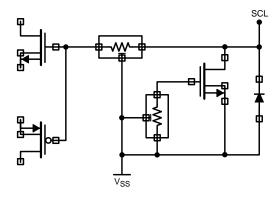

1<sup>2</sup>C CLOCK CIRCUIT DIAGRAM

Figure 2. Logic Diagram

# **Typical Performance Characteristics**

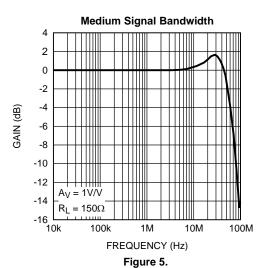

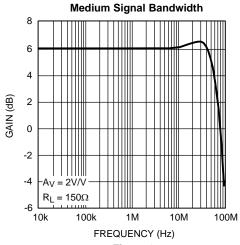

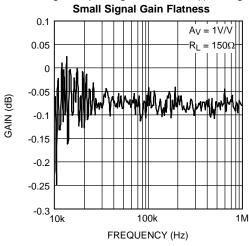

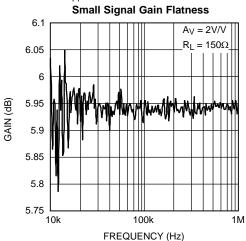

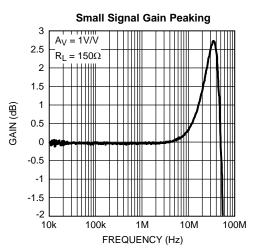

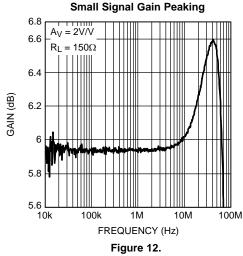

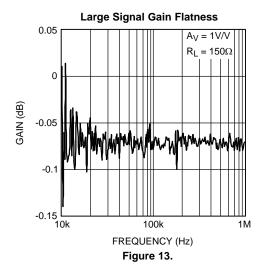

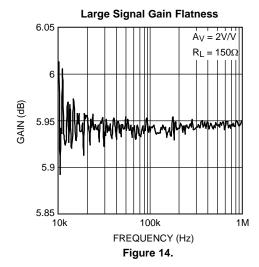

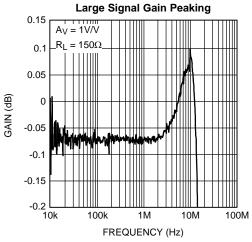

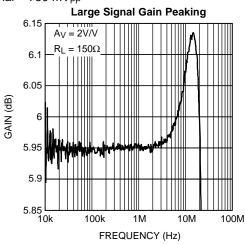

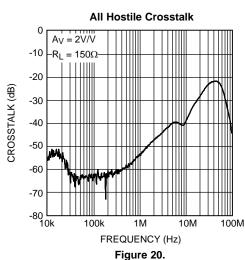

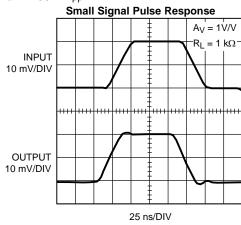

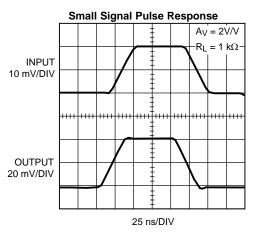

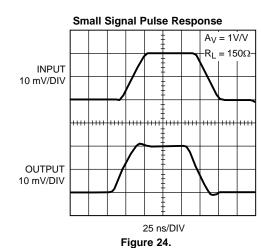

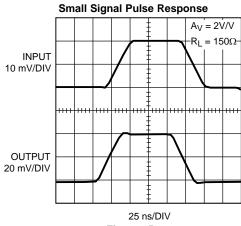

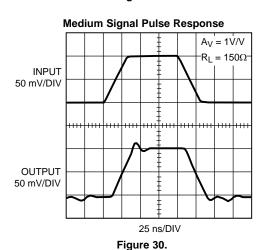

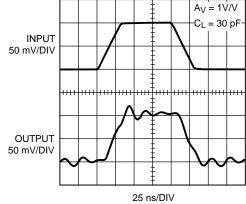

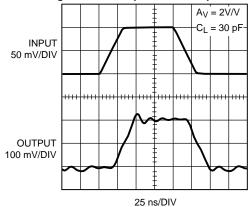

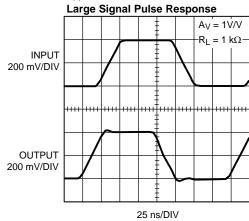

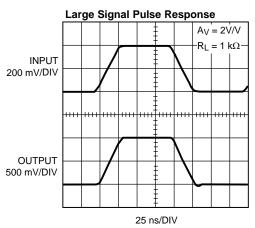

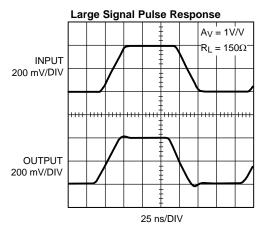

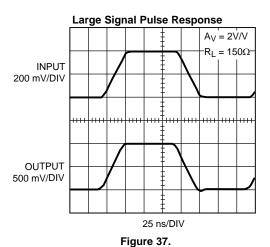

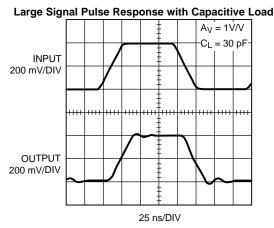

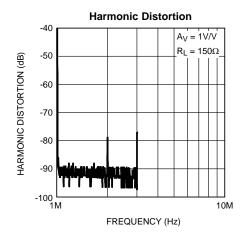

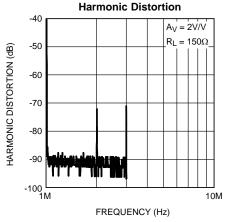

Unless otherwise specified,  $T_A$  = 25°C,  $V_{DD}$  = 5V,  $R_{EXT}$  = 10 k $\Omega$  1%,  $R_L$  = 150 $\Omega$ ,  $C_L$  = 12 pF. Small Signal Input Signal = 20 mV<sub>PP</sub>, Medium Signal Input Signal = 200 mV<sub>PP</sub>, Large Signal Input Signal = 750 mV<sub>PP</sub>

Figure 3.

1M

FREQUENCY (Hz)

Figure 7.

10M

100M

**Small Signal Bandwidth** 8 6 4 GAIN (dB) 2 0 -2  $R_L = 150\Omega$ -6 10k 100k 1M 10M 100M FREQUENCY (Hz)

Figure 4.

Figure 6.

Figure 8.

Submit Documentation Feedback

100k

10k

Unless otherwise specified,  $T_A$  = 25°C,  $V_{DD}$  = 5V,  $R_{EXT}$  = 10 k $\Omega$  1%,  $R_L$  = 150 $\Omega$ ,  $C_L$  = 12 pF. Small Signal Input Signal = 20  $mV_{PP}$ , Medium Signal Input Signal = 200  $mV_{PP}$ , Large Signal Input Signal = 750  $mV_{PP}$

Figure 9.

Figure 10.

Figure 11.

Copyright © 2008-2013, Texas Instruments Incorporated

Unless otherwise specified,  $T_A$  = 25°C,  $V_{DD}$  = 5V,  $R_{EXT}$  = 10 k $\Omega$  1%,  $R_L$  = 150 $\Omega$ ,  $C_L$  = 12 pF. Small Signal Input Signal = 20 mV<sub>PP</sub>, Medium Signal Input Signal = 200 mV<sub>PP</sub>, Large Signal Input Signal = 750 mV<sub>PP</sub>

Figure 16.

All Hostile Crosstalk

1M

100M

FREQUENCY (Hz) FREQUEN Figure 19. Figure

$A_V = 1V/V$

-20

-40

-60

-80

-100

-120 └ 10k

CROSSTALK (dB)

= 150Ω

Unless otherwise specified,  $T_A$  = 25°C,  $V_{DD}$  = 5V,  $R_{EXT}$  = 10 k $\Omega$  1%,  $R_L$  = 150 $\Omega$ ,  $C_L$  = 12 pF. Small Signal Input Signal = 20 mV<sub>PP</sub>, Medium Signal Input Signal = 200 mV<sub>PP</sub>, Large Signal Input Signal = 750 mV<sub>PP</sub>

Figure 21.

Figure 22.

Figure 23.

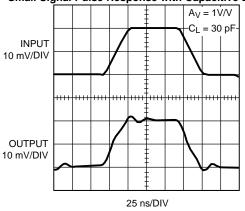

Small Signal Pulse Response with Capacitive Load

Figure 26.

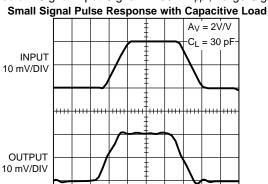

Unless otherwise specified,  $T_A$  = 25°C,  $V_{DD}$  = 5V,  $R_{EXT}$  = 10 k $\Omega$  1%,  $R_L$  = 150 $\Omega$ ,  $C_L$  = 12 pF. Small Signal Input Signal = 20 mV<sub>PP</sub>, Medium Signal Input Signal = 200 mV<sub>PP</sub>, Large Signal Input Signal = 750 mV<sub>PP</sub>

Figure 27.

25 ns/DIV

Figure 28.

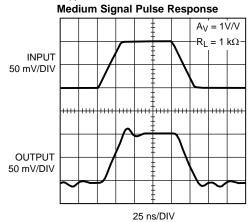

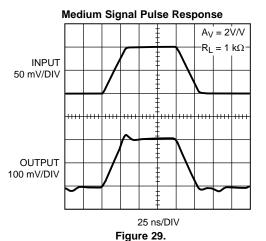

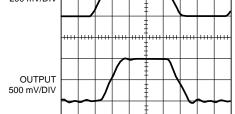

**Medium Signal Pulse Response**

$A_V = 2V/V$

$R_L = 150\Omega^-$

OUTPUT 100 mV/DIV

Figure 31.

25 ns/DIV

Medium Signal Pulse Response with Capacitive Load

Figure 32.

Submit Documentation Feedback

**INPUT**

50 mV/DIV

Unless otherwise specified,  $T_A$  = 25°C,  $V_{DD}$  = 5V,  $R_{EXT}$  = 10 k $\Omega$  1%,  $R_L$  = 150 $\Omega$ ,  $C_L$  = 12 pF. Small Signal Input Signal = 20 mV<sub>PP</sub>, Medium Signal Input Signal = 200 mV<sub>PP</sub>, Large Signal Input Signal = 750 mV<sub>PP</sub>

Figure 33.

Figure 34.

Figure 35.

Figure 36.

Figure 38.

Unless otherwise specified,  $T_A$  = 25°C,  $V_{DD}$  = 5V,  $R_{EXT}$  = 10 k $\Omega$  1%,  $R_L$  = 150 $\Omega$ ,  $C_L$  = 12 pF. Small Signal Input Signal = 20 mV<sub>PP</sub>, Medium Signal Input Signal = 200 mV<sub>PP</sub>, Large Signal Input Signal = 750 mV<sub>PP</sub>

0.6V Output Level = 0 IRE 1.3V Output Level = 100 IRE

out Level = 100 IRE Figure 40.

25 ns/DIV

0.6V Output Level = 0 IRE 1.3V Output Level = 100 IRE

Figure 41.

0.6V Output Level = 0 IRE 1.3V Output Level = 100 IRE

Figure 43.

0.6V Output Level = 0 IRE 1.3V Output Level = 100 IRE

Figure 42.

0.6V Output Level = 0 IRE 1.3V Output Level = 100 IRE

Figure 44.

Unless otherwise specified,  $T_A$  = 25°C,  $V_{DD}$  = 5V,  $R_{EXT}$  = 10 k $\Omega$  1%,  $R_L$  = 150 $\Omega$ ,  $C_L$  = 12 pF. Small Signal Input Signal = 20 mV<sub>PP</sub>, Medium Signal Input Signal = 200 mV<sub>PP</sub>, Large Signal Input Signal = 750 mV<sub>PP</sub>

0.6V Output Level = 0 IRE 1.3V Output Level = 100 IRE

Figure 45.

0.6V Output Level = 0 IRE 1.3V Output Level = 100 IRE

A<sub>V</sub> = 1V/V R<sub>L</sub> = 150Ω 0.6 0.7 0.8 0.9 1 1.1 1.2 1.3 OUTPUT VIDEO LEVEL (V)

Differential Gain

0.6V Output Level = 0 IRE 1.3V Output Level = 100 IRE

Figure 46.

Figure 47.

Figure 48.

Figure 49.

#### APPLICATION INFORMATION

#### **FUNCTIONAL OVERVIEW**

The LMH6586 is a non-blocking, analog video crosspoint switch with 32 input channels and 16 output channels. The inputs have integrated DC restore clamp circuits for biasing the AC-coupled video inputs. The fully buffered outputs have selectable gain and can drive one back-terminated video load ( $150\Omega$ ). The LMH6586 includes an extra output (VOUT\_16) with 1X fixed gain that can be used to feed any input's video signal to an external video sync separator, such as the LMH1980 or LMH1981.

Each input and each output can be individually placed in shutdown mode by programming the input shutdown and output shutdown registers, respectively. Additionally, the PWDN pin (pin 70) can be set high to enable Power Down mode, which shuts down all input and output video channels while preserving all register settings.

The LMH6586 also features both video detection and sync detection functions on each input channel. Additional flexibility is provided by user-defined threshold levels for both video and sync detection features. The status of both detection schemes can be read from the video and sync detection status registers. Additionally, the FLAG output (pin 75) can be used to indicate if video detection or sync detection is triggered on any combination of input channels and detection types enabled by the user.

#### **OUTPUT BUFFER GAIN**

The LMH6586 has an output buffer with a selectable gain of 1X or 2X. When the GAIN\_SEL input (pin 61) is set low, output channels 0–15 will have a gain of 1X. When it is set high, they will have a gain of 2X. Regardless of the gain select setting, output channel 16 has 1X fixed gain since the output is intended to drive an optional external sync separator through a 0.1 µF capacitor and no load termination.

#### **VIDEO DETECTION**

This type of detection can be configured to indicate when an input's video signal is detected above the threshold level ("presence of video") or below the threshold level ("loss of video"). The video threshold voltage level is common to all 32 input channels and is selectable by programming register 0x1D. As shown in Table 1, the three LSBs (bits 2:0) of this register can be used to set the threshold level in 95 mV steps (typical) above to the sync tip level of the DC-restored input. Additionally, to prevent undesired triggering on high-frequency picture content, such as on-screen display (OSD) or text, the detection circuit actually analyzes a low-pass-filtered version of the video signal. The first-order RC filter is included on-chip and has a corner frequency of about 1 kHz.

Registers 0x04 to 0x07 (read-only) contain the video detection status bits for all 32 input channels. Any input (m) has a video detection status bit (VD\_m) that can flag high when either loss of video or presence of video is detected, depending on the respective invert control bit. Registers 0x0C to 0x0F contain the video detection invert control bits for all input channels. When the invert bit (VD\_INV\_m) is set to 0 (default setting), the respective status bit (VD\_m) will flag high when loss of video is detected on the input; otherwise, when the invert bit is set to 1, the status bit will flag high when presence of video is detected.

Threshold level above the Register 0x1D [2:0] sync tip level 0 0 491 mV 0 0 1 587 mV 0 1 0 683 mV 0 1 1 778 mV 1 0 0 873 mV 1 0 1 968 mV 1 1 0 1062 mV

1156 mV

Table 1. Video Detect Threshold Voltage<sup>(1)</sup>

(1) See Video Detect parameters in Electrical Characteristics

1

Product Folder Links: LMH6586

1

1

www.ti.com

The following example illustrates a practical use of video detection in a real-world system. A bank's ATM surveillance system could consist of a video camera, a LMH6586 crosspoint switch, a video recorder, and control system. When no one is using the ATM, the area being monitored by the camera could have strong backlighting, so the camera would output a normally high video level. When a person approaches the area, most of the backlighting would be blocked by the person and cause a measurable decrease in the video level. This change in camera's video level could be detected by the LMH6586, which could then flag the security system to begin recording of the activity. Once the person leaves the area, the LMH6586 could clear the flag.

#### SYNC DETECTION

The LMH6586 also features a sync detection circuit that can indicate when an input's negative-going sync pulse is not detected below the threshold level ("loss of sync"). The sync threshold voltage level is common to all 32 input channels and is defined by the bias voltage on the VREF\_SYNC input (pin 65), which may be set using a simple voltage divider circuit. The recommended voltage level at the VREF\_SYNC pin is 350 mV to ensure proper operation.

Registers 0x00 to 0x03 (read-only) contain the sync detection status bits for all 32 input channels. Any input (m) has a sync detection status bit (SD\_m) that can flag high when a loss of sync is detected; otherwise, the status bit will be low to indicate presence of sync.

### **DETECTION FLAG OUTPUT**

The FLAG output (pin 75) can flag high if either video detection or sync detection is triggered based on the user-defined enable settings for the video and sync detection status bits. Any of the input's video detection status bits (VD\_m) and sync detection status bits (SD\_m) can be logically OR-ed into this single FLAG output pin. Registers 0x10 to 0x13 contain the video detection enable bits and registers 0x14 to 0x17 contain the sync detection enable bits for all input channels. Any input (m) has both a video detection enable bit (VD\_EN\_m) and a sync detection enable bit (SD\_EN\_m). When any enable bit is set low, the respective status bit will be excluded from the OR-ing function used to set the FLAG output; otherwise, when the enable bit is set high, the respective status bit will be included in the FLAG output function. Therefore, the FLAG will only logical-OR the status bits of the channel(s) and type(s) of detection that are specifically enabled by the user.

#### **SWITCH MATRIX**

The LMH6586 uses 512 CMOS analog switches to form a 32 x 16 crosspoint switch. The LMH6586 is a non-blocking crosspoint switch which means that any one of the 32 inputs can be routed to any of the 16 outputs. The switch can only be configured by programming through the  $I^2$ C bus interface.

#### DC RESTORATION

Because the LMH6586 uses a single 5V supply and typical composite video signals contain signal components both above and below 0V (video blanking level), proper input signal biasing is required to ensure the video signal is within the operating range of the amplifier. To simplify the external biasing circuitry, each input of the LMH6586 has a dedicated DC restore clamp circuit to allow AC-coupled input operation using a 0.1 uF coupling capacitor. Please refer to AC COUPLING for details on how the coupling capacitor value was determined.

#### **AC COUPLING**

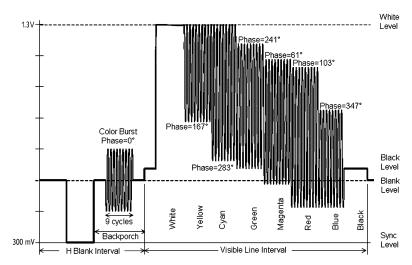

Each video input uses an integrated DC restore clamp circuit to servo the sync tip of the AC-coupled video input signal to the DC voltage received at the VREF\_CLAMP input (pin 66). For proper AC-coupled operation, the LMH6586 requires video signals with negative sync pulses. The VREF\_CLAMP level can be set in range of 300 mV to 1.0V using a voltage divider network. For optimum performance and reduced power consumption, it is recommended to set VREF\_CLAMP to 300 mV. Therefore, assuming a video input amplitude of  $1V_{PP}$ , the bottom of the sync tip level would be clamped to 300 mV above ground and the peak white video level would be at 1.3V.

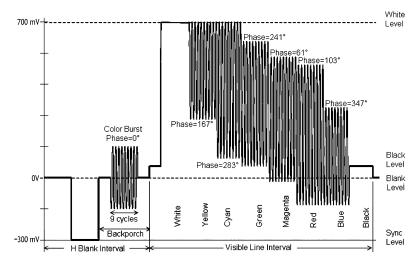

Figure 50. Input Video Signal Before DC Restore Clamp

Figure 51. Input Video Signal After DC Restore Clamp

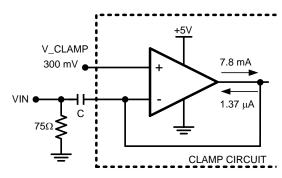

The equivalent DC restore clamp circuit is shown below.

Figure 52. Clamp Circuit

Typically the clamp voltage is set to 300 mV. During the sync pulse period, the clamp circuit amplifier sources current and the coupling capacitor will not discharge. However, during the active video period, the clamp amplifier will sink current and cause the coupling capacitor to discharge through the  $75\Omega$  resistor. To limit this discharge to an acceptable value we must choose an appropriate value of the AC coupling capacitor. The value of the AC coupling capacitor can be calculated as follows:

Cap Discharge Time T = Line Period - Sync Period

$T = 63.5 \mu s - 4.7 \mu s$

$T = 58.8 \mu s$

Discharge current I =  $1.37 \mu A$

Charge Q = I\*T

$Q = 1.37 \mu A * 58.8 \mu s$

Q = 80.55 pC

Q = C\*V

C = Q/V

Typical acceptable voltage drop V = 0.1% of 700 mV

V = 0.7 mV

Capacitor Value C = 80.55 pC/ 0.7 mV

$C = 0.115 \mu F$

Thus the suggested AC coupling capacitor value is 0.1  $\mu$ F. A larger value will reduce line droop at the expense of longer input settling time.

#### **VIDEO INPUTS AND OUTPUTS**

The LMH6586 has 32 inputs which accept standard NTSC or PAL composite video signals. The input video signal should be AC coupled through a 0.1  $\mu$ F coupling capacitor for proper operation. Each input is buffered before the switch matrix, which provides high input impedance. Input buffering enables any single output to be broadcasted to all 16 outputs at a time without loading of the input source. Each input buffer can be individually shut down using the input shutdown registers. When shutdown the input buffers are high impedance, which reduces power consumption and crosstalk.

The LMH6586 has 16 video outputs each of which is buffered through a programmable 1X or 2X gain output buffer. The outputs are capable of driving  $150\Omega$  loads. When the output gain is set to 1X (GAIN\_SEL = 0), the output signal sync tip is set to the VREF\_CLAMP voltage level; otherwise, when the gain is set to 2X (GAIN\_SEL = 1), the output signal sync tip is set to twice the VREF\_CLAMP level. Each output can be individually shut down using the output shutdown registers. When shutdown the outputs are high impedance, which reduces power consumption and crosstalk, and also enables multiple outputs to be connected together for expanding the matrix array size. Note that output short circuit protection is not provided, so care must be taken to ensure only one output is active when output channels are tied together in expansion configurations.

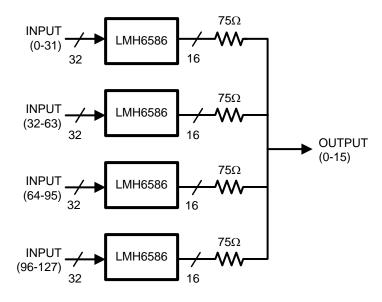

### INPUT EXPANSION

The LMH6586 has the capability for creating larger switching matrices. Depending on the number of input and output channels required, the number of devices required can be calculated. To implement a 128 x 16 non-blocking matrix arrange the building blocks in a grid. The inputs are connected in parallel while the outputs are wired-or together. When using this configuration care must be taken to ensure that only one of the four outputs is active. The other three outputs should be placed in shutdown mode by using the appropriate shutdown bit in the output shutdown registers. This reduces output loading and the risk of output short circuit conditions, which can lead to device overheating and even damage to the channel or device.

The figure below shows the 128 input x 16 output switching matrix using four LMH6586 devices. To construct larger matrices use the same technique with more devices.

Because the LMH6586 has 2-bit configurable slave address inputs, up to four LMH6586 devices can be connected to a common I<sup>2</sup>C bus. For more devices additional I<sup>2</sup>C buses may be required.

Figure 53. 128 x 16 Crosspoint Array

#### DRIVING CAPACITIVE LOAD

When many outputs are wired together, as in the case of expansion, each output buffer sees the normal load impedance as well as the impedance the other shutdown outputs. This impedance has a resistive and a capacitive component. The resistive components reduce the total effective load for the driving output. Total capacitance is the sum of the capacitance of all the outputs and depends on the size of the matrix. As the size of the matrix increases, the length of the PC board traces also increases, adding more capacitance. The output buffers have been designed to drive more than 30 pF of capacitance while still maintaining a good AC response. If the output capacitance exceeds this amount then the AC response will be degraded. To prevent this, one option is to reduce the number of output wired-or together by using more LMH6586 device. Another option is to put a resistor in series with the output before the capacitive load to limit excessive ringing and oscillations.

A low pass filter is created from the series resistor (R) and parasitic capacitance (C) to ground. A single R-C does not affect the performance at video frequencies, however, in large system, there may be many such R-Cs cascaded in series. This may result in high frequency roll-off resulting in "softening of the picture". There are two solutions to improve performance in this case. One way is to design the PC board traces with some inductance between the R and C elements. By routing the traces in a repeating "S" configuration, the traces that are nearest each other will exhibit a mutual inductance increasing the total inductance. This series inductance causes the amplitude response to increase or peak at higher frequencies, offsetting the roll-off from the parasitic capacitance. Another solution is to add a small-value inductor between the R and C elements to add peaking to the frequency response.

#### THERMAL MANAGEMENT

The LMH6586 operates on a 5V supply and draws a load current of approximately 300 mA. Thus it dissipates approximately 1.75W of power. In addition, each equivalent video load (150 $\Omega$ ) connected to the outputs should be budgeted 30 mW of power consumption.

The following calculations show the thermal resistance,  $\theta_{JA}$ , required, to ensure safe operation and to prevent exceeding the maximum junction temperature, given the maximum power dissipation.

$$P_{DMAX} = (T_{JMAX} - T_{AMAX})/\theta_{JA}$$

where

- T<sub>IMAX</sub> = Maximum junction temperature = 150°C

- T<sub>AMAX</sub> = Maximum ambient temperature = +85°C

- $\theta_{JA}$  = Thermal resistance of the package

(1)

The maximum power dissipation actually produced by an IC is the total quiescent supply current times the total power supply voltage, plus the power in the IC due to the load, or:

$$P_{DMAX} = V_S \times I_{SMAX} + \sum_{i=1}^{n} (V_S - V_{OUTi}) \times \frac{V_{OUTi}}{R_{Li}}$$

#### where

- V<sub>S</sub> = Supply voltage = 5V

- I<sub>SMAX</sub> = Maximum quiescent supply current = 300 mA

- V<sub>OUT</sub> = Maximum output voltage of the application = 2.6V

- $R_L$  = Load resistance tied to ground = 150 $\Omega$

#### Calculating:

$P_{DMAX} = 2.2656$

The required  $\theta_{JA}$  to dissipate  $P_{DMAX}$  is =  $(T_{JMAX} - T_{AMAX})/P_{DMAX}$

The table below shows the  $\theta_{JA}$  values with airflow and different heatsinks.

| LMH6586VS 80-Pin TQFT<br>LMHXPT<br>Analog Video Crosspoint Board | 0 LFPM<br>@ 0.50 watt | 0 LFPM<br>@ 1.0 watt | 0 LFPM<br>@ 2.0 watt | 0 LFPM @2.8<br>watt | 225 LFPM @<br>2.8 watt | 500 LFPM @ 2.8 watt |

|------------------------------------------------------------------|-----------------------|----------------------|----------------------|---------------------|------------------------|---------------------|

| NO Heat Sink                                                     | 32.2                  | 30.9                 | 29.4                 | 28.6                | 26.8                   | 25.3                |

| Small Tower<br>x y = 9.57x9.69 mm/ht. 6.28 mm                    | 25.5                  | 24.6                 | 23.6                 | 22.9                | 19.2                   | 15.9                |

| Aluminum 12 rail<br>x y = 9.82x10.73 mm/ht.10.07 mm              | 25.2                  | 24.1                 | 23.0                 | 22.2                | 16.4                   | 14.2                |

| Anodized 9 rail<br>x y = 6.10x7.30 mm/ht. 13.67 mm               | 24.4                  | 23.3                 | 22.1                 | 21.3                | 15.6                   | 13.6                |

| Round Tower<br>diameter = 14.35 mm/ht. 4.47 mm                   | 24.2                  | 23.9                 | 22.9                 | 22.4                | 18.2                   | 15.4                |

### **REXT RESISTOR**

The REXT external resistor (pin 67) establishes the internal bias current and precise reference voltage for the LMH6586. For optimal performance, REXT should be a 10 k $\Omega$  1% precision resistor with a low temperature coefficient to ensure proper operation over a wide temperature range. Using a REXT resistor with less precision may result in reduced performance against temperature, supply voltage, input signal, or part-to-part variations.

#### SYNC SEPARATOR OUTPUT

In addition to the 16 video outputs, the LMH6586 has an extra output (V\_OUT16) which can select any input channel. This channel's output buffer only has a gain of 1 since it is not meant to drive a  $150\Omega$  video load. Instead, this video output can be AC coupled to a non-terminated input of an external video sync separator, such as Tl's LMH1980 or LMH1981. The sync separator can extract the synchronization (sync) timing signals, which can be useful for video triggering or phase-locked loop (PLL) clock generation circuits. Refer to the LMH1980 or LMH1981 datasheet for more information about these sync separator devices.

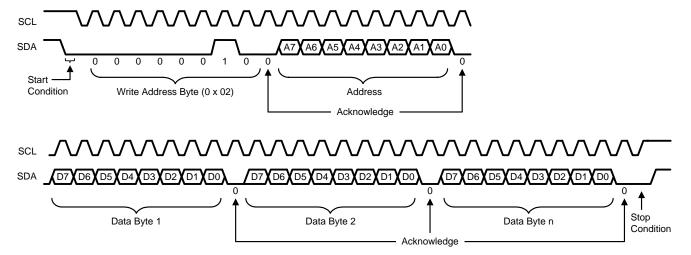

#### I<sup>2</sup>C INTERFACE

A microcontroller can be used to configure the LMH6586 via the  $I^2C$  interface. The protocol of the interface begins with a start pulse followed by a byte comprised of a seven-bit slave device address and a read/write bit as the LSB. The two lowest bits of the seven-bit slave address are defined by the external connections of inputs ADDR[1] (pin 72) and ADDR[0] (pin 71), where ADDR[0] is the least significant bit. Because there are four different combinations of the two ADDR pins, it's possible to have up to four different LMH6586 devices with unique slave addresses on a common  $I^2C$  bus. See  $I^2C$  Device Slave Address Lookup Table.

### Table 2. I<sup>2</sup>C Device Slave Address Lookup Table

| ADDR[1]<br>(pin 72) | ADDR[0]<br>(pin 71) | 7-bit I <sup>2</sup> C Slave Address (binary) |

|---------------------|---------------------|-----------------------------------------------|

| 0                   | 0                   | 0000 000x                                     |

| 0                   | 1                   | 0000 001x                                     |

| 1                   | 0                   | 0000 010x                                     |

| 1                   | 1                   | 0000 011x                                     |

For example, if ADDR[1] is set low and ADDR[0] is set high, then the 7-bit slave address would be "0000 001" in binary. Therefore, the address byte for write sequences is 0x02 ("0000 0010") and the address byte read sequences is 0x03 ("0000 0011"). Figure 54 and Figure 55 show write and read sequences across the I<sup>2</sup>C interface.

#### WRITE SEQUENCE

The write sequence begins with a start condition, which consists of the master pulling SDA low while SCL is held high. The slave device address is sent next. The address byte is made up of an address of seven bits (7:1) and the read/write bit (0). Bit 0 is low to indicate a write operation. Each byte that is sent is followed by an acknowledge (ACK) bit. When SCL is high the master will release the SDA line. The slave must pull SDA low to acknowledge. The address of the register to be written to is sent next. Following the register address and the ACK bit, the data byte for the register is sent. When more than one data byte is sent, the register pointer is automatically incremented to write to the next address location. Note that each data byte is followed by an ACK bit until a stop condition is encountered, indicating the end of the sequence.

The timing diagram for the write sequence is shown in Figure 54, which uses the 7-bit slave device address from the previous example above.

Figure 54. LMH6586 Write Sequence

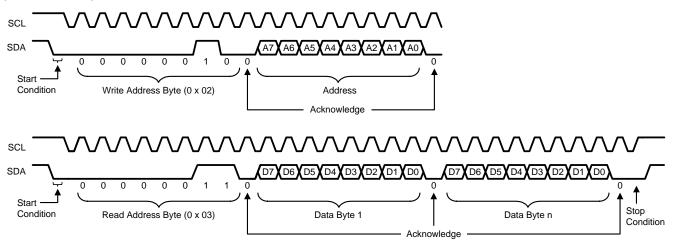

#### READ SEQUENCE

Read sequences are comprised of two I<sup>2</sup>C transfers shown. The first is the address access transfer, which consists of a write sequence that transfers only the address to be accessed. The second is the data read transfer, which starts at the address accessed in the first transfer and increments to the next address per data byte read until a stop condition is encountered.

The address access transfer consists of a start condition, the slave device address including the read/write bit (a zero, indicating a write), and the ACK bit. The next byte is the address to be accessed, followed by the ACK bit and the stop condition to indicate the end of the address access transfer.

The subsequent read data transfer consists of a start condition, the slave device address including the read/write bit (a one, indicating a read), and the ACK bit. The next byte is the data read from the initial access address. Subsequent read data bytes will correspond to the next increment address locations. Note that each data byte is followed by an ACK bit until a stop condition is encountered, indicating the end of the sequence.

The timing diagram for the read sequence is shown in Figure 55, which uses the 7-bit slave address from the previous examples.

Figure 55. LMH6586 Read Sequence

#### REGISTER DESCRIPTIONS

#### **Video and Sync Detection Status Registers**

Registers 0x00 to 0x03 (read-only) contain the sync detection status bits for all 32 input channels. Any input (m) has a sync detection status bit (SD\_m) that can flag high when a loss of sync is detected; otherwise, the status bit will be low to indicate presence of sync.

Registers 0x04 to 0x07 (read-only) contain the video detection status bits for all 32 input channels. Any input (m) has a video detection status bit (VD\_m) that can flag high when either loss of video or presence of video is detected, depending on the respective invert control bit (see Video Detection Invert Registers). Assuming the default setting for the invert control bit, the status bit (VD\_m) will flag high when loss of video is detected on the input; otherwise, the status bit will be low indicating presence of video.

#### **Video and Sync Detection Control Registers**

### Video Detection Invert Registers

Registers 0x0C to 0x0F contain the video detection invert control bits for all input channels. Any input (m) has a invert control bit that can invert the polarity of the video detection status bit (VD\_INV\_m). When the invert bit (VD\_INV\_m) is set to 0 (default), the respective status bit (VD\_m) will flag high to indicate loss of video on the input; otherwise, when the invert bit is set to 1, the status bit will flag high to indicate presence of video.

#### Video and Sync Detection Enable Registers:

Registers 0x10 to 0x13 contain the video detection enable bits and registers 0x14 to 0x17 contain the sync detection enable bits for all input channels. Any input (m) has both a video detection enable bit (VD\_EN\_m) and a sync detection enable bit (SD\_EN\_m). When any enable bit is set low, the respective status bit will be excluded from the OR-ing function used to set the FLAG output; otherwise, when the enable bit is set high, the respective status bit will be included in the FLAG output function. Therefore, the FLAG will only logical-OR the status bits of the channel(s) and type(s) of detection that are specifically enabled by the user as described in DETECTION FLAG OUTPUT.

#### **Video Detection Threshold Control Register**

The video threshold voltage level is common to all 32 input channels and is selectable by programming VDT[2:0] in register 0x1D. As shown in Table 1, the three LSBs (bits 2:0) of this register can be used to set the threshold level in 95 mV steps (typical) above to the sync tip level of the DC-restored input. Refer to VIDEO DETECTION for more information.

#### Input and Output Shutdown Registers

Each input channel and each output channel can be individually placed in shutdown (power save) mode to reduce power consumption. Registers 0x18 to 0x1B contain the input shutdown bits (IN\_PS\_m) and registers 0x1E and 0x1F contain the output shutdown bits (OUT\_PS\_n), where "m" is any input channel and "n" is any output channel. To place any input or output channel in shutdown mode, the respective bit should be set high; otherwise, it should be set low for normal input or output operation. When in shutdown mode, the buffer (input or output) will be placed in a high-impedance state.

Note: To put the entire device in power save mode, the PWDN input (pin 70) should be set high; otherwise, it should be set low for normal operation.

#### **Video Input Selection Registers**

Registers 0x20 to 0x30 are used to control the routing of the crosspoint switch. Each output has a dedicated input selection register, which can be programmed to select any input channel for routing to its respective output.

#### LMH6586 REGISTER MAP

Table 3. Video and Sync Detection Status Registers

| Register                       | Address | R/W | Default | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------------------------------|---------|-----|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| SYNC DETECT OUT (CH 0-7)       | 0x00h   | R   |         | SD_7  | SD_6  | SD_5  | SD_4  | SD_3  | SD_2  | SD_1  | SD_0  |

| SYNC DETECT OUT (CH 8-15)      | 0x01h   | R   |         | SD_15 | SD_14 | SD_13 | SD_12 | SD_11 | SD_10 | SD_9  | SD_8  |

| SYNC DETECT OUT (CH 16-23)     | 0x02h   | R   |         | SD_23 | SD_22 | SD_21 | SD_20 | SD_19 | SD_18 | SD_17 | SD_16 |

| SYNC DETECT OUT (CH 24-31)     | 0x03h   | R   |         | SD_31 | SD_30 | SD_29 | SD_28 | SD_27 | SD_26 | SD_24 | SD_24 |

| VIDEO DETECT OUT (CH 0-7)      | 0x04h   | R   |         | VD_7  | VD_6  | VD_5  | VD_4  | VD_3  | VD_2  | VD_1  | VD_0  |

| VIDEO DETECT OUT<br>(CH 8-15)  | 0x05h   | R   |         | VD_15 | VD_14 | VD_13 | VD_12 | VD_11 | VD_10 | VD_9  | VD_8  |

| VIDEO DETECT OUT<br>(CH 16-23) | 0x06h   | R   |         | VD_23 | VD_22 | VD_21 | VD_20 | VD_19 | VD_18 | VD_17 | VD_16 |

| VIDEO DETECT OUT<br>(CH 24-31) | 0x07h   | R   |         | VD_31 | VD_30 | VD_29 | VD_28 | VD_27 | VD_26 | VD_24 | VD_24 |

## Table 4. Video and Sync Detection Control Registers

| Tuble 4. Video and Syllo Detection Control Registers |                |     |         |               |               |               |               |               |               |               |               |

|------------------------------------------------------|----------------|-----|---------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|

| Register                                             | Address        | R/W | Default | Bit 7         | Bit 6         | Bit 5         | Bit 4         | Bit 3         | Bit 2         | Bit 1         | Bit 0         |

| RESERVED                                             | 0x08h<br>0x0Bh | R/W | 0x00    | RSV           |

| VIDEO DETECT<br>INVERT (CH 0-7)                      | 0x0Ch          | R/W | 0x00    | VD_<br>INV_7  | VD_<br>INV_6  | VD_<br>INV_5  | VD_<br>INV_4  | VD_<br>INV_3  | VD_<br>INV_2  | VD_<br>INV_1  | VD_<br>INV_0  |

| VIDEO DETECT<br>INVERT (CH 8-15)                     | 0x0Dh          | R/W | 0x00    | VD_<br>INV_15 | VD_<br>INV_14 | VD_<br>INV_13 | VD_<br>INV_12 | VD_<br>INV_11 | VD_<br>INV_10 | VD_<br>INV_9  | VD_<br>INV_8  |

| VIDEO DETECT<br>INVERT (CH 16-23)                    | 0x0Eh          | R/W | 0x00    | VD_<br>INV_23 | VD_<br>INV_22 | VD_<br>INV_21 | VD_<br>INV_20 | VD_<br>INV_19 | VD_<br>INV_18 | VD_<br>INV_17 | VD_<br>INV_16 |

| VIDEO DETECT<br>INVERT (CH 24-31)                    | 0x0Fh          | R/W | 0x00    | VD_<br>INV_31 | VD_<br>INV_30 | VD_<br>INV_29 | VD_<br>INV_28 | VD_<br>INV_27 | VD_<br>INV_26 | VD_<br>INV_24 | VD_<br>INV_24 |

| SYNC DETECT<br>ENABLE (CH 0-7)                       | 0x10h          | R/W | 0x00    | SD_<br>EN_7   | SD_<br>EN_6   | SD_<br>EN_5   | SD_<br>EN_4   | SD_<br>EN_3   | SD_<br>EN_2   | SD_<br>EN_1   | SD_<br>EN_0   |

| SYNC DETECT<br>ENABLE (CH 8-15)                      | 0x11h          | R/W | 0x00    | SD_<br>EN_15  | SD_<br>EN_14  | SD_<br>EN_13  | SD_<br>EN_12  | SD_<br>EN_11  | SD_<br>EN_10  | SD_<br>EN_9   | SD_<br>EN_8   |

| SYNC DETECT<br>ENABLE (CH 16-23)                     | 0x12h          | R/W | 0x00    | SD_<br>EN_23  | SD_<br>EN_22  | SD_<br>EN_21  | SD_<br>EN_20  | SD_<br>EN_19  | SD_<br>EN_18  | SD_<br>EN_17  | SD_<br>EN_16  |

| SYNC DETECT<br>ENABLE (CH 24-31)                     | 0x13h          | R/W | 0x00    | SD_<br>EN_31  | SD_<br>EN_30  | SD_<br>EN_29  | SD_<br>EN_28  | SD_<br>EN_27  | SD_<br>EN_26  | SD_<br>EN_25  | SD_<br>EN_24  |

| VIDEO DETECT<br>ENABLE (CH 0-7)                      | 0x14h          | R/W | 0x00    | VD_<br>EN_7   | VD_<br>EN_6   | VD_<br>EN_5   | VD_<br>EN_4   | VD_<br>EN_3   | VD_<br>EN_2   | VD_<br>EN_1   | VD_<br>EN_0   |

| VIDEO DETECT<br>ENABLE (CH 8-15)                     | 0x15h          | R/W | 0x00    | VD_<br>EN_15  | VD_<br>EN_14  | VD_<br>EN_13  | VD_<br>EN_12  | VD_<br>EN_11  | VD_<br>EN_10  | VD_<br>EN_9   | VD_<br>EN_8   |

| VIDEO DETECT<br>ENABLE (CH 16-23)                    | 0x16h          | R/W | 0x00    | VD_<br>EN_23  | VD_<br>EN_22  | VD_<br>EN_21  | VD_<br>EN_20  | VD_<br>EN_19  | VD_<br>EN_18  | VD_<br>EN_17  | VD_<br>EN_16  |

| VIDEO DETECT<br>ENABLE (CH 24-31)                    | 0x17h          | R/W | 0x00    | VD_<br>EN_31  | VD_<br>EN_30  | VD_<br>EN_29  | VD_<br>EN_28  | VD_<br>EN_27  | VD_<br>EN_26  | VD_<br>EN_25  | SD_<br>EN_24  |

# Table 5. Video Detection Threshold Control Registers

| Register                  | Address | R/W | Default | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0 |

|---------------------------|---------|-----|---------|-------|-------|-------|-------|-------|-------|----------|-------|

| VIDEO DETECT<br>THRESHOLD | 0x1Dh   | R/W | 0x00    |       |       | RSV   |       |       |       | VDT[2:0] |       |

# Table 6. Input and Output Shutdown Registers

| Register                        | Address | R/W | Default | Bit 7         | Bit 6         | Bit 5         | Bit 4         | Bit 3         | Bit 2         | Bit 1        | Bit 0        |

|---------------------------------|---------|-----|---------|---------------|---------------|---------------|---------------|---------------|---------------|--------------|--------------|

| INPUT SHUTDOWN<br>(CH 0-7)      | 0x18h   | R/W | 0x00    | IN_<br>PS_7   | IN_<br>PS_6   | IN_<br>PS_5   | IN_<br>PS_4   | IN_<br>PS_3   | IN_<br>PS_2   | IN_<br>PS_1  | IN_<br>PS_0  |

| INPUT SHUTDOWN<br>(CH 8-15)     | 0x19h   | R/W | 0x00    | IN_<br>PS_15  | IN_<br>PS_14  | IN_<br>PS_13  | IN_<br>PS_12  | IN_<br>PS_11  | IN_<br>PS_10  | IN_<br>PS_9  | IN_<br>PS_8  |

| INPUT SHUTDOWN<br>(CH 16-23)    | 0x1Ah   | R/W | 0x00    | IN_<br>PS_23  | IN_<br>PS_22  | IN_<br>PS_21  | IN_<br>PS_20  | IN_<br>PS_19  | IN_<br>PS_18  | IN_<br>PS_17 | IN_<br>PS_16 |

| INPUT SHUTDOWN<br>(CH 24-31)    | 0x1Bh   | R/W | 0x00    | IN_<br>PS_31  | IN_<br>PS_30  | IN_<br>PS_29  | IN_<br>PS_28  | IN_<br>PS_27  | IN_<br>PS_26  | IN_<br>PS_25 | IN_<br>PS_24 |

| OUTPUT<br>SHUTDOWN<br>(CH 0-7)  | 0x1Eh   | R/W | 0x00    | OUT_<br>PS_7  | OUT_<br>PS_6  | OUT_<br>PS_5  | OUT_<br>PS_4  | OUT_<br>PS_3  | OUT_<br>PS_2  | OUT_<br>PS_1 | OUT_<br>PS_0 |

| OUTPUT<br>SHUTDOWN<br>(CH 8-15) | 0x1Fh   | R/W | 0x00    | OUT_<br>PS_15 | OUT_<br>PS_14 | OUT_<br>PS_13 | OUT_<br>PS_12 | OUT_<br>PS_11 | OUT_<br>PS_10 | OUT_<br>PS_9 | OUT_<br>PS_8 |

# Table 7. Video Input Selection Registers

| Register             | Address | R/W | Default | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2   | Bit 1  | Bit 0 |

|----------------------|---------|-----|---------|-------|-------|-------|-------|---------|---------|--------|-------|

| CH 0 OUTPUT          | 0x20h   | R/W | 0x00    |       | RSV   |       | ,     | SELECTE | D INPUT | CH[4:0 | ]     |

| CH 1 OUTPUT          | 0x21h   | R/W | 0x00    |       | RSV   |       | 5     | SELECTE | D INPUT | CH[4:0 | ]     |

| CH 2 OUTPUT          | 0x22h   | R/W | 0x00    |       | RSV   |       | 5     | SELECTE | D INPUT | CH[4:0 | ]     |

| CH 3 OUTPUT          | 0x23h   | R/W | 0x00    |       | RSV   |       | ,     | SELECTE | D INPUT | CH[4:0 | ]     |

| CH 4 OUTPUT          | 0x24h   | R/W | 0x00    |       | RSV   |       | ,     | SELECTE | D INPUT | CH[4:0 | ]     |

| CH 5 OUTPUT          | 0x25h   | R/W | 0x00    |       | RSV   |       | ,     | SELECTE | D INPUT | CH[4:0 | ]     |

| CH 6 OUTPUT          | 0x26h   | R/W | 0x00    |       | RSV   |       | ,     | SELECTE | D INPUT | CH[4:0 | ]     |

| CH 7 OUTPUT          | 0x27h   | R/W | 0x00    |       | RSV   |       | 5     | SELECTE | D INPUT | CH[4:0 | ]     |

| CH 8 OUTPUT          | 0x28h   | R/W | 0x00    |       | RSV   |       | ,     | SELECTE | D INPUT | CH[4:0 | ]     |

| CH 9 OUTPUT          | 0x29h   | R/W | 0x00    |       | RSV   |       | ,     | SELECTE | D INPUT | CH[4:0 | ]     |

| CH 10 OUTPUT         | 0x2Ah   | R/W | 0x00    |       | RSV   |       | ,     | SELECTE | D INPUT | CH[4:0 | ]     |

| CH 11 OUTPUT         | 0x2Bh   | R/W | 0x00    |       | RSV   |       | 5     | SELECTE | D INPUT | CH[4:0 | ]     |

| CH 12 OUTPUT         | 0x2Ch   | R/W | 0x00    |       | RSV   |       | 5     | SELECTE | D INPUT | CH[4:0 | ]     |

| CH 13 OUTPUT         | 0x2Dh   | R/W | 0x00    |       | RSV   |       | ,     | SELECTE | D INPUT | CH[4:0 | ]     |

| CH 14 OUTPUT         | 0x2Eh   | R/W | 0x00    |       | RSV   |       | ,     | SELECTE | D INPUT | CH[4:0 | ]     |

| CH 15 OUTPUT         | 0x2Fh   | R/W | 0x00    |       | RSV   |       |       | SELECTE | D INPUT | CH[4:0 | ]     |

| CH 16 OUTPUT (extra) | 0x30h   | R/W | 0x00    |       | RSV   |       | 5     | SELECTE | D INPUT | CH[4:0 | ]     |

# **REVISION HISTORY**

| Cł | nanges from Revision C (March 2013) to Revision D  | Page |

|----|----------------------------------------------------|------|

| •  | Changed layout of National Data Sheet to TI format | 26   |

# PACKAGE OPTION ADDENDUM

10-Dec-2020

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

|                  |        |              |                    |      |                |              | (6)                           |                     |              |                         |         |

| LMH6586VS/NOPB   | ACTIVE | TQFP         | PFC                | 80   | 119            | RoHS & Green | NIPDAU                        | Level-3-260C-168 HR | -40 to 85    | LMH6586VS               | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

www.ti.com 5-Jan-2022

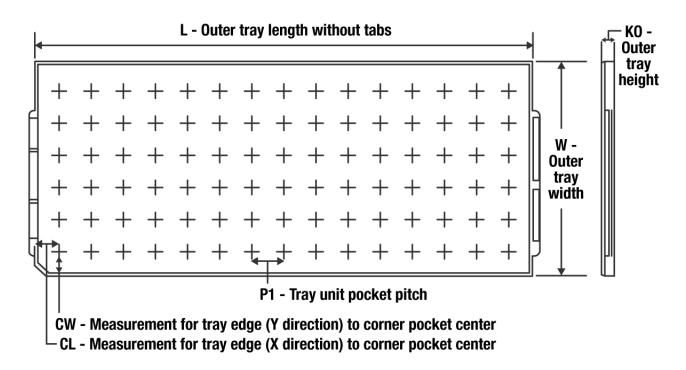

### **TRAY**

Chamfer on Tray corner indicates Pin 1 orientation of packed units.

\*All dimensions are nominal

| Device         | Package<br>Name | Package<br>Type | Pins | SPQ | Unit array<br>matrix | Max<br>temperature<br>(°C) | L (mm) | W<br>(mm) | Κ0<br>(μm) | P1<br>(mm) | CL<br>(mm) | CW<br>(mm) |

|----------------|-----------------|-----------------|------|-----|----------------------|----------------------------|--------|-----------|------------|------------|------------|------------|

| LMH6586VS/NOPB | PFC             | TQFP            | 80   | 119 | 7X17                 | 150                        | 322.6  | 135.9     | 7620       | 17.9       | 14.3       | 13.95      |

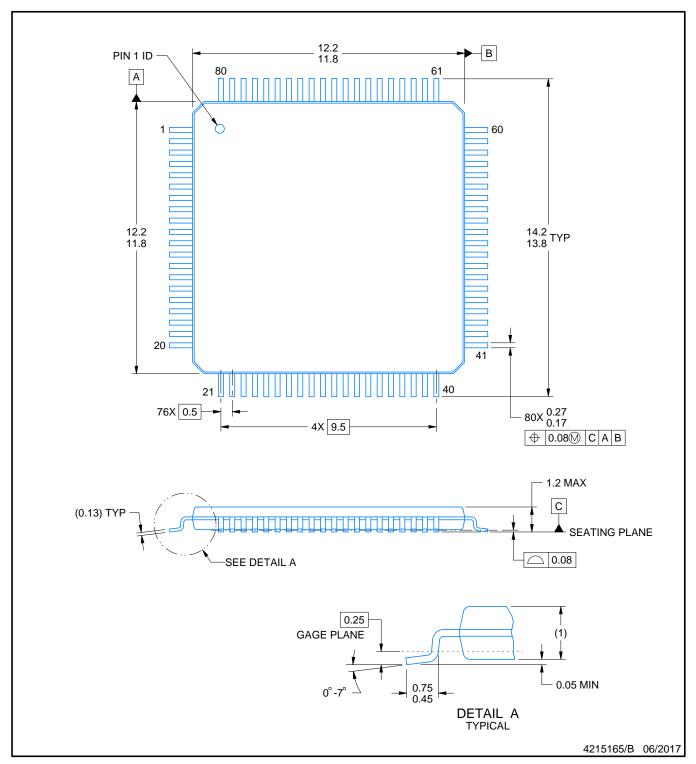

PLASTIC QUAD FLATPACK

### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. Reference JEDEC registration MS-026.

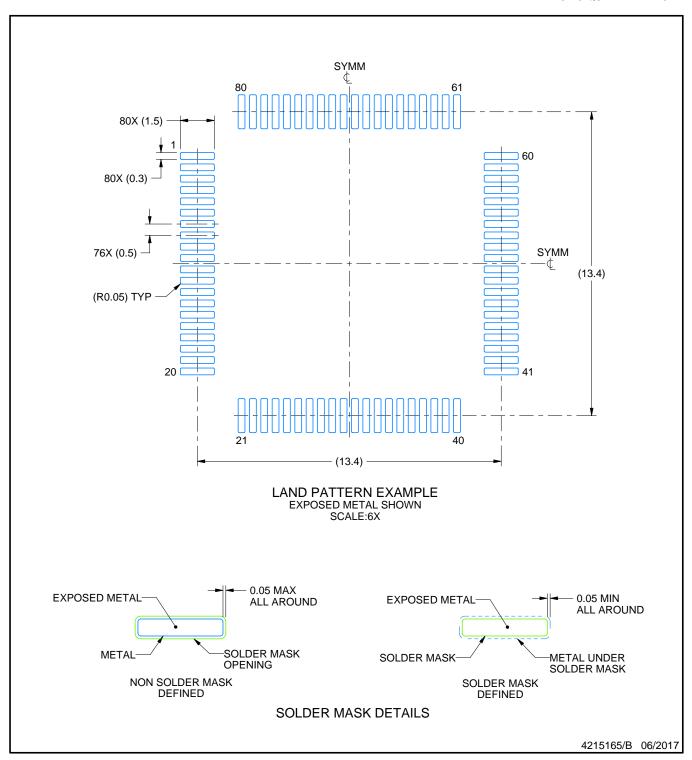

PLASTIC QUAD FLATPACK

NOTES: (continued)

- 4. Publication IPC-7351 may have alternate designs.

- Solder mask tolerances between and around signal pads can vary based on board fabrication site.

For more information, see Texas Instruments literature number SLMA004 (www.ti.com/lit/slma004).

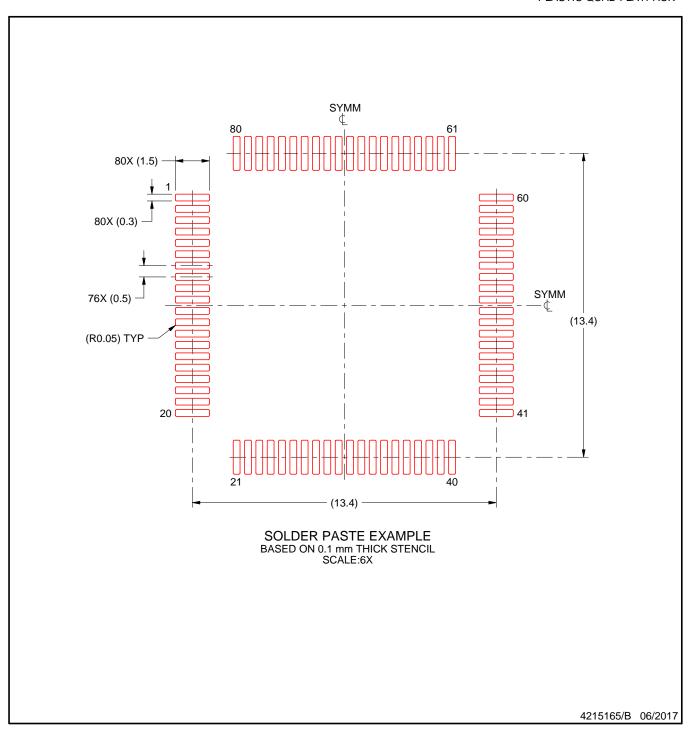

PLASTIC QUAD FLATPACK

NOTES: (continued)

<sup>7.</sup> Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

<sup>8.</sup> Board assembly site may have different recommendations for stencil design.

### **IMPORTANT NOTICE AND DISCLAIMER**

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated