SBAS690C -MAY 2015-REVISED APRIL 2018

ADS52J90

# ADS52J90 10-Bit, 12-Bit, 14-Bit, Multichannel, Low-Power, High-Speed ADC with LVDS, JESD Outputs

#### **Features**

- 16-Channel ADC Configurable to Convert 8, 16, or 32 Inputs

- 10-, 12-, and 14-Bit Resolution Modes

- Maximum ADC Conversion Rate:

- 100 MSPS in 10-Bit Mode

- 80 MSPS in 12-Bit Mode

- 65 MSPS in 14-Bit Mode

- 16 ADCs Configurable to Convert:

- 8 Inputs with a Sampling Rate of a 2X ADC Conversion Rate

- 16 Inputs with a Sampling Rate of a 1X ADC Conversion Rate

- 32 Inputs with a Sampling Rate of a 0.5X ADC Conversion Rate

- LVDS Outputs with 16X, 14X, 12X, and 10X Serialization

- 5-Gbps JESD Interface:

- Supported in 16-Input and 32-Input Modes

- JESD204B Subclass 0, 1, and 2

- 2, 4, or 8 Channels per JESD Lane

- Optional Digital I-Q Demodulator (1)

- Supplies: 1.2 V, 1.8 V

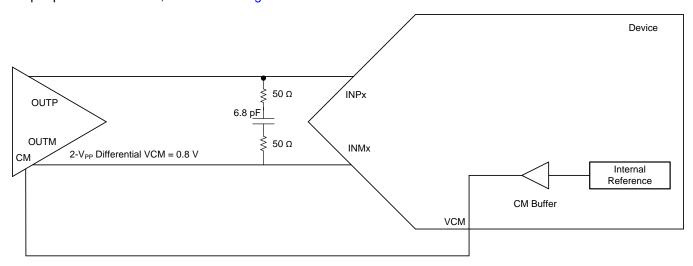

- 2-V<sub>PP</sub> Differential Input, 0.8-V Common-Mode

- Differential or Single-Ended Input Clock

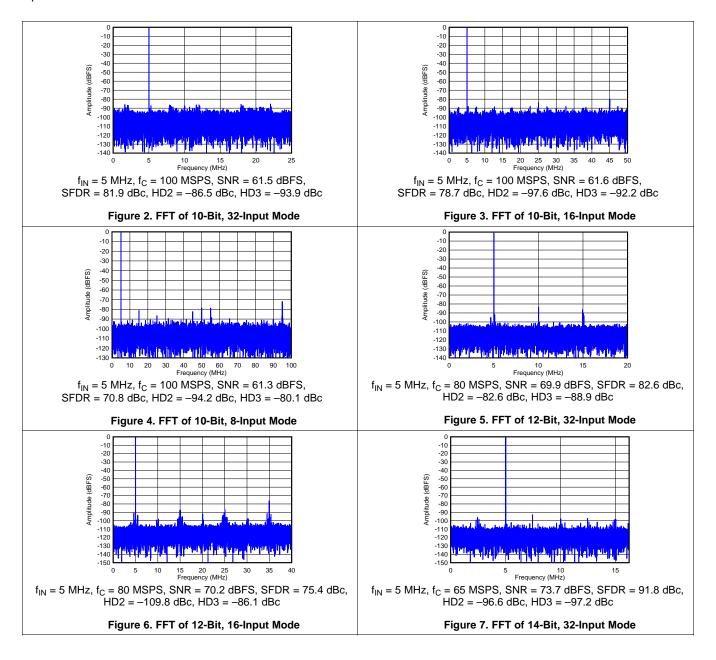

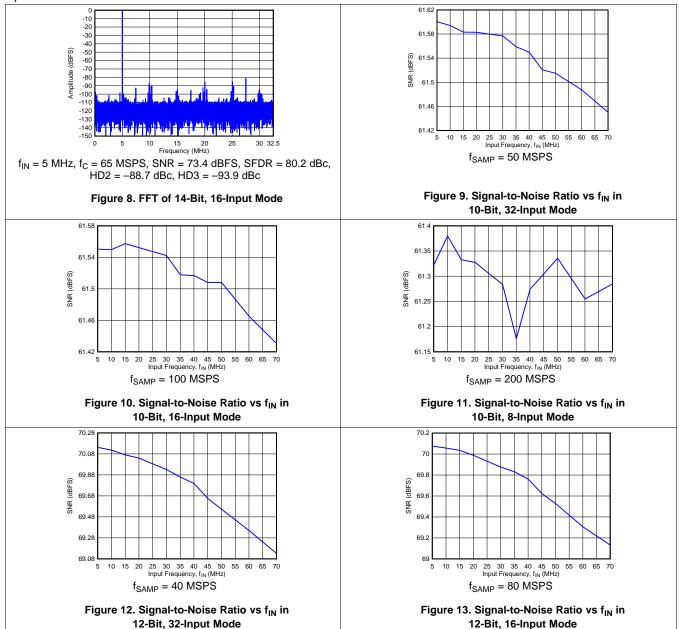

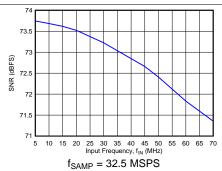

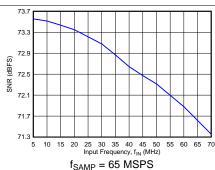

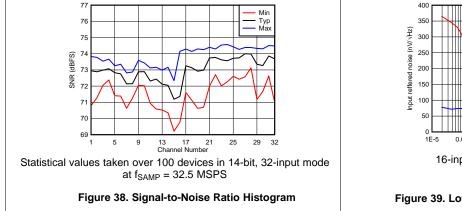

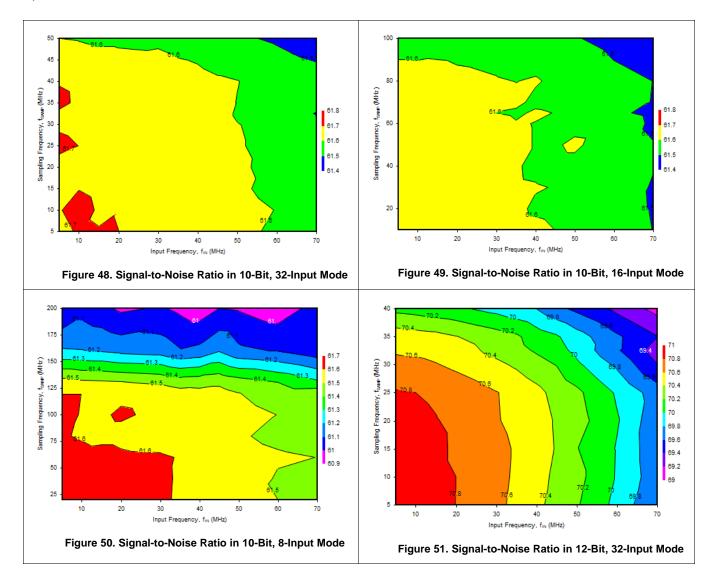

- Signal-to-Noise Ratio (SNR):

- 61 dBFS in 10-Bit Mode

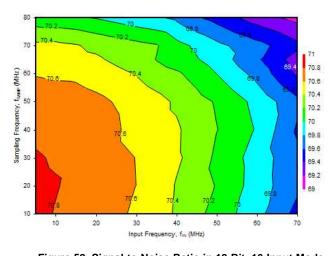

- 70 dBFS in 12-Bit Mode

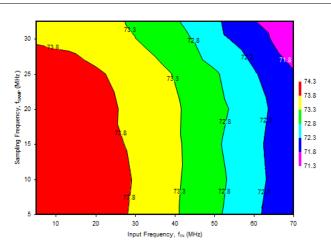

- 73.5 dBFS in 14-Bit Mode

- Power at 100 MSPS: 41 mW/Channel

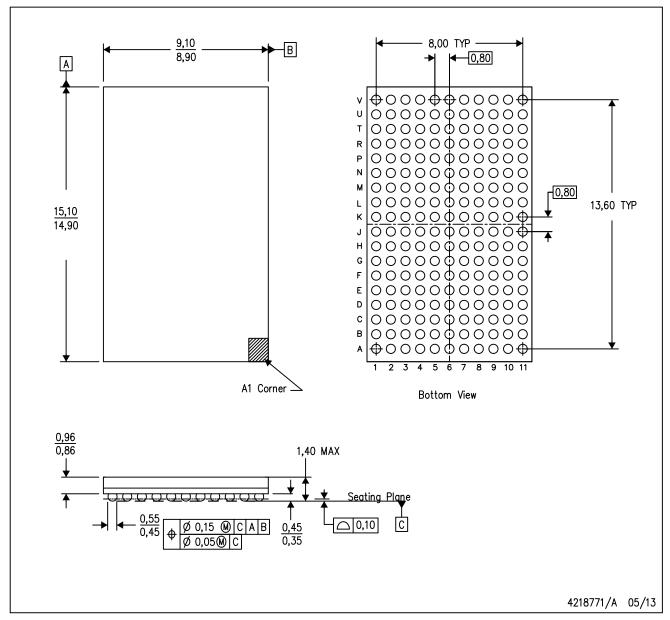

- Package: NFBGA-198 (9 mm x 15 mm)

- Pb-Free (RoHS Compliant) and Green

#### Applications

- Ultrasound Imaging

- Portable Instrumentation

- SONAR and RADAR

- High-Speed Multichannel Data Acquisition

## 3 Description

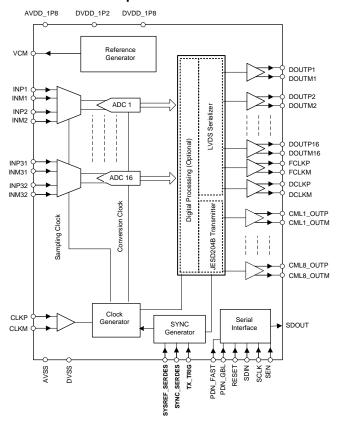

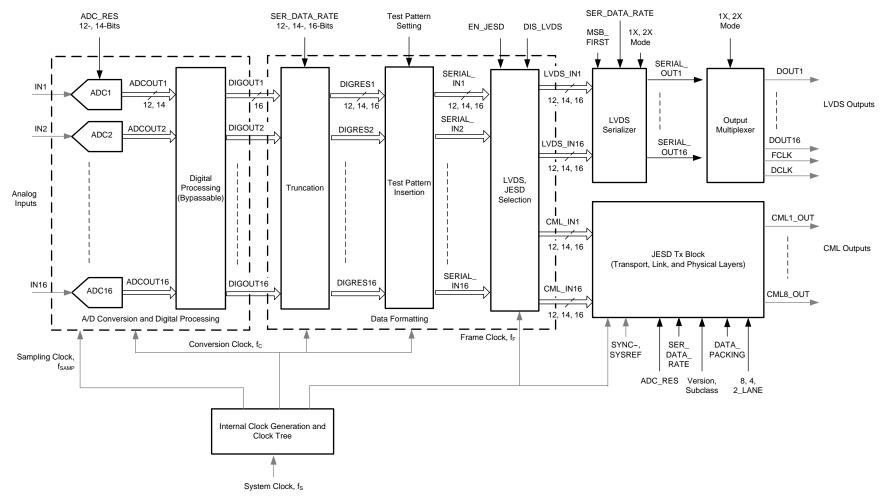

The ADS52J90 is a low-power, high-performance, 16channel, analog-to-digital converter (ADC). The conversion rate of each ADC goes up to a maximum of 100 MSPS in 10-bit mode. The maximum conversion rate reduces when the ADC resolution is set to a higher value.

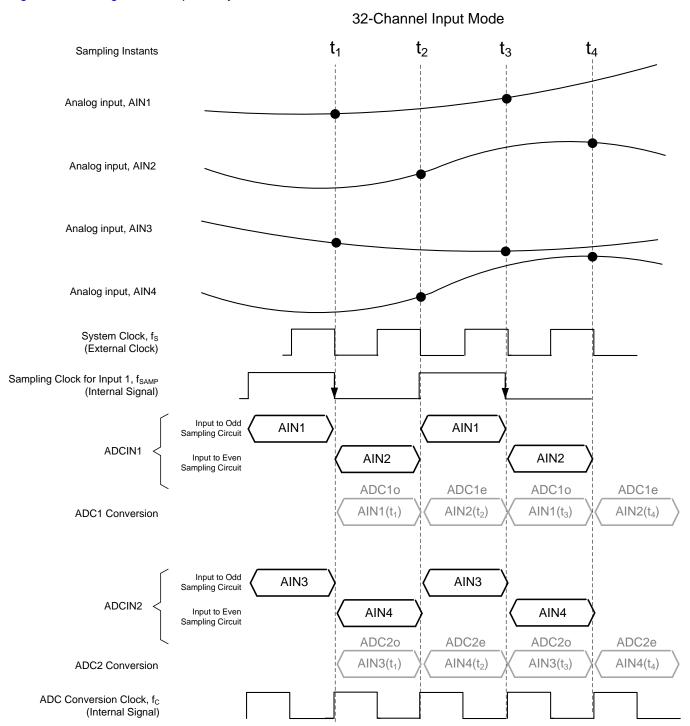

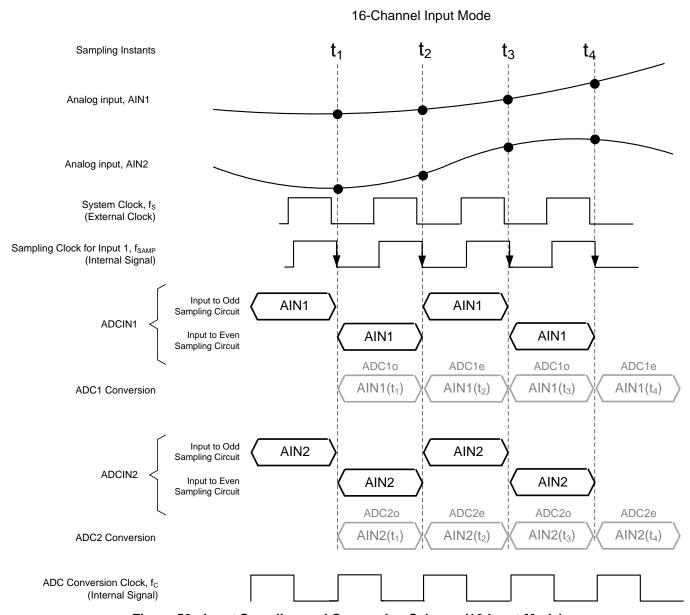

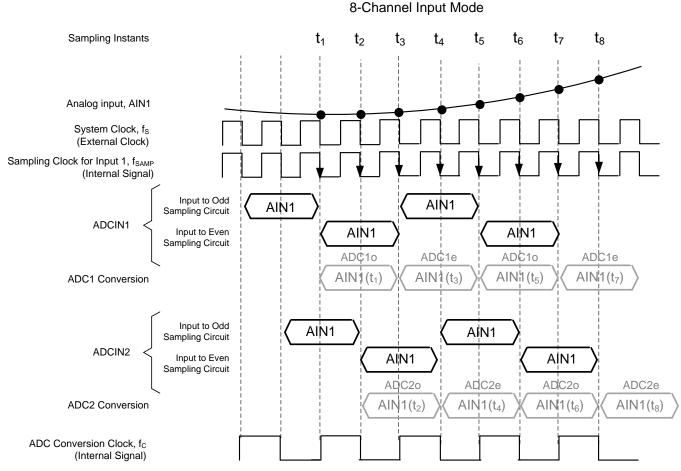

The device can be configured to accept 8, 16, or 32 inputs. In 32-input mode, each ADC alternately samples and converts two different inputs each at an effective sampling rate that is half of the ADC conversion rate. In 8-bit input mode, two ADCs convert the same input in an interleaved manner, resulting in an effective sampling rate that is twice the ADC conversion rate. The ADC is designed to scale its power with the conversion rate.

#### **Device Information**

| PART NUMBER | PACKAGE     | BODY SIZE (NOM)    |  |  |

|-------------|-------------|--------------------|--|--|

| ADS52J90    | NFBGA (198) | 9.00 mm × 15.00 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

#### Simplified Schematic

Not detailed in this document. For details and information, contact factory.

## **Table of Contents**

| 1 | Features 1                                   | 8.4 Device Functional Modes              | 73              |

|---|----------------------------------------------|------------------------------------------|-----------------|

| 2 | Applications 1                               | 8.5 Programming                          | 76              |

| 3 | Description 1                                | 9 Application and Implementation         | <mark>77</mark> |

| 4 | Revision History2                            | 9.1 Application Information              | 77              |

| 5 | Description (continued) 4                    | 9.2 Typical Application                  | 78              |

| 6 | Pin Configuration and Functions 5            | 9.3 Do's and Don'ts                      | 90              |

| 7 | Specifications                               | 10 Power Supply Recommendations          | <b>3</b> 90     |

| • | 7.1 Absolute Maximum Ratings                 | 10.1 Power Sequencing and Initialization | ion 90          |

|   | 7.2 ESD Ratings                              | 11 Layout                                | 92              |

|   | 7.3 Recommended Operating Conditions         | 11.1 Power Supply, Grounding, and B      | ypassing 92     |

|   | 7.4 Thermal Information                      | 11.2 Layout Guidelines                   | 92              |

|   | 7.5 Electrical Characteristics               | 11.3 Layout Example                      | 93              |

|   | 7.6 Digital Characteristics                  | 12 Register Map                          | 94              |

|   | 7.7 Timing Requirements: Signal Chain        | 12.1 ADC Registers                       | 94              |

|   | 7.8 Timing Requirements: JESD Interface      | 12.2 JESD Serial Interface Registers .   | 134             |

|   | 7.9 Timing Requirements: Serial Interface    | 13 Device and Documentation Supp         | ort 149         |

|   | 7.10 Typical Characteristics                 | 13.1 Documentation Support               | 149             |

|   | 7.11 Typical Characteristics: JESD Interface | 13.2 Community Resources                 | 149             |

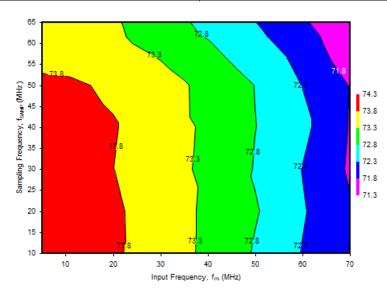

|   | 7.12 Typical Characteristics: Contour Plots  | 13.3 Trademarks                          |                 |

| 8 | Detailed Description                         | 13.4 Electrostatic Discharge Caution     | 149             |

|   | 8.1 Overview                                 | 13.5 Glossary                            | 149             |

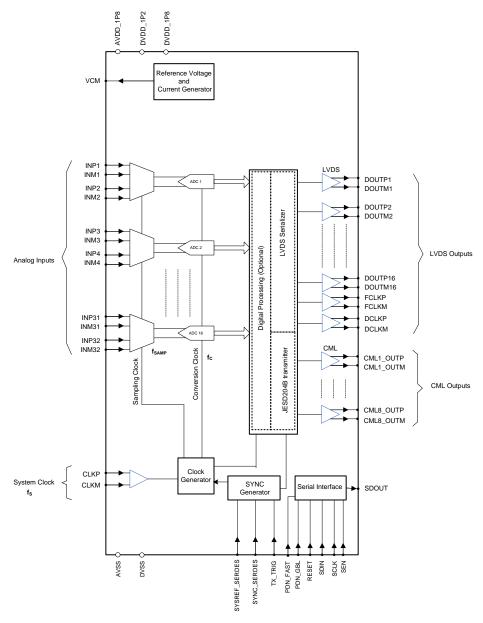

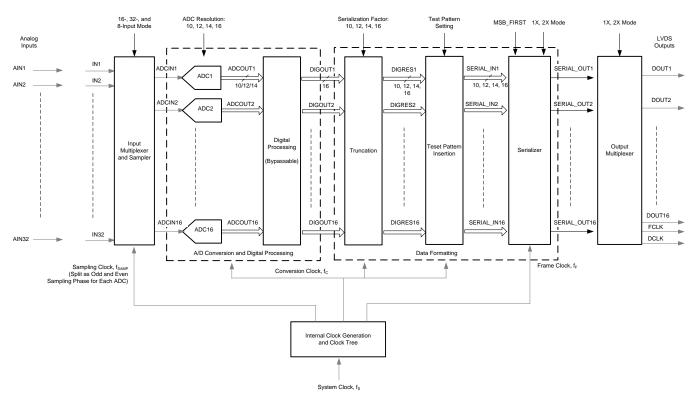

|   | 8.2 Functional Block Diagrams                | 14 Mechanical, Packaging, and Orde       |                 |

|   | 8.3 Feature Description                      | Information                              | 149             |

|   |                                              |                                          |                 |

## 4 Revision History

|   | _                 | . •                  |                            |

|---|-------------------|----------------------|----------------------------|

| • | Changed HPF_ROUND | _ENABLE register bit | (register 15, bit 5) to HP |

Changes from Revision B (August 2015) to Revision C

**Page**

| • | Changed HPF_ROUND_ENABLE register bit (register 15, bit 5) to HPF_ROUND_EN_CH1-8 and HPF_ROUND_EN_CH9-16 bits in last paragraph of Digital HPF section | 40   |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • | Changed Masking of the Various Reset Operations Resulting from SYNC~ or SYSREF table                                                                   |      |

|   | Added Interfacing SYNC~ and SYSREF Between the FPGA and ADCs section                                                                                   |      |

| • | Changed Mapping of Analog Inputs to LVDS Outputs (8-Input Mode, 1X Data Rate) table                                                                    | . 84 |

| • | Changed Mapping of Analog Inputs to LVDS Outputs (8-Input Mode, 2X Data Rate) table                                                                    | . 85 |

| • | Changed description for the value 001 in Pattern Mode Bit Description table                                                                            | . 99 |

| • | Changed bit 5 from HPF_ROUND_EN to HPF_ROUND_EN_CH1-8 in Register 15                                                                                   | 109  |

| • | Changed bit 5 from 0 to HPF_ROUND_EN_CH9-16 in Register 2Dh                                                                                            | 123  |

| • | Changed description for JESD_RESET1 in Register 70                                                                                                     | 135  |

|   | Changed description of JESD_RESET2 and JESD_RESET3 in Register 74                                                                                      |      |

## Changes from Revision A (June 2015) to Revision B

**Page**

| • | Added JESD Interface Optional Demodulator and Features bullets                                               | . 1 |

|---|--------------------------------------------------------------------------------------------------------------|-----|

| • | Changed Simplified Schematic                                                                                 | . 1 |

| • | Added JESD interface information to <i>Description</i> section                                               | . 4 |

| • | Added footnote 1 to Pin Functions table                                                                      | 6   |

| • | Changed description of SPI_DIG_EN pin in Pin Functions table                                                 | . 8 |

| • | Changed title of Current Consumption with LVDS Interface Enabled section of Electrical Characteristics table | 12  |

| • | Changed Current Consumption with JESD Interface Enabled section of Electrical Characteristics table          | 12  |

Submit Documentation Feedback

Copyright © 2015-2018, Texas Instruments Incorporated

#### www.ti.com

|          | Added SPI_DIG_EN to Digital Inputs section title of Digital Characteristics table             |                  |

|----------|-----------------------------------------------------------------------------------------------|------------------|

| •        | Changed V <sub>OC-CML</sub> parameter name in <i>JESD Interface Timing Requirements</i> table | 15               |

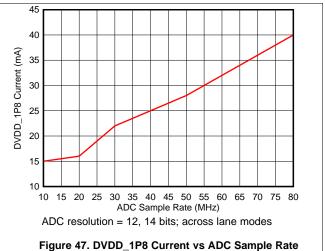

| •        | Added Figure 47                                                                               | 25               |

| •        | Added LVDS, JESD discussion to second paragraph of Overview section                           | <mark>5</mark> 1 |

| _        | Added Community Resources section                                                             | 140              |

| <u> </u> | Traded Community Traded Coulon                                                                |                  |

|          | nanges from Original (May 2015) to Revision A                                                 | Page             |

| Ch       |                                                                                               | Page             |

| Ch       | nanges from Original (May 2015) to Revision A                                                 | <b>Page</b>      |

## 5 Description (continued)

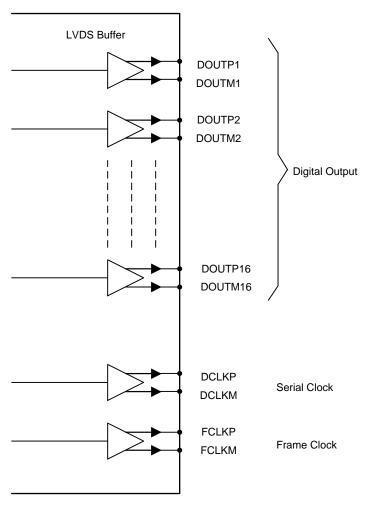

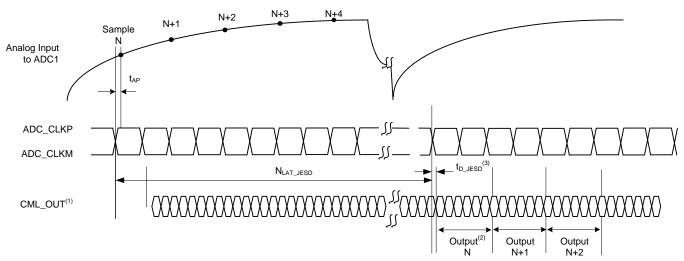

The ADC outputs are serialized and output through a low-voltage differential signaling (LVDS) interface along with a frame clock and a high-speed bit clock

The device also has an optional JESD204B interface while operating in the 16-input and 32-input modes. This interface runs up to 5 Gbps.

The ADS52J90 is available in a 9-mm  $\times$  15-mm, 0.8-mm pitch, NFBGA-198 package and is specified over a temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

# 6 Pin Configuration and Functions

ZZE Package NFBGA-198 (15 mm × 9 mm) Top View

|   | 1     | 2     | 3     | 4        | 5        | 6          | 7                  | 8        | 9         | 10        | 11        |

|---|-------|-------|-------|----------|----------|------------|--------------------|----------|-----------|-----------|-----------|

| Α | INM2  | INP2  | INP1  | AVDD_1P8 | SDIN     | RESET      | DVDD_1P2           | DVSS     | CML1_OUTP | CML1_OUTM | CML2_OUTP |

| В | INM3  | INP3  | INM1  | AVSS     | SEN      | SPI_DIG_EN | SCLK               | DVDD_1P2 | DOUTP1    | DOUTM1    | CML2_OUTM |

| С | INM5  | INP5  | INP4  | AVSS     | SDOUT    | PDN_FAST   | PDN_GBL            | DVDD_1P2 | DOUTP2    | DOUTM2    | CML3_OUTP |

| D | INM6  | INP6  | INM4  | AVSS     | NC       | TX_TRIG    | DVSS               | DVDD_1P2 | DOUTP3    | DOUTM3    | CML3_OUTM |

| Е | INM7  | INP7  | INM8  | INP8     | NC       | AVDD_1P8   | DVSS               | DVDD_1P8 | DOUTP4    | DOUTM4    | CML4_OUTP |

| F | INM9  | INP9  | INM10 | INP10    | VCM      | AVDD_1P8   | DVDD_1P2           | DVDD_1P8 | DOUTP5    | DOUTM5    | CML4_OUTM |

| G | INM11 | INP11 | INM12 | INP12    | AVDD_1P8 | AVDD_1P8   | DVDD_1P2           | DVDD_1P8 | DOUTP6    | DOUTM6    | DOUTM8    |

| Н | INM13 | INP13 | INM14 | INP14    | AVSS     | AVSS       | DVSS               | DVSS     | DOUTP7    | DOUTM7    | DOUTP8    |

| J | INM15 | INP15 | INM16 | INP16    | AVSS     | AVSS       | DVSS               | DVSS     | FCLKP     | DVDD_1P8  | DCLKP     |

| K | INM17 | INP17 | INM18 | INP18    | AVSS     | AVSS       | DVSS               | DVSS     | FCLKM     | DVSS      | DCLKM     |

| L | INM19 | INP19 | INM20 | INP20    | AVSS     | AVSS       | DVSS               | DVSS     | DOUTP10   | DOUTM10   | DOUTP9    |

| М | INM21 | INP21 | INM22 | INP22    | AVDD_1P8 | AVDD_1P8   | DVDD_1P2           | DVDD_1P8 | DOUTP11   | DOUTM11   | DOUTM9    |

| N | INM23 | INP23 | INM24 | INP24    | NC       | AVDD_1P8   | DVDD_1P2           | DVDD_1P8 | DOUTP12   | DOUTM12   | CML8_OUTM |

| Р | INM25 | INP25 | INM26 | INP26    | NC       | AVDD_1P8   | SYNCM_<br>SERDES   | DVDD_1P8 | DOUTP13   | DOUTM13   | CML8_OUTP |

| R | INM27 | INP27 | INM28 | AVSS     | AVSS     | DVSS       | SYNCP_<br>SERDES   | DVDD_1P2 | DOUTP14   | DOUTM14   | CML7_OUTM |

| Т | INM29 | INP29 | INP28 | AVSS     | AVSS     | DVDD_1P2   | SYSREFM_<br>SERDES | DVDD_1P2 | DOUTP15   | DOUTM15   | CML7_OUTP |

| U | INM30 | INP30 | INM32 | AVSS     | CLKM     | AVSS       | SYSREFP_<br>SERDES | DVDD_1P2 | DOUTP16   | DOUTM16   | CML6_OUTM |

| V | INM31 | INP31 | INP32 | AVDD_1P8 | CLKP     | AVSS       | DVDD_1P2           | DVSS     | CML5_OUTP | CML5_OUTM | CML6_OUTP |

#### Pin Functions<sup>(1)</sup>

|           | Pin Functions <sup>(1)</sup>                                                 |     |                                                                        |  |  |  |

|-----------|------------------------------------------------------------------------------|-----|------------------------------------------------------------------------|--|--|--|

|           | PIN                                                                          | I/O | DESCRIPTION                                                            |  |  |  |

| NAME      | NO.                                                                          |     |                                                                        |  |  |  |

| AVDD_1P8  | A4, E6, F6, G5, G6, M5,<br>M6, N6, P6, V4                                    | Р   | 1.8-V analog supply voltage                                            |  |  |  |

| AVSS      | B4, C4, D4, H5, H6, J5,<br>J6, K5, K6, L5, L6, R4, R5,<br>T4, T5, U4, U6, V6 | G   | Analog ground                                                          |  |  |  |

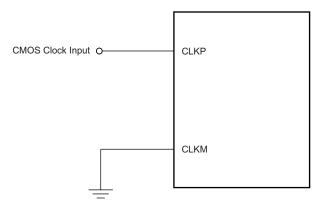

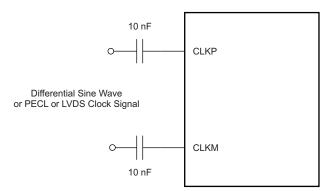

| CLKM      | U5                                                                           |     | Differential clock input pins. A single-ended clock is also supported. |  |  |  |

| CLKP      | V5                                                                           | I   | See the Clock Input section for further details.                       |  |  |  |

| CML1_OUTM | A10                                                                          |     | 1500                                                                   |  |  |  |

| CML1_OUTP | A9                                                                           | 0   | JESD output lane 1                                                     |  |  |  |

| CML2_OUTM | B11                                                                          |     | IFOD A ALL O                                                           |  |  |  |

| CML2_OUTP | A11                                                                          | 0   | JESD output lane 2                                                     |  |  |  |

| CML3_OUTM | D11                                                                          | _   | IFOR                                                                   |  |  |  |

| CML3_OUTP | C11                                                                          | 0   | JESD output lane 3                                                     |  |  |  |

| CML4_OUTM | F11                                                                          | _   |                                                                        |  |  |  |

| CML4_OUTP | E11                                                                          | 0   | JESD output lane 4                                                     |  |  |  |

| CML5_OUTM | V10                                                                          |     | 1500 5                                                                 |  |  |  |

| CML5_OUTP | V9                                                                           | 0   | JESD output lane 5                                                     |  |  |  |

| CML6_OUTM | U11                                                                          |     |                                                                        |  |  |  |

| CML6_OUTP | V11                                                                          | 0   | JESD output lane 6                                                     |  |  |  |

| CML7_OUTM | R11                                                                          |     |                                                                        |  |  |  |

| CML7_OUTP | T11                                                                          | 0   | JESD output lane 7                                                     |  |  |  |

| CML8_OUTM | N11                                                                          |     |                                                                        |  |  |  |

| CML8_OUTP | P11                                                                          | 0   | JESD output lane 8                                                     |  |  |  |

| DCLKM     | K11                                                                          |     |                                                                        |  |  |  |

| DCLKP     | J11                                                                          | 0   | LVDS bit clock output                                                  |  |  |  |

| DOUTM1    | B10                                                                          |     |                                                                        |  |  |  |

| DOUTP1    | B9                                                                           | 0   | LVDS data lane 1                                                       |  |  |  |

| DOUTM2    | C10                                                                          |     |                                                                        |  |  |  |

| DOUTP2    | C9                                                                           | 0   | LVDS data lane 2                                                       |  |  |  |

| DOUTM3    | D10                                                                          |     |                                                                        |  |  |  |

| DOUTP3    | D9                                                                           | 0   | LVDS data lane 3                                                       |  |  |  |

| DOUTM4    | E10                                                                          |     |                                                                        |  |  |  |

| DOUTP4    | E9                                                                           | 0   | LVDS data lane 4                                                       |  |  |  |

| DOUTM5    | F10                                                                          |     |                                                                        |  |  |  |

| DOUTP5    | F9                                                                           | 0   | LVDS data lane 5                                                       |  |  |  |

| DOUTM6    | G10                                                                          |     |                                                                        |  |  |  |

| DOUTP6    | G9                                                                           | 0   | LVDS data lane 6                                                       |  |  |  |

| DOUTM7    | H10                                                                          |     |                                                                        |  |  |  |

| DOUTP7    | H9                                                                           | 0   | LVDS data lane 7                                                       |  |  |  |

| DOUTM8    | G11                                                                          |     |                                                                        |  |  |  |

| DOUTP8    | H11                                                                          | 0   | LVDS data lane 8                                                       |  |  |  |

| DOUTM9    | M11                                                                          |     |                                                                        |  |  |  |

| DOUTP9    | L11                                                                          | 0   | LVDS data lane 9                                                       |  |  |  |

| DOUTM10   | L10                                                                          |     |                                                                        |  |  |  |

| DOUTP10   | L9                                                                           | 0   | LVDS data lane 10                                                      |  |  |  |

| DOUTM11   | M10                                                                          |     |                                                                        |  |  |  |

| DOUTP11   | M9                                                                           | 0   | LVDS data lane 11                                                      |  |  |  |

| DOUTM12   | N10                                                                          |     |                                                                        |  |  |  |

| DOUTP12   |                                                                              | 0   | LVDS data lane 12                                                      |  |  |  |

| DOUTF12   | N9                                                                           |     |                                                                        |  |  |  |

<sup>(1)</sup> If the JESD interface is not used, then do not connect the CMLx, SYNCx, and SYSREFx pins. If the LVDS interface is not used, then do not connect DOUTx, DCLKx, and FCLKx.

## Pin Functions<sup>(1)</sup> (continued)

|          | PIN                                                           |     |                                                                                           |

|----------|---------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------|

| NAME     | NO.                                                           | I/O | DESCRIPTION                                                                               |

| DOUTM13  | P10                                                           |     |                                                                                           |

| DOUTP13  | P9                                                            | 0   | LVDS data lane 13                                                                         |

| DOUTM14  | R10                                                           |     |                                                                                           |

| DOUTP14  | R9                                                            | 0   | LVDS data lane 14                                                                         |

| DOUTM15  | T10                                                           |     |                                                                                           |

| DOUTP15  | T9                                                            | 0   | LVDS data lane 15                                                                         |

| DOUTM16  | U10                                                           |     |                                                                                           |

| DOUTP16  | U9                                                            | 0   | LVDS data lane 16                                                                         |

| DVDD_1P2 | A7, B8, C8, D8, F7, G7, M7, N7, R8, T6, T8, U8, V7            | Р   | 1.2-V digital supply voltage                                                              |

| DVDD_1P8 | E8, F8, G8, J10, M8, N8,<br>P8                                | Р   | 1.8-V digital supply voltage                                                              |

| DVSS     | A8, D7, E7, H7, H8, J7,<br>J8, K7, K8, K10, L7, L8,<br>R6, V8 | G   | Digital ground                                                                            |

| FCLKM    | K9                                                            | 0   | LVDS frame clock output                                                                   |

| FCLKP    | J9                                                            |     | LVDO ITAITIE CIOCK OULPUL                                                                 |

| INM1     | B3                                                            | 1   | Differential analog input 1 pins; see Table 1 for mapping to external inputs in 8-, 16-,  |

| INP1     | A3                                                            | !   | and 32-input modes                                                                        |

| INM2     | A1                                                            | 1   | Differential analog input 2 pins; see Table 1 for mapping to external inputs in 8-, 16-,  |

| INP2     | A2                                                            | !   | and 32-input modes                                                                        |

| INM3     | B1                                                            | 1   | Differential analog input 3 pins; see Table 1 for mapping to external inputs in 8-, 16-,  |

| INP3     | B2                                                            | ı   | and 32-input modes                                                                        |

| INM4     | D3                                                            |     | Differential analog input 4 pins; see Table 1 for mapping to external inputs in 8-, 16-,  |

| INP4     | C3                                                            | 1   | and 32-input modes                                                                        |

| INM5     | C1                                                            |     | Differential analog input 5 pins; see Table 1 for mapping to external inputs in 8-, 16-,  |

| INP5     | C2                                                            | 1   | and 32-input modes                                                                        |

| INM6     | D1                                                            |     | Differential analog input 6 pins; see Table 1 for mapping to external inputs in 8-, 16-,  |

| INP6     | D2                                                            | ı   | and 32-input modes                                                                        |

| INM7     | E1                                                            |     | Differential analog input 7 pins; see Table 1 for mapping to external inputs in 8-, 16-,  |

| INP7     | E2                                                            | I   | and 32-input modes                                                                        |

| INM8     | E3                                                            |     | Differential analog input 8 pins; see Table 1 for mapping to external inputs in 8-, 16-,  |

| INP8     | E4                                                            | I   | and 32-input modes                                                                        |

| INM9     | F1                                                            |     | Differential analog input 9 pins; see Table 1 for mapping to external inputs in 8-, 16-,  |

| INP9     | F2                                                            | I   | and 32-input modes                                                                        |

| INM10    | F3                                                            |     | Differential analog input 10 pins; see Table 1 for mapping to external inputs in 8-, 16-, |

| INP10    | F4                                                            | I   | and 32-input modes                                                                        |

| INM11    | G1                                                            |     | Differential analog input 11 pins; see Table 1 for mapping to external inputs in 8-, 16-, |

| INP11    | G2                                                            | I   | and 32-input modes                                                                        |

| INM12    | G3                                                            |     | Differential analog input 12 pins; see Table 1 for mapping to external inputs in 8-, 16-, |

| INP12    | G4                                                            | I   | and 32-input modes                                                                        |

| INM13    | H1                                                            |     | Differential analog input 13 pins; see Table 1 for mapping to external inputs in 8-, 16-, |

| INP13    | H2                                                            | I   | and 32-input modes                                                                        |

| INM14    | H3                                                            | 1   | Differential analog input 14 pins; see Table 1 for mapping to external inputs in 8-, 16-, |

| INP14    | H4                                                            |     | and 32-input modes                                                                        |

| INM15    | J1                                                            | 1   | Differential analog input 15 pins; see Table 1 for mapping to external inputs in 8-, 16-, |

| INP15    | J2                                                            |     | and 32-input modes                                                                        |

| INM16    | J3                                                            |     | Differential analog input 16 pins; see Table 1 for mapping to external inputs in 8-, 16-, |

| INP16    | J4                                                            | I   | and 32-input modes                                                                        |

| INM17    | K1                                                            |     | Differential analog input 17 pins; see Table 1 for mapping to external inputs in 8-, 16-, |

| INP17    | K2                                                            | ı   | and 32-input modes                                                                        |

|          |                                                               |     |                                                                                           |

## Pin Functions<sup>(1)</sup> (continued)

|              |                | Pin Fur            | nctions <sup>(1)</sup> (continued)                                                                                                                                                                  |  |  |  |

|--------------|----------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| i            | PIN            | 1/0                | DESCRIPTION                                                                                                                                                                                         |  |  |  |

| NAME         | NO.            | 1/0                | DESCRIPTION                                                                                                                                                                                         |  |  |  |

| INM18        | K3             |                    | Differential analog input 18 pins; see Table 1 for mapping to external inputs in 8-, 16-,                                                                                                           |  |  |  |

| INP18        | K4             | l                  | and 32-input modes                                                                                                                                                                                  |  |  |  |

| INM19        | L1             |                    | Differential analog input 19 pins; see Table 1 for mapping to external inputs in 8-,                                                                                                                |  |  |  |

| INP19        | L2             | and 32-input modes |                                                                                                                                                                                                     |  |  |  |

| INM20        | L3             |                    | Differential analog input 20 pins; see Table 1 for mapping to external inputs in 8-, 16-,                                                                                                           |  |  |  |

| INP20        | L4             | - I                | and 32-input modes                                                                                                                                                                                  |  |  |  |

| INM21        | M1             |                    | Differential analog input 21 pins; see Table 1 for mapping to external inputs in 8-, 16-,                                                                                                           |  |  |  |

| INP21        | M2             | l                  | and 32-input modes                                                                                                                                                                                  |  |  |  |

| INM22        | M3             |                    | Differential analog input 22 pins; see Table 1 for mapping to external inputs in 8-, 16-,                                                                                                           |  |  |  |

| INP22        | M4             | - I                | and 32-input modes                                                                                                                                                                                  |  |  |  |

| INM23        | N1             |                    | Differential analog input 23 pins; see Table 1 for mapping to external inputs in 8-, 16-,                                                                                                           |  |  |  |

| INP23        | N2             | - I                | and 32-input modes                                                                                                                                                                                  |  |  |  |

| INM24        | N3             |                    | Differential analog input 24 pins; see Table 1 for mapping to external inputs in 8-, 16-,                                                                                                           |  |  |  |

| INP24        | N4             |                    | and 32-input modes                                                                                                                                                                                  |  |  |  |

| INM25        | P1             |                    | Differential analog input 25 pins; see Table 1 for mapping to external inputs in 8-, 16-,                                                                                                           |  |  |  |

| INP25        | P2             | - I                | and 32-input modes                                                                                                                                                                                  |  |  |  |

| INM26        | P3             |                    | Differential analog input 26 pins; see Table 1 for mapping to external inputs in 8-, 16-,                                                                                                           |  |  |  |

| INP26        | P4             | - 1                | and 32-input modes                                                                                                                                                                                  |  |  |  |

| INM27        | R1             |                    | Differential analog input 27 pins; see Table 1 for mapping to external inputs in 8-, 16-,                                                                                                           |  |  |  |

| INP27        | R2             | - I                | and 32-input modes                                                                                                                                                                                  |  |  |  |

| INM28        | R3             |                    | Differential analog input 28 pins; see Table 1 for mapping to external inputs in 8-, 16-,                                                                                                           |  |  |  |

| INP28        | Т3             | - I                | and 32-input modes                                                                                                                                                                                  |  |  |  |

| INM29        | T1             |                    | Differential analog input 29 pins; see Table 1 for mapping to external inputs in 8-, 16-,                                                                                                           |  |  |  |

| INP29        | T2             | - 1                | and 32-input modes                                                                                                                                                                                  |  |  |  |

| INM30        | U1             |                    | Differential analog input 30 pins; see Table 1 for mapping to external inputs in 8-, 16-,                                                                                                           |  |  |  |

| INP30        | U2             | _ I                | and 32-input modes                                                                                                                                                                                  |  |  |  |

| INM31        | V1             |                    | Differential analog input 31 pins; see Table 1 for mapping to external inputs in 8-, 16-,                                                                                                           |  |  |  |

| INP31        | V2             | - 1                | and 32-input modes                                                                                                                                                                                  |  |  |  |

| INM32        | U3             |                    | Differential analog input 32 pins; see Table 1 for mapping to external inputs in 8-, 16-,                                                                                                           |  |  |  |

| INP32        | V3             | - I                | and 32-input modes                                                                                                                                                                                  |  |  |  |

| NC           | D5, E5, N5, P5 | _                  | Do not connect; leave floating.                                                                                                                                                                     |  |  |  |

| PDN_FAST     | C6             | 1                  | Fast power-down control pin (active high) with an internal pulldown resistor of 20 kΩ. For active high, a 1.8-V logic level is recommended.                                                         |  |  |  |

| PDN_GBL      | C7             | 1                  | Global power-down control input (active high) with an internal pulldown resistor of 20 kΩ. For active high, a 1.8-V logic level is recommended.                                                     |  |  |  |

| SPI_DIG_EN   | B6             | I                  | Reserved for digital functionality. This pin can be left floating or be connected to the 1.8-V supply. This pin has an internal pullup resistor of $20 \text{ k}\Omega$ .                           |  |  |  |

| RESET        | A6             | 1                  | Hardware reset pin (active high) with an internal pulldown resistor of 20 kΩ. For active high, a 1.8-V logic level is recommended.                                                                  |  |  |  |

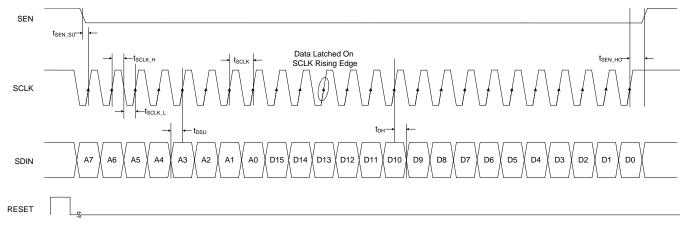

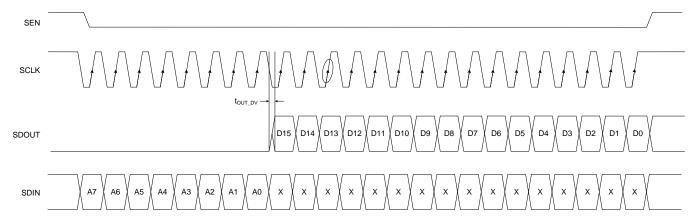

| SCLK         | B7             | 1                  | Serial interface clock input with an internal pulldown resistor of 20 k $\Omega$ . For active high,                                                                                                 |  |  |  |

| SDIN         | A5             | 1                  | <ul> <li>a 1.8-V logic level is recommended.</li> <li>Serial interface data input with an internal pulldown resistor of 20 kΩ. For active high, a</li> </ul>                                        |  |  |  |

|              |                |                    | 1.8-V logic level is recommended.  Serial interface data readout. High impedance when readout is disabled. 1.8-V logic.                                                                             |  |  |  |

| SDOUT        | C5             | 0                  | level is recommended.  Serial interface enable with an internal pullup resistor of 20 kΩ. 1.8-V logic level is                                                                                      |  |  |  |

| SEN          | B5             | 1                  | recommended.                                                                                                                                                                                        |  |  |  |

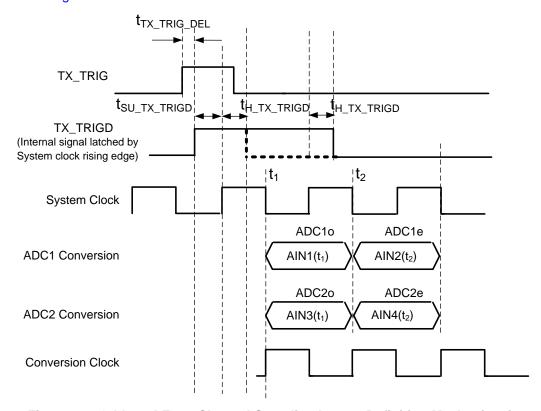

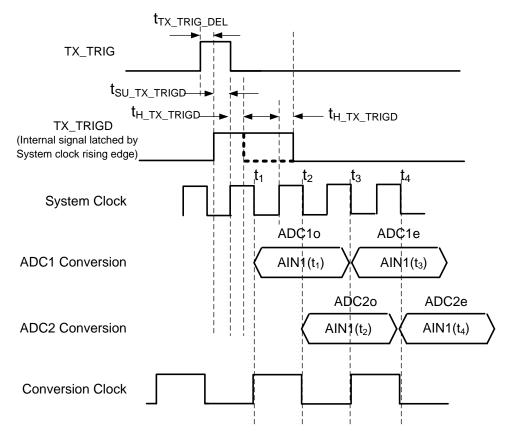

| TX_TRIG      | D6             | I                  | 1.8-V logic; a pulse on TX_TRIG must be applied after power-up to ensure that all internal clock dividers are synchronized $^{(2)}.$ Has an internal pull-down resistor of 20 k $\Omega$ to ground. |  |  |  |

| SYNCM_SERDES | P7             |                    | Frame synchronization input as per JESD204B standard                                                                                                                                                |  |  |  |

| SYNCP_SERDES | R7             | '                  | Traine synomenication input as per second standard                                                                                                                                                  |  |  |  |

(2) See the  $\underline{\textit{Device Synchronization Using TX\_TRIG}}$  section for more details on synchronization using TX\\_TRIG.

## Pin Functions<sup>(1)</sup> (continued)

| PIN            |     | I/O | DESCRIPTION                                                                                   |  |

|----------------|-----|-----|-----------------------------------------------------------------------------------------------|--|

| NAME           | NO. | 1/0 | DESCRIPTION                                                                                   |  |

| SYSREFM_SERDES | T7  |     | Frame clock and local multiframe clock (LMFC) synchronization input as per                    |  |

| SYSREFP_SERDES | U7  |     | JESD204B, subclass 1 standard                                                                 |  |

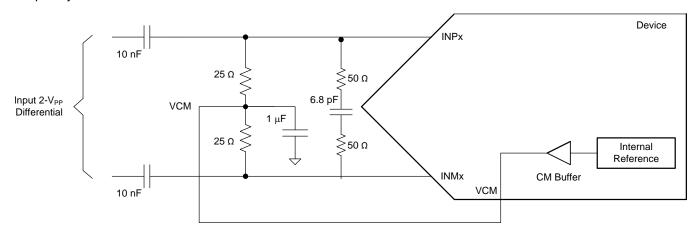

| VCM            | F5  | 0   | Common-mode output pin for biasing analog input signals. Connect a 10-µF capacitor to ground. |  |

## 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                                           |                                                                                                                            | MIN  | MAX                             | UNIT |  |

|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------|---------------------------------|------|--|

|                                                           | AVDD_1P8                                                                                                                   | -0.3 | 2.2                             |      |  |

| Voltage                                                   | DVDD_1P2                                                                                                                   | -0.3 | 1.35                            | V    |  |

|                                                           | DVDD_1P8                                                                                                                   | -0.3 | 2.2                             |      |  |

| Analog input pins (INM <sub>i</sub> , INP <sub>i</sub> )  |                                                                                                                            | -0.3 | Minimum [2.2, (AVDD_1P8 + 0.3)] | V    |  |

| CLKP, CLKM                                                |                                                                                                                            | -0.3 | Minimum [2.2, (AVDD_1P8 + 0.3)] | V    |  |

| Digital control pins                                      | PDN_GBL, PDN_FAST, RESET, SCLK, SDIN, SEN, TX_TRIG, SPI_DIG_EN, SYNCM_SERDES, SYNCP_SERDES, SYSREFM_SERDES, SYSREFP_SERDES | -0.3 | Minimum [2.2, (DVDD_1P8 + 0.3)] | V    |  |

| Maximum operating junction temperature, T <sub>JMax</sub> |                                                                                                                            |      | 105                             | °C   |  |

| Storage temperature, T <sub>s</sub>                       |                                                                                                                            |      | 150                             | °C   |  |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 7.2 ESD Ratings

|                                            |                         |                                                                     | VALUE | UNIT |

|--------------------------------------------|-------------------------|---------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> Electrostatic discharge | Floatrootatio diacharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±1000 | \/   |

|                                            | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101 (2) | ±250  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

|                         | PARAMETER                                    | TEST CONDITIONS                      | MIN                | NOM | MAX                | UNIT     |

|-------------------------|----------------------------------------------|--------------------------------------|--------------------|-----|--------------------|----------|

| TEMPERATURE             | <u> </u>                                     |                                      | •                  |     |                    |          |

| T <sub>A</sub>          | Ambient                                      |                                      | -40                |     | 85                 | °C       |

| SUPPLIES                |                                              |                                      |                    |     |                    |          |

| V <sub>(AVDD_1P8)</sub> | 1.8-V analog supply voltage                  |                                      | 1.7                | 1.8 | 1.9                | V        |

| V <sub>(DVDD_1P8)</sub> | 1.8-V digital supply voltage                 |                                      | 1.7                | 1.8 | 1.9                | V        |

| V <sub>(DVDD_1P2)</sub> | 1.2-V digital supply voltage                 |                                      | 1.15               | 1.2 | 1.25               | V        |

| ANALOG INPUT            | Г                                            |                                      |                    |     |                    |          |

| V <sub>(INx)</sub>      | Voltage range at analog input pins           |                                      | VCM - 0.5          |     | VCM + 0.5          | V        |

| V <sub>IN(CM)</sub>     | Input common-mode range at analog input pins |                                      | 0.7                | 0.8 | 0.9                | V        |

| V <sub>IN(FS)</sub>     | Input differential full-scale voltage        |                                      |                    | 2   |                    | $V_{PP}$ |

| F <sub>IN</sub>         | Analog input frequency range (1)             |                                      | 0                  |     | 70                 | MHz      |

| ANALOG OUTP             | PUT                                          |                                      |                    |     |                    |          |

| I <sub>(VCM)</sub>      | External loading on VCM pin                  | ±50-mV change in VCM                 |                    |     | 100                | μA       |

| CLOCK INPUT             |                                              |                                      |                    |     |                    |          |

|                         | System clock frequency                       | 16-input mode, 10-bit ADC resolution | 5                  |     | 100                |          |

|                         |                                              | 16-input mode, 12-bit ADC resolution | 5                  |     | 80                 |          |

|                         |                                              | 16-input mode, 14-bit ADC resolution | 5                  |     | 65                 |          |

| $f_S$                   |                                              | 32-input mode, 10-bit ADC resolution | 5                  |     | 100                | MSPS     |

|                         |                                              | 32-input mode, 12-bit ADC resolution | 5                  |     | 80                 |          |

|                         |                                              | 32-input mode, 14-bit ADC resolution | 5                  |     | 65                 |          |

|                         |                                              | 8-input mode, 10-bit ADC resolution  | 10                 |     | 200                |          |

|                         |                                              | Sine-wave, ac-coupled                | 0.7                |     |                    |          |

| $V_{CLKP} - V_{CLKM}$   | Differential clock amplitude                 | LVPECL, ac-coupled                   |                    | 1.6 |                    | $V_{PP}$ |

|                         |                                              | LVDS, ac-coupled                     | 0.35               | 0.7 |                    |          |

| V <sub>CLKP</sub>       | Single-ended clock amplitude                 | LVCMOS on CLKP with CLKM grounded    |                    | 1.8 |                    | $V_{PP}$ |

|                         | Input clock duty cycle                       |                                      | 40%                | 50% | 60%                |          |

| DIGITAL INPUT           | s                                            |                                      |                    |     |                    |          |

| V <sub>IH</sub>         | Digital input minimum, high level            |                                      | 0.75 ×<br>DVDD_1P8 | 1.8 |                    | V        |

| V <sub>IL</sub>         | Digital input maximum, low level             |                                      |                    | 0   | 0.25 ×<br>DVDD_1P8 | V        |

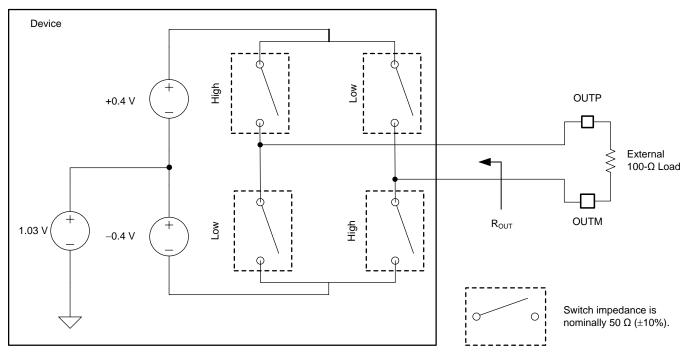

| DIGITAL OUTP            | UT (LVDS)                                    |                                      |                    |     |                    |          |

| R <sub>LOAD</sub>       | Differential load resistance                 | Between DOUTP and DOUTM              |                    | 100 |                    | Ω        |

| DIGITAL OUTP            | UT (CML)                                     |                                      |                    | -   |                    | -        |

| R <sub>CML</sub>        | Load resistance from each CML outp           | out to a common mode                 |                    | 50  |                    | Ω        |

<sup>(1)</sup> Performance degradation may be seen at high input frequencies.

#### 7.4 Thermal Information

| 7.7 11101            |                                              |             |       |

|----------------------|----------------------------------------------|-------------|-------|

|                      |                                              | ADS52J90    |       |

|                      | THERMAL METRIC <sup>(1)</sup>                | ZZE (NFBGA) | UNITS |

|                      |                                              | 198 PINS    |       |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 33.7        | °C/W  |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 4.9         | °C/W  |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 14.1        | °C/W  |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.1         | °C/W  |

| ΨЈВ                  | Junction-to-board characterization parameter | 14.1        | °C/W  |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | N/A         | °C/W  |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

#### 7.5 Electrical Characteristics

Typical values are across ADC resolution and input modes, unless otherwise specified. Typical values are at 25°C, AVDD\_1P8 = DVDD\_1P8 = 1.8 V, DVDD\_1P2 = 1.2 V. External  $100-\Omega$  differential load between LVDS outputs, 4-pF load capacitor from each LVDS output to ground, and 1X data rate mode.

All ADCs are powered up and the input signal is a -1-dBFS tone at 5 MHz applied on one channel at a time.

|                    | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | TEST CONDITIONS                                                                               | MIN  | TYP                  | MAX | UNIT |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------|----------------------|-----|------|--|

| ADC                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                               |      |                      |     |      |  |

| N                  | ADC resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32-channel input, 16-channel input                                                            | 10   |                      | 14  | Bits |  |

| N <sub>adc</sub>   | ADC resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8-channel input                                                                               |      | 10                   |     | Dita |  |

|                    | Number of ADCs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                               |      | 16                   |     | ADCs |  |

| CLOCK DO           | MAINS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                               |      |                      | •   |      |  |

|                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10-bit ADC resolution                                                                         |      |                      | 100 |      |  |

| f <sub>C</sub>     | Conversion rate of each ADC (conversion clock frequency)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12-bit ADC resolution                                                                         |      |                      | 80  | MSPS |  |

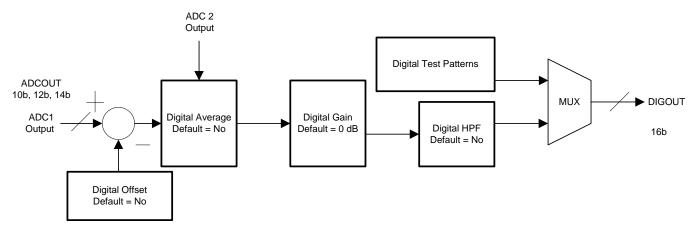

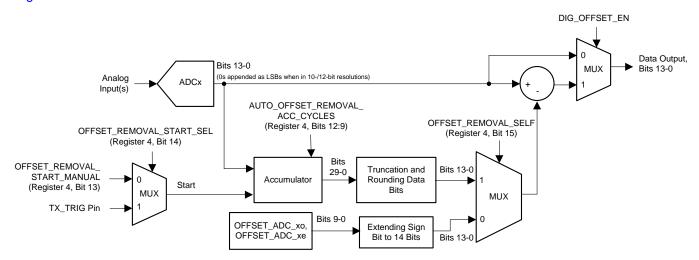

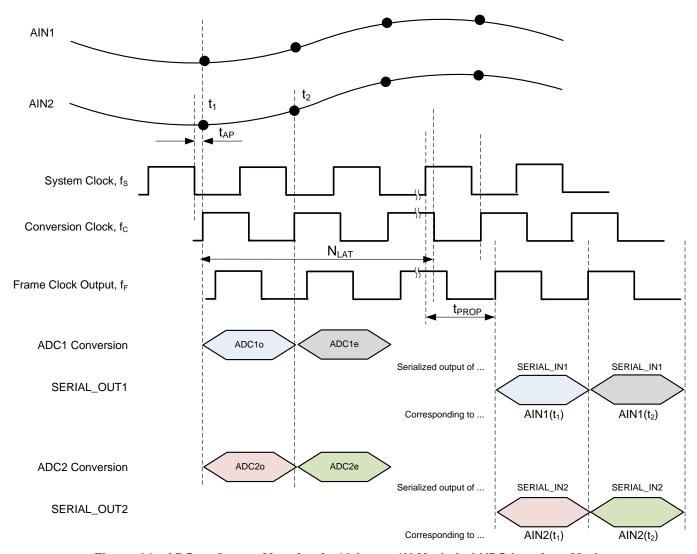

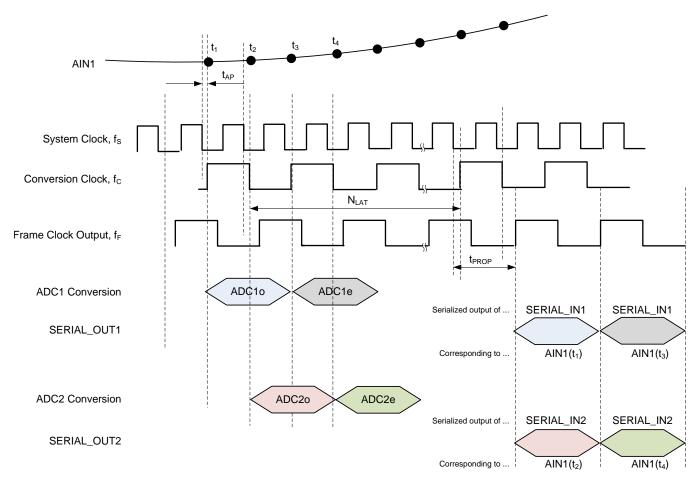

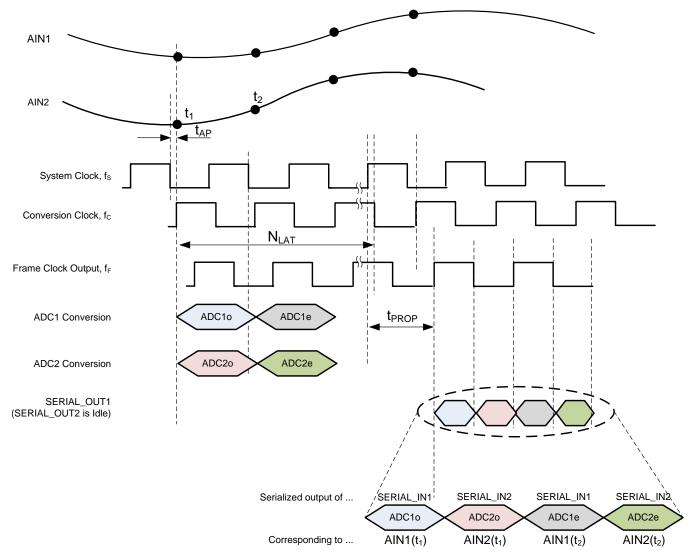

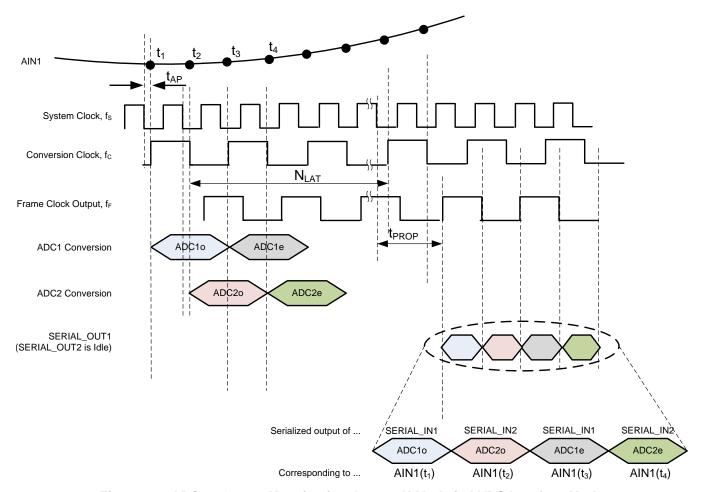

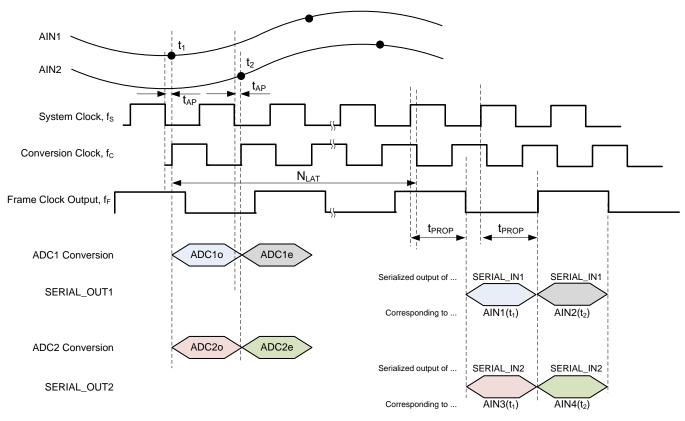

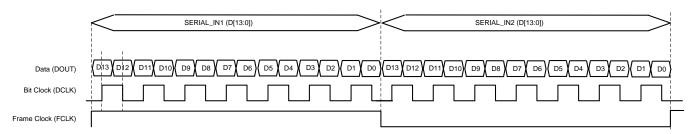

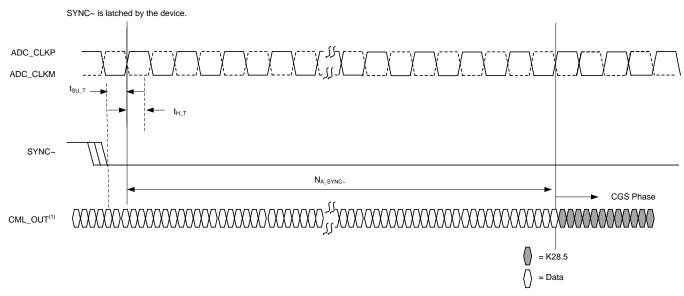

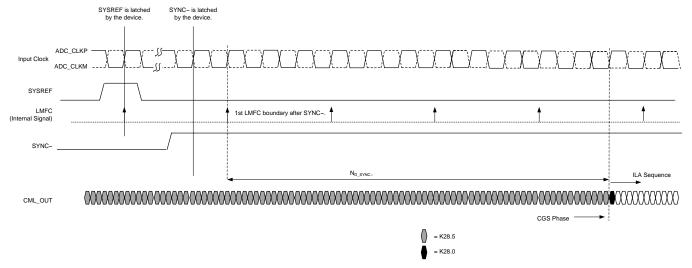

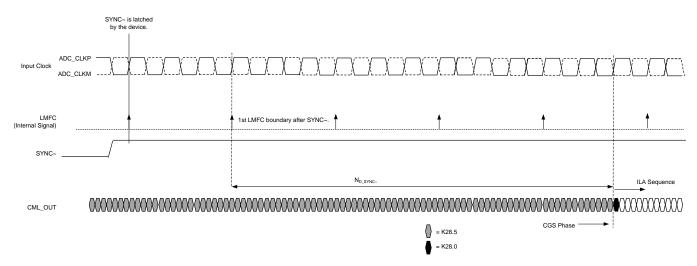

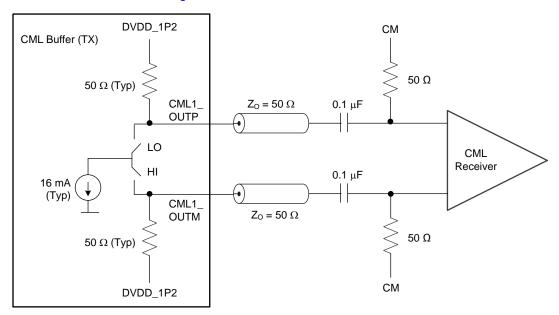

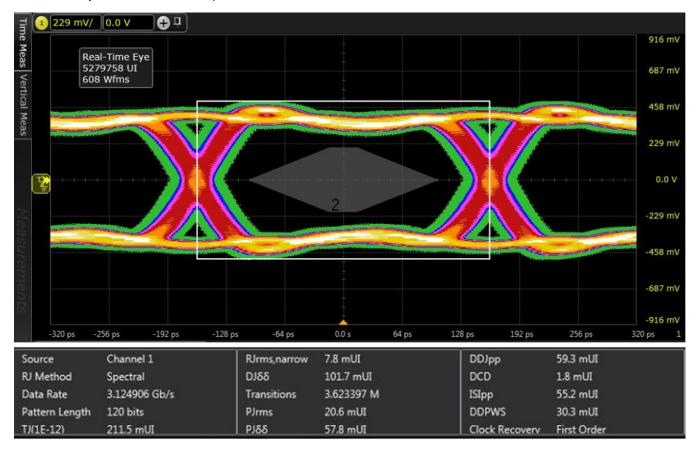

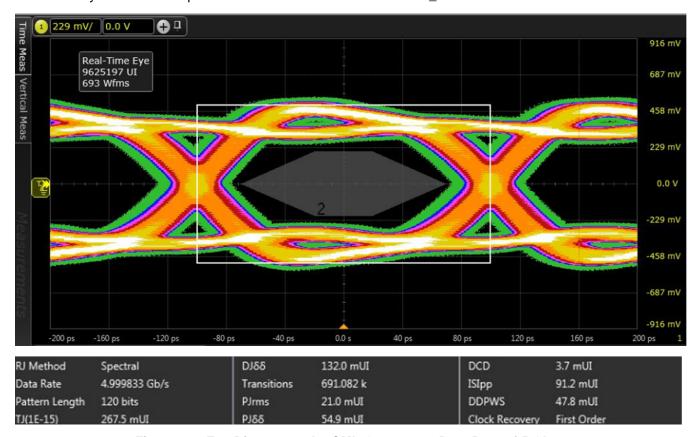

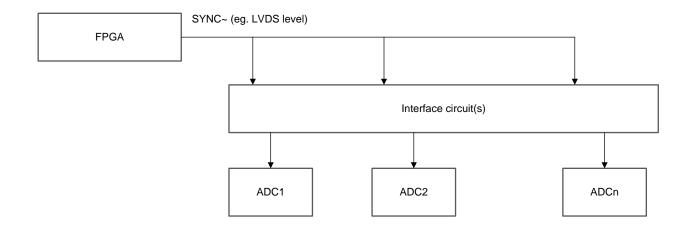

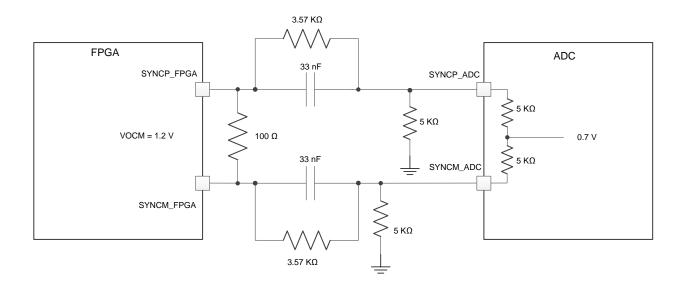

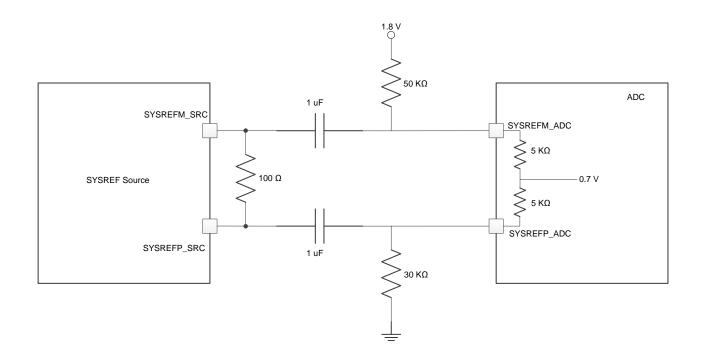

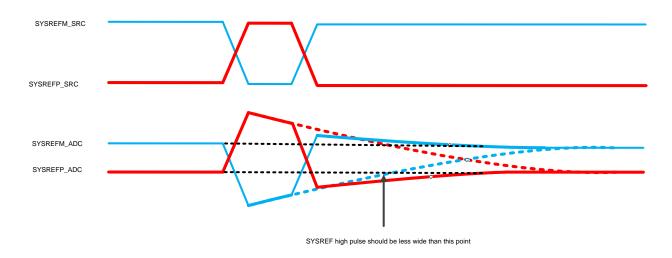

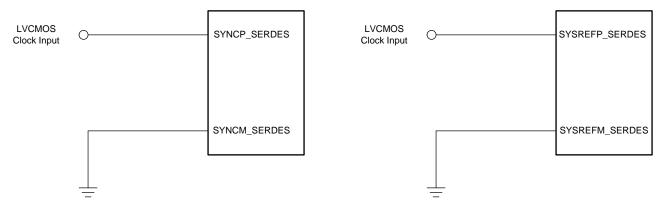

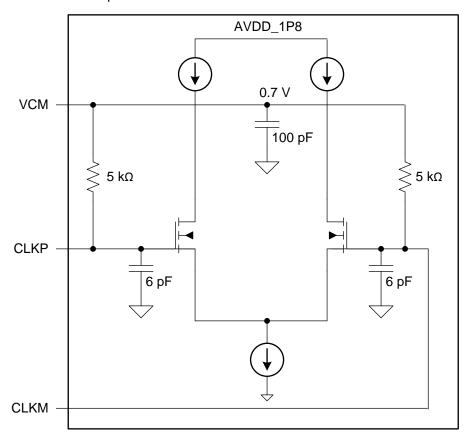

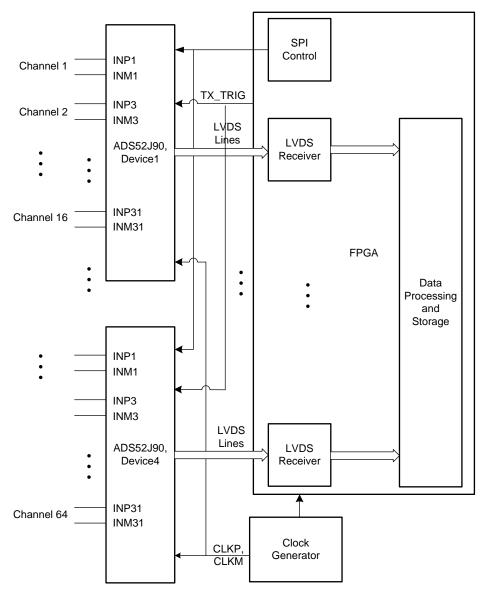

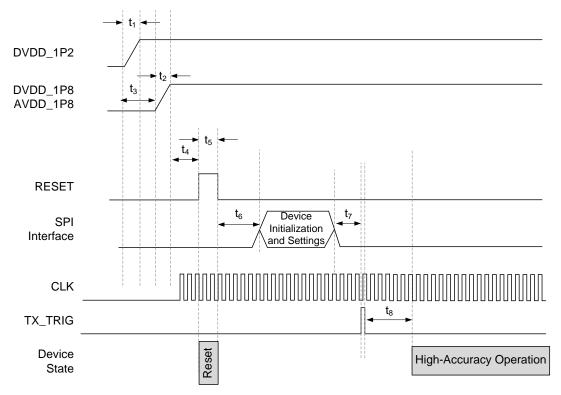

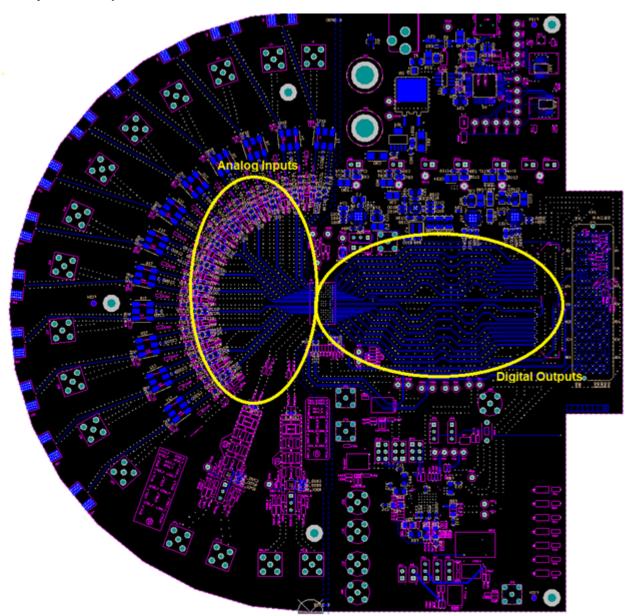

|                    | (complete all of the control of the | 14-bit ADC resolution                                                                         |      |                      | 65  |      |  |