# AWRL6432 Single-Chip 57- to 64GHz Automotive Radar Sensor

#### 1 Features

- **FMCW Transceiver**

- Integrated PLL, transmitter, receiver, baseband and ADC

- 57GHz 64GHz coverage with 7GHz continuous bandwidth

- 3 receive channels and 2 transmit channels

- Range typically up to 25m

- 11dBm typical output power per Tx

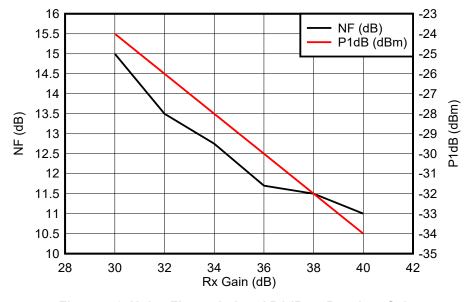

- 11dB Typical noise figure

- -89dBc/Hz typical phase noise at 1MHz

- FMCW operation

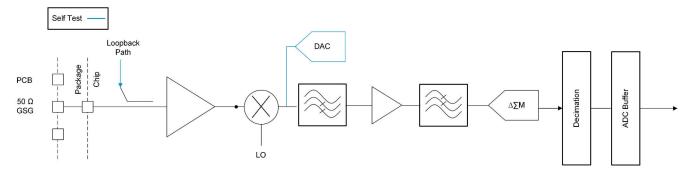

- 5MHz IF bandwidth, real-only Rx channels

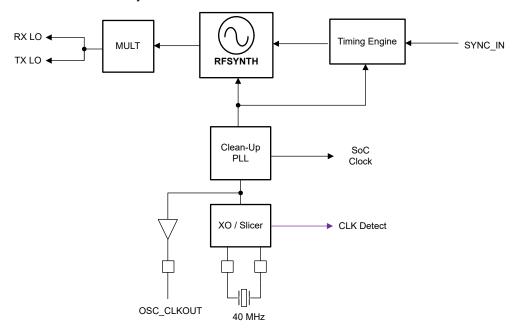

- Ultra-accurate chirp engine based on fractional-N PLL

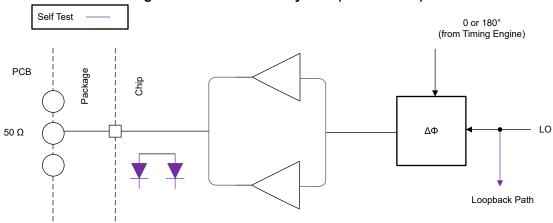

- Per transmitter binary phase shifter

- Processing elements

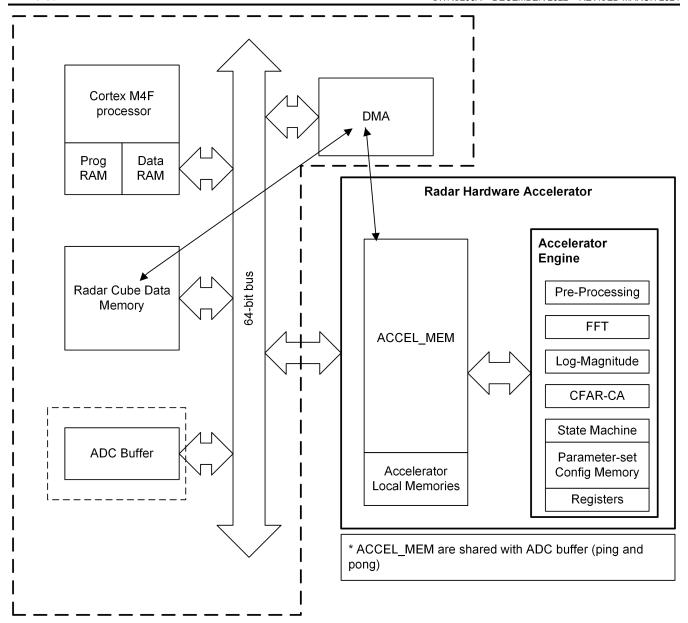

- Arm® M4F® core with single precision FPU (160MHz)

- TI Radar Hardware Accelerator (HWA 1.2) for FFT, log magnitude, and CFAR operations (80MHz)

- Supports multiple low-power modes

- Idle mode and deep sleep mode

- Power management

- 1.8V and 3.3V IO support

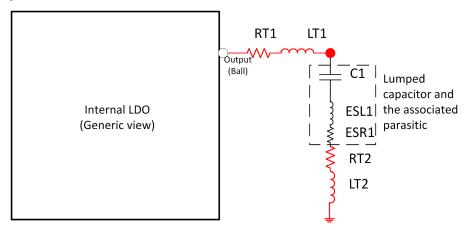

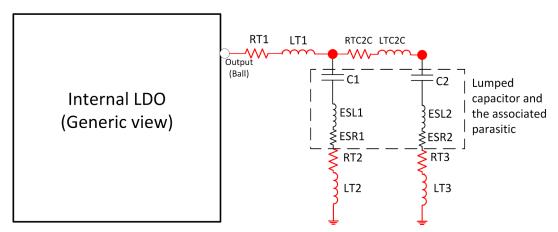

- Built-in LDO network for enhanced PSRR

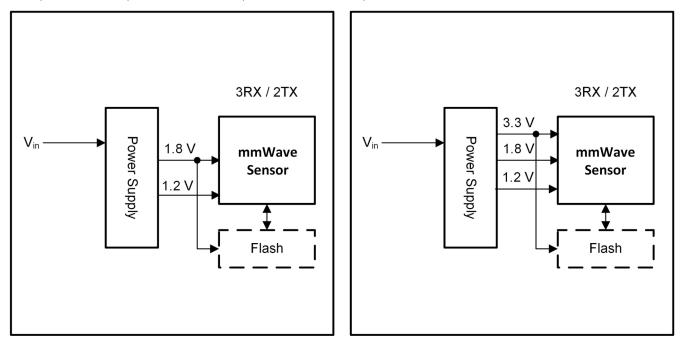

- BOM-Optimized and Power-Optimized modes

- One or two power rails for 1.8V IO mode, two or three power rails for 3.3V IO mode

- Built-in calibration and self-test

- Built-in Firmware (ROM)

- Self-Contained on chip calibration system

- Host Interface

- UART

- CAN-FD

- SPI

- LIN

- RDIF (Radar Data Interface) for raw ADC sample

- Other interfaces available to user application

- QSPI

- 12C

- JTAG

- GPIOs

- PWM Interface

- Internal memory

- 1MB of On-Chip RAM

- Configurable L3 shared memory for Radar Cube

- Data and Code RAM of (512/640/768KB)

- Functional Safety-Compliant Targeted

- Developed for functional safety applications

- Hardware integrity up to ASIL-B targeted

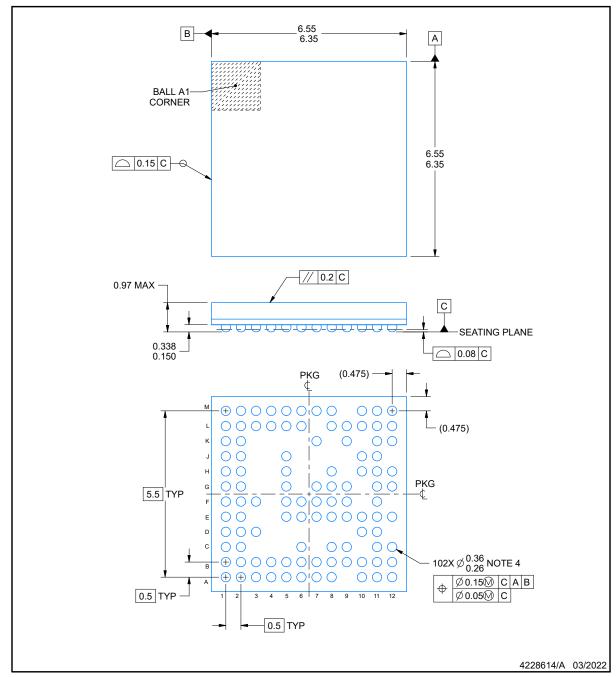

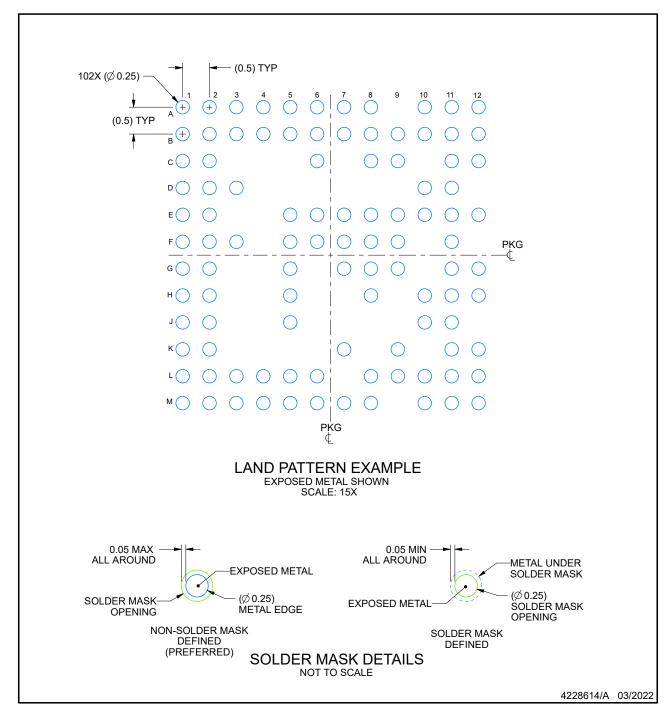

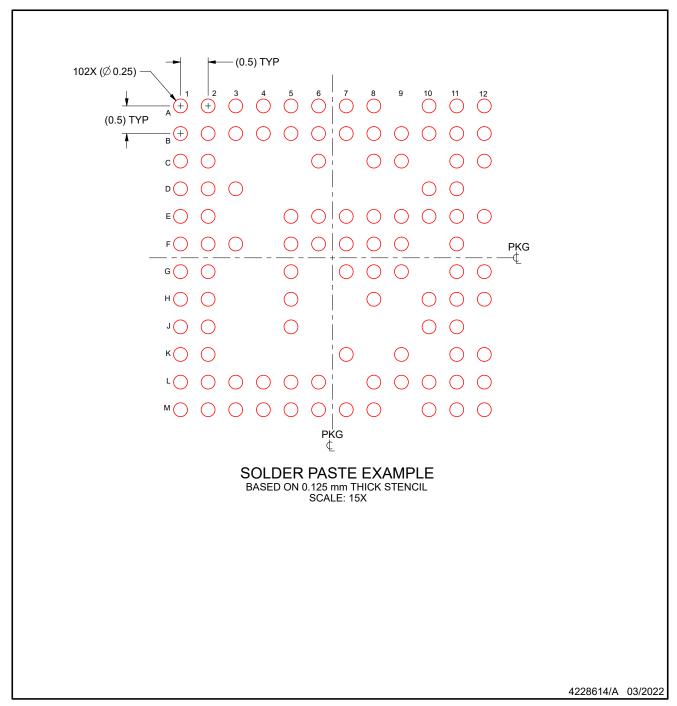

- FCCSP package having 12 x 12 BGA grid, 102 BGA balls; Package size: 6.45mm x 6.45mm

- AEC Q-100 Qualified

- Clock source

- 40.0MHz crystal for primary clock

- Supports externally driven clock (Square/Sine) at 40.0MHz

- 32kHz internal oscillator for low power operations

- Supports temperature operating range

- Operating junction temperature range: –40°C to

## TEXAS INSTRUMENTS www.ti.com

## 2 Applications

- · Interior cabin sensing

- · Child presence detection

- Occupancy detection

- Driver vital sign monitoring

- Seat belt reminder

- Intruder detection

- Gesture based HMI

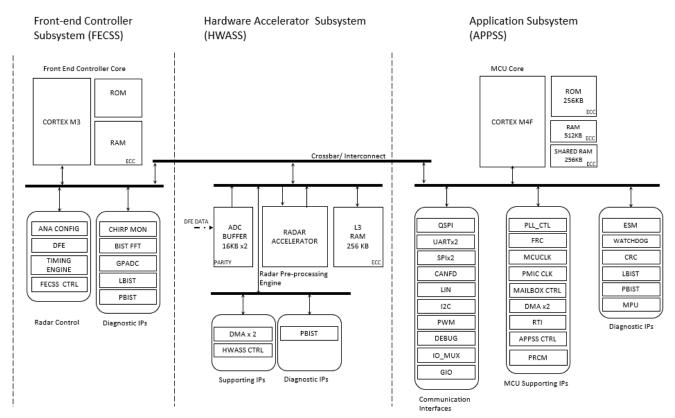

## 3 Description

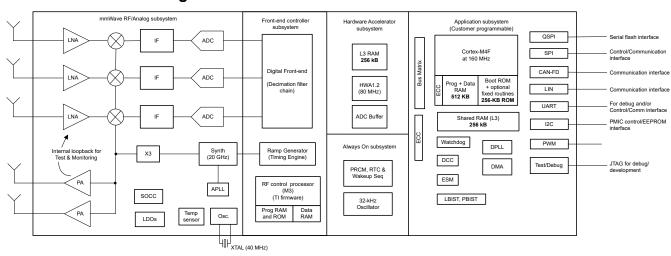

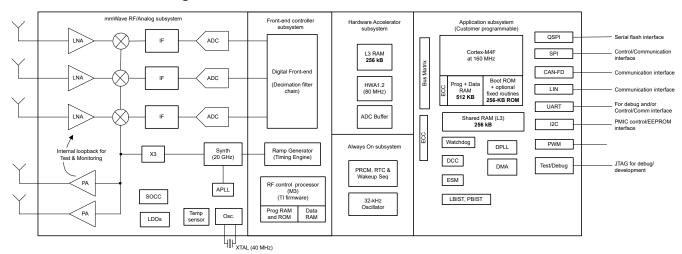

The AWRL6432 mmWave Sensor device is an integrated single chip mmWave sensor based on FMCW radar technology. The device is capable of operation in the 57GHz to 63.9GHz band and is partitioned into mainly four power domains:

- **RF/Analog Sub-System**: This block includes all the RF and Analog components required to transmit and receive the RF signals.

- Front-End Controller sub-System (FECSS): FECSS contains processor, responsible for radar front-end configuration, control, and calibration.

- Application Sub-System (APPSS): APPSS is where the device implements a user programmable ARM

Cortex M4 allowing for custom control and automotive interface applications. Top Sub-System (TOPSS) is

part of the APPSS power domain and contains the clocking and power management sub-blocks.

- Hardware Accelerator (HWA): HWA block supplements the APPSS by offloading common radar processing such as FFT, Constant False Alarm rate (CFAR), scaling, and compression.

AWRL6432 is specifically designed to have separate control for each of the above-mentioned power domains to control the states (power ON or OFF) based on use case requirements. The device also features the capability to exercise various low-power states like sleep and deep sleep, where low-power sleep mode is achieved by clock gating and by turning off the internal IP blocks of the device. The device also provides the option of keeping some contents of the device, like Application image or RF profile retained in such scenarios.

Additionally, the device is built with TI's low power 45nm RF CMOS process and enables unprecedented levels of integration in an extremely small form factor. AWRL6432 is designed for low power, self-monitored, ultra-accurate radar systems in the automotive space for applications like child presence detection, intrusion monitoring, gesture detection, and occupancy detection.

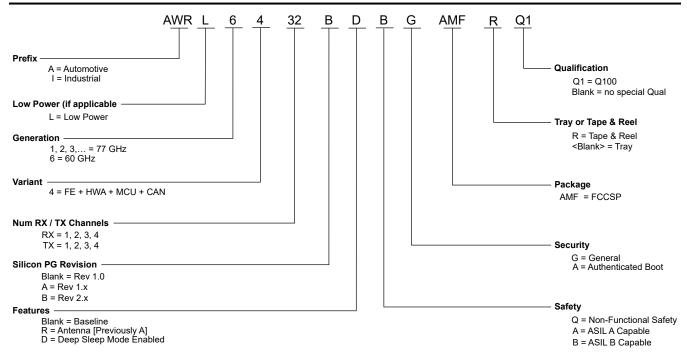

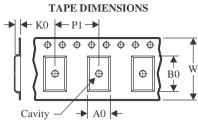

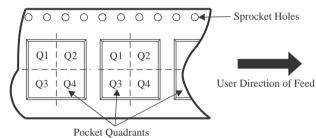

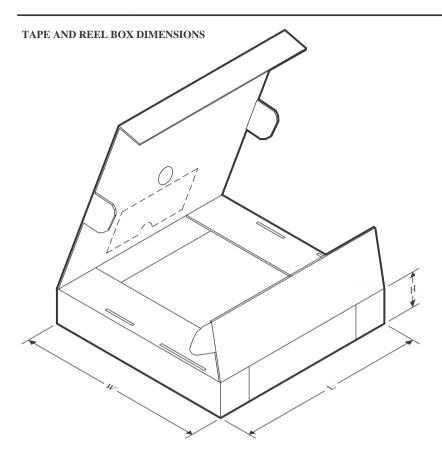

Table 3-1. Packaging Information

| PRODUCTION PART NUMBER <sup>(1)</sup> | PACKAGE          | BODY SIZE <sup>(2)</sup> | TRAY / TAPE<br>AND REEL | DESCRIPTION                                                                                           |

|---------------------------------------|------------------|--------------------------|-------------------------|-------------------------------------------------------------------------------------------------------|

| AWRL6432BDBGAMFRQ1                    | AMF (FCCSP, 102) | 6.45mm x 6.45mm          | Tape and Reel           | Automotive production variant. Functional Safety targeted. High quantity                              |

| AWRL6432BDBGAMFQ1                     | AMF (FCCSP, 102) | 6.45mm x 6.45mm          | Tray                    | Automotive production variant. Functional Safety targeted. Low quantity                               |

| AWRL6432BDBAAMFRQ1                    | AMF (FCCSP, 102) | 6.45mm x 6.45mm          | Tape and Reel           | Automotive production variant. Functional Safety targeted. High quantity. Authenticated Boot capable. |

| AWRL6432BDBAAMFQ1                     | AMF (FCCSP, 102) | 6.45mm x 6.45mm          | Tray                    | Automotive production variant. Functional Safety targeted. Low quantity. Authenticated Boot capable   |

<sup>(1)</sup> For more information, see Section 13

<sup>(2)</sup> For more information, see Section 11.1

# **4 Functional Block Diagram**

Figure 4-1. Functional Block Diagram

# **Table of Contents**

| 1 Features                                       | 7.13 Timing and Switching Characteristics | 30               |

|--------------------------------------------------|-------------------------------------------|------------------|

| 2 Applications                                   |                                           |                  |

| 3 Description                                    |                                           |                  |

| 4 Functional Block Diagram                       | 8.2 Functional Block Diagram              | 5                |

| 5 Device Comparison                              | 5 8.3 Subsystems                          | <mark>5</mark> 3 |

| 5.1 Related Products                             |                                           |                  |

| 6 Terminal Configurations and Functions          | 8 8.5 Memory Partitioning Options         | 59               |

| 6.1 Pin Diagrams                                 |                                           |                  |

| 6.2 Signal Descriptions                          |                                           | 6                |

| 7 Specifications                                 |                                           | 62               |

| 7.1 Absolute Maximum Ratings1                    | 7 10.1 Application Information            | 62               |

| 7.2 ESD Ratings 1                                | 7 10.2 Reference Schematic                | 62               |

| 7.3 Power-On Hours (POH)1                        | 7 11 Device and Documentation Support     | 63               |

| 7.4 Recommended Operating Conditions1            | 8 11.1 Device Nomenclature                | 6                |

| 7.5 VPP Specifications for One-Time Programmable | 11.2 Tools and Software                   | 64               |

| (OTP) eFuses1                                    | 8 11.3 Documentation Support              | 6 <sub>4</sub>   |

| 7.6 Power Supply Specifications2                 | 0 11.4 Support Resources                  | 6 <sub>4</sub>   |

| 7.7 Power Save Modes2                            | 6 11.5 Trademarks                         | 6                |

| 7.8 Peak Current Requirement per Voltage Rail2   | 7 11.6 Electrostatic Discharge Caution    | 6                |

| 7.9 RF Specification2                            | 8 11.7 Glossary                           | 6                |

| 7.10 Supported DFE Features2                     |                                           | 6                |

| 7.11 CPU Specifications3                         |                                           |                  |

| 7.12 Thermal Resistance Characteristics3         | 0 Information                             | 6                |

# **5 Device Comparison**

The following table compares the features of radar devices.

**Table 5-1. Device Features Comparison**

| FUNCTION                                             | AWRL6432        | AWRL1432                          | AWR6843AOP (1)   | AWR6843 (1)      | AWR1843 (1)      | AWR1843AOP (1)   | AWR1642      | AWR1443      |

|------------------------------------------------------|-----------------|-----------------------------------|------------------|------------------|------------------|------------------|--------------|--------------|

|                                                      |                 |                                   |                  |                  |                  |                  |              | AVICIA43     |

| Antenna on Package (AOP)                             | -               | -                                 | Yes              | -                | -                | Yes              | -            | -            |

| Number of receivers                                  | 3               | 3                                 | 4                | 4                | 4                | 4                | 4            | 4            |

| Number of transmitters                               | 2               | 2                                 | 3 <sup>(2)</sup> | 3 <sup>(2)</sup> | 3 <sup>(2)</sup> | 3 <sup>(2)</sup> | 2            | 3            |

| RF frequency range                                   | 57 to 64GHz     | 76 to 81GHz                       | 60 to 64 GHz     | 60 to 64 GHz     | 76 to 81 GHz     | 60 to 64GHz      | 76 to 81 GHz | 76 to 81 GHz |

| On-chip memory                                       | 1MB             | 1MB                               | 1.75MB           | 1.75MB           | 2MB              | 1.75MB           | 1.5MB        | 576KB        |

| Max I/F (Intermediate Frequency) (MHz)               | 5               | 5                                 | 10               | 10               | 10               | 10               | 5            | 5            |

| Max real sampling rate (Msps)                        | 12.5            | 12.5                              | 25               | 25               | 25               | 25               | 12.5         | 12.5         |

| Max complex sampling rate (Msps)                     | -               | -                                 | 12.5             | 12.5             | 12.5             | 12.5             | 6.25         | 6.25         |

| Safety and Security                                  |                 |                                   |                  |                  |                  |                  | •            |              |

| Functional Safety -Compliance                        | ASIL-B Targeted | ASIL-B<br>Targeted <sup>(3)</sup> | ASIL-B           | ASIL-B           | ASIL-B           | ASIL-B           | -            | -            |

| Device Security <sup>(4)</sup>                       | -               | -                                 | Yes              | Yes              | Yes              | Yes              | Yes          | -            |

| Processors                                           |                 |                                   |                  |                  |                  |                  | •            |              |

| MCU                                                  | M4F             | M4F                               | R4F              | R4F              | R4F              | R4F              | R4F          | R4F          |

| DSP                                                  | -               | -                                 | C674x            | C674x            | C674x            | C674x            | C674x        | -            |

| HWA                                                  | Yes             | Yes                               | Yes              | Yes              | Yes              | Yes              | -            | Yes          |

| Peripherals                                          |                 |                                   |                  |                  |                  |                  |              |              |

| Serial Peripheral Interface (SPI) ports              | 2               | 2                                 | 2                | 2                | 2                | 2                | 2            | 1            |

| Quad Serial Peripheral<br>Interface (QSPI)           | Yes             | Yes                               | Yes              | Yes              | Yes              | Yes              | Yes          | Yes          |

| Inter-Integrated Circuit (I2C) interface             | 1               | 1                                 | 1                | 1                | 1                | 1                | 1            | 1            |

| Controller Area Network<br>(Classical CAN) interface | -               | -                                 | -                | -                | 1                | -                | 1            | 1            |

| Controller Area Network (CAN-FD) interface           | 1               | 1                                 | 2                | 2                | 1                | 2                | -            | -            |

| DSP Trace                                            | -               | -                                 | Yes              | Yes              | Yes              | Yes              | Yes          | -            |

| PWM                                                  | Yes             | Yes                               | Yes              | Yes              | Yes              | Yes              | Yes          | -            |

Table 5-1. Device Features Comparison (continued)

|                          |                                                                                     |                   | i abio o | - 1. Device i catale. | o oompanoo.        | i (oonunaoa)       |                    |                   |                   |

|--------------------------|-------------------------------------------------------------------------------------|-------------------|----------|-----------------------|--------------------|--------------------|--------------------|-------------------|-------------------|

| FUNCTIO                  | N                                                                                   | AWRL6432          | AWRL1432 | AWR6843AOP (1)        | AWR6843 (1)        | AWR1843 (1)        | AWR1843AOP (1)     | AWR1642           | AWR1443           |

| DMM Inter                | face                                                                                | -                 | -        | Yes                   | Yes                | Yes                | Yes                | Yes               | -                 |

| Hardware                 | In Loop (HIL/DMM)                                                                   | -                 | -        | Yes                   | Yes                | Yes                | Yes                | Yes               | -                 |

| GPADC                    |                                                                                     | Yes               | Yes      | Yes                   | Yes                | Yes                | Yes                | Yes               | Yes               |

| ADC Raw                  | Data Capture                                                                        | RDIF              | RDIF     | LVDS                  | LVDS               | LVDS               | LVDS               | LVDS              | LVDS              |

| LIN                      |                                                                                     | Yes               | Yes      | -                     | -                  | -                  | -                  | -                 | -                 |

| UART                     |                                                                                     | 2                 | 2        | 2                     | 2                  | 2                  | 2                  | 2                 | 2                 |

| 1V bypass                | mode                                                                                | N/A               | N/A      | Yes                   | Yes                | Yes                | Yes                | Yes               | Yes               |

| JTAG                     |                                                                                     | Yes               | Yes      | Yes                   | Yes                | Yes                | Yes                | Yes               | Yes               |

| Per Chirp of phase shift | configurable TX<br>ter                                                              | BPM Only          | BPM Only | Yes <sup>(5)</sup>    | Yes <sup>(5)</sup> | Yes <sup>(5)</sup> | Yes <sup>(5)</sup> | BPM only          | BPM Only          |

| Product<br>status        | Product Preview<br>(PP), Advance<br>Information (AI),<br>or Production<br>Data (PD) | PD <sup>(6)</sup> | Al       | PD <sup>(6)</sup>     | PD <sup>(6)</sup>  | PD <sup>(6)</sup>  | PD <sup>(6)</sup>  | PD <sup>(6)</sup> | PD <sup>(6)</sup> |

<sup>(1)</sup> Developed for Functional Safety applications, the device supports hardware integrity up to ASIL-B. Refer to the related documentation for more details. Non-Functional Safety Variants are also available for AWRL6432 device.

<sup>(2) 3</sup> Tx Simultaneous operation is supported only with 1V LDO bypass and PA LDO disable mode. In this mode, the 1V supply needs to be fed on the V<sub>OUT</sub> PA pin.

<sup>(3)</sup> As the certification can get secured at different times and post certificate the target will be updated to "compliant" from "compliance targeted" only in related data sheets, please refer to the respective data sheets for most recent compliance status.

<sup>(4)</sup> Device security features including Secure Boot and Customer Programmable Keys are available in select devices for only select part variants as indicated by the Device Type identifier in Section 3. Device Information table.

<sup>(5) 6</sup> bits linear Phase Shifter.

<sup>(6)</sup> PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty.

#### 5.1 Related Products

For information about other devices in this family of products or related products see the links that follow.

mmWave Sensors

TI's mmWave sensors rapidly and accurately sense range, angle and velocity with less power using the smallest footprint mmWave sensor portfolio for automotive applications.

Automotive mmWave Sensors

TI's automotive mmWave sensor portfolio offers high-performance radar front end to ultra-high resolution, small and low-power single-chip radar solutions. TI's scalable sensor portfolio enables design and development of ADAS, in-cabin and near field system solution for every performance, application and sensor configuration ranging from comfort functions to safety functions in all vehicles.

Companion Products for AWRL6432

Review products that are similar to this product.

Reference designs for AWRL6432

TI Designs Reference Design Library is a robust reference design library spanning analog, embedded processor and connectivity. Created by TI experts to help you jump-start your system design, all TI Designs include schematic or block diagrams, BOMs, and design files to speed your time to market. Search and download designs at ti.com/reference-designs.

Vehicle occupant detection reference design

This reference design demonstrates the use of the AWRL6432/AWR6843 60GHz single-chip mmWave sensor with integrated Hardware Accelerator, as a Vehicle Occupant Detection (VOD) and Child Presence Detection (CPD) Sensor enabling the detection of life forms in a vehicle.

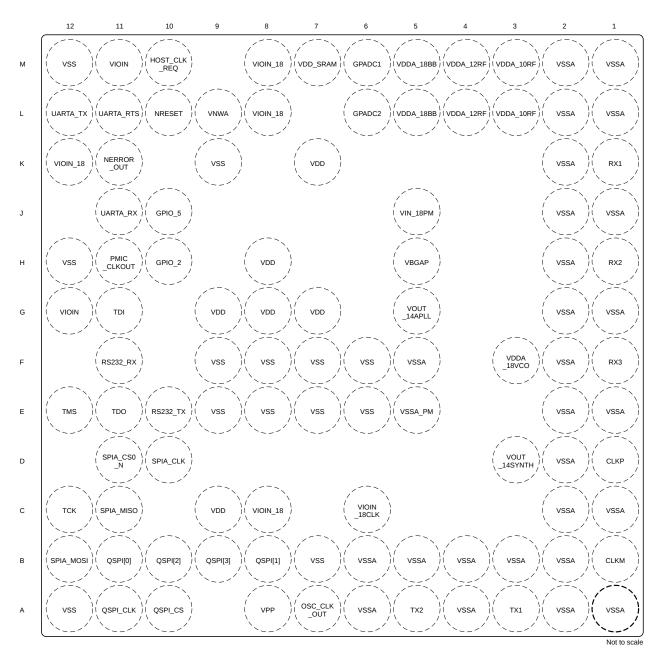

# **6 Terminal Configurations and Functions**

# 6.1 Pin Diagrams

Figure 6-1. FCCSP Pin Diagram (Top View)

## **6.2 Signal Descriptions**

#### Note

All digital IO pins of the device (except NRESET) are non-failsafe; hence, care needs to be taken that they are not driven externally without the VIO supply being present to the device.

Table 6-1. Analog Signal Descriptions

| SIGNAL NAME | DESCRIPTION   | PIN TYPE | BGA PIN |

|-------------|---------------|----------|---------|

| CLKM        | XTAL CLKM pin | Α        | B1      |

**INSTRUMENTS** www.ti.com

## **Table 6-1. Analog Signal Descriptions (continued)**

| SIGNAL NAME  | DESCRIPTION                                                                      | PIN TYPE | BGA PIN |

|--------------|----------------------------------------------------------------------------------|----------|---------|

| CLKP         | XTAL CLKP pin                                                                    | А        | D1      |

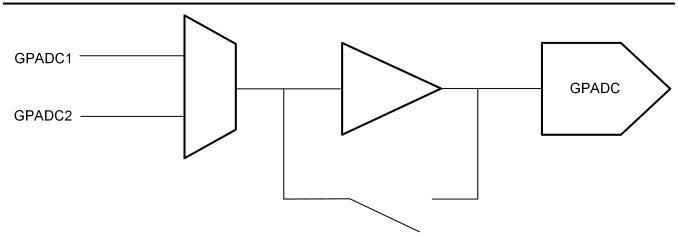

| GPADC1       | GPADC input 1                                                                    | А        | M6      |

| GPADC2       | GPADC input 2                                                                    | А        | L6      |

| NRESET       | NRESET input                                                                     | А        | L10     |

| OSC_CLK_OUT  | Oscillator Clock output                                                          | А        | A7      |

| RX1          | RX channel 1                                                                     | А        | K1      |

| RX2          | RX channel 2                                                                     | А        | H1      |

| RX3          | RX channel 3                                                                     | А        | F1      |

| TX1          | TX channel 1                                                                     | А        | A3      |

| TX2          | TX channel 2                                                                     | Α        | A5      |

| VBGAP        | BandGap reference pin                                                            | А        | H5      |

| VDDA_10RF    | Internal LDO output for RF Supply of 1.0V. External Capacitor needed on this pin | A        | L3, M3  |

| VOUT_14APLL  | 1.4V LDO output. External Capacitor is needed on this pin.                       | A        | G5      |

| VOUT_14SYNTH | 1.4V LDO output. External Capacitor is needed on this pin.                       | A        | D3      |

**Table 6-2. CAN Signal Descriptions**

| SIGNAL NAME | DESCRIPTION       | PIN TYPE | BGA PIN |

|-------------|-------------------|----------|---------|

| CAN_FD_RX   | CAN Receive Data  | I        | J11     |

| CAN_FD_TX   | CAN Transmit Data | 0        | L12     |

Table 6-3, Clock Signal Descriptions

|             | Table 0-3. Clock Signal Descriptions                                                                                                 |          |                           |  |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------------|--|--|--|

| SIGNAL NAME | DESCRIPTION                                                                                                                          | PIN TYPE | BGA PIN                   |  |  |  |

| MCU_CLKOUT  | MCU clock output                                                                                                                     | 0        | K11, M10                  |  |  |  |

| PMIC_CLKOUT | PMIC clock output. This also serves as a Sense On Power Line. Impacts boot mode SOP1.                                                | 0        | H11                       |  |  |  |

| RTC_CLK_IN  | RTC clock input This is used as wakeup source for exiting from deep sleep. For more details, refer to the Technical Reference Manual | I        | B8, E12, H10, K11,<br>L11 |  |  |  |

**Table 6-4. EPWM Signal Descriptions**

| SIGNAL NAME   | DESCRIPTION      | PIN TYPE | BGA PIN            |

|---------------|------------------|----------|--------------------|

| EPWMA         | EPWM Output A    | 0        | C11, D11, G11, L11 |

| EPWMB         | EPWM Output B    | 0        | B12, C12, D10, J10 |

| EPWM_SYNC_IN  | EPWM Sync Input  | I        | E10, E12, J10      |

| EPWM_SYNC_OUT | EPWM Sync output | 0        | E12                |

**Table 6-5. GPIO Signal Descriptions**

| SIGNAL NAME | DESCRIPTION                  | PIN TYPE | BGA PIN |

|-------------|------------------------------|----------|---------|

| GPIO_0      | General Purpose Input/Output | Ю        | B12     |

| GPIO_1      | General Purpose Input/Output | Ю        | C11     |

| GPIO_2      | General Purpose Input/Output | Ю        | H10     |

| GPIO_3      | General Purpose Input/Output | Ю        | J11     |

Copyright © 2024 Texas Instruments Incorporated

Submit Document Feedback

**Table 6-5. GPIO Signal Descriptions (continued)**

| SIGNAL NAME | DESCRIPTION                  | PIN TYPE | BGA PIN |

|-------------|------------------------------|----------|---------|

| GPIO_4      | General Purpose Input/Output | Ю        | K11     |

| GPIO_5      | General Purpose Input/Output | Ю        | J10     |

| GPIO_6      | General Purpose Input/Output | Ю        | L11     |

| GPIO_7      | General Purpose Input/Output | Ю        | M10     |

Table 6-6. I2C Signal Descriptions

| SIGNAL NAME | DESCRIPTION | PIN TYPE | BGA PIN                    |

|-------------|-------------|----------|----------------------------|

| I2C_SCL     | I2C Clock   |          | B10, D10, E10, L12,<br>M10 |

| I2C_SDA     | I2C Data    | Ю        | B9, D11, F11, H10,<br>J11  |

**Table 6-7. JTAG Signal Descriptions**

| SIGNAL NAME | DESCRIPTION                                                                                 | PIN TYPE | BGA PIN |

|-------------|---------------------------------------------------------------------------------------------|----------|---------|

| TCK         | JTAG Test Clock Input                                                                       | I        | C12     |

| TDI         | JTAG Test Data Input                                                                        | I        | G11     |

| TDO         | JTAG Test Data Output. Also serves as a Sense On Power [Reset] Line Impacts boot mode SOP0. | 0        | E11     |

| TMS         | JTAG Test Mode Select Input                                                                 | I        | E12     |

**Table 6-8. LIN Signal Descriptions**

| SIGNAL NAME | DESCRIPTION       | PIN TYPE | BGA PIN                    |

|-------------|-------------------|----------|----------------------------|

| LIN_RX      | LIN Receive Data  | I        | F11, H10, J10, J11         |

| LIN_TX      | LIN Transmit Data | -        | E10, H11, L11, L12,<br>M10 |

Table 6-9. RDIF Signal Descriptions

|              | <u> </u>         |          |         |

|--------------|------------------|----------|---------|

| SIGNAL NAME  | DESCRIPTION      | PIN TYPE | BGA PIN |

| RDIF_CLK     | RDIF Clock       | 0        | L11     |

| RDIF_D0      | RDIF data 0      | 0        | H10     |

| RDIF_D1      | RDIF data 1      | 0        | J11     |

| RDIF_D2      | RDIF data 2      | 0        | L12     |

| RDIF_D3      | RDIF data 3      | 0        | K11     |

| RDIF_FRM_CLK | RDIF Frame Clock | 0        | M10     |

**Table 6-10. Power Supply Signal Descriptions**

| SIGNAL NAME | DESCRIPTION        | PIN TYPE | BGA PIN                   |

|-------------|--------------------|----------|---------------------------|

| VDD         | 1.2V Core supply   | PWR      | C9, G7, G8, G9, H8,<br>K7 |

| VDDA_12RF   | 1.2V RF Supply     | PWR      | L4, M4                    |

| VDDA_18BB   | 1.8V analog supply | PWR      | L5, M5                    |

| VDDA_18VCO  | 1.8V analog supply | PWR      | F3                        |

| VDD_SRAM    | 1.2V SRAM supply   | PWR      | M7                        |

| VIN_18PM    | 1.8V core supply   | PWR      | J5                        |

| VIOIN       | 1.8V analog supply | PWR      | G12, M11                  |

| VIOIN_18    | 1.8V analog supply | PWR      | C8, K12, L8, M8           |

Table 6-10. Power Supply Signal Descriptions (continued)

| SIGNAL NAME | DESCRIPTION                                       | PIN TYPE | BGA PIN                                                                                                               |

|-------------|---------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------|

| VIOIN_18CLK | 1.8V analog supply                                | PWR      | C6                                                                                                                    |

| VNWA        | 1.2V VNWA supply. Always connected to SRAM supply | PWR      | L9                                                                                                                    |

| VPP         | Voltage supply for fuse chain                     | PWR      | A8                                                                                                                    |

| VSS         | Ground                                            | GND      | A12, B7, E6, E7, E8,<br>E9, F6, F7, F8, F9,<br>H12, K9, M12                                                           |

| VSSA        | Ground                                            | GND      | A1, A2, A4, A6, B2,<br>B3, B4, B5, B6, C1,<br>C2, D2, E1, E2, F2,<br>F5, G1, G2, H2, J1,<br>J2, K2, L1, L2, M1,<br>M2 |

| VSSA_PM     | Ground                                            | GND      | E5                                                                                                                    |

## **Table 6-11. QSPI Signal Descriptions**

| SIGNAL NAME | DESCRIPTION      | PIN<br>TYPE | BGA PIN |

|-------------|------------------|-------------|---------|

| QSPI_D0     | QSPI Data bit 0  | Ю           | B11     |

| QSPI_D1     | QSPI Data bit 1  | I           | B8      |

| QSPI_D2     | QSPI Data bit 2  | 1           | B10     |

| QSPI_D3     | QSPI Data bit 3  | 1           | B9      |

| QSPI_SCLK   | QSPI clock       | Ю           | A11     |

| QSPI_CS     | QSPI Chip select | 0           | A10     |

Table 6-12. RS232 Debug Signal Descriptions

| SIGNAL NAME | DESCRIPTION                                         | PIN TYPE | BGA PIN |

|-------------|-----------------------------------------------------|----------|---------|

| RS232_RX    | Debug UART (Operates as Bus Main) - Receive Signal  | 1        | F11     |

| RS232_TX    | Debug UART (Operates as Bus Main) - Transmit Signal | 0        | E10     |

**Table 6-13. SPIA Signal Descriptions**

| SIGNAL NAME | DESCRIPTION        | PIN TYPE | BGA PIN |

|-------------|--------------------|----------|---------|

| SPIA_CLK    | SPIA Clock         | Ю        | D10     |

| SPIA_CS0_N  | SPIA Chip Select 0 | Ю        | D11     |

| SPIA_MISO   | SPIA MISO          | Ю        | C11     |

| SPIA_MOSI   | SPIA MOSI          | Ю        | B12     |

**Table 6-14. SPIB Signal Descriptions**

| SIGNAL NAME | DESCRIPTION        | PIN TYPE | BGA PIN  |

|-------------|--------------------|----------|----------|

| SPIB_CLK    | SPIB Clock         | Ю        | A11, D10 |

| SPIB_CS0_N  | SPIB Chip Select 0 | Ю        | A10, D11 |

| SPIB_MISO   | SPIB MISO          | Ю        | B8, C11  |

| SPIB_MOSI   | SPIB MOSI          | Ю        | B11, B12 |

**Table 6-15. System Signal Descriptions**

| SIGNAL NAME  | DESCRIPTION               | PIN TYPE | BGA PIN |

|--------------|---------------------------|----------|---------|

| HOST_CLK_REQ | Host clock request output | 0        | M10     |

| NERROR_OUT   | NERROR output signal      | 0        | K11     |

## **Table 6-15. System Signal Descriptions (continued)**

| SIGNAL NAME    | DESCRIPTION          | PIN TYPE | BGA PIN                         |

|----------------|----------------------|----------|---------------------------------|

| SYNC_IN        | Sync input           |          | B9, E12, J10, J11,<br>K11       |

| WARM_RESET_OUT | Warm reset output    | 0        | E12, H10                        |

| WU_REQIN       | Wakeup Request input |          | B10, H10, K11, L11,<br>L12, M10 |

## Table 6-16. UARTA Signal Descriptions

| SIGNAL NAME | DESCRIPTION         | PIN TYPE | BGA PIN |  |

|-------------|---------------------|----------|---------|--|

| UARTA_RTS   | UARTA RTS output    | 0        | L11     |  |

| UARTA_RX    | UARTA Receive Data  | I        | J11     |  |

| UARTA_TX    | UARTA Transmit Data | 0        | L12     |  |

## **Table 6-17. UARTB Signal Descriptions**

| SIGNAL NAME | DESCRIPTION         | PIN TYPE | BGA PIN  |

|-------------|---------------------|----------|----------|

| UARTB_RX    | UARTB Receive Data  | I        | F11, J11 |

| UARTB_TX    | UARTB Transmit Data | 0        | E10, L12 |

Table 6-18. Pin Muxing Table

|                       |                          |                            | 1able 6-18                         |                                                | iig iai     | 710             |                                         |                                         |                              |

|-----------------------|--------------------------|----------------------------|------------------------------------|------------------------------------------------|-------------|-----------------|-----------------------------------------|-----------------------------------------|------------------------------|

| BGA<br>BALL<br>NUMBER | BALL NAME <sup>(2)</sup> | SIGNAL NAME <sup>(3)</sup> | PINCNTL<br>REGISTER <sup>(4)</sup> | PIN CNTL<br>REGISTER<br>ADDRESS <sup>(5)</sup> | MODE<br>(6) | <b>TYPE</b> (7) | PULL UP/<br>DOWN<br>TYPE <sup>(8)</sup> | BALL STATE<br>DURING RST <sup>(9)</sup> | BALL STATE<br>AFTER RST (10) |

| H10                   | GPIO_2                   | GPIO_2                     | PADAL_CFG_                         | 0x5A00                                         | 0           | 10              | PU/PD                                   | OFF/OFF/OFF                             | OFF/OFF/OFF                  |

|                       |                          | LIN_RX                     | REG                                | 002C                                           | 1           | I               | -                                       |                                         |                              |

|                       |                          | WARM_RESET_OUT             |                                    |                                                | 2           | 0               | -                                       |                                         |                              |

|                       |                          | I2C_SDA                    | 1                                  |                                                | 3           | 10              | -                                       |                                         |                              |

|                       |                          | SPIA_CS1_N                 |                                    |                                                | 4           | 10              |                                         |                                         |                              |

|                       |                          | WU_REQIN                   |                                    |                                                | 5           | ı               | -                                       |                                         |                              |

|                       |                          | RTC_CLK_IN                 |                                    |                                                | 6           | ı               | -                                       |                                         |                              |

|                       |                          | MDO_D0                     |                                    |                                                | 7           | 0               | -                                       |                                         |                              |

| J10                   | GPIO_5                   | GPIO_5                     | PADAV_CFG_                         | 0x5A00 0054                                    | 0           | 10              | PU/PD                                   | OFF/OFF/OFF                             | OFF/OFF/OFF                  |

|                       | _                        | SYNC_IN                    | REG                                |                                                | 1           | ı               | -                                       |                                         |                              |

|                       |                          | LIN_RX                     |                                    |                                                | 2           | ı               | -                                       |                                         |                              |

|                       |                          | EPWMB                      |                                    |                                                | 3           | 0               | _                                       |                                         |                              |

|                       |                          | EPWM_SYNC_IN               | -                                  |                                                | 4           | ı               | _                                       |                                         |                              |

|                       |                          | MDO_D3                     |                                    |                                                | 5           | 0               | _                                       |                                         |                              |

| M10                   | HOST_CLK_REQ             | HOST_CLK_REQ               | PADAX_CFG_                         | 0x5A00                                         | 0           | 0               | PU/PD                                   | OFF/OFF/OFF                             | OFF/SS/OFF                   |

|                       |                          | GPIO_7                     | REG                                | 005C                                           | 1           | 10              |                                         |                                         |                              |

|                       |                          | MCU_CLKOUT                 | -                                  |                                                | 2           | 0               | _                                       |                                         |                              |

|                       |                          | LIN_TX                     | _                                  |                                                | 3           | 0               | _                                       |                                         |                              |

|                       |                          | WU_REQIN                   | _                                  |                                                | 4           | ı               | _                                       |                                         |                              |

|                       |                          | SPIB_MISO                  | _                                  |                                                | 5           | IO              | _                                       |                                         |                              |

|                       |                          | I2C_SCL                    | _                                  |                                                | 6           | 10              |                                         |                                         |                              |

|                       |                          | MDO_D3                     | _                                  |                                                | 8           | 0               |                                         |                                         |                              |

|                       |                          | _                          | _                                  |                                                | 9           | 0               | -                                       |                                         |                              |

| K11                   | NERROR_OUT               | MDO_FRM_CLK NERROR_OUT     | PADAU_CFG_                         | 0x5A00 0050                                    |             | 0               | PU/PD                                   | OFF/OFF/OFF                             | OFF/OFF/OFF                  |

| KII                   | NEINION_OUT              | GPIO_4                     | REG                                | 0.0000000000000000000000000000000000000        | 1           | 10              |                                         | 011/011/011                             | 011/011/011                  |

|                       |                          | SYNC_IN                    | _                                  |                                                | 2           | ı               | -                                       |                                         |                              |

|                       |                          | _                          | _                                  |                                                | 3           | IO              | _                                       |                                         |                              |

|                       |                          | SPIB_CS0_N                 | -                                  |                                                | 4           | ı               | _                                       |                                         |                              |

|                       |                          | WU_REQIN                   | -                                  |                                                |             | 1               | _                                       |                                         |                              |

|                       |                          | RTC_CLK_IN                 | _                                  |                                                | 5           | · .             | _                                       |                                         |                              |

|                       |                          | MCU_CLKOUT                 | _                                  |                                                | 6           | 0               | -                                       |                                         |                              |

| 1144                  | DMIC OLKOUT              | MDO_D3                     | DADAK OFO                          | 0                                              | 7           | 0               | DLI/DD                                  | 055/055/055                             | 055/055/055                  |

| H11                   | PMIC_CLKOUT              | PMIC_CLKOUT                | PADAK_CFG_<br>REG                  | 0x5A00 0028                                    |             | 0               | PU/PD                                   | OFF/OFF/OFF                             | OFF/OFF/OFF                  |

|                       |                          | LIN_TX                     |                                    |                                                | 1           | 0               | -                                       |                                         |                              |

|                       |                          | SPIA_CS1_N                 |                                    |                                                | 2           | 10              | -                                       |                                         |                              |

| D.1.1                 | O O D I I O              | MDO_FRM_CLK                | 54546.050                          | 0.5100.0000                                    | 3           | 0               | 511/55                                  | 055/055/055                             | 055/055/055                  |

| B11                   | QSPI[0]                  | QSPI[0]                    | PADAC_CFG_<br>REG                  | 0x5A00 0008                                    |             | 10              | PU/PD                                   | OFF/OFF/OFF                             | OFF/OFF/OFF                  |

|                       |                          | SPIB_MOSI                  | _                                  |                                                | 1           | 10              | _                                       |                                         |                              |

|                       | 0.001111                 | MDO_D0                     | D.D                                | 0.5455                                         | 2           | 0               | D11/5-                                  | 055/655/5                               | 0=========                   |

| B8                    | QSPI[1]                  | QSPI[1]                    | PADAD_CFG_<br>REG                  | 0x5A00<br>000C                                 | 0           | 1               | PU/PD                                   | OFF/OFF/OFF                             | OFF/OFF/OFF                  |

|                       |                          | SPIB_MISO                  | ļ <b></b>                          |                                                | 1           | Ю               |                                         |                                         |                              |

|                       |                          | RTC_CLK_IN                 | 1                                  |                                                | 2           | I               |                                         |                                         |                              |

|                       |                          | MDO_D3                     |                                    |                                                | 3           | 0               |                                         |                                         |                              |

| B10                   | QSPI[2]                  | QSPI[2]                    | PADAE_CFG_<br>REG                  | 0x5A00 0010                                    | 0           | I               | PU/PD                                   | OFF/OFF/OFF                             | OFF/OFF/OFF                  |

|                       |                          | I2C_SCL                    | 1,,,,,                             |                                                | 1           | Ю               |                                         |                                         |                              |

|                       |                          | WU_REQIN                   |                                    |                                                | 2           | I               |                                         |                                         |                              |

|                       |                          | MDO_D1                     |                                    |                                                | 3           | 0               |                                         |                                         |                              |

# **Table 6-18. Pin Muxing Table (continued)**

| BGA<br>BALL<br>NUMBER | BALL NAME <sup>(2)</sup> | SIGNAL NAME(3) | PINCNTL<br>REGISTER <sup>(4)</sup> | PIN CNTL<br>REGISTER<br>ADDRESS <sup>(5)</sup> | MODE<br>(6) | <b>TYPE</b> (7) | PULL UP/<br>DOWN<br>TYPE <sup>(8)</sup> | BALL STATE<br>DURING RST <sup>(9)</sup> | BALL STATE<br>AFTER RST (10) |       |       |       |             |            |

|-----------------------|--------------------------|----------------|------------------------------------|------------------------------------------------|-------------|-----------------|-----------------------------------------|-----------------------------------------|------------------------------|-------|-------|-------|-------------|------------|

| B9                    | QSPI[3]                  | QSPI[3]        | PADAF_CFG_                         | 0x5A00 0014                                    | 0           | ı               | PU/PD                                   | OFF/OFF/OFF                             | OFF/OFF/OFF                  |       |       |       |             |            |

|                       |                          | I2C_SDA        | REG                                |                                                | 1           | Ю               |                                         |                                         |                              |       |       |       |             |            |

|                       |                          | SYNC_IN        |                                    |                                                | 2           | I               |                                         |                                         |                              |       |       |       |             |            |

|                       |                          | MDO_D2         |                                    |                                                | 3           | 0               |                                         |                                         |                              |       |       |       |             |            |

| A11                   | QSPI_CLK                 | QSPI_CLK       | PADAA_CFG_                         | 0x5A00 0000                                    | 0           | Ю               | PU/PD                                   | OFF/OFF/OFF                             | OFF/OFF/OFF                  |       |       |       |             |            |

|                       |                          | SPIB_CLK       | REG                                |                                                | 1           | Ю               |                                         |                                         |                              |       |       |       |             |            |

|                       |                          | MDO_CLK        |                                    |                                                | 2           | 0               |                                         |                                         |                              |       |       |       |             |            |

| A10                   | QSPI_CS                  | QSPI_CS        | PADAB_CFG_                         | 0x5A00 0004                                    | 0           | 0               | PU/PD                                   | OFF/OFF/OFF                             | OFF/OFF/OFF                  |       |       |       |             |            |

|                       |                          | SPIB_CS0_N     | REG                                |                                                | 1           | Ю               |                                         |                                         |                              |       |       |       |             |            |

|                       |                          | MDO_FRM_CLK    |                                    |                                                | 2           | 0               |                                         |                                         |                              |       |       |       |             |            |

| F11                   | RS232_RX                 | RS232_RX       | PADAP_CFG_                         | 0x5A00                                         | 0           | ı               | PU/PD                                   | OFF/OFF/UP                              | ON/OFF/UP                    |       |       |       |             |            |

|                       |                          | I2C_SDA        | REG                                | 003C                                           | 1           | Ю               |                                         |                                         |                              |       |       |       |             |            |

|                       |                          | UARTB_RX       |                                    |                                                | 2           | I               |                                         |                                         |                              |       |       |       |             |            |

|                       |                          | LIN_RX         |                                    |                                                | 3           | ı               |                                         |                                         |                              |       |       |       |             |            |

|                       |                          | MDO_D2         |                                    |                                                | 4           | 0               |                                         |                                         |                              |       |       |       |             |            |

|                       |                          | SPIB_MISO      |                                    |                                                | 5           | Ю               |                                         |                                         |                              |       |       |       |             |            |

| E10                   | RS232_TX                 | RS232_TX       | PADAO_CFG_                         | 0x5A00 0038                                    | 0           | 0               | PU/PD                                   | PU/PD                                   | PU/PD                        | PU/PD | PU/PD | PU/PD | OFF/OFF/OFF | OFF/SS/OFF |

|                       |                          | I2C_SCL        | REG                                |                                                | 1           | Ю               |                                         |                                         |                              |       |       |       |             |            |

|                       |                          | UARTB_TX       |                                    |                                                | 2           | 0               |                                         |                                         |                              |       |       |       |             |            |

|                       |                          | LIN_TX         |                                    |                                                | 3           | 0               |                                         |                                         |                              |       |       |       |             |            |

|                       |                          | EPWM_SYNC_IN   |                                    |                                                | 4           | I               |                                         |                                         |                              |       |       |       |             |            |

|                       |                          | MDO_D1         |                                    |                                                | 5           | 0               |                                         |                                         |                              |       |       |       |             |            |

|                       |                          | SPIB_CS1_N     |                                    |                                                | 6           | Ю               |                                         |                                         |                              |       |       |       |             |            |

| D10                   | SPIA_CLK                 | SPIA_CLK       | PADAG_CFG_                         | 0x5A00 0018                                    | 0           | Ю               | PU/PD                                   | OFF/OFF/OFF                             | OFF/OFF/OFF                  |       |       |       |             |            |

|                       |                          | EPWMB          | REG                                |                                                | 1           | 0               | -                                       |                                         |                              |       |       |       |             |            |

|                       |                          | I2C_SCL        |                                    |                                                | 2           | Ю               | -                                       |                                         |                              |       |       |       |             |            |

|                       |                          | SPIB_CLK       |                                    |                                                | 3           | Ю               | -                                       |                                         |                              |       |       |       |             |            |

|                       |                          | MDO_CLK        |                                    |                                                | 4           | 0               | -                                       |                                         |                              |       |       |       |             |            |

| D11                   | SPIA_CS0_N               | SPIA_CS0_N     | PADAH_CFG_                         | 0x5A00                                         | 0           | Ю               | PU/PD                                   | OFF/OFF/OFF                             | OFF/OFF/OFF                  |       |       |       |             |            |

|                       |                          | EPWMA          | REG                                | 001C                                           | 1           | 0               | -                                       |                                         |                              |       |       |       |             |            |

|                       |                          | I2C_SDA        |                                    |                                                | 2           | 10              |                                         |                                         |                              |       |       |       |             |            |

|                       |                          | SPIB_CS0_N     |                                    |                                                | 3           | Ю               | -                                       |                                         |                              |       |       |       |             |            |

|                       |                          | MDO_D3         |                                    |                                                | 4           | 0               | -                                       |                                         |                              |       |       |       |             |            |

| C11                   | SPIA_MISO                | SPIA_MISO      | PADAJ_CFG_                         | 0x5A00 0024                                    | 0           | Ю               | PU/PD                                   | OFF/OFF/OFF                             | OFF/OFF/OFF                  |       |       |       |             |            |

|                       | _                        | GPIO_1         | REG                                |                                                | 1           | Ю               | -                                       |                                         |                              |       |       |       |             |            |

|                       |                          | EPWMA          |                                    |                                                | 2           | 0               | -                                       |                                         |                              |       |       |       |             |            |

|                       |                          | SPIB MISO      |                                    |                                                | 3           | Ю               | _                                       |                                         |                              |       |       |       |             |            |

|                       |                          | MDO_D2         | +                                  |                                                | 4           | 0               | _                                       |                                         |                              |       |       |       |             |            |

| B12                   | SPIA MOSI                | SPIA_MOSI      | PADAI_CFG_                         | 0x5A00 0020                                    | 0           | Ю               | PU/PD                                   | OFF/OFF/OFF                             | OFF/OFF/OFF                  |       |       |       |             |            |

|                       |                          | GPIO_0         | REG                                |                                                | 1           | 10              |                                         |                                         |                              |       |       |       |             |            |

|                       |                          | EPWMB          | +                                  |                                                | 2           | 0               | 1                                       |                                         |                              |       |       |       |             |            |

|                       |                          | SPIB_MOSI      | +                                  |                                                | 3           | 10              | -                                       |                                         |                              |       |       |       |             |            |

|                       |                          | MDO_D1         | +                                  |                                                | 4           | 0               | +                                       |                                         |                              |       |       |       |             |            |

| C12                   | TCK                      | TCK            | PADAT_CFG_                         | 0x5A00                                         | 0           | ı               | PU/PD                                   | OFF/OFF/DOWN                            | ON/OFF/DOWN                  |       |       |       |             |            |

|                       |                          | EPWMB          | REG                                | 004C                                           | 1           | 0               | - 5, 5                                  | 33                                      | 3311750777                   |       |       |       |             |            |

|                       |                          | SPIB_CS1_N     | -                                  |                                                | 2           | 10              | -                                       |                                         |                              |       |       |       |             |            |

|                       |                          | SPIB_MOSI      | -                                  |                                                | 3           | 10              | -                                       |                                         |                              |       |       |       |             |            |

|                       |                          |                |                                    |                                                |             |                 |                                         |                                         |                              |       |       |       |             |            |

#### www.ti.com

## Table 6-18. Pin Muxing Table (continued)

| BC4                   |                          |                | 0-10. PIII IV                      |                                                | - ,50       |                 | ,                                       |                                         |                              |

|-----------------------|--------------------------|----------------|------------------------------------|------------------------------------------------|-------------|-----------------|-----------------------------------------|-----------------------------------------|------------------------------|

| BGA<br>BALL<br>NUMBER | BALL NAME <sup>(2)</sup> | SIGNAL NAME(3) | PINCNTL<br>REGISTER <sup>(4)</sup> | PIN CNTL<br>REGISTER<br>ADDRESS <sup>(5)</sup> | MODE<br>(6) | <b>TYPE</b> (7) | PULL UP/<br>DOWN<br>TYPE <sup>(8)</sup> | BALL STATE<br>DURING RST <sup>(9)</sup> | BALL STATE<br>AFTER RST (10) |

| G11                   | TDI                      | TDI            | PADAR_CFG_                         | 0x5A00 0044                                    | 0           | I               | PU/PD                                   | OFF/OFF/DOWN                            | ON/OFF/DOWN                  |

|                       |                          | EPWMA          | REG                                |                                                | 1           | 0               |                                         |                                         |                              |

|                       |                          | SPIB_CS0_N     | 1                                  |                                                | 2           | 10              |                                         |                                         |                              |

| E11                   | TDO                      | TDO            | PADAS_CFG_                         | 0x5A00 0048                                    | 0           | 0               | PU/PD                                   | OFF/OFF/OFF                             | OFF/SS/OFF                   |

|                       |                          | MDO_FRM_CLK    | REG                                |                                                | 1           | 0               |                                         |                                         |                              |

| E12                   | TMS                      | TMS            | PADAQ_CFG_                         | 0x5A00 0040                                    | 0           | I               | PU/PD                                   | OFF/OFF/UP                              | ON/OFF/UP                    |

|                       |                          | WARM_RESET_OUT | REG                                |                                                | 1           | 0               |                                         |                                         |                              |

|                       |                          | SPIA_CS1_N     | ]                                  |                                                | 2           | Ю               |                                         |                                         |                              |

|                       |                          | SYNC_IN        | ]                                  |                                                | 3           | I               |                                         |                                         |                              |

|                       |                          | SPIB_MISO      | ]                                  |                                                | 4           | Ю               |                                         |                                         |                              |

|                       |                          | SPIB_CLK       | 1                                  |                                                | 5           | 10              |                                         |                                         |                              |

|                       |                          | RTC_CLK_IN     | 1                                  |                                                | 6           | I               |                                         |                                         |                              |

|                       |                          | EPWM_SYNC_IN   | 1                                  |                                                | 7           | I               |                                         |                                         |                              |

|                       |                          | EPWM_SYNC_OUT  | 1                                  |                                                | 8           | 0               |                                         |                                         |                              |

| L11                   | UARTA_RTS                | UART_RTS       | PADAW_CFG_                         | 0x5A00 0058                                    | 0           | 0               | PU/PD                                   | OFF/OFF/OFF                             | OFF/OFF/OFF                  |

|                       |                          | GPIO_6         | REG                                |                                                | 1           | 10              |                                         |                                         |                              |

|                       |                          | LIN_TX         | ]                                  |                                                | 2           | 0               |                                         |                                         |                              |

|                       |                          | SPIB_CLK       | ]                                  |                                                | 3           | Ю               |                                         |                                         |                              |

|                       |                          | WU_REQIN       | ]                                  |                                                | 4           | I               |                                         |                                         |                              |

|                       |                          | EPWMA          | ]                                  |                                                | 5           | 0               |                                         |                                         |                              |

|                       |                          | RTC_CLK_IN     | ]                                  |                                                | 6           | I               |                                         |                                         |                              |

|                       |                          | MDO_CLK        | ]                                  |                                                | 7           | 0               |                                         |                                         |                              |

| J11                   | UARTA_RX                 | UARTA_RX       | PADAM_CFG_                         | 0x5A00 0030                                    | 0           | I               | PU/PD                                   | OFF/OFF/OFF                             | OFF/OFF/OFF                  |

|                       |                          | GPIO_3         | REG                                |                                                | 1           | Ю               |                                         |                                         |                              |

|                       |                          | LIN_RX         | ]                                  |                                                | 2           | I               |                                         |                                         |                              |

|                       |                          | CAN_FD_RX      | ]                                  |                                                | 3           | I               |                                         |                                         |                              |

|                       |                          | SYNC_IN        |                                    |                                                | 4           | I               |                                         |                                         |                              |

|                       |                          | UARTB_RX       |                                    |                                                | 5           | I               |                                         |                                         |                              |

|                       |                          | I2C_SDA        |                                    |                                                | 6           | 10              |                                         |                                         |                              |

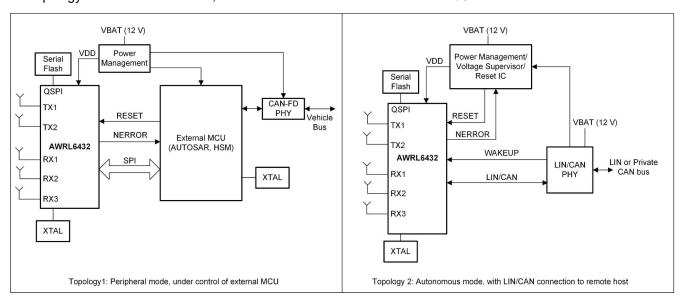

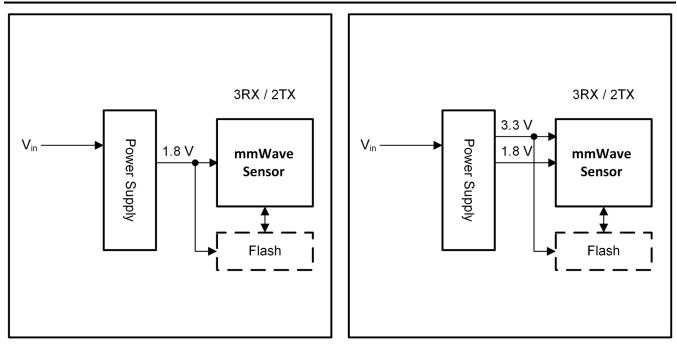

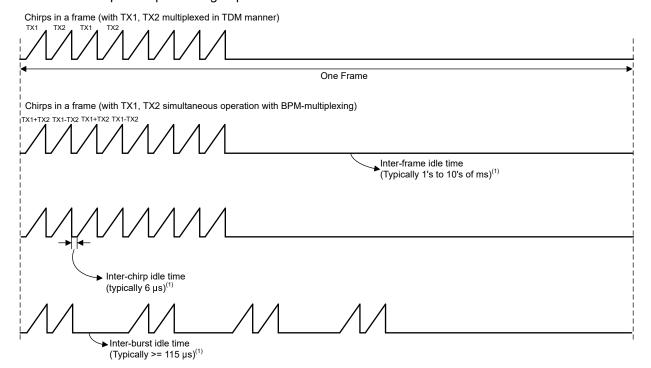

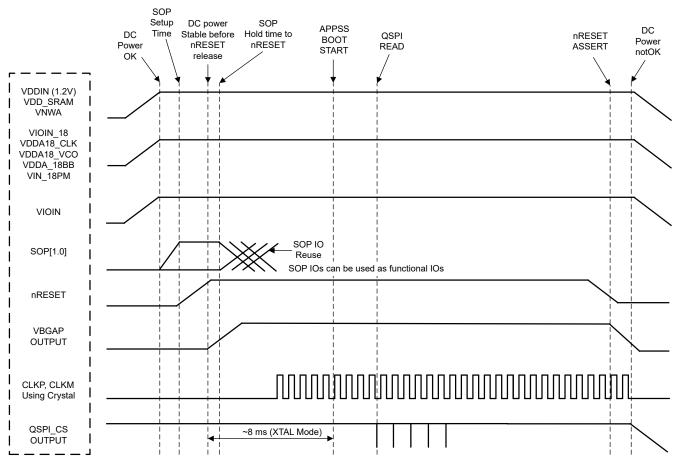

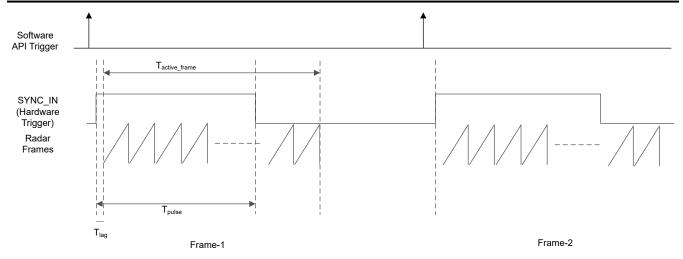

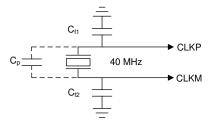

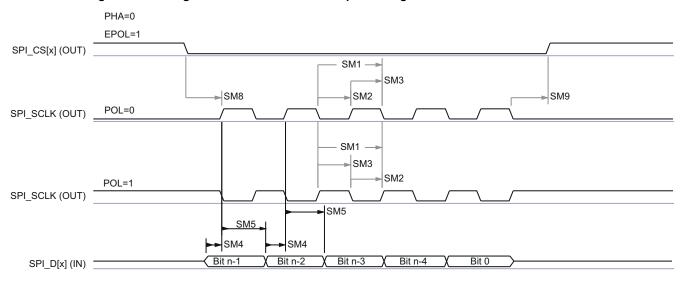

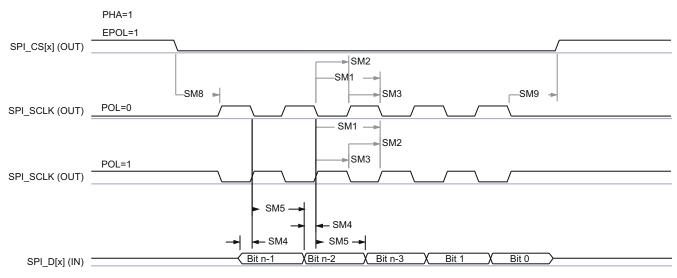

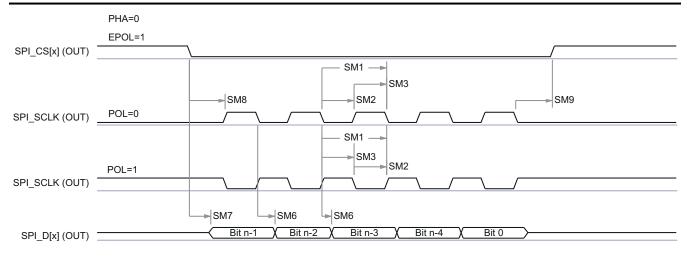

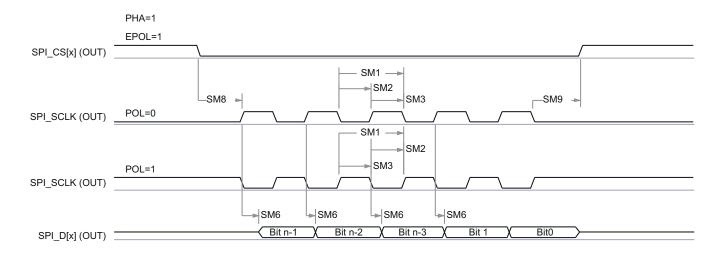

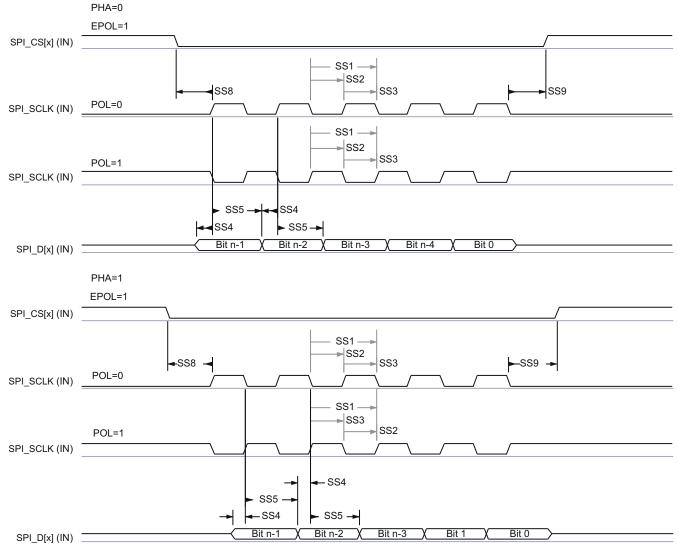

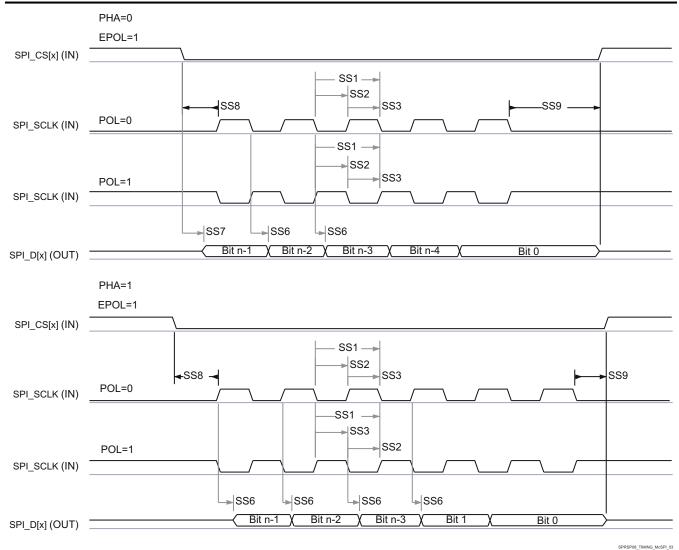

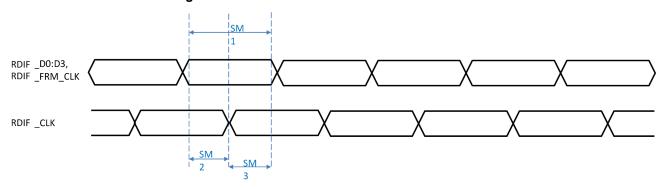

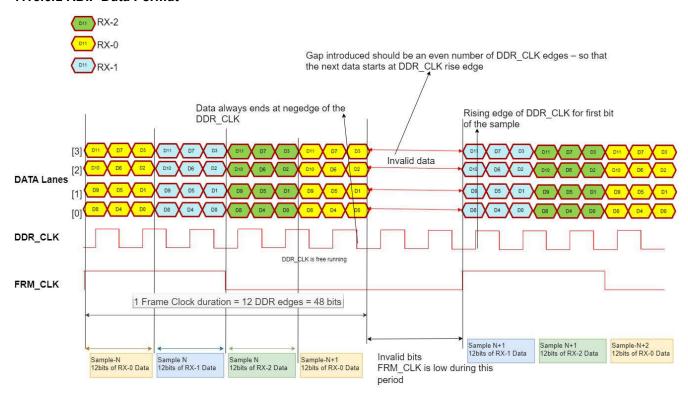

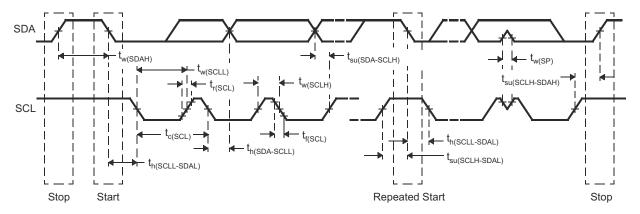

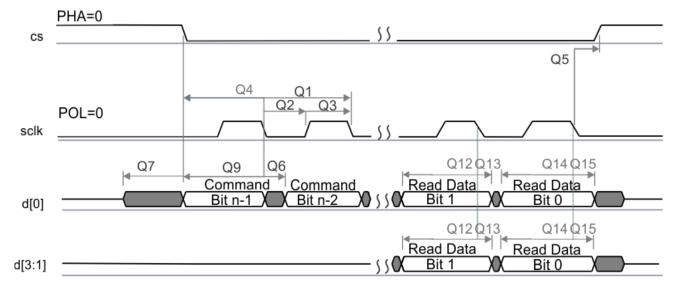

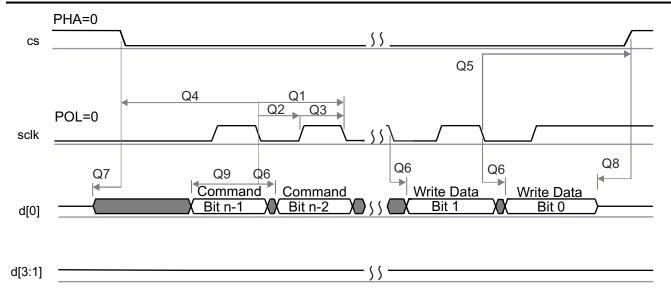

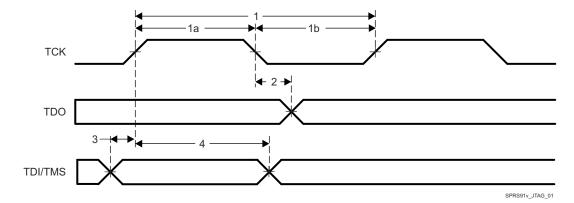

|                       |                          | MDO_D1         |                                    |                                                | 7           | 0               |                                         |                                         |                              |