# SYNCHRONOUS SWITCHMODE, LI-ION AND LI-POLYMER CHARGE-MANAGEMENT IC WITH INTEGRATED POWER FETs ( bqSWITCHER™)

Check for Samples: bq24105-Q1

#### **FEATURES**

- Qualified for Automotive Applications

- Ideal For Highly Efficient Charger Designs For Single-, Two-, or Three-Cell Li-lon and Li-Polymer Battery Packs

- Also for LiFePO<sub>4</sub> Battery (see Using bq24105 to Charge LiFePO4 Battery)

- Integrated Synchronous Fixed-Frequency PWM Controller Operating at 1.1 MHz With 0% to 100% Duty Cycle

- Integrated Power FETs For Up To 2-A Charge Rate

- High-Accuracy Voltage and Current Regulation

- Stand-Alone (Built-In Charge Management and Control) Version

- Status Outputs For LED or Host Processor Interface Indicates Charge-In-Progress, Charge Completion, Fault, and AC-Adapter Present Conditions

- 20-V Maximum Voltage Rating on IN and OUT Pins

- High-Side Battery Current Sensing

- Battery Temperature Monitoring

- Automatic Sleep Mode for Low Power Consumption

- Reverse Leakage Protection Prevents Battery Drainage

- Thermal Shutdown and Protection

- Built-In Battery Detection

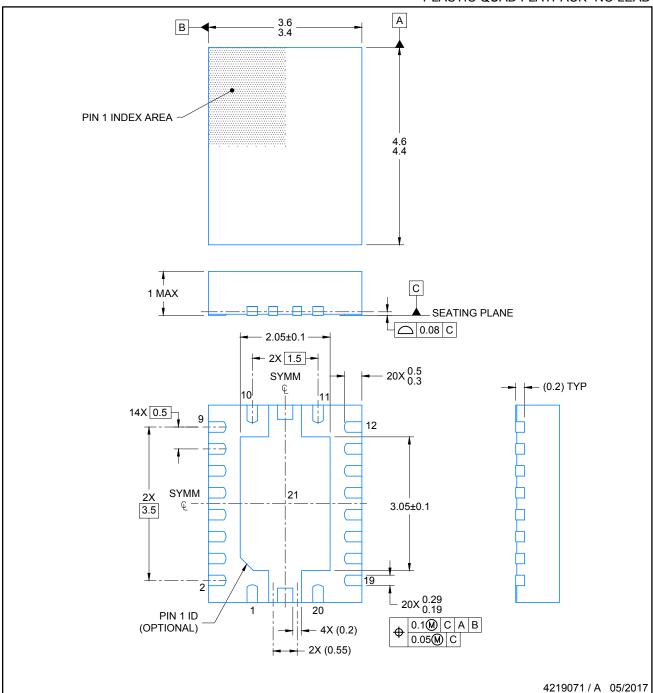

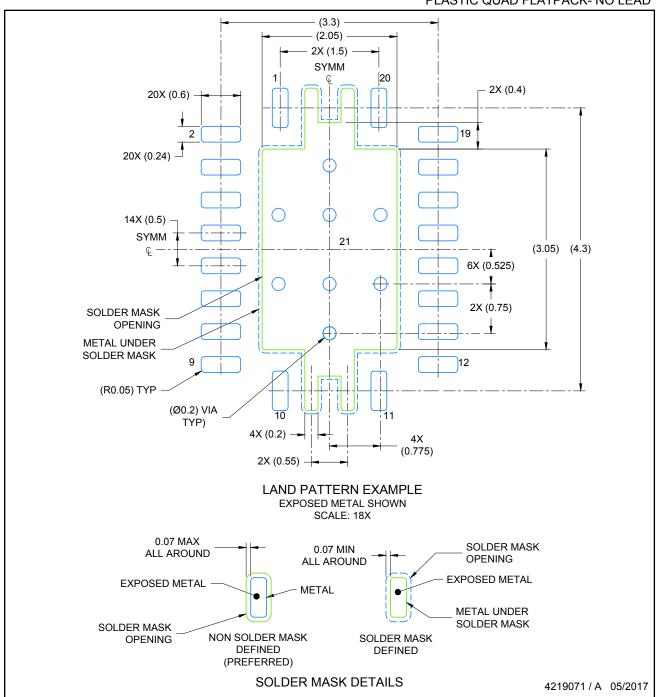

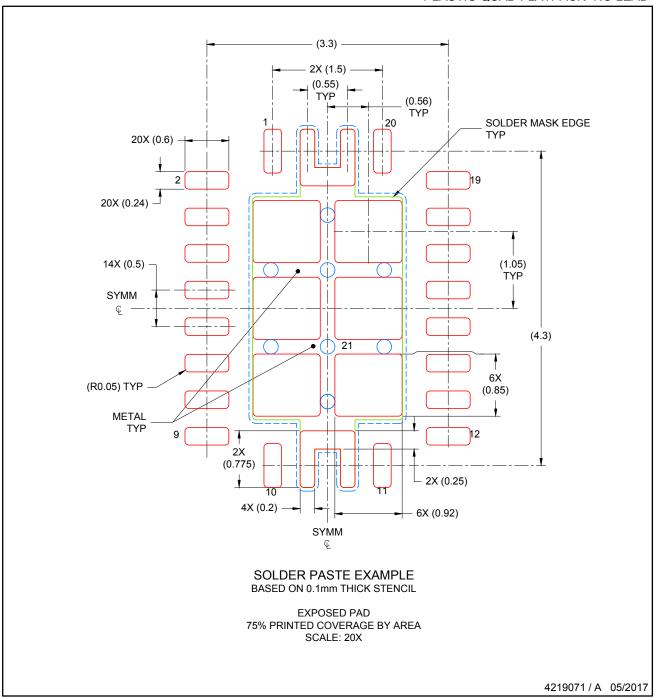

- Available in 20-Pin, 3.5 mm x 4.5 mm, QFN Package

#### DESCRIPTION

The bqSWITCHER™ series are highly integrated Liion and Li-polymer switch-mode charge management devices targeted at a wide range of portable applications. The bqSWITCHER™ series offers integrated synchronous PWM controller and power FETs, high-accuracy current and voltage regulation, charge preconditioning, charge status, and charge termination, in a small, thermally enhanced QFN package.

The bqSWITCHER charges the battery in three phases: conditioning, constant current, and constant voltage. Charge is terminated based on user-selectable minimum current level. A programmable charge timer provides a safety backup for charge termination. The bqSWITCHER automatically restarts the charge cycle if the battery voltage falls below an internal threshold. The bqSWITCHER automatically enters sleep mode when V<sub>CC</sub> supply is removed.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

bqSWITCHER, PowerPAD are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### ORDERING INFORMATION(1)

| T <sub>A</sub> |            | PACKAGE <sup>(2)</sup> | ORDERABLE PA      | RT NUMBER TOP-SIDE MARKING |

|----------------|------------|------------------------|-------------------|----------------------------|

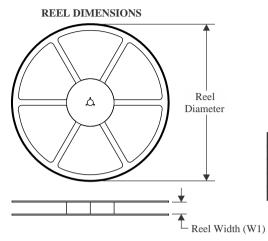

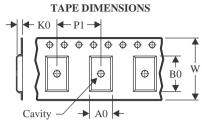

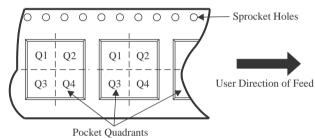

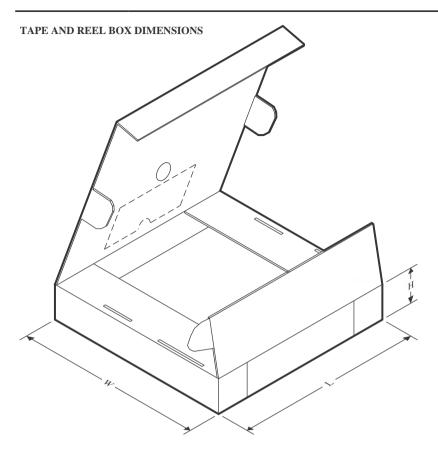

| -40°C to 85°   | C QFN – RI | HL Reel of 30          | DO BQ24105IRHLRQ1 | BQ24105                    |

- (1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

- Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

### ABSOLUTE MAXIMUM RATINGS(1)

over operating free-air temperature range (unless otherwise noted)

|                  | Supply voltage range (with respect to V <sub>SS</sub> )        | IN, VCC                            | 20 V           |

|------------------|----------------------------------------------------------------|------------------------------------|----------------|

|                  |                                                                | STAT1, STAT2, PG, CE, SNS, BAT     | –0.3 V to 20 V |

|                  |                                                                | OUT                                | –0.7 V to 20 V |

|                  | Input voltage range (with respect to V <sub>SS</sub> and PGND) | TS, TTC                            | 7 V            |

|                  |                                                                | VTSB                               | 3.6 V          |

|                  |                                                                | ISET1, ISET2                       | 3.3 V          |

|                  | Voltage difference between SNS and BAT inputs (V <sub>SI</sub> | <sub>NS</sub> – V <sub>BAT</sub> ) | ±1 V           |

|                  | Output sink                                                    | STAT1, STAT2, PG                   | 10 mA          |

|                  | Output current (average)                                       | OUT                                | 2.2 A          |

| $T_A$            | Operating free-air temperature range                           |                                    | -40°C to 85°C  |

| $T_J$            | Junction temperature range                                     | -40°C to 125°C                     |                |

| T <sub>stg</sub> | Storage temperature                                            | –65°C to 150°C                     |                |

|                  | Lead temperature 1,6 mm (1/16 inch) from case for 1            | 0 seconds                          | 300°C          |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### **PACKAGE DISSIPATION RATINGS**

| PACKAGE            | θ <sub>JA</sub> | $\theta_{JC}$ | T <sub>A</sub> < 40°C<br>POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 40°C |

|--------------------|-----------------|---------------|---------------------------------------|------------------------------------------------|

| RHL <sup>(1)</sup> | 46.87°C/W       | 2.5°C/W       | 1.81 W                                | 0.021 W/°C                                     |

<sup>(1)</sup> This data is based on using the JEDEC High-K board, and the exposed die pad is connected to a copper pad on the board. This is connected to the ground plane by a 2x3 via matrix.

## RECOMMENDED OPERATING CONDITIONS

|                                                       | MIN                 | MAX               | UNIT |

|-------------------------------------------------------|---------------------|-------------------|------|

| Supply voltage, V <sub>CC</sub> and IN (Tie together) | 4.35 <sup>(1)</sup> | 16 <sup>(2)</sup> | V    |

| Operating junction temperature range, T <sub>J</sub>  | -40                 | 125               | °C   |

- (1) The IC continues to operate below V<sub>min</sub>, to 3.5 V, but the specifications are not tested and not specified.

- (2) The inherent switching noise voltage spikes should not exceed the absolute maximum rating on either the IN or OUT pins. A tight layout minimizes switching noise.

#### **ELECTRICAL CHARACTERISTICS**

T<sub>J</sub> = 0°C to 125°C and recommended supply voltage range (unless otherwise stated)

| PARAMETER      | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|----------------|-----------------|-----|-----|-----|------|

| Input Currents |                 |     |     |     |      |

# **ELECTRICAL CHARACTERISTICS (continued)**

$T_J = 0$ °C to 125°C and recommended supply voltage range (unless otherwise stated)

|                      | PARAMETER                                                                                       | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | MIN   | TYP  | MAX  | UNIT                 |

|----------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|----------------------|

|                      |                                                                                                 | V <sub>CC</sub> > V <sub>CC(min)</sub> , PWM switching                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       | 10   |      | -                    |

| I <sub>(VCC)</sub>   | V <sub>CC</sub> supply current                                                                  | $V_{CC} > V_{CC(min)}$ , PWM NOT switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |      | 5    | mA                   |

| · ·/                 |                                                                                                 | $V_{CC} > V_{CC(min)}, \overline{CE} = HIGH$                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |      | 315  | μA                   |

|                      |                                                                                                 | $0^{\circ}\text{C} \le \text{T}_{\text{J}} \le 65^{\circ}\text{C}, \text{V}_{\text{I(BAT)}} = 4.2 \text{ V},$<br>$\text{V}_{\text{CC}} < \text{V}_{(\text{SLP})} \text{ or } \text{V}_{\text{CC}} > \text{V}_{(\text{SLP})} \text{ but not in charge}$                                                                                                                                                                                                                                                               |       |      | 3.5  |                      |

| I <sub>(SLP)</sub>   | Battery discharge sleep current, (SNS, BAT, OUT, FB pins)                                       | $0^{\circ}\text{C} \le \text{T}_{\text{J}} \le 65^{\circ}\text{C}, \text{ V}_{\text{I(BAT)}} = 8.4 \text{ V},$<br>$\text{V}_{\text{CC}} < \text{V}_{\text{(SLP)}} \text{ or V}_{\text{CC}} > \text{V}_{\text{(SLP)}} \text{ but not in charge}$                                                                                                                                                                                                                                                                      |       |      | 5.5  | μΑ                   |

|                      |                                                                                                 | $0^{\circ}\text{C} \le \text{T}_{\text{J}} \le 65^{\circ}\text{C}, \ V_{\text{I(BAT)}} = 12.6 \ \text{V}, \ V_{\text{CC}} < V_{\text{(SLP)}} \ \text{or} \ V_{\text{CC}} > V_{\text{(SLP)}} \ \text{but not in charge}$                                                                                                                                                                                                                                                                                              |       |      | 7.7  |                      |

| Voltage Re           | egulation                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |      |      |                      |

| $V_{IBAT}$           | Feedback regulation REF for bq24105 (W/FB)                                                      | I <sub>IBAT</sub> = 25 nA typical into pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       | 2.1  |      | V                    |

|                      | Voltage regulation accuracy                                                                     | T <sub>A</sub> = 25°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -0.5% |      | 0.5% |                      |

|                      | Voltage regulation accuracy                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -1%   |      | 1%   |                      |

| Current Re           | egulation - Fast Charge                                                                         | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |      |      |                      |

| I <sub>OCHARGE</sub> | Output current range of converter                                                               | $V_{LOWV} \le V_{I(BAT)} < V_{OREG},$<br>$V_{(VCC)} - V_{I(BAT)} > V_{(DO-MAX)}$                                                                                                                                                                                                                                                                                                                                                                                                                                     | 150   |      | 2000 | mA                   |

| V <sub>IREG</sub>    | Voltage regulated across R <sub>(SNS)</sub> Accuracy                                            | $100 \text{ mV} \leq V_{IREG} \leq 200 \text{ mV},$ $V_{IREG} = \frac{1V}{RSET1} \times 1000,$ $Programmed \text{ Where}$ $5  k\Omega \leq RSET1 \leq 10  k\Omega, \text{ Select RSET1 to}$ $program V_{IREG},$ $V_{IREG(measured)} = I_{OCHARGE} + R_{SNS}$ $(-10\% \text{ to } 10\% \text{ excludes errors due to RSET1}$ and $R_{(SNS)}$ tolerances)                                                                                                                                                              | -10%  |      | 10%  |                      |

| V <sub>(ISET1)</sub> | Output current set voltage                                                                      | $V_{(LOWV)} \le V_{I(BAT)} \le V_{O(REG)},$<br>$V_{(VCC)} \le V_{I(BAT)} \times V_{(DO-MAX)}$                                                                                                                                                                                                                                                                                                                                                                                                                        |       | 1    |      | V                    |

| K <sub>(ISET1)</sub> | Output current set factor                                                                       | $V_{LOWV} \le V_{I(BAT)} < V_{O(REG)},$<br>$V_{(VCC)} \le V_{I(BAT)} + v_{(DO-MAX)}$                                                                                                                                                                                                                                                                                                                                                                                                                                 |       | 1000 |      | V/A                  |

| Precharge            | and Short-Circuit Current Regulation                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |      |      |                      |

| $V_{LOWV}$           | Precharge to fast-charge transition voltage threshold, BAT, bq24100/03/03A/04/05/08/09 ICs only |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 68    | 71.4 | 75   | %V <sub>O(REG)</sub> |

| t                    | Deglitch time for precharge to fast charge transition,                                          | Rising voltage;<br>t <sub>RISE</sub> , t <sub>FALL</sub> = 100 ns, 2-mV overdrive                                                                                                                                                                                                                                                                                                                                                                                                                                    | 20    | 30   | 40   | ms                   |

| OPRECHG              | Precharge range                                                                                 | V <sub>I(BAT)</sub> < V <sub>LOWV</sub> , t < t <sub>PRECHG</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 15    |      | 200  | mA                   |

| V <sub>(ISET2)</sub> | Precharge set voltage, ISET2                                                                    | V <sub>I(BAT)</sub> < V <sub>LOWV</sub> , t < t <sub>PRECHG</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       | 100  |      | mV                   |

| <(ISET2)             | Precharge current set factor                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       | 1000 |      | V/A                  |

| Vireg-pre            | Voltage regulated across R <sub>SNS</sub> -Accuracy                                             | $100 \text{ mV} \leq \text{V}_{\text{IREG-PRE}} \leq 100 \text{ mV},$ $\text{V}_{\text{IREG-PRE}} = \frac{0.1 \text{V}}{\text{RSET2}} \times 1000,$ $(\text{PGM}) \text{ Where}$ $1.2 \text{ k}\Omega \leq \text{RSET2} \leq 10 \text{ k}\Omega, \text{ Select RSET1}$ to program \text{V}_{\text{IREG-PRE}}, \text{V}_{\text{IREG-PRE}} (\text{Measured}) = \text{I}_{\text{OPRE-CHG}} \times \text{R}_{\text{SNS}} (-20\% \text{ to 20% excludes errors due to RSET1} and \text{R}_{\text{SNS}} \text{tolerances}) | -20%  |      | 20%  |                      |

| Charge Te            | rmination (Current Taper) Detection                                                             | , ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |      |      |                      |

| I <sub>TERM</sub>    | Charge current termination detection range                                                      | $V_{I(BAT)} > V_{RCH}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15    |      | 200  | mA                   |

| $V_{TERM}$           | Charge termination detection set voltage, ISET2                                                 | $V_{I(BAT)} > V_{RCH}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       | 100  |      | mV                   |

| (ISET2)              | Termination current set factor                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       | 1000 |      | V/A                  |

|                      | Charger termination accuracy                                                                    | $V_{I(BAT)} > V_{RCH}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -20%  |      | 20%  |                      |

|                      |                                                                                                 | Both rising and falling,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |      |      |                      |

# **ELECTRICAL CHARACTERISTICS (continued)**

$T_J = 0$  °C to 125 °C and recommended supply voltage range (unless otherwise stated)

|                         | PARAMETER                                   | TEST CONDITIONS                                                                                                                                    | MIN   | TYP   | MAX             | UNIT    |

|-------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-----------------|---------|

| % <sub>LTF</sub>        | Cold temperature threshold, TS, % of bias   | V <sub>LTF</sub> = V <sub>O(VTSB)</sub> × % LTF/100                                                                                                | 72.8% | 73.5% | 74.2%           |         |

| % <sub>HTF</sub>        | Hot temperature threshold, TS, % of bias    | V <sub>HTF</sub> = V <sub>O(VTSB)</sub> × % HTF/100                                                                                                | 33.7% | 34.4% | 35.1%           |         |

| % <sub>TCO</sub>        | Cutoff temperature threshold, TS, % of bias | V <sub>TCO</sub> = V <sub>O(VTSB)</sub> <b>x</b> % TCO/100                                                                                         | 28.7% | 29.3% | 29.9%           |         |

|                         | LTF hysteresis                              |                                                                                                                                                    | 0.5%  | 1%    | 1.5%            |         |

| t <sub>dg-TS</sub>      | Deglitch time for temperature fault, TS     | Both rising and falling,<br>2-mV overdrive t <sub>RISE</sub> , t <sub>FALL</sub> = 100 ns                                                          | 20    | 30    | 40              | ms      |

| V <sub>O(VTSB)</sub>    | TS bias output voltage                      | $ \begin{vmatrix} V_{CC} > V_{IN(min)}, \\ I_{(VTSB)} = 10 \text{ mA } 0.1  \mu\text{F} \leq C_{O(VTSB)} \leq 1  \mu\text{F} $                     |       | 3.15  |                 | V       |

| V <sub>O(VTSB)</sub>    | TS bias voltage regulation accuracy         | $\label{eq:VCC} \begin{split} &V_{CC}>_{IN(min)}, \\ &I_{(VTSB)}=10 \text{ mA } 0.1  \mu\text{F} \leq C_{O(VTSB)} \leq 1  \mu\text{F} \end{split}$ | -10%  |       | 10%             |         |

| Battery Re              | charge Threshold                            |                                                                                                                                                    |       |       |                 |         |

| V <sub>RCH</sub>        | Recharge threshold voltage                  | Below V <sub>OREG</sub>                                                                                                                            | 75    | 100   | 125             | mV/cell |

| t <sub>dg-RCH</sub>     | Deglitch time                               | $V_{I(BAT)}$ < decreasing below threshold,<br>$t_{FALL}$ = 100 ns 10-mV overdrive                                                                  | 20    | 30    | 40              | ms      |

| Stat1, Stat             | 2, and <del>PG</del> Outputs                |                                                                                                                                                    | ·     |       |                 |         |

| V <sub>OL(STATx)</sub>  | Low-level output saturation voltage, STATx  | I <sub>O</sub> = 5 mA                                                                                                                              |       |       | 0.5             | V       |

| $V_{OL(\overline{PG})}$ | Low-level output saturation voltage, PG     | I <sub>O</sub> = 10 mA                                                                                                                             |       |       | 0.1             | V       |

| CE Input                |                                             |                                                                                                                                                    |       |       |                 |         |

| V <sub>IL</sub>         | Low-level input voltage                     | $I_{IL} = 5 \mu A$                                                                                                                                 | 0     |       | 0.4             | V       |

| V <sub>IH</sub>         | High-level input voltage                    | I <sub>IH</sub> = 20 μA                                                                                                                            | 1.3   |       | V <sub>CC</sub> | V       |

| TTC Input               |                                             |                                                                                                                                                    | ·     |       |                 |         |

| t <sub>PRECHG</sub>     | Precharge timer                             |                                                                                                                                                    | 1440  | 1800  | 2160            | s       |

| t <sub>CHARGE</sub>     | Programmable charge timer range             | $t_{(CHG)} = C_{(TTC)} \times K_{(TTC)}$                                                                                                           | 25    |       | 572             | minutes |

|                         | Charge timer accuracy                       | 0.01 μF ≤ C <sub>(TTC)</sub> ≤ 0.18 μF                                                                                                             | -10%  |       | 10%             |         |

| K <sub>TTC</sub>        | Timer multiplier                            |                                                                                                                                                    |       | 2.6   |                 | min/nF  |

| C <sub>TTC</sub>        | Charge time capacitor range                 |                                                                                                                                                    | 0.01  |       | 0.22            | μF      |

| V <sub>TTC_EN</sub>     | TTC enable threshold voltage                | V <sub>(TTC)</sub> rising                                                                                                                          |       | 200   |                 | mV      |

# **ELECTRICAL CHARACTERISTICS (continued)**

|                       | PARAMETER                                                                                       | TEST CONDITIONS                                                                                                     | MIN                                          | TYP  | MAX                                           | UNIT                 |  |

|-----------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------|-----------------------------------------------|----------------------|--|

| Sleep Com             | parator                                                                                         |                                                                                                                     | •                                            |      |                                               |                      |  |

| .,                    | Olean media anto thorobald                                                                      | 2.3 V ≤ V <sub>I(OUT)</sub> ≤ V <sub>OREG,</sub> for 1 or 2 cells                                                   | V <sub>CC</sub> ≤ V <sub>IBAT</sub><br>+5 mV |      | V <sub>CC</sub> ≤ V <sub>IBAT</sub><br>+75 mV | V                    |  |

| V <sub>SLP-ENT</sub>  | Sleep-mode entry threshold                                                                      | $V_{I(OUT)} = 12.6 \text{ V}, R_{IN} = 1 \text{ k}\Omega$<br>bq24105/15 <sup>(1)</sup>                              | V <sub>CC</sub> ≤ V <sub>IBAT</sub><br>-4 mV |      | V <sub>CC</sub> ≤ V <sub>IBAT</sub><br>+73 mV | V                    |  |

| V <sub>SLP-EXIT</sub> | Sleep-mode exit hysteresis,                                                                     | 2.3 V ≤ V <sub>I(OUT)</sub> ≤ V <sub>OREG</sub>                                                                     | 40                                           |      | 160                                           | mV                   |  |

|                       | Deglitab time for along mode                                                                    | V <sub>CC</sub> decreasing below threshold,<br>t <sub>FALL</sub> = 100 ns, 10-mV overdrive,<br>PMOS turns off       |                                              | 5    |                                               | μs                   |  |

| <sup>t</sup> dg-SLP   | Deglitch time for sleep mode                                                                    | $V_{CC}$ decreasing below threshold, $t_{FALL}$ = 100 ns, 10-mV overdrive, STATx pins turn off                      | 20                                           | 30   | 40                                            | ms                   |  |

| UVLO                  |                                                                                                 |                                                                                                                     |                                              |      |                                               |                      |  |

| V <sub>UVLO-ON</sub>  | IC active threshold voltage                                                                     | V <sub>CC</sub> rising                                                                                              | 3.15                                         | 3.30 | 3.50                                          | V                    |  |

|                       | IC active hysteresis                                                                            | V <sub>CC</sub> falling                                                                                             | 120                                          | 150  |                                               | mV                   |  |

| PWM                   |                                                                                                 |                                                                                                                     |                                              |      |                                               |                      |  |

|                       |                                                                                                 | $7 \text{ V} \leq \text{V}_{CC} \leq \text{V}_{CC(max)}$                                                            |                                              |      | 400                                           |                      |  |

|                       | Internal P-channel MOSFET on-resistance                                                         | 4.5 V ≤ V <sub>CC</sub> ≤ 7 V                                                                                       |                                              |      | 500                                           |                      |  |

|                       |                                                                                                 | 7 V ≤ V <sub>CC</sub> ≤ V <sub>CC(max)</sub>                                                                        |                                              |      | 130                                           |                      |  |

|                       | Internal N-channel MOSFET on-resistance                                                         | 4.5 V ≤ V <sub>CC</sub> ≤ 7 V                                                                                       |                                              |      | 150                                           |                      |  |

| f <sub>osc</sub>      | Oscillator frequency                                                                            |                                                                                                                     |                                              | 1.1  |                                               | MHz                  |  |

|                       | Frequency accuracy                                                                              |                                                                                                                     | -9%                                          |      | 9%                                            |                      |  |

| D <sub>MAX</sub>      | Maximum duty cycle                                                                              |                                                                                                                     |                                              |      | 100%                                          |                      |  |

| D <sub>MIN</sub>      | Minimum duty cycle                                                                              |                                                                                                                     | 0%                                           |      |                                               |                      |  |

| t <sub>TOD</sub>      | Switching delay time (turn on)                                                                  |                                                                                                                     |                                              | 20   |                                               | ns                   |  |

| t <sub>syncmin</sub>  | Minimum synchronous FET on time                                                                 |                                                                                                                     |                                              | 60   |                                               | ns                   |  |

| Synonini              | Synchronous FET minimum current-off threshold <sup>(2)</sup>                                    |                                                                                                                     | 50                                           |      | 400                                           | mA                   |  |

| Battery De            | tection                                                                                         |                                                                                                                     |                                              |      | I.                                            |                      |  |

| I <sub>DETECT</sub>   | Battery detection current during time-out fault                                                 | V <sub>I(BAT)</sub> < V <sub>OREG</sub> - V <sub>RCH</sub>                                                          |                                              | 2    |                                               | mA                   |  |

| I <sub>DISCHRG1</sub> | Discharge current                                                                               | V <sub>SHORT</sub> < V <sub>I(BAT)</sub> < V <sub>OREG</sub> - V <sub>RCH</sub>                                     |                                              | 400  |                                               | μA                   |  |

| t <sub>DISCHRG1</sub> | Discharge time                                                                                  | V <sub>SHORT</sub> < V <sub>I(BAT)</sub> < V <sub>OREG</sub> - V <sub>RCH</sub>                                     |                                              | 1    |                                               | S                    |  |

| I <sub>WAKE</sub>     | Wake current                                                                                    | V <sub>SHORT</sub> < V <sub>I(BAT)</sub> < V <sub>OREG</sub> - V <sub>RCH</sub>                                     |                                              | 2    |                                               | mA                   |  |

| t <sub>WAKE</sub>     | Wake time                                                                                       | V <sub>SHORT</sub> < V <sub>I(BAT)</sub> < V <sub>OREG</sub> - V <sub>RCH</sub>                                     |                                              | 0.5  |                                               | S                    |  |

| I <sub>DISCHRG2</sub> | Termination discharge current                                                                   | Begins after termination detected, V <sub>I(BAT)</sub> ≤ V <sub>OREG</sub>                                          |                                              | 400  |                                               | μΑ                   |  |

| t <sub>DISCHRG2</sub> | Termination time                                                                                |                                                                                                                     |                                              | 262  |                                               | ms                   |  |

| Output Ca             | pacitor                                                                                         |                                                                                                                     | 1                                            |      | '                                             |                      |  |

| C <sub>OUT</sub>      | Required output ceramic capacitor range from SNS to PGND, between inductor and $R_{\text{SNS}}$ |                                                                                                                     | 4.7                                          | 10   | 47                                            | μF                   |  |

| C <sub>SNS</sub>      | Required SNS capacitor (ceramic) at SNS pin                                                     |                                                                                                                     |                                              | 0.1  |                                               | μF                   |  |

| Protection            |                                                                                                 |                                                                                                                     |                                              |      |                                               |                      |  |

| V <sub>OVP</sub>      | OVP threshold voltage                                                                           | Threshold over V <sub>OREG</sub> to turn off P-channel MOSFET, STAT1, and STAT2 during charge or termination states | 110                                          | 117  | 121                                           | %V <sub>O(REG)</sub> |  |

| I <sub>LIMIT</sub>    | Cycle-by-cycle current limit                                                                    |                                                                                                                     | 2.6                                          | 3.6  | 4.5                                           | Α                    |  |

| V <sub>SHORT</sub>    | Short-circuit voltage threshold, BAT                                                            | V <sub>I(BAT)</sub> falling                                                                                         | 1.95                                         | 2    | 2.05                                          | V/cell               |  |

| I <sub>SHORT</sub>    | Short-circuit current                                                                           | $V_{I(BAT)} \le V_{SHORT}$                                                                                          | 35                                           |      | 65                                            | mA                   |  |

| T <sub>SHTDWN</sub>   | Thermal trip                                                                                    |                                                                                                                     |                                              | 165  |                                               | °C                   |  |

|                       | Thermal hysteresis                                                                              |                                                                                                                     |                                              | 10   |                                               | °C                   |  |

For bq24105 and bq24115 only.  $R_{\text{IN}}$  is connected between IN and PGND pins and needed to ensure sleep entry. N-channel always turns on for ~60 ns and then turns off if current is too low.

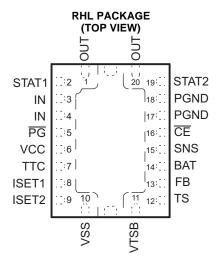

# **TERMINAL FUNCTIONS**

| TERMINAL VO            |       | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|------------------------|-------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                   | NO.   | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| BAT                    | 14    | I   | Battery voltage sense input. Bypass it with a 0.1 μF capacitor to PGND if there are long <i>inductive</i> leads to battery.                                                                                                                                                                                                                                              |  |  |  |

| CE                     | 16    | I   | Charger enable input. This active low input, if set high, suspends charge and places the device in the low-power sleep mode. Do not pull up this input to VTSB.                                                                                                                                                                                                          |  |  |  |

| FB                     | 13    | I   | Output voltage analog feedback adjustment. Connect the output of a resistive voltage divider powered from the battery terminals to this node to adjust the output battery voltage regulation.                                                                                                                                                                            |  |  |  |

| IN                     | 3, 4  | I   | Charger input voltage.                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| ISET1                  | 8     | I/O | Charger current set point 1 (fast charge). Use a resistor to ground to set this value.                                                                                                                                                                                                                                                                                   |  |  |  |

| ISET2                  | 9     | I/O | Charge current set point 2 (precharge and termination), set by a resistor connected to ground.                                                                                                                                                                                                                                                                           |  |  |  |

| OUT                    | 1, 20 | 0   | Charge current output inductor connection. Connect a zener TVS diode between OUT pin and PGND pin to clamp the voltage spike to protect the power MOSFETs during abnormal conditions.                                                                                                                                                                                    |  |  |  |

| PG                     | 5     | 0   | Power-good status output (open drain). The transistor turns on when a valid V <sub>CC</sub> is detected. It is turned off in the sleep mode. PG can be used to drive a LED or communicate with a host processor.                                                                                                                                                         |  |  |  |

| PGND                   | 17,18 |     | Power ground input                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| SNS                    | 15    | I   | Charge current-sense input. Battery current is sensed via the voltage drop developed on this pin by an external sense resistor in series with the battery pack. A 0.1-µF capacitor to PGND is required.                                                                                                                                                                  |  |  |  |

| STAT1                  | 2     | 0   | Charge status 1 (open-drain output). When the transistor turns on indicates charge in process. When it is off and with the condition of STAT2 indicates various charger conditions (see Table 1).                                                                                                                                                                        |  |  |  |

| STAT2                  | 19    | 0   | Charge status 2 (open-drain output). When the transistor turns on indicates charge is done. When it is off and with the condition of STAT1 indicates various charger conditions (see Table 1).                                                                                                                                                                           |  |  |  |

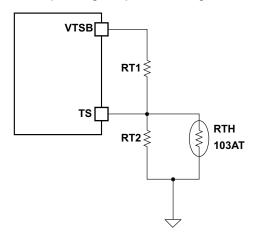

| TS                     | 12    | I   | Temperature sense input. This input monitors its voltage against an internal threshold to determine if charging is allowed. Use an NTC thermistor and a voltage divider powered from VTSB to develop this voltage (see Figure 6).                                                                                                                                        |  |  |  |

| TTC                    | 7     | ı   | Timer and termination control. Connect a capacitor from this node to GND to set the bqSWITCHER timer. When this input is low, the timer and termination detection are disabled.                                                                                                                                                                                          |  |  |  |

| VCC                    | 6     | Į   | Analog device input. A 0.1-μF capacitor to VSS is required.                                                                                                                                                                                                                                                                                                              |  |  |  |

| VSS                    | 10    |     | Analog ground input                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| VTSB                   | 11    | 0   | TS internal bias regulator voltage. Connect capacitor (with a value between a 0.1-μF and 1-μF) between this output and VSS.                                                                                                                                                                                                                                              |  |  |  |

| Exposed<br>Thermal Pad | Pad   |     | There is an internal electrical connection between the exposed thermal pad and VSS. The exposed thermal pad must be connected to the same potential as the VSS pin on the printed circuit board. The power pad can be used as a $star$ ground connection between $V_{SS}$ and PGND. A common ground plane may be used. VSS pin must be connected to ground at all times. |  |  |  |

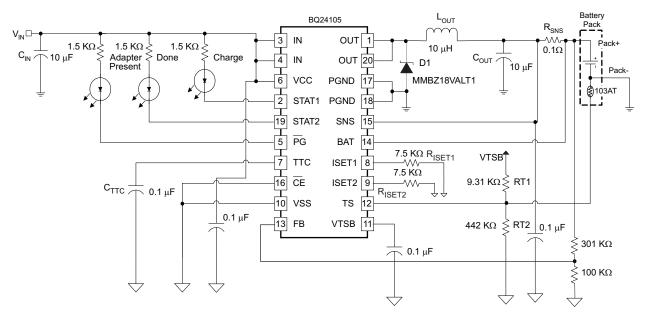

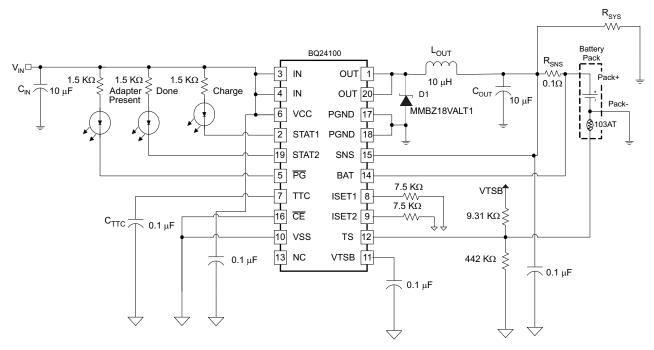

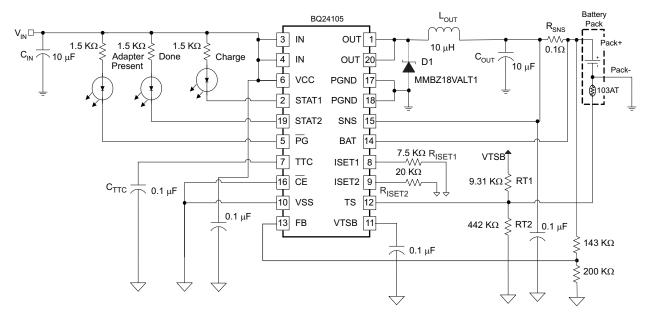

# TYPICAL APPLICATION CIRCUIT

Figure 1. Stand-Alone 2-Cell Application

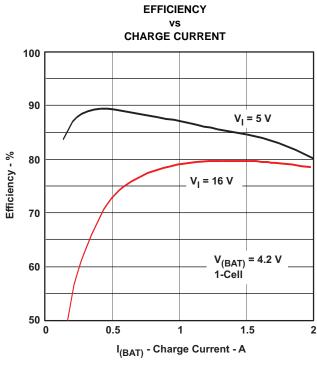

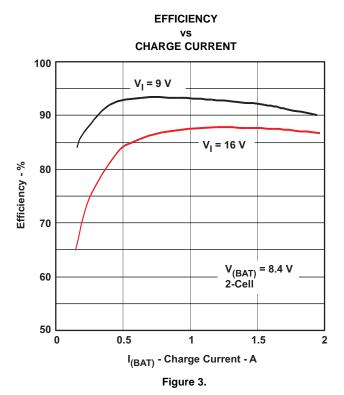

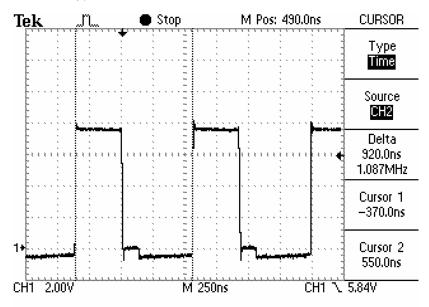

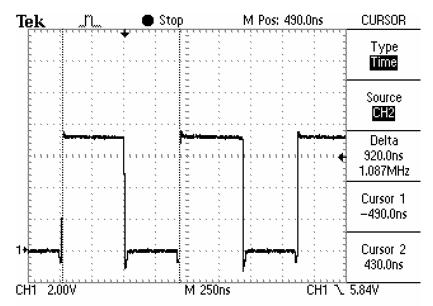

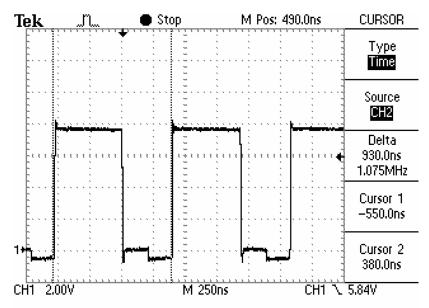

# **TYPICAL OPERATING PERFORMANCE**

Figure 2.

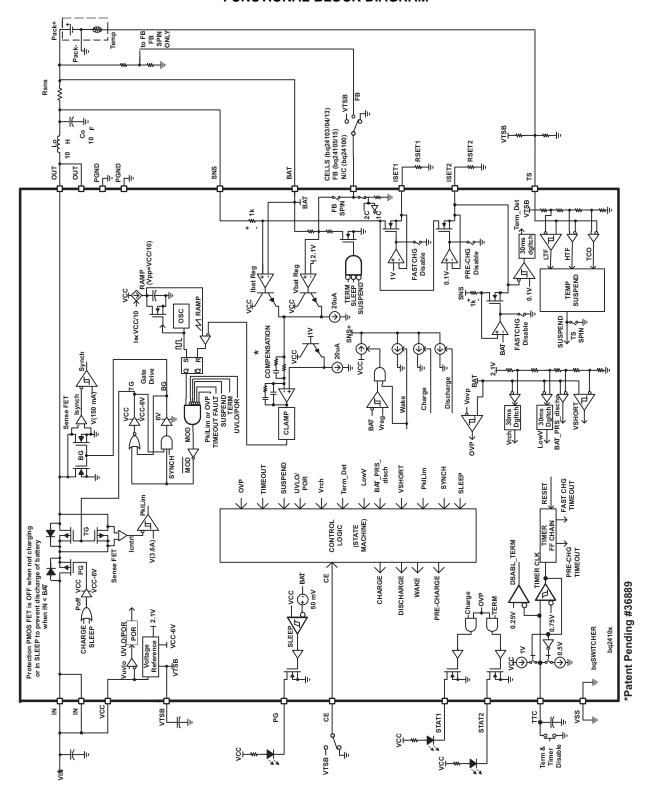

### **FUNCTIONAL BLOCK DIAGRAM**

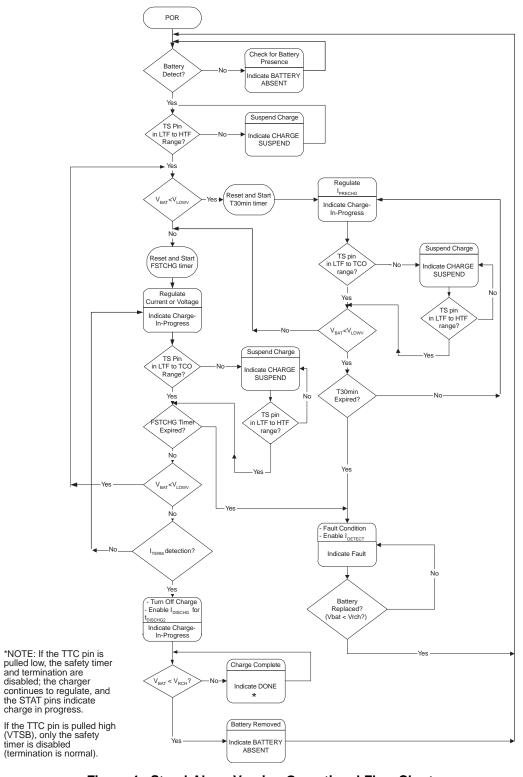

#### **OPERATIONAL FLOW CHART**

Figure 4. Stand-Alone Version Operational Flow Chart

#### **DETAILED DESCRIPTION**

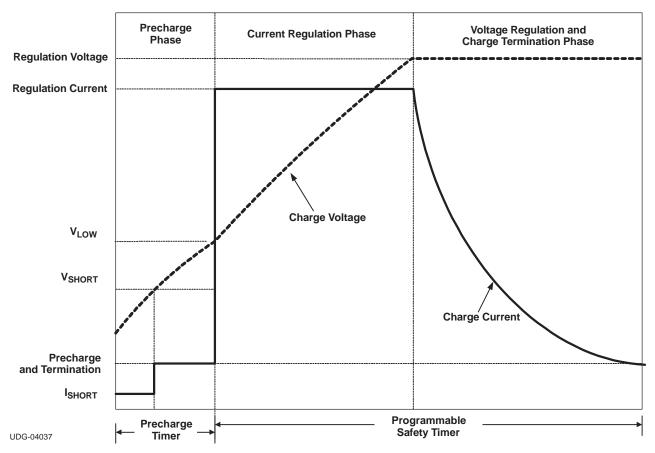

The bqSWITCHER™ supports a precision Li-ion or Li-polymer charging system for one-, two-, or three-cell applications. See Figure 4 for a typical charge profile.

Figure 5. Typical Charging Profile

#### **PWM Controller**

The bq24105 provides an integrated fixed 1MHz frequency voltage-mode controller with Feed-Forward function to regulate charge current or voltage. This type of controller is used to help improve line transient response, thereby simplifying the compensation network used for both continuous and discontinuous current conduction operation. The voltage and current loops are internally compensated using a Type-III compensation scheme that provides enough phase boost for stable operation, allowing the use of small ceramic capacitors with very low ESR. There is a 0.5-V offset on the bottom of the PWM ramp to allow the device to operate between 0% to 100% duty cycle.

The internal PWM gate drive can directly control the internal PMOS and NMOS power MOSFETs. The high-side gate voltage swings from  $V_{CC}$  (when off), to  $V_{CC}$  – 6 (when on and  $V_{CC}$  is greater than 6 V) to help reduce the conduction losses of the converter by enhancing the gate an extra volt beyond the standard 5V. The low-side gate voltage swings from 6 V, to turn on the NMOS, down to PGND to turn it off. The bq24105 has two back to back common-drain P-MOSFETs on the high side. An input P-MOSFET prevents battery discharge when IN is lower than BAT. The second P-MOSFET behaves as the switching control FET, eliminating the need of a bootstrap capacitor.

Cycle-by-cycle current limit is sensed through the internal high-side sense FET. The threshold is set to a nominal 3.6A peak current. The low-side FET also has a current limit that decides if the PWM Controller will operate in synchronous or non-synchronous mode. This threshold is set to 100mA and it turns off the low-side NMOS before the current reverses, preventing the battery from discharging. Synchronous operation is used when the current of the low-side FET is greater than 100mA to minimize power losses.

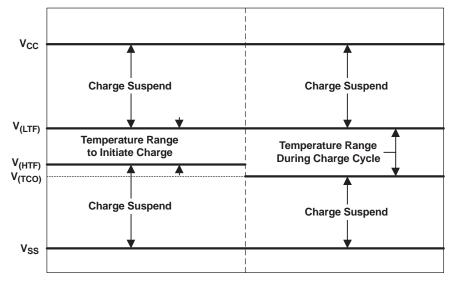

#### **Temperature Qualification**

The bqSWITCHER continuously monitors battery temperature by measuring the voltage between the TS pin and VSS pin. A negative temperature coefficient thermistor (NTC) and an external voltage divider typically develop this voltage. The bqSWITCHER compares this voltage against its internal thresholds to determine if charging is allowed. To initiate a charge cycle, the battery temperature must be within the  $V_{(LTF)}$ -to- $V_{(HTF)}$  thresholds. If battery temperature is outside of this range, the bqSWITCHER suspends charge and waits until the battery temperature must be within the  $V_{(LTF)}$ -to- $V_{(TCO)}$  thresholds. If battery temperature is outside of this range, the bqSWITCHER suspends charge and waits until the battery temperature is within the  $V_{(LTF)}$ -to- $V_{(HTF)}$  range. The bqSWITCHER suspends charge by turning off the PWM and holding the timer value (i.e., timers are not reset during a suspend condition). Note that the bias for the external resistor divider is provided from the VTSB output. Applying a constant voltage between the  $V_{(LTF)}$ -to- $V_{(HTF)}$  thresholds to the TS pin disables the temperature-sensing feature.

$$RT2 = \frac{V_{O(VTSB)} \times RTH_{COLD} \times RTH_{HOT} \times \left[\frac{1}{V_{LTF}} - \frac{1}{V_{HTF}}\right]}{RTH_{HOT} \times \left(\frac{V_{O(VTSB)}}{V_{HTF}} - 1\right) - RTH_{COLD} \times \left(\frac{V_{O(VTSB)}}{V_{LTF}} - 1\right)}$$

RT1 =

$$\frac{\frac{V_{O(VTSB)}}{V_{LTF}} - 1}{\frac{1}{RT2} + \frac{1}{RTH_{COLD}}}$$

Where:

$$V_{LTF} = V_{O(VTSB)} \times \%_{LTF+100} / 100$$

$$V_{HTF} = V_{O(VTSB)} \times \%_{HTF+100} / 100$$

(1)

Figure 6. TS Pin Thresholds

# **Battery Preconditioning (Precharge)**

On power up, if the battery voltage is below the  $V_{LOWV}$  threshold, the bqSWITCHER applies a precharge current,  $I_{PRECHG}$ , to the battery. This feature revives deeply discharged cells. The bqSWITCHER activates a safety timer,  $t_{PRECHG}$ , during the conditioning phase. If the  $V_{LOWV}$  threshold is not reached within the timer period, the bqSWITCHER turns off the charger and enunciates FAULT on the STATx pins. In the case of a FAULT condition, the bqSWITCHER reduces the current to  $I_{DETECT}$ .  $I_{DETECT}$  is used to detect a battery replacement condition. Fault condition is cleared by POR or battery replacement.

The magnitude of the precharge current,  $I_{O(PRECHG)}$ , is determined by the value of programming resistor,  $R_{(ISET2)}$ , connected to the ISET2 pin.

$$I_{O(PRECHG)} = \frac{K_{(ISET2)} \times V_{(ISET2)}}{\left(R_{(ISET2)} \times R_{(SNS)}\right)}$$

(2)

where

R<sub>SNS</sub> is the external current-sense resistor

$V_{(ISET2)}$  is the output voltage of the ISET2 pin

K<sub>(ISET2)</sub> is the V/A gain factor

$V_{(ISET2)}$  and  $K_{(ISET2)}$  are specified in the Electrical Characteristics table.

## **Battery Charge Current**

The battery charge current,  $I_{O(CHARGE)}$ , is established by setting the external sense resistor,  $R_{(SNS)}$ , and the resistor,  $R_{(ISET1)}$ , connected to the ISET1 pin.

In order to set the current, first choose  $R_{(SNS)}$  based on the regulation threshold  $V_{IREG}$  across this resistor. The best accuracy is achieved when the  $V_{IREG}$  is between 100 mV and 200 mV.

$$R_{(SNS)} = \frac{V_{IREG}}{I_{OCHARGE}}$$

(3)

If the results is not a standard sense resistor value, choose the next larger value. Using the selected standard value, solve for  $V_{IREG}$ . Once the sense resistor is selected, the ISET1 resistor can be calculated using the following equation:

$$R_{ISET1} = \frac{K_{ISET1} \times V_{ISET1}}{R_{SNS} \times I_{CHARGE}}$$

(4)

# **Battery Voltage Regulation**

The voltage regulation feedback occurs through the BAT pin. This input is tied directly to the positive side of the battery pack. The bqSWITCHER monitors the battery-pack voltage between the BAT and VSS pins.

Output regulation voltage is specified as:

$$VOREG = \frac{(R1 + R2)}{R2} \times VIBAT$$

(5)

where R1 and R2 are resistor divider from BAT to FB and FB to VSS, respectively.

Recharge threshold voltage is specified as:

$$V_{RCH} = \frac{(R1 + R2)}{R2 \times 50 \text{ mV}}$$

(6)

# **Charge Termination and Recharge**

The bqSWITCHER monitors the charging current during the voltage regulation phase. Once the termination threshold,  $I_{TERM}$ , is detected, the bqSWITCHER terminates charge. The termination current level is selected by the value of programming resistor,  $R_{(ISET2)}$ , connected to the ISET2 pin.

$$I_{TERM} = \frac{K_{(ISET2)} \times V_{TERM}}{\left(R_{(ISET2)} \times R_{(SNS)}\right)}$$

(7)

where

R<sub>(SNS)</sub> is the external current-sense resistor

V<sub>TERM</sub> is the output of the ISET2 pin

K<sub>(ISET2)</sub> is the A/V gain factor

V<sub>TERM</sub> and K<sub>(ISET2)</sub> are specified in the Electrical Characteristics table

As a safety backup, the bqSWITCHER also provides a programmable charge timer. The charge time is programmed by the value of a capacitor connected between the TTC pin and GND by the following formula:

$$t_{CHARGE} = C_{(TTC)} \times K_{(TTC)}$$

(8)

where

C<sub>(TTC)</sub> is the capacitor connected to the TTC pin

K<sub>(TTC)</sub> is the multiplier

A new charge cycle is initiated when one of the following conditions is detected:

- The battery voltage falls below the V<sub>RCH</sub> threshold.

- Power-on reset (POR), if battery voltage is below the V<sub>RCH</sub> threshold

- CE toggle

- · TTC pin, described as follows.

In order to disable the charge termination and safety timer, the user can pull the TTC input below the  $V_{TTC\_EN}$  threshold. Going above this threshold enables the termination and safety timer features and also resets the timer. Tying TTC high disables the safety timer only.

#### Sleep Mode

The bqSWITCHER enters the low-power sleep mode if the VCC pin is removed from the circuit. This feature prevents draining the battery during the absence of VCC.

# **Charge Status Outputs**

The open-drain STAT1 and STAT2 outputs indicate various charger operations as shown in Table 1. These status pins can be used to drive LEDs or communicate to the host processor. Note that OFF indicates that the open-drain transistor is turned off.

**Table 1. Status Pins Summary**

| Charge State                                                         | STAT1 | STAT2 |

|----------------------------------------------------------------------|-------|-------|

| Charge-in-progress                                                   | ON    | OFF   |

| Charge complete                                                      | OFF   | ON    |

| Charge suspend, timer fault, overvoltage, sleep mode, battery absent | OFF   | OFF   |

### **Table 2. Status Pins Summary**

| Charge State                                                    | STAT1           | STAT2 |

|-----------------------------------------------------------------|-----------------|-------|

| Battery absent                                                  | OFF             | OFF   |

| Charge-in-progress                                              | ON              | OFF   |

| Charge complete                                                 | OFF             | ON    |

| Battery over discharge, V <sub>I(BAT)</sub> < V <sub>(SC)</sub> | ON/OFF (0.5 Hz) | OFF   |

| Charge suspend (due to TS pin and internal thermal protection)  | ON/OFF (0.5 Hz) | OFF   |

| Precharge timer fault                                           | ON/OFF (0.5 Hz) | OFF   |

| Fast charge timer fault                                         | ON/OFF (0.5 Hz) | OFF   |

| Sleep mode                                                      | OFF             | OFF   |

# **PG** Output

The open-drain  $\overline{PG}$  (power good) indicates when the AC-to-DC adapter (i.e.,  $V_{CC}$ ) is present. The output turns on when sleep-mode exit threshold,  $V_{SLP-EXIT}$ , is detected. This output is turned off in the sleep mode. The  $\overline{PG}$  pin can be used to drive an LED or communicate to the host processor.

# **CE** Input (Charge Enable)

The  $\overline{\text{CE}}$  digital input is used to disable or enable the charge process. A low-level signal on this pin enables the charge and a high-level  $V_{CC}$  signal disables the charge. A high-to-low transition on this pin also resets all timers and fault conditions. Note that the  $\overline{\text{CE}}$  pin cannot be pulled up to VTSB voltage. This may create power-up issues.

## **Timer Fault Recovery**

As shown in Figure 6, bqSWITCHER provides a recovery method to deal with timer fault conditions. The following summarizes this method.

**Condition 1** V<sub>I(BAT)</sub> above recharge threshold (V<sub>OREG</sub> - V<sub>RCH</sub>) and timeout fault occurs.

Recovery method: bqSWITCHER waits for the battery voltage to fall below the recharge threshold. This could happen as a result of a load on the battery, self-discharge or battery removal. Once the battery falls below the recharge threshold, the bqSWITCHER clears the fault and enters the battery absent detection routine. A POR or CE toggle also clears the fault.

Condition 2 Charge voltage below recharge threshold (V<sub>OREG</sub> – V<sub>RCH</sub>) and timeout fault occurs

Recovery method: Under this scenario, the bqSWITCHER applies the I<sub>DETECT</sub> current. This small current is used to detect a battery removal condition and remains on as long as the battery voltage stays below the recharge threshold. If the battery voltage goes above the recharge threshold, then the bqSWITCHER disables the I<sub>DETECT</sub> current and executes the recovery method described in Condition 1. Once the battery falls below the recharge threshold, the bqSWITCHER clears the fault and enters the battery absent detection routine. A POR or CE toggle also clears the fault.

## **Output Overvoltage Protection**

The bqSWITCHER provides a built-in overvoltage protection to protect the device and other components against damages if the battery voltage gets too high, as when the battery is suddenly removed. When an overvoltage condition is detected, this feature turns off the PWM and STATx pins. The fault is cleared once  $V_{IBAT}$  drops to the recharge threshold ( $V_{OREG} - V_{RCH}$ ).

#### Inductor, Capacitor, and Sense Resistor Selection Guidelines

The bqSWITCHER provides internal loop compensation. With this scheme, best stability occurs when LC resonant frequency,  $f_0$  is approximately 16 kHz (8 kHz to 32 kHz). Equation 9 can be used to calculate the value of the output inductor and capacitor. Table 3 provides a summary of typical component values for various charge rates.

$$f_0 = \frac{1}{2\pi \times \sqrt{L_{\text{OUT}} \times C_{\text{OUT}}}} \tag{9}$$

**Table 3. Output Components Summary**

| CHARGE CURRENT                     | 0.5 A  | 1 A   | 2 A                          |

|------------------------------------|--------|-------|------------------------------|

| Output inductor, L <sub>OUT</sub>  | 22 µH  | 10 µH | 4.7 μH                       |

| Output capacitor, C <sub>OUT</sub> | 4.7 µF | 10 μF | 22 μF (or 2 × 10 μF) ceramic |

| Sense resistor, R <sub>(SNS)</sub> | 0.2 Ω  | 0.1 Ω | 0.05 Ω                       |

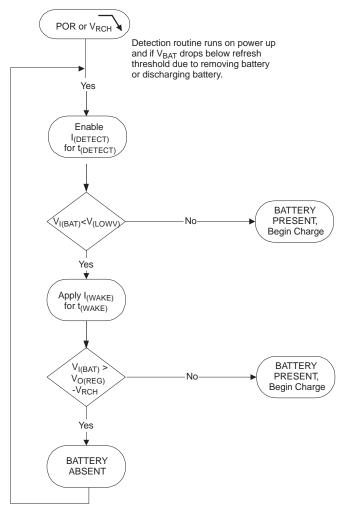

### **Battery Detection**

For applications with removable battery packs, bqSWITCHER provides a battery absent detection scheme to reliably detect insertion and/or removal of battery packs.

Figure 7. Battery Absent Detection

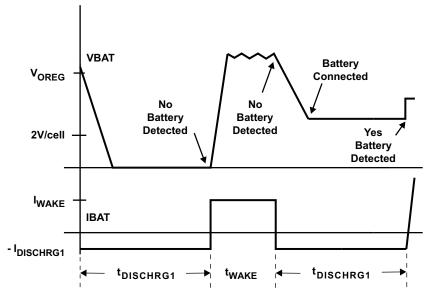

The voltage at the BAT pin is held above the battery recharge threshold,  $V_{OREG} - V_{RCH}$ , by the charged battery following fast charging. When the voltage at the BAT pin falls to the recharge threshold, either by a load on the battery or due to battery removal, the bqSWITCHER begins a battery absent detection test. This test involves enabling a detection current,  $I_{DISCHARGE1}$ , for a period of  $t_{DISCHARGE1}$  and checking to see if the battery voltage is below the short circuit threshold,  $V_{SHORT}$ . Following this, the wake current,  $I_{WAKE}$  is applied for a period of  $t_{WAKE}$  and the battery voltage is checked again to ensure that it is above the recharge threshold. The purpose of this current is to attempt to *close* an open battery pack protector, if one is connected to the bqSWITCHER.

Passing both of the discharge and charge tests indicates a battery absent fault at the STAT pins. Failure of either test starts a new charge cycle. For the absent battery condition, typically the voltage on the BAT pin rises and falls between 0V and  $V_{OVP}$ thresholds indefinitely.

Figure 8. Battery Detect Timing Diagram

## **Battery Detection Example**

In order to detect a *no battery* condition during the discharge and wake tests, the maximum output capacitance should not exceed the following:

a. Discharge (

$$I_{DISCHRG1}$$

= 400  $\mu$ A,  $t_{DISCHRG1}$  = 1s,  $V_{SHORT}$  = 2V)

$$C_{MAX\_DIS} = \frac{I_{DISCHRG1} \times t_{DISCHRG1}}{V_{OREG} - V_{SHORT}}$$

$$C_{MAX\_DIS} = \frac{400 \ \mu A \times 1s}{4.2 \ V - 2 \ V}$$

$$C_{MAX\_DIS} = 182 \ \mu F$$

(10)

b. Wake (

$$I_{WAKE}$$

= 2 mA,  $t_{WAKE}$  = 0.5 s,  $V_{OREG} - V_{RCH}$  = 4.1V)

$$C_{MAX\_WAKE} = \frac{I_{WAKE} \times t_{WAKE}}{\left(V_{OREG} - V_{RCH}\right) - 0 \text{ V}}$$

$$C_{MAX\_WAKE} = \frac{2 \text{ mA} \times 0.5 \text{s}}{(4.2 \text{ V} - 0.1 \text{ V}) - 0 \text{V}}$$

$$C_{MAX\_WAKE} = 244 \,\mu\text{F}$$

battery detection scheme is 100 µF which will allow for process and temperature variations.

Based on these calculations the recommended maximum output capacitance to ensure proper operation of the

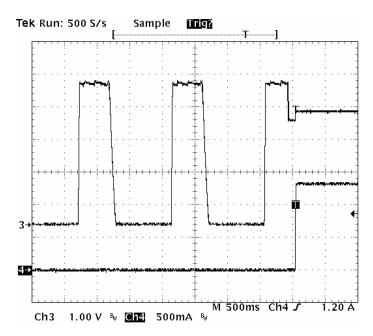

Figure 9 shows the battery detection scheme when a battery is inserted. Channel 3 is the output signal and Channel 4 is the output current. The output signal switches between  $V_{OREG}$  and GND until a battery is inserted. Once the battery is detected, the output current increases from 0A to 1.3A, which is the programmed charge current for this application.

(11)

Figure 9. Battery Detection Waveform When a Battery is Inserted

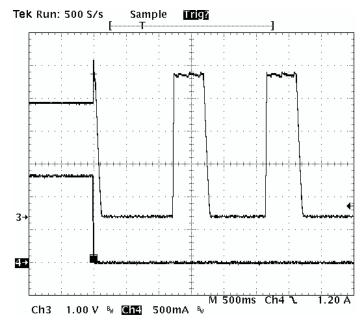

Figure 10 shows the battery detection scheme when a battery is removed. Channel 3 is the output signal and Channel 4 is the output current. When the battery is removed, the output signal goes up due to the stored energy in the inductor and it crosses the  $V_{OREG} - V_{RCH}$  threshold. At this point the output current goes to 0A and the IC terminates the charge process and turns on the  $I_{DISCHG2}$  for  $I_{DISCHG2}$ . This causes the output voltage to fall down below the  $V_{OREG} - V_{RCHG}$  threshold triggering a *Battery Absent* condition and starting the battery detection scheme.

Figure 10. Battery Detection Waveform When a Battery is Removed

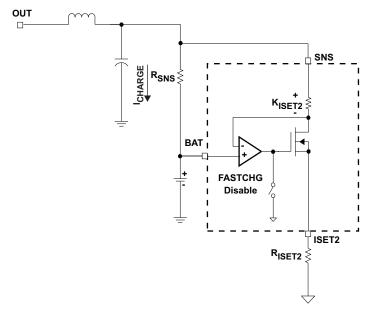

## **Current Sense Amplifier**

A current sense amplifier feature that translates the charge current into a DC voltage is offered. Figure 11 is a block diagram of this feature.

Figure 11. Current Sense Amplifier

The voltage on the ISET2 pin can be used to calculate the charge current. Equation 12 shows the relationship between the ISET2 voltage and the charge current:

$$I_{CHARGE} = \frac{V_{ISET2} \times K_{(ISET2)}}{R_{SNS} \times R_{ISET2}}$$

(12)

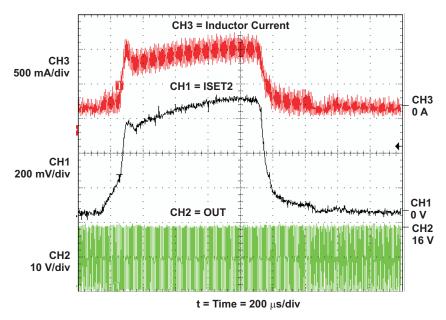

This feature can be used to monitor the charge current (Figure 12) during the current regulation phase (Fastcharge only) and the voltage regulation phase. The schematic for the application circuit for this waveform is shown in Figure 14

Figure 12. Current Sense Amplifier Charge Current Waveform

# **bqSWITCHER SYSTEM DESIGN EXAMPLE**

The following section provides a detailed system design example for the bq24100.

# **System Design Specifications:**

- V<sub>IN</sub> = 16V

- V<sub>BAT</sub> = 4.2V (1-Cell)

- I<sub>CHARGE</sub> = 1.33 A

- I<sub>PRECHARGE</sub> = I<sub>TERM</sub> = 133 mA

- Safety Timer = 5 hours

- Inductor Ripple Current = 30% of Fast Charge Current

- Initiate Charge Temperature = 0°C to 45°C

- 1. Determine the inductor value  $(L_{\mbox{\scriptsize OUT}})$  for the specified charge current ripple:

$$\Delta I_{L} = I_{CHARGE} \times I_{CHARGE} Ripple$$

$$L_{OUT} = \frac{V_{BAT} \times (V_{INMAX} - V_{BAT})}{V_{INMAX} \times f \times \Delta I_{L}}$$

$$L_{OUT} = \frac{4.2 \times (16 - 4.2)}{16 \times (1.1 \times 10^{6}) \times (1.33 \times 0.3)}$$

$$L_{OUT} = 7.06 \,\mu\text{H}$$

(13)

Set the output inductor to standard 10 µH. Calculate the total ripple current with using the 10 µH inductor:

$$\Delta I_{L} = \frac{V_{BAT} \times (V_{INMAX} - V_{BAT})}{V_{INMAX} \times f \times L_{OUT}}$$

$$\Delta I_{L} = \frac{4.2 \times (16 - 4.2)}{16 \times (1.1 \times 10^{6}) \times (10 \times 10^{-6})}$$

$$\Delta I_{L} = 0.282 \text{ A}$$

(14)

Calculate the maximum output current (peak current):

$$I_{LPK} = I_{OUT} + \frac{\Delta I_{L}}{2}$$

$$I_{LPK} = 1.33 + \frac{0.282}{2}$$

$$I_{LPK} = 1.471 \text{ A}$$

(15)