Data sheet acquired from Harris Semiconductor SCHS109B – Revised June 2003

# CMOS Programmable Divide-by-"N" Counter

Standard "A"-Series Types (3-to-15-Volt Rating)

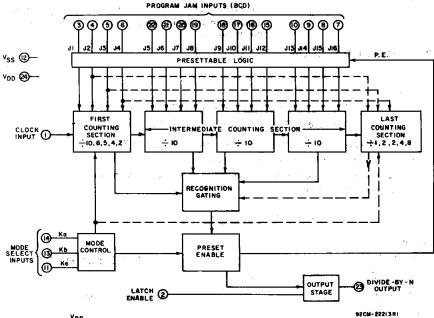

■CD4059 standard "A"-Series types are divide-by-N down-counters that can be programmed to divide an input frequency by any number "N" from 3 to 15,999. The output signal is a pulse one clock-cycle wide occurring at a rate equal to the input frequency divided by N. This single output has TTL drive capability. The down-counter is preset by means of 16 jam inputs.

The three Mode-Select Inputs Ka, Kb, and Kc determine the modulus ("divide-by" number) of the first and last counting sections in accordance with the truth table shown in Table I. Every time the first (fastest) counting section goes through one cycle, it reduces by 1 the number that has been preset (jammed) into the three decades of the intermediate counting section and into the last counting section, which consists of flip-flops that are not needed for operating the first counting section. For example, in the ÷ 2 mode, only one flip-flop is needed in the first counting section. Therefore the last counting section has three flip-flops that can be preset to a maximum count of seven with a place value of thousands. If ÷ 10 is desired for the first section. Ka is set to 1, Kb to 1, and Kc to 0. Jam Inputs J1, J2, J3, and J4 are used to preset the first counting section and there is no last counting section. The intermediate counting section consists of three cascaded BCD decade (÷ 10) counters presettable by means of Jam Inputs J5 through J16.

The Mode-Select Inputs permit frequency-synthesizer channel separations of 10, 12.5, 20, 25, or 50 parts. These inputs set the maximum value of N at 9999 (when the first counting section divides by 5 or 10) or 15,999 (when the first counting section divides by 8, 4, or 2).

The three decades of the intermediate counting section can be preset to a binary 15 instead of a binary 9, while their place values are still 1, 10, and 100, multiplied by the number of the  $\div$  N mode. For example, in the  $\div$  8 mode, the number from which counting-down begins can be preset to:

3rd decade: 1500 2nd decade: 150 1st decade: 15 Last counting section 1000

The total of these numbers (2665) times 8 equals 21,320. The first counting section can be preset to 7. Therefore, 21,327 is the maximum possible count in the ÷ 8 mode.

The highest count of the various modes is shown in the column entitled Extended

Counter Range of Table 1. Control inputs Kb and Kc can be used to initiate and lock the counter in the "master preset" state. In this condition the flip-flops in the counter are preset in accordance with the jam inputs and the counter remains in that state as long as Kb and Kc both remain low. The counter begins to count down from the preset state when a counting mode other than the master preset mode is selected.

The counter should always be put in the master preset mode before the ÷5 mode is selected.

Whenever the master preset mode is used, control signals Kb=0 and Kc=0 must be applied for at least 3 full clock pulses.

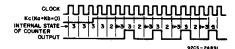

After the Master Preset Mode inputs have been changed to one of the  $\div$  modes, the next positive-going clock transition changes an internal flip-flop so that the countdown can begin at the second positive-going clock transition. Thus, after an MP (Master Preset) mode, there is always one extra count before the output goes high. Fig.1 illustrates a total count of 3 ( $\div$  8 mode). If the Master Preset mode is started two clock cycles or less before an output pulse, the output pulse will appear at the time due. If the Master Preset Mode is not used the counter jumps back to the "JAM" count when the output pulse appears.

Fig. 1 - Total count of 3.

A "1" on the Latch Enable input will cause the counter output to remain high once an output pulse occurs, and to remain in the high state until the latch input returns to "0". If the Latch Enable is "0", the output pulse will remain high for only 1 cycle of the clock-input signal.

As illustrated in the sample applications, this device is particularly advantageous in communication digital frequency synthesis (VHF, UHF, FM, AM, etc.) where programmable divide-by-"N" counters are an integral part of the synthesizer phase-locked-loop subsystem. The CD4059A can also be used to perform the synthesizer "Fixed Divide-by-R" counting function. It is also useful in general-purpose counters for instrumentation functions such as totalizers, production counters, and "time out" timers.

Operational and Performance Features:

- Synchronous Programmable ÷ N Counter:

N = 3 to 9999 or 15,999

- Presettable down-counter

CD4059A Types

- Fully static operation

- Mode-select control of initial decade counting function (÷ 10,8,5,4,2)

- T<sup>2</sup>L drive capability

- Master preset initialization

- Latchable ÷ N output

- Quiescent current specified to 15 volts

- Max. input leakage current of 1 μA at 15 volts, full package-temperature range

- 1 volt noise margin, full packagetemperature range

- 5-V and 10-V parametric ratings

Applications

- Communications digital frequency synthesizers: VHF, UHF, FM, AM, etc.

- Fixed or programmable frequency division

- "Time out" timer for consumer-application industrial controls

- Companion Application Note, ICAN-6374, "Application of the CMOS CD4059A Programmable Divide-by-N Counter in FM and Citizens Band Transceiver Digital Tuners"

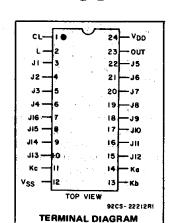

The CD4059A-series types are supplied in 24-lead dual-in-line plastic packages (E suffix), and 24-lead small-outline packages (M and M96 suffixes).

# MAXIMUM RATINGS, Absolute-Maximum Values:DC SUPPLY-VOLTAGE RANGE, (VDD)Voltages referenced to $V_{SS}$ Terminal)-0.5V to +15VINPUT VOLTAGE RANGE, ALL INPUTS-0.5V to $V_{DD}$ +0.5VPOWER DISSIPATION PER PACKAGE (PD):For $T_A = -55^{\circ}C$ to +100°C500mWFor $T_A = +100^{\circ}C$ to +125°CDerate Linearly to 100mWDEVICE DISSIPATION PER OUTPUT TRANSISTORFOR $T_A = FULL$ PACKAGE-TEMPERATURE RANGE (All Package Types)100mWOPERATING-TEMPERATURE RANGE ( $T_{AD}$ )-55°C to +125°CSTORAGE TEMPERATURE RANGE ( $T_{SIg}$ )-65°C to +150°CLEAD TEMPERATURE (DURING SOLDERING):At distance 1/16 $\pm$ 1/32 inch (1.59 $\pm$ 0.79mm) from case for 10s max

### STATIC ELECTRICAL CHARACTERISTICS

|                         | C          | onditio  | ons /  | 4 . 1 .      |               | L             | imits             |                                                  | •                 |                |       |  |

|-------------------------|------------|----------|--------|--------------|---------------|---------------|-------------------|--------------------------------------------------|-------------------|----------------|-------|--|

| Characteristic          | Vo         | VIN      | VDD    | J            | ·             |               |                   |                                                  |                   |                | Units |  |

| * *                     | (V)        | (V)      | (V)    | -55°         | _40°          | +850          | +1250             |                                                  | +25°              |                | ļ     |  |

|                         |            |          |        |              | <del></del>   |               |                   | Min.                                             |                   | Max.           | ļ     |  |

| Quiescent Device        |            |          | 5      | 10           | 10            | 700           | 300               |                                                  | 0.02              | 10             |       |  |

| Current,                |            | <b>├</b> | 10     | 20           | 20            | 200           | 400               |                                                  | 0.02              | 20             | μA    |  |

| IL Max.                 | v.         | 25d -    | : 15   | - '          | <u> </u>      |               |                   |                                                  |                   | 500            | 7.4   |  |

| Output Voltage:         | ٠          | 100      | .2811  | . 77         |               | • •           | - 1.              | ٠.                                               |                   | :              |       |  |

| Low Level,              | · j.       | 0,5      | 5      |              |               | .05           | **_*              | -                                                | 0                 | 0.05           | 37    |  |

| VOL Max.                | . 1        | 0,10     | 10     |              | . 0           | .05           | 12.3              | -                                                | 0                 | 0.05           | l v   |  |

| High Level,             | (177)      | 0,5      | ·· 5   |              | 4             | .95           |                   | 4.95                                             | 5                 |                |       |  |

| VOH Min.                | *:         | 0,10     | 10     | , ,          | 9             | .95           |                   | 9.95                                             | 10                | -              | ]     |  |

| Noise Immunity:         |            |          |        |              |               |               | · · · · · · · · · | <u> </u>                                         |                   |                | · .   |  |

| Inputs Low,             |            |          | - 5    | 2            | 1             | .5            |                   | 1.5                                              | 2.25              | L              |       |  |

| V <sub>NL</sub> Min.    |            |          | 10     |              |               | 3             | 3                 | 4.5                                              | -                 | - v            |       |  |

| Inputs High,            | ,          |          | 5      |              | 1             | .5            | 1                 | 2.25                                             | -                 |                |       |  |

| VNH Min.                |            |          | 10     |              |               | 3             |                   | 3                                                | 4.5               |                |       |  |

| Noise Margin:           | ٠.         |          |        |              |               |               |                   | · · ·                                            |                   |                |       |  |

| inputs Low,             | 4.5        |          | - 5    |              |               |               | -1                |                                                  | 1.                |                |       |  |

| VNML Min.               | 9          |          | 10     | ,            | ··            |               | <del>- i</del>    |                                                  |                   |                | ·     |  |

| Inputs High,            | 0.5        |          | - 5    |              |               |               | 1                 |                                                  |                   |                | ٧     |  |

| VNMH Min.               | 1          |          | 10     |              |               |               | <del></del>       |                                                  |                   |                | ł     |  |

|                         |            |          | -      |              |               |               | <del></del>       | <i>.</i>                                         |                   | · ·            |       |  |

| Output Drive            |            |          | ,      |              |               |               |                   |                                                  |                   | 1              |       |  |

| Current:<br>N-Channel   |            |          |        |              |               |               | e                 | ' '                                              |                   |                | **    |  |

| (Sink)                  | 0.4        |          | 5      | 2.5          | 2.3           | 1.6           | 1.4               | 2                                                | 4                 | <u> </u>       |       |  |

| IDN Min.                | 0.5        |          | 10     | 5            | 4.7           | 3.3           | 2.8               | 4                                                | 9                 | - "            |       |  |

|                         | 2.5        |          | _      |              | 10            |               | 1 15              | <del>                                     </del> | 20                | -              | mΑ    |  |

| P-Channel<br>(Source)   | 2.5<br>4.6 |          | 5<br>5 | -2<br>-0.5   | -1.8<br>-0.45 | -1.3<br>-0.36 | -1.15<br>-0.3     | -1.6<br>-0.4                                     |                   | <del>  -</del> |       |  |

| (Source)                | 9.5        |          | 10     | -U.5<br>-1.1 | -0.45         | -0.75         | -0.65             | -0.4                                             | -1.8              |                |       |  |

|                         | 9.0        |          | 10     | -1.1         |               | -0.75         | 0.05              | _0.9                                             | -1.8              | <del></del> -  | ├     |  |

| Input Leakage Current:* |            |          | 15     |              |               | ±1            |                   | • 1°                                             | ±10 <sup>-5</sup> | ±1             | μΑ    |  |

| IIL, IIH Max.           |            |          |        |              |               |               |                   | * .                                              |                   |                | + 1   |  |

<sup>\*</sup> Any Input

# OPERATING CONDITIONS AT TA = 25°C

For maximum reliability, nominal operating conditions should be selected so that operation is always within the following ranges.

| Characteristic                                        | VDD     | Min.       | Max.     | Units |

|-------------------------------------------------------|---------|------------|----------|-------|

| Supply Voltage<br>Range<br>(over full temp.<br>range) | . –     | 3          | 12       | v     |

| Clock Pulse<br>Width                                  | 5<br>10 | 200<br>100 | _        | ns    |

| Clock Input<br>Frequency                              | 5<br>10 | =-         | 1.5<br>3 | MHz   |

| Clock Input Rise<br>and Fall Time                     | 5<br>10 | 1,1        | 15<br>5  | μs    |

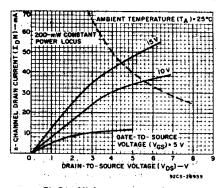

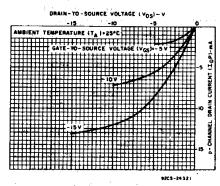

Fig.2 — Minimum output n-channel drain characteristics.

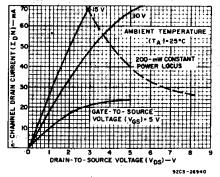

Fig.3 — Typical output n-channel drain characteristics.

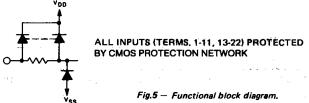

Fig.4 - Minimum output p-channel drain characteristics.

DYNAMIC ELECTRICAL CHARACTERISTICS AT TA = 25°C, CL = 50 pF, Input  $t_r, t_f$  = 20 ns, RL = 200 kΩ

| CHARACTERISTIC                                        | CONDI-<br>TIONS<br>VDD | ALI        | UNITS |          |                  |  |  |

|-------------------------------------------------------|------------------------|------------|-------|----------|------------------|--|--|

|                                                       | , (V)                  | Min.       | Тур.  | Max.     |                  |  |  |

| Bransation Balay Time: tay to                         | .5                     | <i>"</i> – | 180   | 360      |                  |  |  |

| Propagation Delay Time; tpHL, tpLH                    | 10                     | -          | 90    | 180      | ns               |  |  |

| Transition Time:                                      | 5                      |            | 35    | 70       | 1, 7<br>14 (1) 1 |  |  |

|                                                       | 10                     |            | 100   | 200      | ns               |  |  |

| · <sup>t</sup> tlh .                                  | 10                     | -          | 50    | 100      | 1                |  |  |

| Mariana Chali Iana Fasiiana fa                        | 5                      | 1.5        | 3     | <u> </u> | MII-             |  |  |

| Maximum Clock Input Frequency, fCL                    | 10                     | 3          | 6     | <u> </u> | MHz              |  |  |

| Average Input Capacitance, C <sub>I</sub> (any input) | _                      | -          | 5     | -        | pF               |  |  |

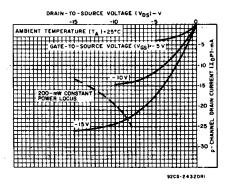

Fig.6 — Typical output p-channel drain characteristics.

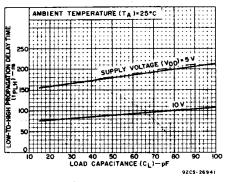

Fig.7 — Typical low-to-high propagation delay time vs. load capacitance.

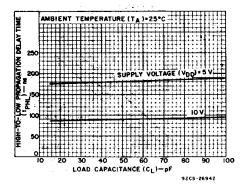

Fig.8 - Typical high-to-low propagation delay time vs. load capacitance.

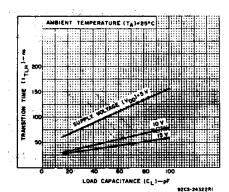

Fig.9 - Typical low-to-high transition time vs. load capacitance.

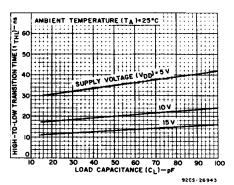

Fig.10 — Typical high-to-low transition time vs. load capacitance.

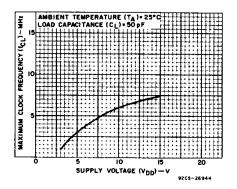

Fig.11 — Typical max. clock frequency vs. supply voltage.

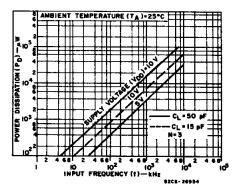

Fig. 12 — Typical power dissipation vs. input frequency.

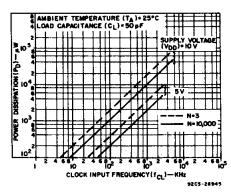

Fig. 13 — Typical power dissipation vs. clock input frequency.

### TABLE I

| s  | MODE SELECT INPUT FIRST COUNTING SECTION |     |                             |                            |                         |                    | T COUN<br>SECTIO           |                               | COUNTER<br>RANGE<br>DESIGN EXTENDE |        |  |

|----|------------------------------------------|-----|-----------------------------|----------------------------|-------------------------|--------------------|----------------------------|-------------------------------|------------------------------------|--------|--|

| Ka | Kb                                       | Kc  | MODE<br>Di-<br>vides<br>by: | Can be preset to a max of: | Jam≜<br>inputs<br>used: | MODE Di- vides by: | Can be preset to a max of: | Jam <sup>≜</sup> inputs used: | Мах.                               | Max.   |  |

| 1  | 1                                        | 1   | 2                           | 1                          | J1                      | 8                  | 7                          | J2,J3,J4                      | 15,999                             | 17,331 |  |

| 0  | 1                                        | 1   | 4                           | 3                          | J1,J2                   | 4                  | 3                          | J3,J4                         | 15,999                             | 18,663 |  |

| 1  | 0                                        | 1   | 5#                          | 4                          | J1,J2,J3                | 2                  | 1                          | J4                            | 9,999                              | 13,329 |  |

| 0  | 0                                        | 1   | 8                           | 7                          | J1,J2,J3                | 2                  | 1                          | J4                            | 15,999                             | 21,327 |  |

| 1  | 1                                        | . 0 | 10                          | 9                          | J1,J2,J3,J4             | 1                  | 0                          | ľ –                           | 9,999                              | 16,659 |  |

| х  | 0                                        | 0   | MAST                        | TER PRE                    | SET                     | MAS                | TER PR                     | ESET                          | -                                  | _      |  |

X = Don't Care

▲ J1 = Least significant bit.

J4 = Most significant bit.

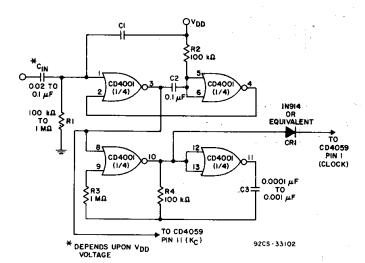

#Operation in the ÷5 mode (1st counting section) requires going through the Master Preset mode prior to going into the ÷5 mode. At power turn-on, kc must be a logic "O" for a period of 3 input clock pulses after V<sub>DD</sub> reaches a minimum of 3 volts. See Fig. 21 for a suggested external preset circuit.

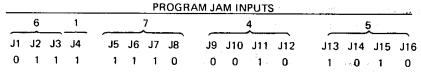

### HOW TO PRESET THE CD4059A TO DESIRED + N

The value N is determined as follows:

MODE= First counting section divider (10, 8, 5, 4 or 2)

To calculate preset values for any N count, divide the N count by the Mode.

The resultant is the corresponding preset values of the 5th through 2nd decade with the remainder being equal to the 1st decade value.

Preset Value =

$$\frac{N}{\text{Mode}}$$

(2)

Examples:

|   |    |    |    |    | ٢  | HOC | HAM | JAM: | INPU | TS (B | CD) |     |     |     | ٠   |  |

|---|----|----|----|----|----|-----|-----|------|------|-------|-----|-----|-----|-----|-----|--|

|   | 4  | _  | 1_ |    |    | 5   |     |      | . !  | 9     |     |     | 9   | 3   |     |  |

| 1 | J2 | J3 | J4 | J5 | J6 | J7  | J8  | J9   | J10  | J11   | J12 | J13 | J14 | J15 | J16 |  |

| ) | 0  | 1  | 1  | 1  | 0  | 1   | 0   | 1    | 0    | 0     | 1   | 0   | 1   | 1   | 0   |  |

To verify the results use equation 1:

Ka Kb Kc

MODE SELECT = 8

Copyright © 2003, Texas Instruments Incorporated

To verify:

N = 8 (1000 X 1 + 100 X 5 + 10 X 4 + 1 X 7) + 6 N = 12382

MODE SELECT = 10

C) N = 8479, Mode = 10

1 to 1 dist

Ka Kb Kc 1 1 0

PROGRAM JAM INPUTS

9 7 4 8

J1 J2 J3 J4 J5 J6 J7 J8 J9 J10 J11 J12 J13 J14 J15 J16

1 0 0 1 1 1 1 0 0 0 1 0 0 0 0 1

To Verify:

$N = 10 (1000 \times 0 + 100 \times 8 + 10 \times 4 + 1 \times 7) + 9$ N = 8479

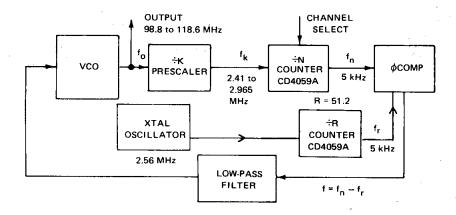

### DIGITAL PHASE-LOCKED LOOP (PLL) FOR FM BAND SYNTHESIZER

### 1) Calculating Min & Max "N" Values :

Output Freq. Range ( $\tau_0$ ) = 98.8 to 118.6 MHz Channel Spacing Freq. ( $f_c$ ) = 200 kHz

Division Factor (k) = 40

Reference Freq. (fr) =

$$\frac{f_C}{k} = \frac{200}{40}$$

kHz = 5 kHz

$$f_{k} = \frac{f_{0}}{40}$$

:  $f_{k}Max. = \frac{118.6 \text{ MHz}}{40} = 2.965 \text{ MHz}$ ;  $f_{k}Min = \frac{98.8 \text{ MHz}}{40} = 2.47 \text{ MHz}$

$\therefore N = \frac{f_{0}}{f_{0}}$

$$N_{Max} = \frac{118.6 \text{ MHz}}{200 \text{ kHz}} = 593$$

$N_{Min} = \frac{98.8 \text{ MHz}}{200 \text{ kHz}} = 494$   $R = \frac{2.56 \text{ MHz}}{5 \text{ kHz}} = 512$

### "CASCADING" VIA OTHER COUNTERS

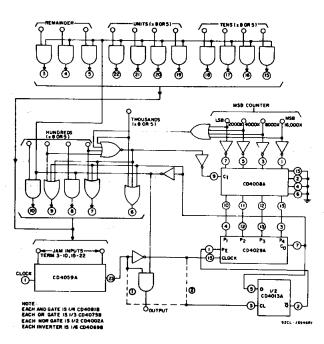

Fig. 14 shows a BCD-switch compatible arrangement suitable for ÷ 8 and ÷ 5 modes. which can be adapted, with slight changes, to the other divide-by-modes. In order to be able to preset to any number from three to about 256,000, while preserving the BCDswitch compatible character of the jam inputs, a rather complex cascading scheme is required. Such a cascading scheme is necessary because the CD4059A can never be preset to a count less than 3 and logic is needed to detect the condition that one of the numbers to be preset in the CD4059A is rather small. In order to simplify the detection logic, only that condition is detected where the jam inputs to terminals 6, 7, and 9 would be low during one count. If such a condition is detected, and if at least 1 is expected to be jammed into the MSB counter, the detection logic removes one from the number to be jammed into the MSB counter (with a place value of 2000 times the divide-by-mode) and jams the same 2000 into the CD4059A by forcing terminals 6, 7, and 9 high.

The clock of the CD4013A may be driven directly from the output of the CD4059A, as shown by dashed option (1), or by the inverted output of the CD4059A, option (2). If option (2) is used the CD4029A cannot count cycles shorter than 3. If option (1) is used propagation delay problems may occur at high counting speeds.

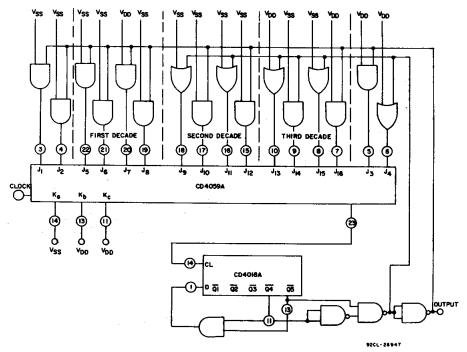

The general circuit in Fig.14 can be simplified considerably if the range of the cascaded counters does not have to start at a very low value. Fig.15 shows an arrangement in the ÷ 4 mode, where the counting range extends in a BCD-switch compatible manner from 88,003 to 103,999. The arrangement shown in Fig.15 is easy to follow; once during each cycle, the less significant digits are jammed in (14,712 in this case) and then 11,000 (4 x 2750) is jammed in eight times in succession, by forcing jam inputs high or low, as required.

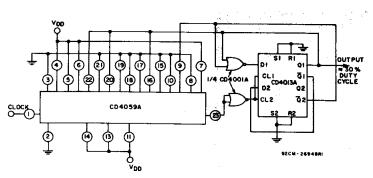

Numbers larger than the extended counter range can also be produced by cascading the CD4059A with some other counting device. Fig.16 shows such an arrangement where only one fixed divide-by number is desired which is close to three times the extended counter range as shown in the last column of Table I.. The dual flip-flop wired to produce a ÷ 3 count, can be replaced by other counters such as the CD4029, CD4510, CD4516, CD4017, or the CD4022. In Fig.16 the ÷ N subsystem is preset once to a number smaller than the desired divide-by number. This smaller number represents the less significant digits of the divide-by number. The subsystem is then preset one or more times to a round number (e.g. 1000, 2000) and multiplied by the number of the divide-by mode (÷ 2 in the example of Fig.16). It is important that the second counting device has an output that is high or low, as the case may be, during only one of its counting

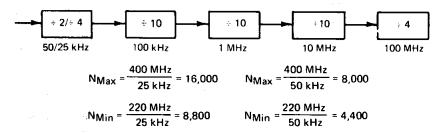

# 2) ÷ N Counter Configuration for UHF — 220 to 400 MHz Channel Spacing: 50 kHz or 25 kHz

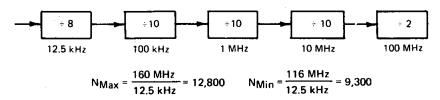

### 3) ÷ N Counter Configuration to VHF - 116 MHz

### Channel Spacing = 12.5 kHz

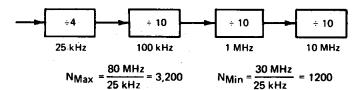

### 4) ÷ N Counter Configuration for VHF -- 30 to 80 MHz Channel Spacing: 25 kHz

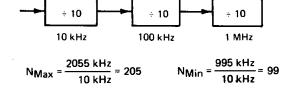

# 5) $\div$ N Counter Configuration for AM - 995 to 2055 kHz Channel Spacing = 10 kHz

Fig.14 — BCD switch-compatible  $\div N$  system of the most general kind.

Fig.15 - Dividing by any number from 88,003 to 103,999.

Fig. 16 - Division by 47,690 in ÷2 mode.

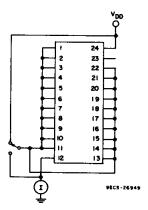

Fig.17 - Quiescent device current test circuit.

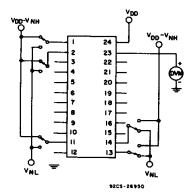

Fig.18 — Noise immunity test circuit.

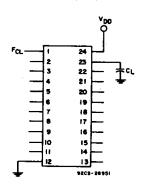

Fig. 19 -- Power dissipation test circuit (ell ÷ modes).

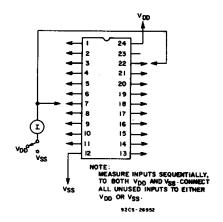

Fig.20 - Input leakage current test circuit,

Copyright © 2003, Texas Instruments Incorporated

For changing from any mode other than mode 5 (with power on), apply positive pulse to  $C_{\rm in}$ . This circuit automatically selects master preset mode ( $K_b=0$ ,  $K_c=0$ ) before going into the select conditions for mode 5 ( $K_a=1$ ,  $K_b=0$ , K=1). The selection of  $C_1$  and  $C_2$  is critical.  $C_1$  is determined by the VDD voltage—the lower VDD's need larger  $C_1$ 's.  $C_2$  must be 0.1  $\mu F$  or larger.

Fig.21 - CD4059A mode 5 power on master preset circuit.

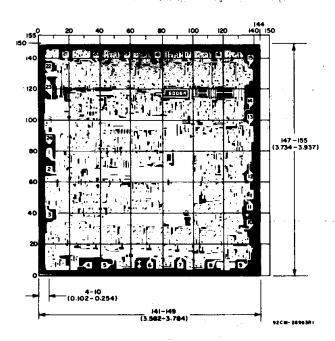

Dimensions in parentheses are in millimeters and are derived from the basic inch dimensions as indicated. Grid graduations are in mils (10<sup>-3</sup> inch).

Dimensions and pad layout for CD4059AH.

www.ti.com 9-Dec-2023

### PACKAGING INFORMATION

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan                | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|------------|--------------|--------------------|------|----------------|-------------------------|-------------------------------|--------------------|--------------|-------------------------|---------|

| CD4059AD3        | ACTIVE     | CDIP SB      | JD                 | 24   | 15             | Non-RoHS &<br>Non-Green | SNPB                          | N / A for Pkg Type | -55 to 125   | CD4059AD/3              | Samples |

| CD4059AM         | ACTIVE     | SOIC         | DW                 | 24   | 25             | RoHS & Green            | NIPDAU                        | Level-1-260C-UNLIM | -55 to 125   | CD4059AM                | Samples |

| CD4059AMG4       | ACTIVE     | SOIC         | DW                 | 24   | 25             | RoHS & Green            | NIPDAU                        | Level-1-260C-UNLIM | -55 to 125   | CD4059AM                | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

### **PACKAGE OPTION ADDENDUM**

www.ti.com 9-Dec-2023

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

### OTHER QUALIFIED VERSIONS OF CD4059A, CD4059A-MIL:

Military: CD4059A-MIL

NOTE: Qualified Version Definitions:

• Catalog - TI's standard catalog product

• Military - QML certified for Military and Defense Applications

### PACKAGE MATERIALS INFORMATION

www.ti.com 5-Jan-2022

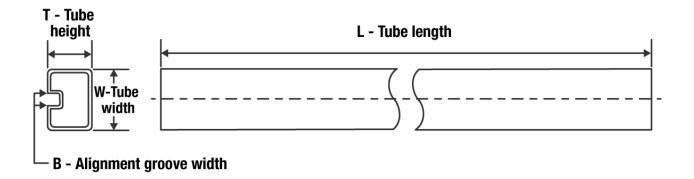

### **TUBE**

### \*All dimensions are nominal

| Device     | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| CD4059AM   | DW           | SOIC         | 24   | 25  | 506.98 | 12.7   | 4826   | 6.6    |

| CD4059AMG4 | DW           | SOIC         | 24   | 25  | 506.98 | 12.7   | 4826   | 6.6    |

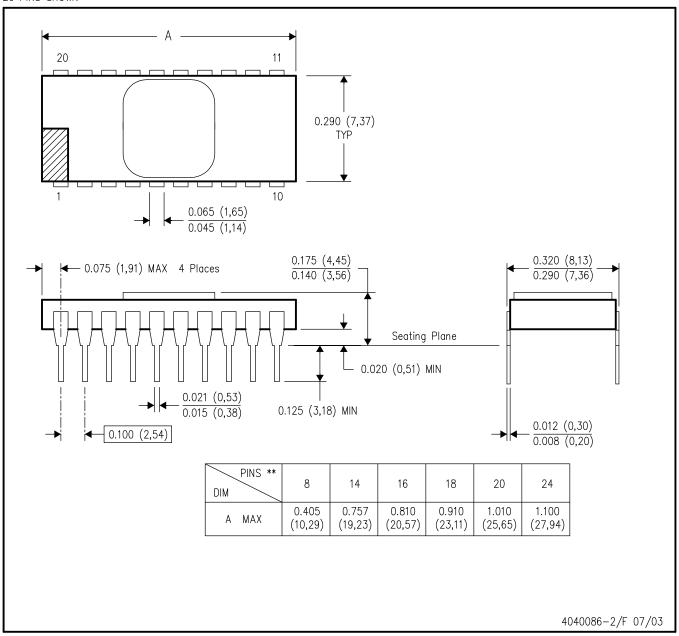

## JD (R-CDIP-T\*\*)

### CERAMIC SIDE-BRAZE DUAL-IN-LINE PACKAGE

20 PINS SHOWN

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. This package is hermetically sealed with a metal lid.

- D. The terminals are gold plated.

- E. Falls within MIL STD 1835 CDIP2 T8, T14, T16, T18, T20 and T24 respectively.

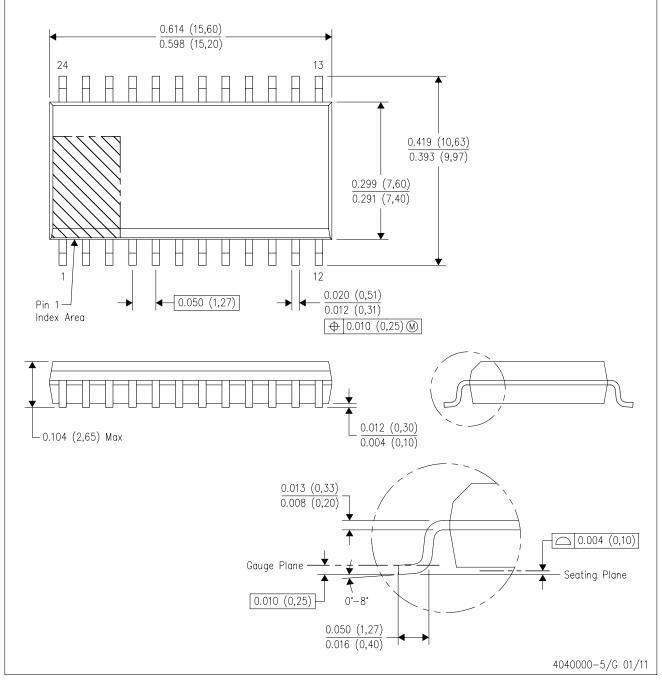

DW (R-PDSO-G24)

### PLASTIC SMALL OUTLINE

NOTES: A. All linear dimensions are in inches (millimeters). Dimensioning and tolerancing per ASME Y14.5M-1994.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

- D. Falls within JEDEC MS-013 variation AD.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated