# DS160UP822 UPI 2.0 16-Gbps 8-Channel Linear Redriver with Four 2x2 Crosspoint

#### 1 Features

- Eight channel linear equalizer supporting UPI 2.0 up to 16 Gbps

- Protocol agnostic linear redriver supporting many high speed interface including DisplayPort, SAS, SATA, XFI

- Provides four 2x2 Crosspoint mux function

- CTLE boosts up to 18 dB at 8 GHz

- Ultra-low latency of 90 ps

- Low additive random jitter of 70 fs with PRBS data

- Single 3.3 V supply

- Low active power of 107 mW/channel

- No heat sink required

- Pin-strap, SMBus/I <sup>2</sup> C or EEPROM programming

- Seamless support for link training

- Support for x4, x8, x16, x24 bus width with one or multiple DS160UP822

- Industrial temperature range of -40°C to 85°C

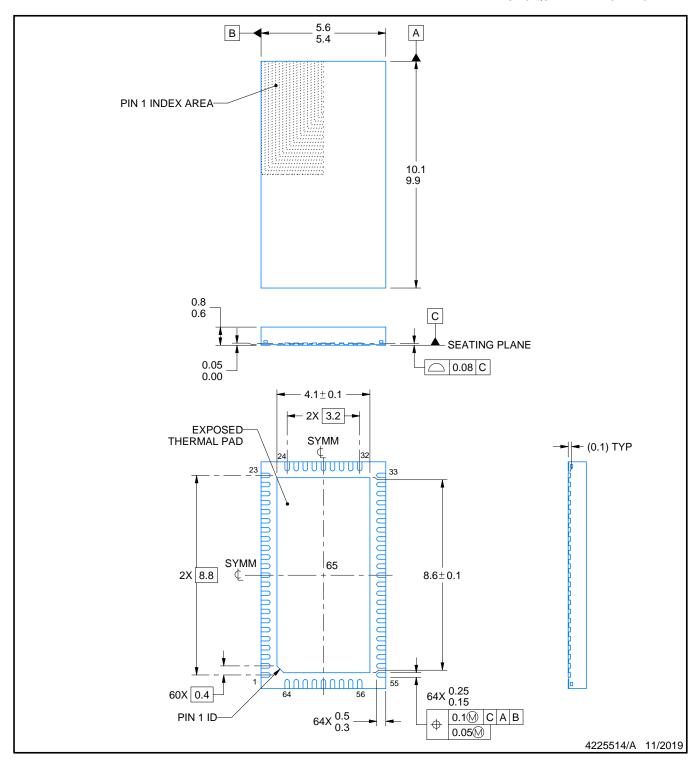

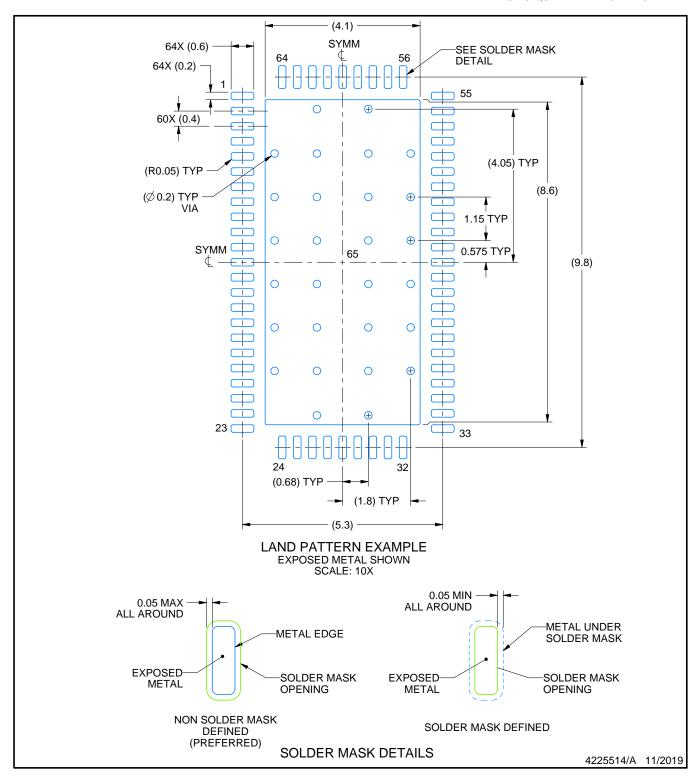

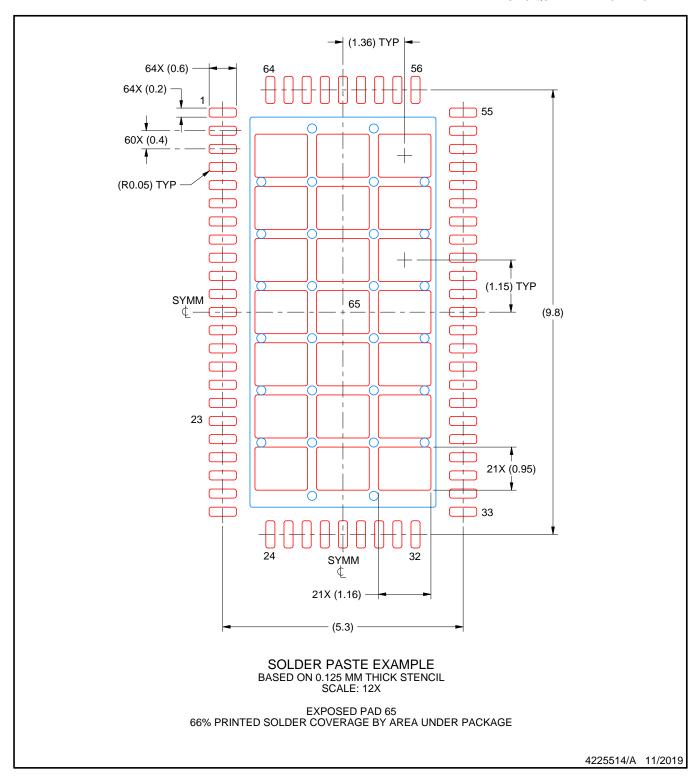

- 5.5 mm × 10 mm, 64-pin WQFN package

# 2 Applications

- Rack server

- Microserver & tower server

- High performance computing

- Hardware accelerator

# 3 Description

The DS160UP822 is an eight channel low-power high-performance linear redriver designed to support Ultra Path Interface (UPI) 2.0 up to 16 Gbps. The device is a protocol agnostic linear redriver that can operate for many differential interfaces.

The DS160UP822 receivers deploy continuous time linear equalizers (CTLE) to provide a high-frequency boost. The equalizer can open an input eye that is completely closed due to inter-symbol interference (ISI) induced by an interconnect medium, such as PCB traces and cables. The linear redriver along with the passive channel as a whole get link trained for best transmit and receive equalization settings resulting in best electrical link and lowest possible latency. Low channel-channel cross-talk, low additive jitter and excellent return loss allows the device to become almost a passive element in the link. The devices has internal linear voltage regulator to provide clean power supply for high speed datapaths that provides high immunity to any supply noise on the board.

The DS160UP822 implements high speed testing production for reliable high manufacturing. The device also has low AC and DC gain variation providing consistant equalization in high volume platform deployment.

#### Device Information (1)

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| DS160UP822  | WQFN (64) | 5.5 mm × 10.00 mm |

For all available packages, see the orderable addendum at the end of the data sheet.

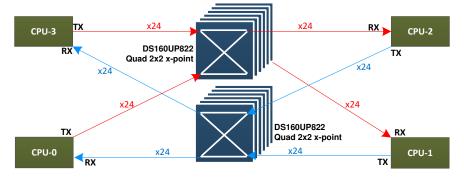

**Typical Application**

# **Table of Contents**

| 1 Features1                                | 7.2 Functional Block Diagram                         | .16 |

|--------------------------------------------|------------------------------------------------------|-----|

| 2 Applications1                            | 7.3 Feature Description                              | .16 |

| 3 Description1                             | 7.4 Device Functional Modes                          | .18 |

| 4 Revision History2                        | 7.5 Programming                                      | 18  |

| 5 Pin Configuration and Functions3         | 8 Application and Implementation                     | 21  |

| Pin Functions4                             | 8.1 Application Information                          | 21  |

| 6 Specifications7                          | 8.2 Typical Applications                             | 21  |

| 6.1 Absolute Maximum Ratings7              | 9 Power Supply Recommendations                       | .25 |

| 6.2 ESD Ratings                            | 10 Layout                                            | .26 |

| 6.3 Recommended Operating Conditions7      | 10.1 Layout Guidelines                               | 26  |

| 6.4 Thermal Information8                   | 10.2 Layout Example                                  | 27  |

| 6.5 DC Electrical Characteristics8         | 11 Device and Documentation Support                  | .28 |

| 6.6 High Speed Electrical Characteristics9 | 11.1 Receiving Notification of Documentation Updates | 28  |

| 6.7 SMBUS/I2C Timing Characteristics10     | 11.2 Community Resources                             | .28 |

| 6.8 Typical Characteristics12              | 11.3 Trademarks                                      | 28  |

| 7 Detailed Description15                   | 12 Mechanical, Packaging, and Orderable              |     |

| 7.1 Overview                               | Information                                          | 28  |

|                                            |                                                      |     |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| DATE          | REVISION | NOTES           |

|---------------|----------|-----------------|

| December 2020 | *        | Initial release |

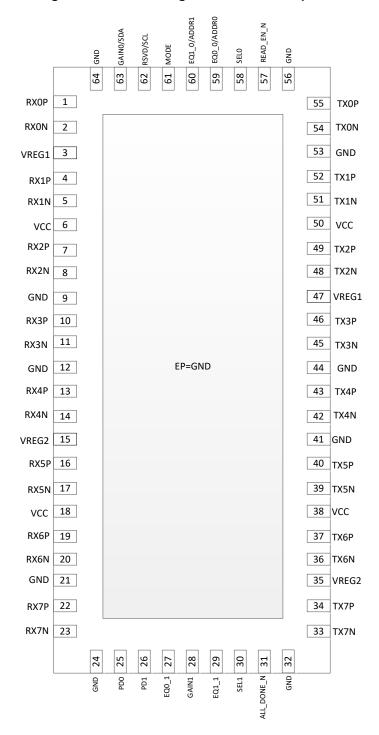

# **5 Pin Configuration and Functions**

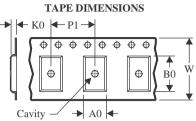

Figure 5-1. NJX Package 64-Pin WQFN Top View

# **Pin Functions**

| PIN           | ı                                         | UO TYPE                                             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------|-------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME          | NO.                                       | I/O, TYPE                                           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ALL_DONE_N    | 31                                        | O, 3.3 V open<br>drain                              | In SMBus/I²C Master Mode: Indicates the completion of a valid EEPROM register load operation. External pullup resistor such as $4.7~\mathrm{k}\Omega$ required for operation. High: External EEPROM load failed or incomplete Low: External EEPROM load successful and complete In SMBus/I²C slave/Pin Mode: This output is High-Z. The pin can be left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| MODE          | 61                                        | I, 4-level                                          | Sets device control configuration modes. 4-level IO pin as defined in Table 7-1. The pin can be exercised at device power up or in normal operation mode.  L0: Pin Mode – device control configuration is done solely by strap pins.  L1: SMBus/I²C Master Mode - device control configuration is read from external EEPROM. When the device has finished reading from the EEPROM successfully, it will drive the ALL_DONE_N pin LOW. SMBus/I²C slave operation is available in this mode before, during or after EEPROM reading. Note during EEPROM reading if the external SMBus/I²C master wants to access the device registers it must support arbitration.  L2: SMBus/I²C Slave Mode – device control configuration is done by an external controller with SMBus/I²C master.  L3 (Float): RESERVED – TI internal test mode. |

| EQ0_0 / ADDR0 | 59                                        | I, 4-level                                          | In Pin Mode:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| EQ1_0 / ADDR1 | 60                                        | I, 4-level                                          | Sets receiver linear equalization (CTLE) for channels 0-3 according to Table 7-2. These pins are sampled at device power-up only. In <b>SMBus/I<sup>2</sup>C Mode:</b> Sets SMBus / I <sup>2</sup> C slave address according to Table 7-3. These pins are sampled at device power-up only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| EQ0_1         | 27                                        | I, 4-level                                          | Sets receiver linear equalization (CTLE) for channels 4-7 according to Table 7-2 in Pin mode. The pin is sampled at device power-up only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| EQ1_1         | 29                                        | I, 4-level                                          | Sets receiver linear equalization (CTLE) for channels 4-7 according to Table 7-2 in Pin mode. The pin is sampled at device power-up only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| GAIN0 / SDA   | 63                                        | I, 4-level / I/O,<br>3.3 V<br>LVCMOS,<br>open drain | In <b>Pin Mode:</b> Flat gain (DC and AC) from the input to the output of the device for channels 0-3. The pin is sampled at device power-up only. In <b>SMBus/l<sup>2</sup>C Mode:</b> 3.3 V SMBus/l <sup>2</sup> C data. External 1 k $\Omega$ to 5 k $\Omega$ pullup resistor is required as per SMBus / I <sup>2</sup> C interface standard.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| GAIN1         | 28                                        | I, 4-level                                          | Flat gain (DC and AC) from the input to the output of the device for channels 4-7 in Pin mode. The pin is sampled at device power-up only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GND           | EP, 9, 12, 21, 24, 32, 41, 44, 53, 56, 64 | Р                                                   | Ground reference for the device. EP: the Exposed Pad at the bottom of the QFN package. It is used as the GND return for the device. The EP should be connected to ground plane(s) through low resistance path. A via array provides a low impedance path to GND. The EP also improves thermal dissipation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PD0           | 25                                        | I, 3.3 V<br>LVCMOS                                  | 2-level logic controlling the operating state of the redriver. Active in all device control modes. The pin has internal 1-M $\Omega$ weak pulldown resistor. High: Power down for channels 0-3 Low: Power up, normal operation for channels 0-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PD1           | 26                                        | I, 3.3 V<br>LVCMOS                                  | 2-level logic controlling the operating state of the redriver. Active in all device control modes. The pin has internal 1-M $\Omega$ weak pulldown resistor. High: Power down for channels 4-7 Low: Power up, normal operation for channels 4-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| READ_EN_N     | 57                                        | I, 3.3 V<br>LVCMOS                                  | In SMBus/I²C Master Mode: After device power up, when the pin is low, it initiates the SMBus / I²C master mode EEPROM read function. Once EEPROM read is complete (indicated by assertion of ALL_DONE_N low), this pin can be held low for normal device operation. During the EEPROM load process the device's signal path is disabled. In SMBus/I²C Slave and Pin Modes: In these modes the pin is not used. The pin can be left floating. The pin has internal 1-M $\Omega$ weak pulldown resistor.                                                                                                                                                                                                                                                                                                                           |

PIN I/O. TYPE DESCRIPTION NAME NO. The pin selects the mux path for channels 0-3. L: straight data path - RX[0/1/2/3][P/N] connected to TX[0/1/2/3][P/N] through the I, 3.3 V SFI 0 58 redriver LVCMOS H: cross data path - RX[0/1/2/3][P/N] connected to TX[1/0/3/2][P/N] through the redriver Active in all device control modes. 59 kΩ internal pull-down. The pin selects the mux path for channels 4-7. L: straight data path - RX[4/5/6/7][P/N] connected to TX[4/5/6/7][P/N] through the I, 3.3 V SEL1 30 redriver. **LVCMOS** H: cross data path - RX[4/5/6/7][P/N] connected to TX[5/4/7/6][P/N] through the redriver Active in all device control modes. 59 kΩ internal pull-down. In Pin Mode: Reserved for TI internal use. The pin must be pulled down to GND I/O. 3.3 V through 1 k $\Omega$  resistor In SMBus/I<sup>2</sup>C Mode: RSVD / SCL 62 LVCMOS. 3.3V SMBus/I²C clock. External 1 k $\Omega$  to 5 k $\Omega$  pullup resistor is required as per SMBus / open drain I<sup>2</sup>C interface standard. Inverting differential inputs to the equalizer. Integrated 50  $\Omega$  termination resistor from RX0N 2 ı the pin to internal CM bias voltage. Channel 0. Noninverting differential inputs to the equalizer. Integrated 50  $\Omega$  termination resistor RX0P 1 from the pin to internal CM bias voltage. Channel 0. Inverting differential inputs to the equalizer. Integrated 50  $\Omega$  termination resistor from RX1N 5 ı the pin to internal CM bias voltage. Channel 1. Noninverting differential inputs to the equalizer. Integrated 50  $\Omega$  termination resistor RX1P 4 from the pin to internal CM bias voltage. Channel 1. Inverting differential inputs to the equalizer. Integrated 50  $\Omega$  termination resistor from RX2N 8 ı the pin to internal CM bias voltage. Channel 2. Noninverting differential inputs to the equalizer. Integrated 50  $\Omega$  termination resistor RX2P 7 from the pin to internal CM bias voltage. Channel 2. Inverting differential inputs to the equalizer. Integrated 50  $\Omega$  termination resistor from RX3N 11 1 the pin to internal CM bias voltage. Channel 3. Noninverting differential inputs to the equalizer. Integrated 50  $\Omega$  termination resistor RX3P 10 from the pin to internal CM bias voltage. Channel 3. Inverting differential inputs to the equalizer. Integrated 50  $\Omega$  termination resistor from RX4N 14 the pin to internal CM bias voltage. Channel 4. Noninverting differential inputs to the equalizer. Integrated 50  $\Omega$  termination resistor RX4P 13 1 from the pin to internal CM bias voltage. Channel 4. Inverting differential inputs to the equalizer. Integrated 50  $\Omega$  termination resistor from RX5N 17 1 the pin to internal CM bias voltage. Channel 5. Noninverting differential inputs to the equalizer. An on-chip, 100  $\Omega$  termination resistor RX5P 16 connects RXP to RXN. Channel 5. Inverting differential inputs to the equalizer. Integrated 50  $\Omega$  termination resistor from RX6N 20 the pin to internal CM bias voltage. Channel 6. Noninverting differential inputs to the equalizer. Integrated 50  $\Omega$  termination resistor RX6P ı 19 from the pin to internal CM bias voltage. Channel 6. Inverting differential inputs to the equalizer. Integrated 50  $\Omega$  termination resistor from RX7N 23 the pin to internal CM bias voltage. Channel 7. Noninverting differential inputs to the equalizer. Integrated 50  $\Omega$  termination resistor RX7P ı 22 from the pin to internal CM bias voltage. Channel 7. TX0N 54 0 Inverting pin for 100  $\Omega$  differential driver output. Channel 0. TX0P 0 55 Non-inverting pin for 100  $\Omega$  differential driver output. Channel 0. TX1N 51 O Inverting pin for 100  $\Omega$  differential driver output. Channel 1. TX1P 52 0 Non-inverting pin for 100  $\Omega$  differential driver output. Channel 1. TX2N 0 48 Inverting pin for 100  $\Omega$  differential driver output. Channel 2. TX2P 49 0 Non-inverting pin for 100  $\Omega$  differential driver output. Channel 2. TX3N Inverting pin for 100  $\Omega$  differential driver output. Channel 3. 45

|       | PIN           | UO TYPE   | DESCRIPTION                                                                                                                                                                                                   |  |  |

|-------|---------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME  | NO.           | I/O, TYPE | DESCRIPTION                                                                                                                                                                                                   |  |  |

| TX3P  | 46            | 0         | Non-inverting pin for 100 $\Omega$ differential driver output. Channel 3.                                                                                                                                     |  |  |

| TX4N  | 42            | 0         | Inverting pin for 100 $\Omega$ differential driver output. Channel 4.                                                                                                                                         |  |  |

| TX4P  | 43            | 0         | Non-inverting pin for 100 $\Omega$ differential driver output. Channel 4.                                                                                                                                     |  |  |

| TX5N  | 39            | 0         | Inverting pin for 100 $\Omega$ differential driver output. Channel 5.                                                                                                                                         |  |  |

| TX5P  | 40            | 0         | Non-inverting pin for 100 $\Omega$ differential driver output. Channel 5.                                                                                                                                     |  |  |

| TX6N  | 36            | 0         | Inverting pin for 100 $\Omega$ differential driver output. Channel 6.                                                                                                                                         |  |  |

| TX6P  | 37            | 0         | Non-inverting pin for 100 $\Omega$ differential driver output. Channel 6.                                                                                                                                     |  |  |

| TX7N  | 33            | 0         | Inverting pin for 100 $\Omega$ differential driver output. Channel 7.                                                                                                                                         |  |  |

| TX7P  | 34            | 0         | Non-inverting pin for 100 $\Omega$ differential driver output. Channel 7.                                                                                                                                     |  |  |

| vcc   | 6, 18, 38, 50 | Р         | Power supply pins. VCC = 3.3 V ±10%. The VCC pins on this device should be connected through a low-resistance path to the board VCC plane.                                                                    |  |  |

| VREG1 | 3, 47         | Р         | Internal voltage regulator output. Must add decoupling caps of 0.1 µF near each pins. The regulator is only for internal use. Do not use to provide power to any external component. Do not connect to VREG2. |  |  |

| VREG2 | 15, 35        | Р         | Internal voltage regulator output. Must add decoupling caps of 0.1 µF near each pi The regulator is only for internal use. Do not use to provide power to any external component. Do not connect to VREG1.    |  |  |

# **6 Specifications**

# **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)(1)

|                             |                                         | MIN  | MAX  | UNIT |

|-----------------------------|-----------------------------------------|------|------|------|

| VCC <sub>ABSMAX</sub>       | Supply voltage (VCC)                    | -0.5 | 4.0  | V    |

| VIO <sub>CMOS,ABSMAX</sub>  | 3.3 V LVCMOS and open drain I/O voltage | -0.5 | 4.0  | V    |

| VIO <sub>4LVL,ABSMAX</sub>  | 4-level input I/O voltage               | -0.5 | 2.75 | V    |

| VIO <sub>HS-RX,ABSMAX</sub> | High-speed I/O voltage (RXnP, RXnN)     | -0.5 | 3.2  | V    |

| VIO <sub>HS-TX,ABSMAX</sub> | High-speed I/O voltage (TXnP, TXnN)     | -0.5 | 2.75 | V    |

| T <sub>J,ABSMAX</sub>       | Junction temperature                    |      | 150  | °C   |

| T <sub>stg</sub>            | Storage temperature range               | -65  | 150  | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±3000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Pins listed as ±3 kV

may actually have higher performance.

### **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                       |                                                                                       |                                                 | MIN   | NOM | MAX  | UNIT |

|-----------------------|---------------------------------------------------------------------------------------|-------------------------------------------------|-------|-----|------|------|

| VCC                   | Supply voltage, VCC to GND                                                            | DC plus AC power should not exceed these limits | 3.0   | 3.3 | 3.6  | V    |

|                       |                                                                                       | DC to <50 Hz, sinusoidal                        |       |     | 250  | mVpp |

| N <sub>VCC</sub>      | Sumply paige telegones 1                                                              | 50 Hz to 500 kHz, sinusoidal                    |       |     | 100  | mVpp |

| INVCC                 | Supply noise tolerance <sup>1</sup>                                                   | 500 kHz to 2.5 MHz, sinusoidal                  |       |     | 33   | mVpp |

|                       |                                                                                       | >2.5 MHz, sinusoidal                            |       |     | 10   | mVpp |

| T <sub>RampVCC</sub>  | VCC supply ramp time                                                                  | From 0 V to 3.0 V                               | 0.150 |     | 100  | ms   |

| TJ                    | Operating junction temperature                                                        |                                                 | -40   |     | 115  | °C   |

| T <sub>A</sub>        | Operating ambient temperature                                                         |                                                 | -40   |     | 85   | °C   |

| PW <sub>LVCMOS</sub>  | Minimum pulse width required for the device to detect a valid signal on LVCMOS inputs | PD1/0, and READ_EN_N                            | 200   |     |      | uS   |

| VCC <sub>SMBUS</sub>  | SMBus/I <sup>2</sup> C SDA and SCL open drain termination voltage                     | Supply voltage for open drain pull-up resistor  |       |     | 3.6  | V    |

| F <sub>SMBus</sub>    | SMBus/I <sup>2</sup> C clock (SCL) frequency in SMBus slave mode                      |                                                 | 10    |     | 400  | kHz  |

| VID <sub>LAUNCH</sub> | Source differential launch amplitude                                                  |                                                 | 800   |     | 1200 | mVpp |

| DR                    | Data rate                                                                             |                                                 | 1     |     | 16   | Gbps |

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### **6.4 Thermal Information**

|                             |                                              | DS160 UP8       |      |

|-----------------------------|----------------------------------------------|-----------------|------|

|                             | THERMAL METRIC <sup>(1)</sup>                | NJX, 64<br>Pins | UNIT |

| $R_{	heta JA	ext{-High}}$ K | Junction-to-ambient thermal resistance       | 22.9            | °C/W |

| $R_{\theta JC(top)}$        | Junction-to-case (top) thermal resistance    | 9.6             | °C/W |

| $R_{\theta JB}$             | Junction-to-board thermal resistance         | 7.2             | °C/W |

| ΨЈТ                         | Junction-to-top characterization parameter   | 1.8             | °C/W |

| ΨЈВ                         | Junction-to-board characterization parameter | 7.1             | °C/W |

| $R_{\theta JC(bot)}$        | Junction-to-case (bottom) thermal resistance | 2.5             | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report.

## **6.5 DC Electrical Characteristics**

over operating free-air temperature and voltage range (unless otherwise noted)

|                         | PARAMETER                                                     | TEST CONDITIONS                                                                           | MIN  | TYP | MAX      | UNIT |

|-------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|-----|----------|------|

| Power                   |                                                               |                                                                                           |      |     | <b>'</b> |      |

| DOWED                   | A                                                             | GAIN1/0 = L3 (default)                                                                    |      | 107 |          | mW   |

| POWER <sub>CH</sub>     | Active power per channel                                      | GAIN1/0 = L0                                                                              |      | 99  |          | mW   |

| I <sub>ACTIVE-8CH</sub> | Device current consumption when all eight channels are active | GAIN1/0 = L3                                                                              |      | 260 | 360      | mA   |

| Іѕтву                   | Device current consumption in standby power mode              | All channels disabled (PD1,0 = H)                                                         |      | 30  | 45       | mA   |

| $V_{REG}$               | Internal regulator output                                     |                                                                                           |      | 2.5 |          | V    |

| Control IO (            | SDA, SCL, PD1, PD0, READ_EN_N, SEL                            | 1, SEL0 pins)                                                                             |      |     |          |      |

| V <sub>IH</sub>         | High level input voltage                                      | SDA, SCL, PD1, PD0, READ_EN_N, SEL1, SEL0 pins                                            | 2.1  |     |          | V    |

| V <sub>IL</sub>         | Low level input voltage                                       | SDA, SCL, PD1, PD0, READ_EN_N, SEL1, SEL0 pins                                            |      |     | 1.08     | V    |

| V <sub>OH</sub>         | High level output voltage                                     | $R_{pull-up}$ = 4.7 k $\Omega$ (SDA, SCL, ALL_DONE_N pins)                                | 2.1  |     |          | V    |

| V <sub>OL</sub>         | Low level output voltage                                      | I <sub>OL</sub> = -4 mA (SDA, SCL,<br>ALL_DONE_N pins)                                    |      |     | 0.4      | V    |

| I <sub>IH,SEL</sub>     | Input high leakage current for SEL pins                       | V <sub>Input</sub> = VCC for SEL1, SEL0 pins                                              |      |     | 80       | μΑ   |

| I <sub>IH</sub>         | Input high leakage current                                    | V <sub>Input</sub> = VCC, (SCL, SDA, PD1, PD0, READ_EN_N pins)                            |      |     | 10       | μΑ   |

| I <sub>IL</sub>         | Input low leakage current                                     | V <sub>Input</sub> = 0 V, (SCL, SDA, PD1, PD0, READ_EN_N, SEL1, SEL0 pins)                | -10  |     |          | μΑ   |

| I <sub>IH,FS</sub>      | Input high leakage current for fail safe input pins           | V <sub>Input</sub> = 3.6 V, VCC = 0 V, (SCL, SDA, , PD1, PD0, READ_EN_N, SEL1, SEL0 pins) |      |     | 200      | μΑ   |

| C <sub>IN-CTRL</sub>    | Input capacitance                                             | SDA, SCL, PD1, PD0, READ_EN_N, SEL1, SEL0 pins                                            |      | 1.5 |          | pF   |

| 4 Level IOs (           | (MODE, GAIN0, GAIN1, EQ0_0, EQ1_0,                            | EQ0_1, EQ1_1, RX_DET pins)                                                                |      |     |          |      |

| IH_4L                   | Input high leakage current, 4 level IOs                       | VIN = 2.5 V                                                                               |      |     | 10       | μΑ   |

| IL_4L                   | Input low leakage current for all 4 level IOs except MODE.    | VIN = GND                                                                                 | -10  |     |          | μΑ   |

| IIL_4L,MODE             | Input low leakage current for MODE pin                        | VIN = GND                                                                                 | -200 |     |          | μΑ   |

| Receiver                |                                                               |                                                                                           |      |     | '        |      |

| V <sub>RX-DC-CM</sub>   | RX DC common mode (CM) voltage                                | Device is in active or standby state                                                      |      | 2.5 |          | V    |

over operating free-air temperature and voltage range (unless otherwise noted)

|                                     | PARAMETER                                              | TEST CONDITIONS                                          | MIN | TYP  | MAX | UNIT |  |

|-------------------------------------|--------------------------------------------------------|----------------------------------------------------------|-----|------|-----|------|--|

| Z <sub>RX-DC</sub>                  | Rx DC single-ended impedance                           |                                                          |     | 50   |     | Ω    |  |

| Z <sub>RX-HIGH-IMP-</sub><br>DC-POS | DC input CM input impedance during Reset or power-down | Inputs are at CM voltage                                 | 20  |      |     | kΩ   |  |

| Transmitter                         | Transmitter                                            |                                                          |     |      |     |      |  |

| Z <sub>TX-DIFF-DC</sub>             | DC differential Tx impedance                           | Impedance of Tx during active signaling, VID,diff = 1Vpp |     | 100  |     | Ω    |  |

| V <sub>TX-DC-CM</sub>               | Tx DC common mode Voltage                              |                                                          |     | 0.75 |     | V    |  |

| I <sub>TX-SHORT</sub>               | Tx Short circuit current                               | Total current the Tx can supply when shorted to GND      |     |      | 90  | mA   |  |

# **6.6 High Speed Electrical Characteristics**

over operating free-air temperature and voltage range (unless otherwise noted)

|                                                                                                                                                                      | PARAMETER                                                          | TEST CONDITIONS                                                                                                                            | MIN | TYP | MAX | UNIT |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Receiver                                                                                                                                                             |                                                                    |                                                                                                                                            |     |     |     |      |

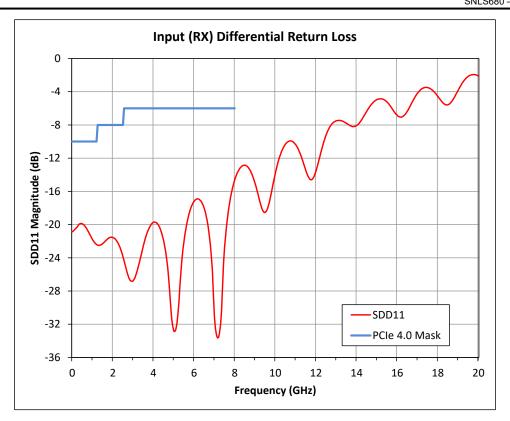

|                                                                                                                                                                      |                                                                    | 50 MHz to 1.25 GHz                                                                                                                         |     | -25 |     | dB   |

| DI                                                                                                                                                                   | Land 1995 and the Landson Land                                     | 1.25 GHz to 2.5 GHz                                                                                                                        |     | -22 |     | dB   |

| KL <sub>RX-DIFF</sub>                                                                                                                                                | Input differential return loss                                     | 2.5 GHz to 4.0 GHz                                                                                                                         |     | -21 |     | dB   |

| RL <sub>RX-DIFF</sub> KT <sub>RX</sub> Fransmitter  RL <sub>TX-DIFF</sub> KT <sub>TX</sub> Device Datap  FPLHD/PHLD  -TX-SKEW  FRJ-DATA  FRJ-INTRINSIC  JITTERTOTAL- |                                                                    | 4.0 GHz to 8.0 GHz                                                                                                                         |     | -16 |     | dB   |

| XT <sub>RX</sub>                                                                                                                                                     | Receive-side pair-to-pair isolation                                | Pair-to-pair isolation (SDD21) between two adjacent receiver pairs from 10 MHz to 8 GHz.                                                   |     | -47 |     | dB   |

| Transmitter                                                                                                                                                          |                                                                    |                                                                                                                                            |     |     |     |      |

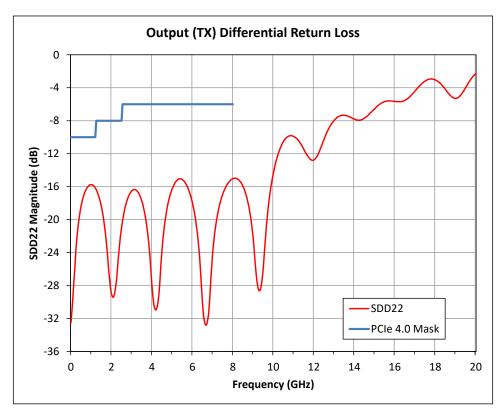

|                                                                                                                                                                      |                                                                    | 50 MHz to 1.25 GHz                                                                                                                         |     | -20 |     | dB   |

| DI                                                                                                                                                                   | Output differential return loss                                    | 1.25 GHz to 2.5 GHz                                                                                                                        |     | -18 |     | dB   |

| NLTX-DIFF                                                                                                                                                            | Output unierential return loss                                     | 2.5 GHz to 4.0 GHz                                                                                                                         |     | -18 |     | dB   |

| KT <sub>TX</sub>                                                                                                                                                     |                                                                    | 4.0 GHz to 8.0 GHz                                                                                                                         |     | -17 |     | dB   |

| XT <sub>TX</sub>                                                                                                                                                     | Transmit-side pair-to-pair isolation                               | Minimum pair-to-pair isolation<br>(SDD21) between two adjacent<br>transmitter pairs from 10 MHz to 8<br>GHz.                               |     | -48 |     | dB   |

| Device Datap                                                                                                                                                         | path                                                               |                                                                                                                                            |     |     |     |      |

| T <sub>PLHD/PHLD</sub>                                                                                                                                               | Input-to-output latency (propagation delay) through a data channel | For either low-to-high or high-to-low transition.                                                                                          |     | 90  | 120 | ps   |

| L <sub>TX-SKEW</sub>                                                                                                                                                 | Lane-to-lane output skew                                           | Between any two lanes within a single transmitter.                                                                                         | -20 |     | 20  | ps   |

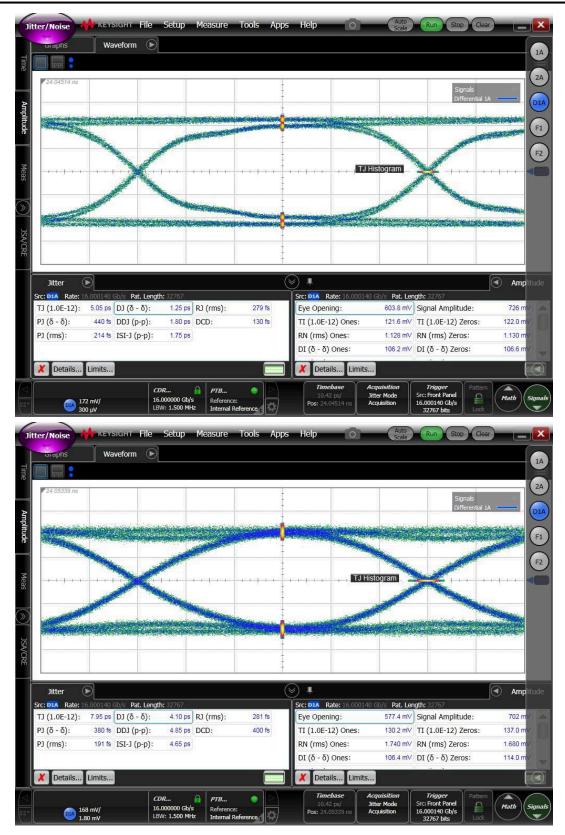

| T <sub>RJ-DATA</sub>                                                                                                                                                 | Additive random jitter with data                                   | Jitter through redriver minus the calibration trace. 16Gbps PRBS15. Minimal input/output channels. Minimum EQ. 800 mVpp-diff input swing.  |     | 70  |     | fs   |

| T <sub>RJ-INTRINSIC</sub>                                                                                                                                            | Intrinsic additive random jitter with clock                        | Jitter through redriver minus the calibration trace. 8 Ghz CK. Minimal input/output channels. Minimum EQ. 400 mVpp-diff input swing.       |     | 90  |     | fs   |

| JITTER <sub>TOTAL</sub> -<br>DATA                                                                                                                                    | Additive total jitter with data                                    | Jitter through redriver minus the calibration trace. 16 Gbps PRBS15. Minimal input/output channels. Minimum EQ. 800 mVpp-diff input swing. |     | 4   |     | ps   |

| JITTER <sub>TOTAL</sub> -<br>INTRINSIC                                                                                                                               | Intrinsic additive total jitter with clock                         | Jitter through redriver minus the calibration trace. 8 Ghz CK. Minimal input/output channels. Minimum EQ. 800 mVpp-diff input swing.       |     | 1   |     | ps   |

over operating free-air temperature and voltage range (unless otherwise noted)

|                       | PARAMETER                               | TEST CONDITIONS                                                            | MIN  | TYP  | MAX | UNIT |

|-----------------------|-----------------------------------------|----------------------------------------------------------------------------|------|------|-----|------|

|                       |                                         | Minimum EQ, GAIN1/0=L0                                                     |      | -4.2 |     | dB   |

|                       |                                         | Minimum EQ, GAIN1/0=L1                                                     |      | -1.8 |     | dB   |

| FLAT-GAIN             | Flat gain (DC and AC) input to output   | Minimum EQ, GAIN1/0=L2                                                     |      | 0.25 |     | dB   |

|                       |                                         | Minimum EQ, GAIN1/0=L3 (float, default)                                    |      | 2    |     | dB   |

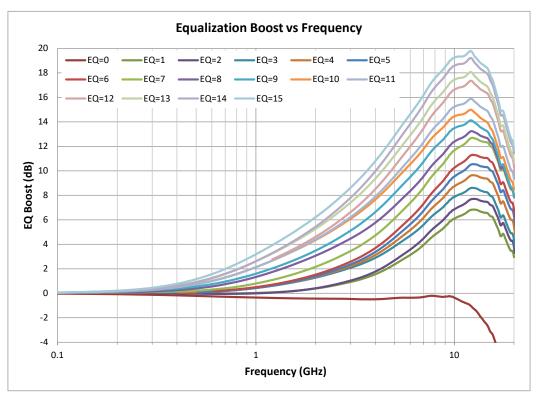

| EQ-MAX <sub>8G</sub>  | EQ boost at max setting (EQ INDEX = 15) | AC gain at 8 GHz relative to gain at 100 MHz. GAIN1/0=L3 (float, default). |      | 18.0 |     | dB   |

| DCGAIN <sub>VAR</sub> | DC gain variation                       | GAIN1/0 = L2, minimum EQ setting.<br>Max-Min.                              | -2.3 |      | 1.7 | dB   |

| EQGAIN <sub>VAR</sub> | EQ boost variation                      | At 8 Ghz. GAIN1/0 = L2, maximum EQ setting. Max-Min.                       | -3.3 |      | 3.7 | dB   |

| LIN <sub>DC</sub>     | Output DC linearity                     | GAIN1/0 = L3 (float, default). 128T pattern at 2.5 Gbps.                   |      | 1000 |     | mVpp |

| LIN <sub>AC</sub>     | Output AC linearity                     | GAIN1/0 = L3 (float, default). 1T pattern at 16 Gbps.                      |      | 750  |     | mVpp |

# **6.7 SMBUS/I2C Timing Characteristics**

over operating free-air temperature range (unless otherwise noted)

|                       | PARAMETER                                                                                         | TEST CONDITIONS                      | MIN | TYP | MAX | UNIT |

|-----------------------|---------------------------------------------------------------------------------------------------|--------------------------------------|-----|-----|-----|------|

| Slave Mode            | 9                                                                                                 |                                      |     |     |     |      |

| t <sub>SP</sub>       | Pulse width of spikes which must be suppressed by the input filter                                |                                      |     |     | 50  | ns   |

| t <sub>HD-STA</sub>   | Hold time (repeated) START condition.<br>After this period, the first clock pulse is<br>generated |                                      | 0.6 |     |     | μs   |

| t <sub>LOW</sub>      | LOW period of the SCL clock                                                                       |                                      | 1.3 |     |     | μs   |

| T <sub>HIGH</sub>     | HIGH period of the SCL clock                                                                      |                                      | 0.6 |     |     | μs   |

| t <sub>SU-STA</sub>   | Set-up time for a repeated START condition                                                        |                                      | 0.6 |     |     | μs   |

| t <sub>HD-DAT</sub>   | Data hold time                                                                                    |                                      | 0   |     |     | μs   |

| t <sub>SU-DAT</sub>   | Data setup time                                                                                   |                                      | 0.1 |     |     | μs   |

| t <sub>r</sub>        | Rise time of both SDA and SCL signals                                                             | Pull-up resistor = 4.7 kΩ, Cb = 10pF |     | 120 |     | ns   |

| t <sub>f</sub>        | Fall time of both SDA and SCL signals                                                             | Pull-up resistor = 4.7 kΩ, Cb = 10pF |     | 2   |     | ns   |

| t <sub>SU-STO</sub>   | Set-up time for STOP condition                                                                    |                                      | 0.6 |     |     | μs   |

| t <sub>BUF</sub>      | Bus free time between a STOP and START condition                                                  |                                      | 1.3 |     |     | μs   |

| t <sub>VD-DAT</sub>   | Data valid time                                                                                   |                                      |     |     | 0.9 | μs   |

| t <sub>VD-ACK</sub>   | Data valid acknowledge time                                                                       |                                      |     |     | 0.9 | μs   |

| C <sub>b</sub>        | capacitive load for each bus line                                                                 |                                      |     |     | 400 | pF   |

| Master Mo             | de                                                                                                |                                      |     |     |     |      |

| f <sub>SCL-M</sub>    | SCL clock frequency                                                                               | MODE = L1 (Master Mode)              |     | 303 |     | kHz  |

| t <sub>LOW-M</sub>    | SCL low period                                                                                    |                                      |     | 1.9 |     | μs   |

| t <sub>HIGH-M</sub>   | SCL high period                                                                                   |                                      |     | 1.4 |     | μs   |

| t <sub>SU-STA-M</sub> | Set-up time for a repeated START condition                                                        |                                      |     | 2   |     | μs   |

| t <sub>HD-STA-M</sub> | Hold time (repeated) START condition.<br>After this period, the first clock pulse is<br>generated |                                      |     | 1.5 |     | μs   |

| t <sub>SU-DAT-M</sub> | Data setup time                                                                                   |                                      |     | 1.4 |     | μs   |

over operating free-air temperature range (unless otherwise noted)

|                       | PARAMETER                             | TEST CONDITIONS                                                                                                                                                                                                                                                                                         | MIN | TYP | MAX | UNIT |  |

|-----------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|--|

| t <sub>HD-DAT-M</sub> | Data hold time                        |                                                                                                                                                                                                                                                                                                         |     | 0.5 |     |      |  |

| t <sub>R-M</sub>      | Rise time of both SDA and SCL signals | Pull-up resistor = 4.7 kΩ, Cb = 10pF                                                                                                                                                                                                                                                                    |     | 120 |     | ns   |  |

| t <sub>F-M</sub>      | Fall time of both SDA and SCL signals | Pull-up resistor = 4.7 kΩ, Cb = 10pF                                                                                                                                                                                                                                                                    |     | 2   |     | ns   |  |

| t <sub>SU-STO-M</sub> | Stop condition setup time             |                                                                                                                                                                                                                                                                                                         |     | 1.5 |     | μs   |  |

| EEPROM Ti             | ming                                  |                                                                                                                                                                                                                                                                                                         |     |     | '   |      |  |

| T <sub>EEPROM</sub>   | EEPROM configuration load time        | Time to assert ALL_DONE_N after READ_EN_N has been asserted. Single device reading its configuration from an EEPROM with common channel configuration with individual channel settings. This time scales with the number of devices reading from the same EEPROM. Does not include power-on reset time. |     | 7.5 |     | ms   |  |

| T <sub>POR</sub>      | Time to first SMBus access            | Power supply stable after initial ramp. Includes initial power-on reset time.                                                                                                                                                                                                                           | 50  |     |     | ms   |  |

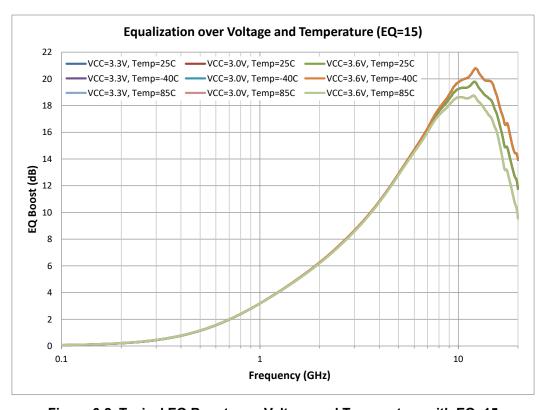

# **6.8 Typical Characteristics**

Figure 6-1. Typical EQ Boost vs Frequency

Figure 6-2. Typical EQ Boost over Voltage and Temperature with EQ=15

Figure 6-3. Typical RX Differential Return Loss

Figure 6-4. Typical TX Differential Return Loss

Figure 6-5. Typical Jitter Characteristics - Top: 16Gbps PRBS15 Input to the Device, Bottom: Output of the Device.

## 7 Detailed Description

### 7.1 Overview

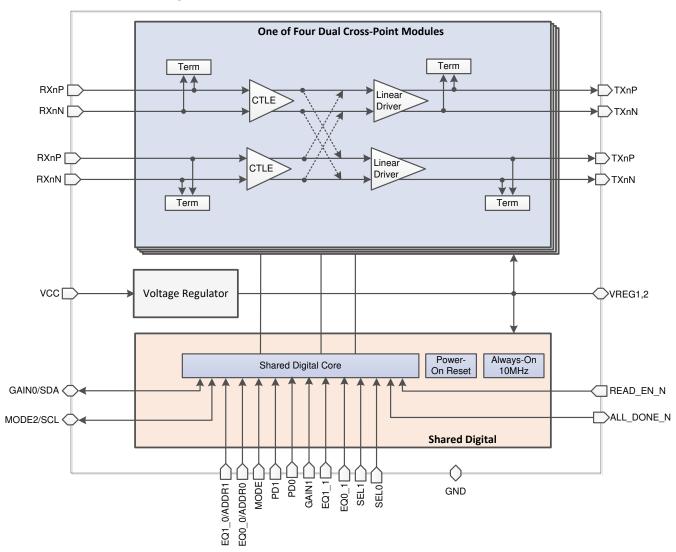

The DS160UP822 is an eight-channel multi-rate linear repeater with integrated signal conditioning. The device provides quad 2x2 crosspoint mux functionality selectable by pin control or SMBus/I<sup>2</sup>C. The device's signal channels operate independently from one another. Each channel includes a continuous-time linear equalizer (CTLE) and a linear output driver, which together compensate for a lossy transmission channel between the source transmitter and the final receiver. The linearity of the data path is specifically designed to preserve any transmit equalization while keeping receiver equalization effective.

The DS160UP822 can be configured three different ways:

**Pin Mode** – device control configuration is done solely by strap pins. Pin mode is expected to be good enough for many system implementation needs.

**SMBus/I<sup>2</sup>C Master Mode** - device control configuration is read from external EEPROM. When the device has finished reading from the EEPROM successfully, it will drive the ALL\_DONE\_N pin LOW. SMBus/I<sup>2</sup>C slave operation is available in this mode before, during or after EEPROM reading. Note during EEPROM reading if the external SMBus/I<sup>2</sup>C master wants to access device registers it must support arbitration. The mode is prefferred when software implementation is not desired.

**SMBus/I<sup>2</sup>C Slave Mode** - provides most flexibility. Requires a SMBus/I<sup>2</sup>C master device to configure the device through writing to its slave address.

### 7.2 Functional Block Diagram

### 7.3 Feature Description

### 7.3.1 Linear Equalization

The DS160UP822 receivers feature a continuous-time linear equalizer (CTLE) that applies high-frequency boost and low-frequency attenuation to help equalize the frequency-dependent insertion loss effects of the passive channel. Table 7-1 shows available equalization boost through EQ control pins (EQ1\_0 and EQ0\_0 for channels 0-3 and EQ1\_1 and EQ0\_1 for channels 4-7), when in Pin Control mode (MODE = L0).

Table 7-1. Equalization Control Settings

|          | EQUALIZATION SETTII                | TYPICAL EQ BOOST (dB)             |         |         |  |  |

|----------|------------------------------------|-----------------------------------|---------|---------|--|--|

| EQ INDEX | EQ1_0 (Ch 0-3) / EQ1_1 (Ch<br>4-7) | EQ0_0 (Ch0-3) / EQ0_1 (Ch<br>4-7) | @ 4 GHz | @ 8 GHz |  |  |

| 0        | L0                                 | LO                                | 0.0     | -0.2    |  |  |

| 1        | L0                                 | L1                                | 1.5     | 4.5     |  |  |

| 2        | L0                                 | L2                                | 2.0     | 5.5     |  |  |

| 3        | LO                                 | L3                                | 2.5     | 6.5     |  |  |

| 4        | L1                                 | LO                                | 2.7     | 7.0     |  |  |

| 5        | L1                                 | L1                                | 3.0     | 8.0     |  |  |

| 6        | L1                                 | L2                                | 4.0     | 9.0     |  |  |

**Table 7-1. Equalization Control Settings (continued)**

|          | EQUALIZATION SETTI                 | TYPICAL EQ BOOST (dB)             |         |         |  |  |

|----------|------------------------------------|-----------------------------------|---------|---------|--|--|

| EQ INDEX | EQ1_0 (Ch 0-3) / EQ1_1 (Ch<br>4-7) | EQ0_0 (Ch0-3) / EQ0_1 (Ch<br>4-7) | @ 4 GHz | @ 8 GHz |  |  |

| 7        | L1                                 | L3                                | 5.0     | 10.0    |  |  |

| 8        | L2                                 | LO                                | 6.0     | 11.0    |  |  |

| 9        | L2                                 | L1                                | 7.0     | 12.0    |  |  |

| 10       | L2                                 | L2                                | 7.5     | 13.0    |  |  |

| 11       | L2                                 | L3                                | 8.0     | 13.5    |  |  |

| 12       | L3                                 | LO                                | 8.5     | 15.0    |  |  |

| 13       | L3                                 | L1                                | 9.5     | 16.5    |  |  |

| 14       | L3                                 | L2                                | 10.0    | 17.0    |  |  |

| 15       | L3                                 | L3                                | 11.0    | 18.0    |  |  |

The equalization of the device can also be set by writing to SMBus/I<sup>2</sup>C registers in slave or master mode. Refer to the *DS160UP822 Programming Guide* (SNLU279) for details.

#### 7.3.2 Flat Gain

The GAIN1 and GAIN0 pins can be used to set the overall datapath flat gain (DC and AC) of the DS160UP822 when the device is in Pin Mode. The pin GAIN0 sets the flat gain for channels 0-3 and GAIN1 sets the same for channels 4-7. The default recommendation for most systems will be GAIN1,0 = L3 (float).

The flat gain and equalization of the DS160UP822 must be set such that the output signal swing at DC and high frequency does not exceed the DC and AC linearity ranges of the devices, respectively.

#### 7.3.3 Cross Point

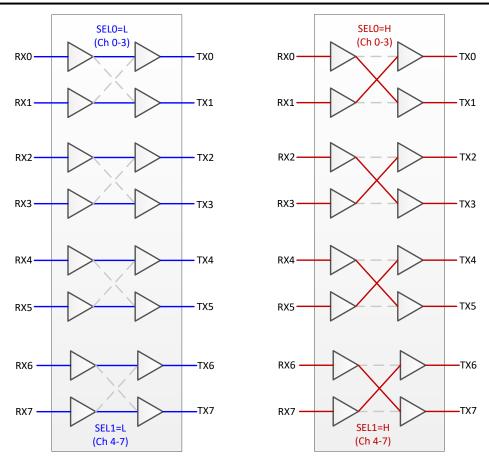

The DS160UP822 provides quad 2x2 cross-point function. Using pin SEL1, SEL0 pins the 8 channel signal paths can be configured as staright connection or quad cross connections. SEL1 pin impacts channel 0-3 and SEL1 configures channels 4-7.

Figure 7-1. DS160UP822 Signal Flow Diagram for Cross-Point Mux Operation

#### 7.4 Device Functional Modes

#### 7.4.1 Active Mode

The device is in normal operation. In this mode PD0/PD1 pins are driven low in a system.

#### 7.4.2 Standby Mode

The device is in standby mode invoked by PD1,0 = H. In this mode, the device is in standby mode conserving power.

### 7.5 Programming

### 7.5.1 Control and Configuration Interface

#### 7.5.1.1 Pin Mode

The DS160UP822 can be fully configured through pin-strap pins. In this mode the device uses 2-level and 4-level pins for device control and signal integrity optimum settings. The *Section 5* section defines the control pins.

#### 7.5.1.1.1 Four-Level Control Inputs

The DS160UP822 has 4-level inputs pins (EQ0\_0, EQ1\_0, EQ0\_1, EQ1\_1, GAIN0, GAIN1, and MODE) that are used to control the configuration of the device. These 4-level inputs use a resistor divider to help set the 4 valid levels and provide a wider range of control settings. External resistors must be of 10% tolerance or better. The pins are sampled at power-up only. The MODE pin can be exercised at device power up or in normal operation mode.

**Table 7-2. 4-Level Control Pin Settings**

| LEVEL | SETTING     |

|-------|-------------|

| LO    | 1 kΩ to GND |

| Table 7-2. 4-Level Control | Pin Settings ( | (continued) |

|----------------------------|----------------|-------------|

|----------------------------|----------------|-------------|

| LEVEL | SETTING      |

|-------|--------------|

| L1    | 13 kΩ to GND |

| L2    | 59 kΩ to GND |

| L3    | F (Float)    |

### 7.5.1.2 SMBUS/I<sup>2</sup>C Register Control Interface

If MODE = L2 (SMBus /  $I^2C$  slave control mode), the DS160UP822 is configured for best signal integrity through a standard  $I^2C$  or SMBus interface that may operate up to 400 kHz. The slave address of the device is determined by the pin strap settings on the ADDR1 and ADDR0 pins. Note slave addresses to access channel 0-3 and Channels 4-7 is different. Channel bank 4-7 has address which is Channel bank 0-3 address +1. The sixteen possible slave addresses (8-bit) for each channel banks of the the device are shown in Table 7-3. In SMBus/ $I^2C$  modes the SCL, SDA pins must be pulled up to a 3.3 V supply with a pull-up resistor. The value of the resistor depends on total bus capacitance. 4.7 k $\Omega$  is a good first approximation for a bus capacitance of 50 pF.

Refer to the DS160UP822 Programming Guide (SNLU279) for register map details.

Table 7-3. SMBUS/I2C Slave Address Settings

| Table 1-3. Swibbonizo Stave Address Settings |       |                                     |                                  |  |  |  |  |  |  |  |  |

|----------------------------------------------|-------|-------------------------------------|----------------------------------|--|--|--|--|--|--|--|--|

| ADDR1                                        | ADDR0 | 7-bit Slave Address Channels<br>0-3 | 7-bit Slave Address Channels 4-7 |  |  |  |  |  |  |  |  |

| L0                                           | LO    | 0x18                                | 0x19                             |  |  |  |  |  |  |  |  |

| L0                                           | L1    | 0x1A                                | 0x1B                             |  |  |  |  |  |  |  |  |

| L0                                           | L2    | 0x1C                                | 0x1D                             |  |  |  |  |  |  |  |  |

| LO                                           | L3    | 0x1E                                | 0x1F                             |  |  |  |  |  |  |  |  |

| L1                                           | LO    | 0x20                                | 0x21                             |  |  |  |  |  |  |  |  |

| L1                                           | L1    | 0x22                                | 0x23                             |  |  |  |  |  |  |  |  |

| L1                                           | L2    | 0x24                                | 0x25                             |  |  |  |  |  |  |  |  |

| L1                                           | L3    | 0x26                                | 0x27                             |  |  |  |  |  |  |  |  |

| L2                                           | LO    | 0x28                                | 0x29                             |  |  |  |  |  |  |  |  |

| L2                                           | L1    | 0x2A                                | 0x2B                             |  |  |  |  |  |  |  |  |

| L2                                           | L2    | 0x2C                                | 0x2D                             |  |  |  |  |  |  |  |  |

| L2                                           | L3    | 0x2E                                | 0x2F                             |  |  |  |  |  |  |  |  |

| L3                                           | LO    | 0x30                                | 0x31                             |  |  |  |  |  |  |  |  |

| L3                                           | L1    | 0x32                                | 0x33                             |  |  |  |  |  |  |  |  |

| L3                                           | L2    | 0x34                                | 0x35                             |  |  |  |  |  |  |  |  |

| L3                                           | L3    | 0x36                                | 0x37                             |  |  |  |  |  |  |  |  |

# 7.5.1.3 SMBus/I <sup>2</sup> C Master Mode Configuration (EEPROM Self Load)

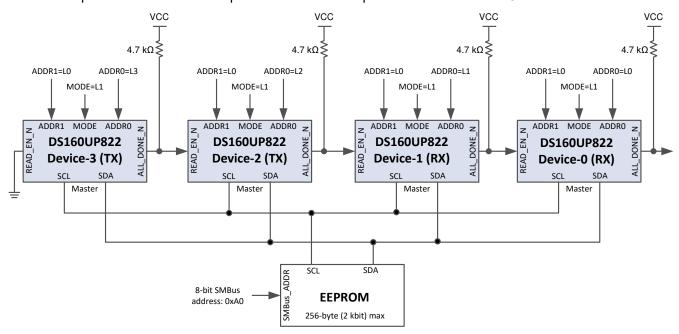

The DS160UP822 can also be configured by reading from EEPROM. To enter into this mode MODE pin must be set to L1. The EEPROM load operation only happens once after device's initial power-up. If the device is configured for SMBus master mode, it will remain in the SMBus IDLE state until the READ\_EN\_N pin is asserted to LOW. After the READ\_EN\_N pin is driven LOW, the device becomes an SMBus master and attempts to self-configure by reading device settings stored in an external EEPROM (SMBus 8-bit address 0xA0). When the device has finished reading from the EEPROM successfully, it will drive the ALL\_DONE\_N pin LOW. SMBus/I²C slave operation is available in this mode before, during or after EEPROM reading. Note during EEPROM reading if the external SMBus/I²C master wants to access the device registers it must support arbitration. Refer to the Understanding EEPROM Programming for PCI-Express 4.0 Redrivers (SNLA342) application report for more information.

When designing a system for using the external EEPROM, the user must follow these specific guidelines:

EEPROM size of 2 kb (256 × 8-bit) is recommended.

- Set MODE = L1, configure for SMBus master mode

- The external EEPROM device address byte must be 0xA0 and capable of 400 kHz operation at 3.3 V supply

- In SMBus/I<sup>2</sup>C modes the SCL, SDA pins must be pulled up to a 3.3 V supply with a pull-up resistor. The value of the resistor depends on total bus capacitance. 4.7 kΩ is a good first approximation for a bus capacitance of 10 pF.

Figure 7-2 shows a use case with four DS160UP822 to implement a configuration, but the user can cascade any number of DS160UP822 devices in a similar way. Tie first device's READ\_EN\_N pin low to automatically initiate EEPROM read at power up. Alternately the READ\_EN\_N pin of the first device can also be controlled by a microcontroller to initiate the EEPROM read manually. Leave the final device's ALL\_DONE\_N pin floating, or connect the pin to a microcontroller input to monitor the completion of the final EEPROM read.

Figure 7-2. Daisy Chain Four DS160UP822 Devices to Read from Single EEPROM

# 8 Application and Implementation

#### Note

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 8.1 Application Information

The DS160UP822 is a high-speed linear repeater which extends the reach of differential channels impaired by loss from transmission media like PCBs and cables. It can be deployed in a variety of different systems. The following sections outline typical applications and their associated design considerations.

### 8.2 Typical Applications

The DS160UP822 is a protocol and interface agnostic linear redriver that can be used in wide range of interfaces including:

- Ultra Path Interconnect (UPI) 1.0/2.0

- DisplayPort 2.0

- SAS

- SATA

- XFI

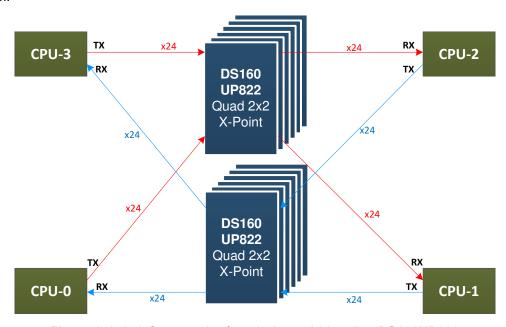

The DS160UP822 is a protocol agnostic linear redriver. Figure 8-1 shows how eight DS160UP822 devices can be used to implement 2x2 crosspoint for x24 bus width to connect four CPUs to provide flexible interconnectivity between them.

Figure 8-1. 2x2 Cross point for x24 bus width using DS160UP822

### 8.2.1 UPI 2x2 Cross Point Mux for x24 Lane Configuration

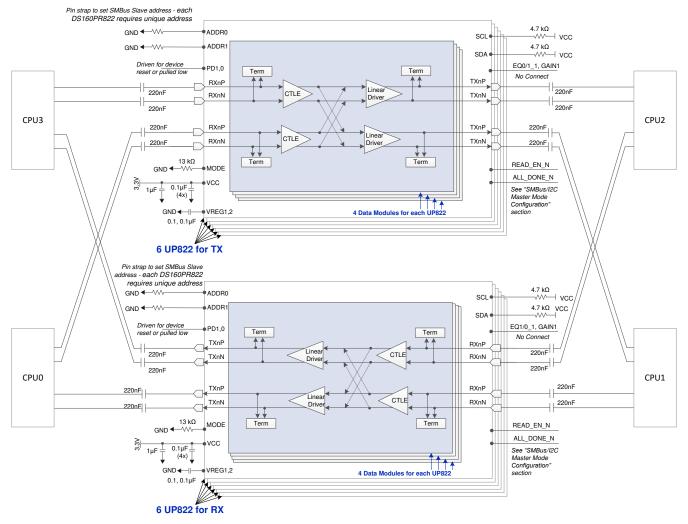

The DS160UP822 can be used in server or motherboard applications as cross point mux to create a flexible CPU to CPU connectivity. The section outlines detailed procedure and design requirement for a typical UPI x24 lane Mux configuration. However, the design recommendations can be used in any lane configuration.

### 8.2.1.1 Design Requirements

As with any high-speed design, there are many factors which influence the overall performance. The following list indicates critical areas for consideration during design.

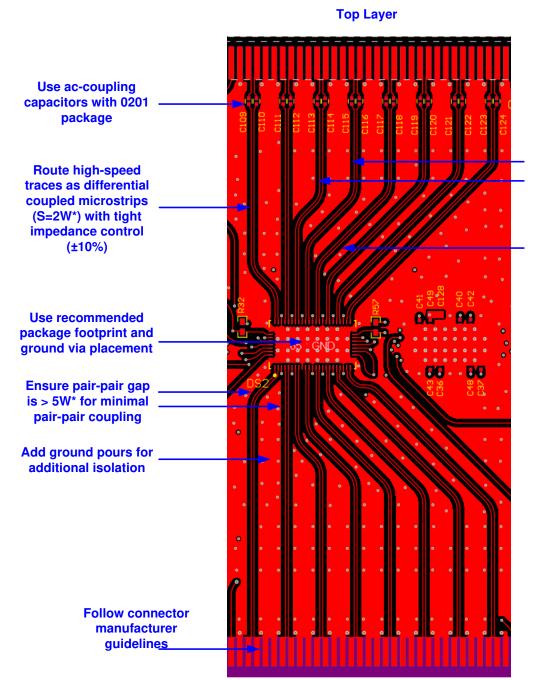

- Use 85  $\Omega$  impedance traces . Length matching on the P and N traces should be done on the single-end segments of the differential pair.

- Use a uniform trace width and trace spacing for differential pairs.

- Place AC-coupling capacitors near to the receiver end of each channel segment to minimize reflections.

- AC-coupling capacitors of 220 nF are recommended, set the maximum body size to 0402, and add a cutout void on the GND plane below the landing pad of the capacitor to reduce parasitic capacitance to GND.

- · Back-drill connector vias and signal vias to minimize stub length.

- Use reference plane vias to ensure a low inductance path for the return current.

### 8.2.1.2 Detailed Design Procedure

For operation in UPI 2.0 links, the DS160UP822 is designed with linear datapth to pass the Tx preset signaling (by root complex and end point) onto the Rx (of root complex and end point) to train and optimize the equalization settings. The linear redriver device helps extend the PCB trace reach distance by boosting the attenuated signals with its equalization, which allows the user to recover the signal by the downstream Rx more easily. The device must be placed in between the Tx and Rx (of root complex and end point) such a way that both RX and TX signal swing stays within the linearity range of the device. Adjustments to the device EQ setting should be performed based on the channel loss to optimize the eye opening in the Rx partner. The available EQ gain settings are provided in Table 7-1. For most systems the default DC gain setting GAIN = floating would be sufficient.

The DS160UP822 can be optimized for a given system utilizing its three configuration modes - Pin Mode, SMBus/I<sup>2</sup>C Master Mode and SMBus/I<sup>2</sup>C Slave Mode. In SMBus/I<sup>2</sup>C modes the SCL, SDA pins must be pulled up to a 3.3 V supply with a pull-up resistor. The value of the resistor depends on total bus capacitance. 4.7 k $\Omega$  is a good first approximation for a bus capacitance of 10 pF.

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

w.ti.com SNLS680 – DECEMBER 2020

Figure 8-2 shows a simplified schematic for UPI 2x2 cross-point mux for x24 lane configuration in SMBus/I<sup>2</sup>C Master Mode.

Figure 8-2. Simplified Schematic for UPI 2x2 cross-point mux for x24Lane Configuration in SMBus/I<sup>2</sup>C Master Mode

#### 8.2.1.3 Application Curves

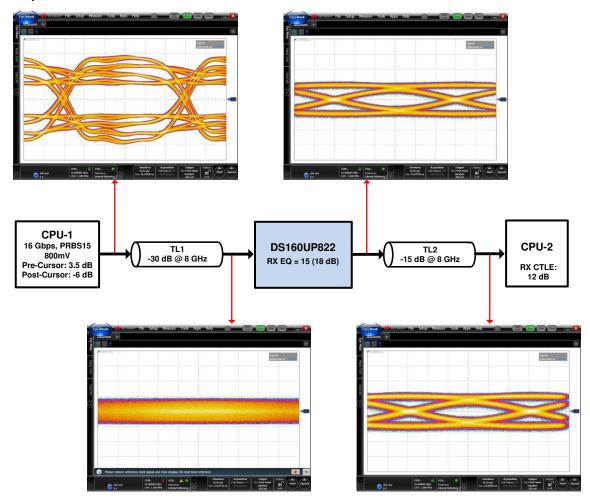

The DS160UP822 is a linear redriver that can be used to extend channel reach of a UPI link. Normally, PCIe-compliant TX and RX are equipt with signal-conditioning functions and can handle channel losses of up to 28 dB at 8 GHz. With the DS160UP822 in the link, the total channel loss between two CPUs can be up to 42 dB at 8 GHz.

Figure 8-3 shows an electric link that models a single channel of a UPI link and eye diagrams measured at different locations along the link. The source that models a UPI TX sends a 16 Gbps PRBS-15 signal with P7 presets. After a transmission channel with -30 dB at 8 GHz insertion loss, the eye diagram is fully closed. The DS160UP822 with its CTLE set to the maximum (18 dB boost) together with the source TX equalization compensates for the losses of the pre-channel (TL1) and opens the eye at the output of the device.

The post-channel (TL2) losses mandate the use of UPI RX equalization functions such as CTLE and DFE that are normally available in receivers.

Figure 8-3. UPI 2.0 Link Reach Extension Using DS160UP822

# 9 Power Supply Recommendations

Follow these general guidelines when designing the power supply:

- 1. The power supply should be designed to provide the operating conditions outlined in the recommended operating conditions section in terms of DC voltage, AC noise, and start-up ramp time.