LDC5071-Q1 SNOSDI7 - DECEMBER 2023

# LDC5071-Q1 Inductive Position Sensor Front-End With Sin/Cos Interface

### 1 Features

- AEC-Q100 qualified with the following results:

- Device temperature grade 0: –40°C to +160°C ambient operating temperature

- High resolution and accuracy of ≤ 1 degree at rotational speeds up to 480,000 RPM

- Differential signal paths with sine and cosine outputs supporting a wide dynamic input range

- Integrated analog front-end IC for contact-less, inductive position sensors for absolute rotary position from 0° to 360°

- Supports operation in harsh environments; immune to stray magnetic fields, dirt, and contamination

- No magnets required

- Input supply operating modes: 5 V and 3.3 V

- Operating current: 22 mA (maximum)

- Integrated LC oscillator in the 2.4-MHz to 5-MHz band to excite the inductive sensor coil

- Differential output drivers with high-voltage protection and large capacitive load capability

- Automatic and manual gain control to maximize dynamic range of output drivers

- Built-in sensor and supply diagnostics

- Reverse voltage and overvoltage protection on input supply and output pins from -15 V to 30 V

- For enhanced functional safety and diagnostics, see LDC5072-Q1

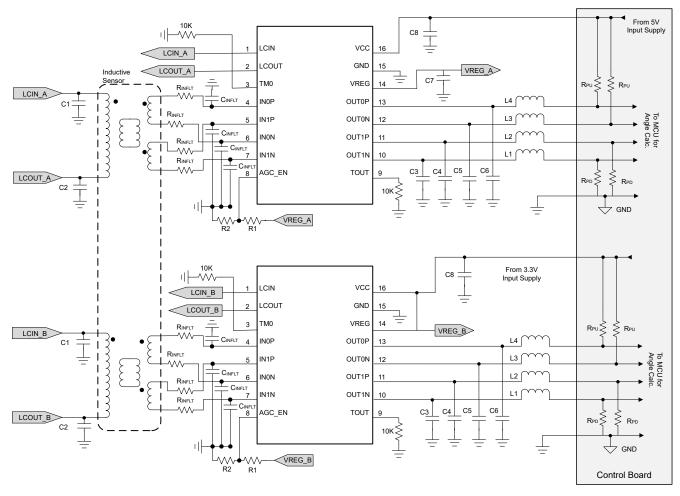

- Supports redundant mode

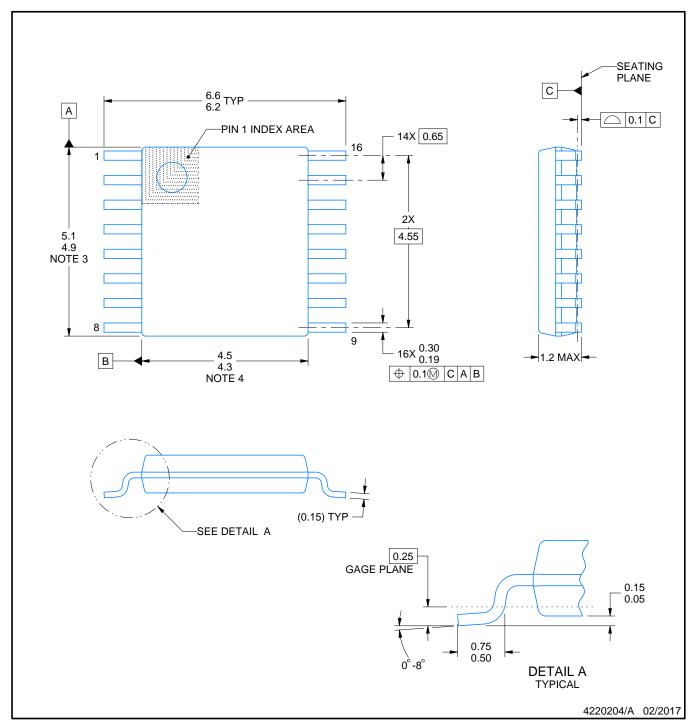

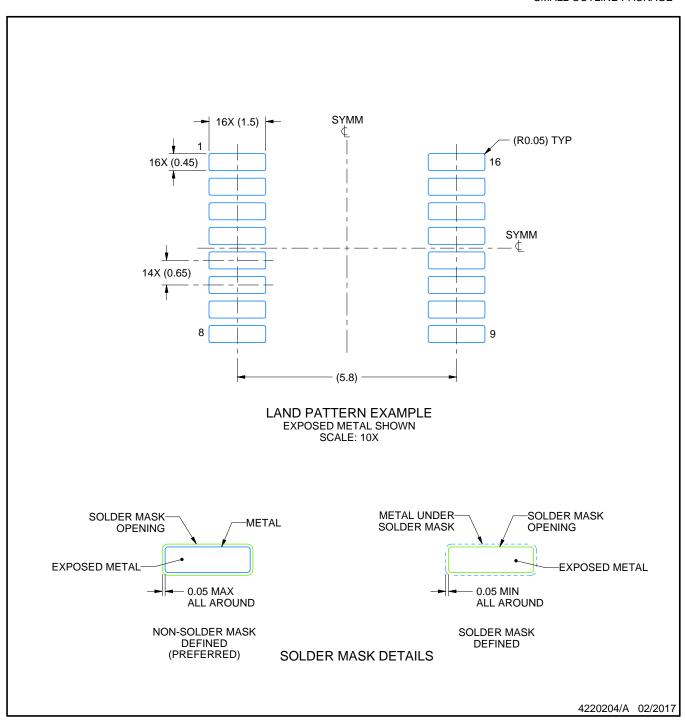

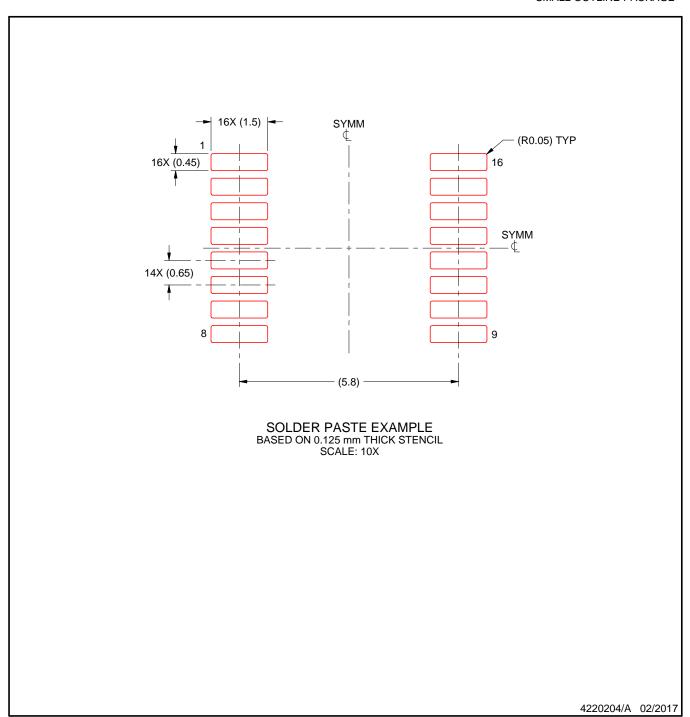

- Package: TSSOP-16 (5.00 mm x 4.40 mm)

# 2 Applications

- EV/HEV traction motor inverters

- Electric power steering

- Brake boost motors

- Shifter systems

- Integrated starter generators

- Pedal position

- Valves and actuators

- Robots

- e-Bikes

# 3 Description

LDC5071-Q1 is a high-speed and accurate inductive sensor used for measuring absolute linear and rotary position in automotive and industrial applications. The device is designed to interface to three inductive sensing coils that are typically on the printed circuit board. One of the coils is connected to the exciter circuit of the LDC5071-Q1 and acts as a transmitter, and the other two secondary coils are used as receivers. The transmitter coil induces a voltage in the secondary coils, which is a function of the conductive target above the sensor coils. The demodulated signals which are produced during LDC5071-Q1 operation are then provided through the differential signal path with sine and cosine outputs.

The LDC5071-Q1 has multiple supply options, 5-V or 3.3-V, to suit different design options and can be connected to a microcontroller to calculate the rotary angle. The manual and automatic gain control (AGC) of the LDC5071-Q1 can be used to control and maximize the dynamic range of the outputs.

The device offers robust protection features to support and monitor signals and overall device operation for a seamless systems protection. The LDC5071-Q1 supports overvoltage, reverse battery and current protection on short to high voltage on output pins. In addition, the device provides immunity against motor noise and can filter out-of-band low- and highfrequency noise.

#### **Package Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup> |

|-------------|------------------------|-----------------------------|

| LDC5071-Q1  | PW (TSSOP, 16)         | 5.00 mm × 4.40 mm           |

- For all available packages, see the orderable addendum at the end of the data sheet.

- The package size (length × width) is a nominal value and includes pins, where applicable.

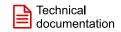

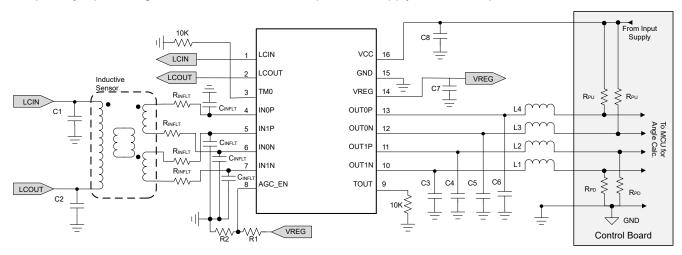

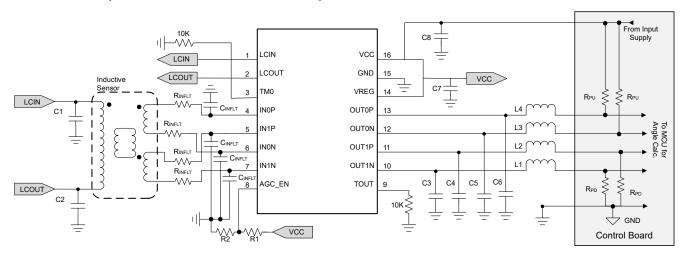

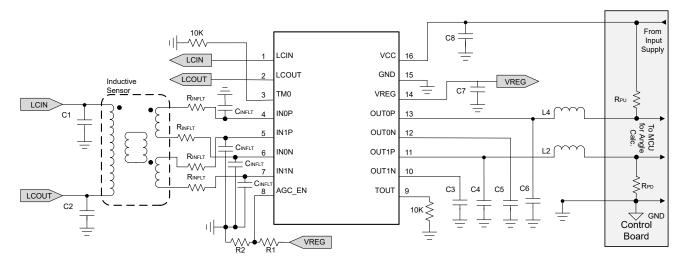

**LDC5071-Q1 Typical Application Diagram**

# **Table of Contents**

| 1 Features                           | 1  | 6.3 Feature Description                              | 13              |

|--------------------------------------|----|------------------------------------------------------|-----------------|

| 2 Applications                       | 1  | 6.4 Device Functional Modes                          | 20              |

| 3 Description                        |    | 7 Application and Implementation                     | 23              |

| 4 Pin Configuration and Functions    | 4  | 7.1 Application Information                          | <mark>23</mark> |

| 5 Specifications                     | 5  | 7.2 Typical Applications                             | <mark>23</mark> |

| 5.1 Absolute Maximum Ratings         | 5  | 7.3 Power Supply Recommendations                     |                 |

| 5.2 ESD Ratings                      | 5  | 7.4 Layout                                           |                 |

| 5.3 Recommended Operating Conditions |    | 8 Device and Documentation Support                   | 32              |

| 5.4 Thermal Information              |    | 8.1 Receiving Notification of Documentation Updates. | 32              |

| 5.5 Electrical Characteristics       | 6  | 8.2 Support Resources                                | 32              |

| 5.6 Diagnostics                      | 9  | 8.3 Trademarks                                       | 32              |

| 5.7 Switching Characteristics        | 10 | 8.4 Electrostatic Discharge Caution                  | 32              |

| 5.8 Typical Characteristics          |    | 8.5 Glossary                                         |                 |

| 6 Detailed Description               |    | 9 Revision History                                   |                 |

| 6.1 Overview                         | 12 | 10 Mechanical, Packaging, and Orderable              |                 |

| 6.2 Functional Block Diagram         |    | Information                                          | 32              |

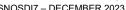

# **4 Pin Configuration and Functions**

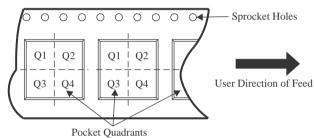

Figure 4-1. PW Package 16-Pin TSSOP Top View

**Table 4-1. Pin Functions**

| PIN |        | TYPE <sup>(1)</sup> | DESCRIPTION                                          |  |  |

|-----|--------|---------------------|------------------------------------------------------|--|--|

| NO. | NAME   |                     | DESCRIP HON                                          |  |  |

| 1   | LCIN   | I/O                 | LC oscillator input                                  |  |  |

| 2   | LCOUT  | I/O                 | LC oscillator output                                 |  |  |

| 3   | ТМО    | I/O                 | Test Mode Input                                      |  |  |

| 4   | IN0P   | I                   | Input channel 0 positive                             |  |  |

| 5   | IN1P   | I                   | Input channel 1 positive                             |  |  |

| 6   | IN0N   | I                   | Input channel 0 negative                             |  |  |

| 7   | IN1N   | I                   | Input channel 1 negative                             |  |  |

| 8   | AGC_EN | I                   | Automatic Gain Control Enable and Fixed Gain Setting |  |  |

| 9   | TOUT   | I/O                 | Test Mode Output                                     |  |  |

| 10  | OUT1N  | 0                   | Output channel 1 negative                            |  |  |

| 11  | OUT1P  | 0                   | Output channel 1 positive                            |  |  |

| 12  | OUT0N  | 0                   | Output channel 0 negative                            |  |  |

| 13  | OUT0P  | 0                   | Output channel 0 positive                            |  |  |

| 14  | VREG   | I/O                 | Regulated 3.3-V Supply output                        |  |  |

| 15  | GND    | G                   | Ground                                               |  |  |

| 16  | VCC    | Р                   | Input Voltage Supply                                 |  |  |

(1) I = input, O = output, I/O = input and output, G = ground, P = power

# **5 Specifications**

# 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                           |                                | MIN  | MAX | UNIT |

|-------------------------------------------|--------------------------------|------|-----|------|

| VCC                                       | Input Supply voltage           | -15  | 30  |      |

| OUT0P, OUT0N, OUT1P, OUT1N                | Output pin voltage             | -15  | 30  |      |

| VREG                                      | Regulator output voltage       | -0.3 | 5.5 | V    |

| GND                                       | Ground Pin voltage             | -0.3 | 0.3 | V    |

| LCOUT, LCIN                               | LC Oscillator pin voltage      | -0.3 | 5.5 |      |

| AGC_EN, TM0, TOUT, IN0P, IN0N, IN1P, IN1N | All other pin voltage          | -0.3 | 5.5 |      |

| T <sub>A</sub>                            | Operating free air temperature | -40  | 160 |      |

| T <sub>J</sub>                            | Operating junction temperature | -40  | 170 | °C   |

| T <sub>stg</sub>                          | Storage temperature range      | -65  | 150 |      |

<sup>(1)</sup> Operation outside the *Absolute Maximum Ratings* may cause permanent device damage. *Absolute Maximum Ratings* do not imply functional operation of the device at these or any other conditions beyond those listed under *Recommended Operating Conditions*. If used outside the *Recommended Operating Conditions* but within the *Absolute Maximum Ratings*, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

# 5.2 ESD Ratings

|                    |                         |                                              |                                                              | VALUE | UNIT |

|--------------------|-------------------------|----------------------------------------------|--------------------------------------------------------------|-------|------|

|                    | Electrostatic discharge | Human-body model (HBM), per AEC Q100-002     | All pins                                                     | ±2000 |      |

| V <sub>(ESD)</sub> |                         | HBM ESD Classification Level 2               | OUT0x, OUT1x, IN0x, IN1x,<br>LCIN, LCOUT, VCC to GND<br>only | ±4000 | V    |

|                    |                         | Charged-device model (CDM), per AEC          | All pins                                                     | ±500  |      |

|                    |                         | Q100-011<br>CDM ESD Classification Level C4B | Corner pins (1, 8, 9, 16)                                    | ±750  |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

### 5.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                    |                                                                                | MIN  | NOM | MAX | UNIT |

|--------------------|--------------------------------------------------------------------------------|------|-----|-----|------|

| V <sub>CC_50</sub> | V <sub>CC</sub> input voltage (5V input mode)                                  | 4.5  | 5   | 5.6 | V    |

| V <sub>CC_33</sub> | V <sub>CC</sub> and V <sub>REG</sub> input voltage (3.3V input mode)           | 3.15 | 3.3 | 3.6 | V    |

| IQ                 | During start-up and in operation (excluding LC oscillator load and OUTxx load) |      |     | 22  | mA   |

#### 5.4 Thermal Information

|                               |                                              | LDC5071-Q1 |      |

|-------------------------------|----------------------------------------------|------------|------|

| THERMAL METRIC <sup>(1)</sup> |                                              | PW (TSSOP) | UNIT |

|                               |                                              | 16 PINS    |      |

| $R_{\theta JA}$               | Junction-to-ambient thermal resistance       | 93.2       | °C/W |

| R <sub>0JC(top)</sub>         | Junction-to-case (top) thermal resistance    | 24.1       | °C/W |

| $R_{\theta JB}$               | Junction-to-board thermal resistance         | 39.7       | °C/W |

| ΨЈТ                           | Junction-to-top characterization parameter   | 0.9        | °C/W |

| ΨЈВ                           | Junction-to-board characterization parameter | 39.1       | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

# **5.5 Electrical Characteristics**

over operating free-air temperature range (unless otherwise noted)

over recommended V<sub>cc</sub> range (unless otherwise noted)

|                           | PARAMETER                                                                                                                                                                                                                                     | TEST CONDITIONS                                                                                                    | MIN   | TYP | MAX   | UNIT   |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------|-----|-------|--------|

| Input Supply              |                                                                                                                                                                                                                                               |                                                                                                                    |       |     |       |        |

| VCC <sub>Ramp</sub>       | Allowed VCC ramp up rate                                                                                                                                                                                                                      |                                                                                                                    | 0.17  |     | 100e6 | V/s    |

| PEXT_VCC                  | External VCC decoupling capacitor range                                                                                                                                                                                                       |                                                                                                                    | 80    | 100 |       | nF     |

| nternal LDO Regula        | ator VREG                                                                                                                                                                                                                                     |                                                                                                                    |       |     |       |        |

| / <sub>VREG</sub>         | Internal LDO output voltage                                                                                                                                                                                                                   |                                                                                                                    | 3.15  | 3.3 | 3.6   |        |

| POR_VREG_UTH              | VREG power-on upper threshold                                                                                                                                                                                                                 |                                                                                                                    |       |     | 3.15  | V      |

| V <sub>POR_VREG_LTH</sub> | VREG power-on lower threshold                                                                                                                                                                                                                 |                                                                                                                    | 2.91  |     |       |        |

| LOAD_REG_EXT              | Maximum external load on VREG (used for setting voltage on AGC_EN pin externally) (Information Only)                                                                                                                                          |                                                                                                                    |       |     | 1     | mA     |

| LIM_VREG                  | VREG current limit                                                                                                                                                                                                                            |                                                                                                                    | 40    |     | 90    |        |

| C <sub>EXT_VREG</sub>     | External VREG decoupling capacitor                                                                                                                                                                                                            |                                                                                                                    | 180   |     | 2000  | nF     |

| Signal Path               |                                                                                                                                                                                                                                               |                                                                                                                    |       |     | •     |        |

| Err <sub>inL</sub>        | Integral Non-Linearity error <sup>(3)</sup> of the signal path transfer function for each channel measured as:  Maximum % deviation of output from a best fit line through measured outputs when input is swept from minium to maximum value. | For static inputs; VCC=5V;<br>-3.5V ≤( V <sub>OUTXP</sub> -V <sub>OUTXN</sub> ) ≤<br>3.5V                          |       | 1%  | 2.5   | %      |

|                           | Propagation Delay through receive stage at room temperature.                                                                                                                                                                                  | Measured as zero crossing of diffrential input (INx) to                                                            | 3.3   |     | 4.6   | μs     |

| PROP_CH                   | Propagation Delay through receive stage across temperature (-40°C to 160°C).                                                                                                                                                                  | zero crossing of differential output (OUTx)  C <sub>OUT</sub> on each pin = 10nF                                   | 3     |     | 5     |        |

| PROP_DIFF                 | Propagation Delay difference between two channels across temperature                                                                                                                                                                          | Measured as delay<br>between the zero crossings<br>of the diffrential outputs.                                     |       |     | 500   | ns     |

| V <sub>OUT_SE</sub>       | Difference between single ended outputs calculated at V <sub>OUT0P</sub> -V <sub>OUT1P</sub>                                                                                                                                                  | Measured for static inputs only for VCC=5V; -1.75V $\leq$ ( $V_{OUT0P}$ - $V_{OUT1P}$ ) $\leq$ 1.75V               |       | 50  | 65    | mV     |

| V <sub>OUT_DIFF</sub>     | Difference between differential output calculated as (V <sub>OUT0P</sub> -V <sub>OUT0N</sub> ) - (V <sub>OUT1P</sub> -V <sub>OUT1N</sub> ) at room temperature                                                                                | Measured for static inputs                                                                                         |       |     | 100   |        |

| Vout diff to              | Deviation of V <sub>OUT_DIFF</sub> at -40°C from room temperature                                                                                                                                                                             | only for VCC=5V; -3.5V $\leq$ (V <sub>OUTxP</sub> -V <sub>OUTxN</sub> ) $\leq$ 3.5V                                |       |     | 20    | mV     |

|                           | Deviation of V <sub>OUT_DIFF</sub> at 160°C from room temperature                                                                                                                                                                             |                                                                                                                    |       |     | 38    |        |

| G                         | Gain mismatch between Channel<br>1 and Channel 2 signal                                                                                                                                                                                       | Fixed Gain Mode;<br>VCC=3.3V 4.55%VREG <<br>$V_{AGC\_EN}$ < 95.45%VREG<br>-40°C $\leq$ T <sub>A</sub> $\leq$ 160°C | -0.4  |     | 0.4   | %      |

| G <sub>MIS_SIG_PATH</sub> | path calculated as (Gain <sub>out1</sub> -Gain <sub>out0</sub> )/<br>((Gain <sub>out1</sub> +Gain <sub>out0</sub> )*0.5) <sup>(2)</sup>                                                                                                       | Fixed Gain Mode; VCC=5.0V; 4.55%VREG < $V_{AGC\_EN}$ < 95.45%VREG<br>-40°C $\leq$ T <sub>A</sub> $\leq$ 160°C      | -0.35 |     | 0.55  | 76     |

| d. "                      | Input referred offset for IN0 channel <sup>(2)</sup> measured with input shorted and exciter coil connected                                                                                                                                   | VCC=3.3V, 5.0V;<br>Fixed Gain Mode;                                                                                |       | 150 | 170   | μV     |

| √ <sub>in_off</sub>       | Input referred offset for IN1 channel <sup>(2)</sup> measured with input shorted and exciter coil connected                                                                                                                                   | 30%VREG < V <sub>AGC_EN</sub> <<br>95.45%VREG<br>-40°C ≤ T <sub>A</sub> ≤ 160°C                                    |       | 50  | 100   | μV     |

| NSIG_PATH_SE              | Input referred noise for the complete signal path for single ended output for each channel <sup>(2)</sup>                                                                                                                                     |                                                                                                                    |       | 25  |       | nV/√H  |

| OSIG_PATH_DIFF            | Input referred noise for the complete signal path for differential output for each channel <sup>(2)</sup>                                                                                                                                     |                                                                                                                    |       | 36  |       | nV/√H: |

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

over operating free-air temperature range (unless otherwise noted) over recommended V<sub>cc</sub> range (unless otherwise noted)

|                                     | PARAMETER                                                                                                          | TEST CONDITIONS                                                                                           | MIN  | TYP  | MAX  | UNIT  |  |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------|------|------|-------|--|

|                                     | LC oscillator differential amplitude                                                                               | 3.15V ≤ V <sub>VREG</sub> ≤ 3.6;<br>T <sub>A</sub> =25°C                                                  | 70   | 75.8 | 81.5 |       |  |

|                                     | LC Oscillator unierential amplitude                                                                                | 3.15V ≤ V <sub>VREG</sub> ≤ 3.6; -40°C<br>< T <sub>A</sub> < 160°C                                        | 64   |      | 87   |       |  |

| $V_{AMP\_LC}$                       |                                                                                                                    | V <sub>POR_VREG_LTH</sub> ≤ V <sub>VREG</sub> ≤ V <sub>POR_VREG_UTH</sub> ; T <sub>A</sub> =25°C          | 69.5 |      | 82.5 | %Vreg |  |

|                                     | V <sub>VREG</sub> is below regulation voltage                                                                      | V <sub>POR_VREG_LTH</sub> ≤ V <sub>VREG</sub> ≤ V <sub>POR_VREG_UTH;</sub> -40°C < T <sub>A</sub> < 160°C | 63   |      | 88   |       |  |

|                                     | PO 11 11/1 10 11/1                                                                                                 | 3.15V ≤ V <sub>VREG</sub> ≤ 3.6;<br>T <sub>A</sub> =25°C                                                  | 47   | 50   | 52.5 |       |  |

|                                     | DC operating point for LC oscillator                                                                               | 3.15V ≤ V <sub>VREG</sub> ≤ 3.6; -40°C<br>< T <sub>A</sub> < 160°C                                        | 43.5 |      | 56.5 |       |  |

| V <sub>DC_LC</sub>                  |                                                                                                                    | V <sub>POR_VREG_LTH</sub> ≤ V <sub>VREG</sub> ≤ V <sub>POR_VREG_UTH</sub> ; T <sub>A</sub> =25°C          | 47.5 |      | 53   | %VREG |  |

|                                     | DC operating point for LC oscillator when V <sub>VREG</sub> is below regulation voltage                            | V <sub>POR_VREG_LTH</sub> ≤ V <sub>VREG</sub> ≤ V <sub>POR_VREG_UTH;</sub> -40°C < T <sub>A</sub> < 160°C | 42.5 |      | 57.5 |       |  |

| I <sub>LIM_LC</sub>                 | RMS value of LC oscillator current limit                                                                           |                                                                                                           | 13   |      | 30   | mA    |  |

| f <sub>OSC_LC</sub> (2)             | LC oscillator resonant frequency                                                                                   |                                                                                                           | 2.4  |      | 5    | MHz   |  |

| THD <sub>LC</sub> <sup>(2)</sup>    | Total harmonic distortion of oscillator output (V <sub>LCIN</sub> -V <sub>LCOUT</sub> )                            |                                                                                                           |      |      | -30  | dB    |  |

| R <sub>PU_LCx</sub>                 | Internal pull up resistance to VREG on LCIN and LCOUT pins                                                         |                                                                                                           | 220  |      | 330  | ΚΩ    |  |

| R <sub>PD_LCx</sub>                 | Internal pull down resistance to GND on LCIN and LCOUT pins                                                        |                                                                                                           | 220  |      | 330  | ΚΩ    |  |

| Rp                                  | Allowed range for equivalent parallel resistance of LC oscillator coil                                             |                                                                                                           | 167  |      | 5000 | Ω     |  |

| L                                   | Allowed range of inductance of excitation coil resonator                                                           |                                                                                                           |      | 5    |      | μΗ    |  |

| C <sub>LC1</sub> , C <sub>LC2</sub> | Allowed range for capacitors for excitation coil                                                                   |                                                                                                           | 100  | 370  |      | pF    |  |

| C <sub>MIS</sub>                    | Allowed capacitor mismatch (between $C_{LC1}$ and $C_{LC2}$ )                                                      |                                                                                                           | -10  |      | 10   | %     |  |

| Receiver                            |                                                                                                                    |                                                                                                           |      |      |      |       |  |

| V <sub>DIFF_REC</sub>               | Allowed range for differential input signal amplitude                                                              | In fixed gain mode, voltage on AGC_EN pin adjusted to set gain to avoid clipping                          | 5    |      | 400  | mVp-p |  |

| V <sub>COM_REC</sub>                | Common mode voltage forced on input signals                                                                        |                                                                                                           | 45   | 50   | 55   | %VREG |  |

| f <sub>LF_BPF_REC</sub>             | Bandpass filter lower cutoff frequency <sup>(1)</sup>                                                              |                                                                                                           | 430  | 600  | 760  | kHz   |  |

| f <sub>UF_BPF_REC</sub>             | Bandpass filter upper cutoff frequency <sup>(1)</sup>                                                              |                                                                                                           | 12   | 20   | 26   | MHz   |  |

| f <sub>LPF_REC</sub>                | Low pass filter (after demodulation)                                                                               |                                                                                                           | 65   | 100  | 125  | kHz   |  |

| $V_{N\_DIFF\_REC}$                  | Amplitude of differential noise on input rejected by receive path for fundamental frequency between 10KHz to 20KHz | Differential input signal >20mVpp, VCC=5V, Sqaure wave noise signal ramp time = 8µs                       |      |      | 1    | Van   |  |

| V <sub>N_COM_REC</sub>              | Amplitude of common mode noise on input rejected by receive path for fundamental frequency between 10KHz to 20KHz  | Differential input signal >20mVpp, VCC=5V, Sqaure wave noise signal ramp time = 8µs                       |      |      | 1    | Vpp   |  |

| R <sub>PU_INxN</sub>                | Internal pull up resistor to VREG on each of the INxN pins                                                         |                                                                                                           | 0.8  | 1    | 1.2  | ΜΩ    |  |

| R <sub>PD_INxP</sub>                | Internal pull down resistor to GND on each of the INxP pins                                                        |                                                                                                           | 0.8  | 1    | 1.2  | IVISZ |  |

| L <sub>REC</sub>                    | Typical Receiver coil inductance (Information only)                                                                |                                                                                                           |      | 0.2  |      | μH    |  |

| R <sub>REC</sub>                    | Typical Receiver coil resistance (Information only)                                                                |                                                                                                           |      | 6    |      | Ω     |  |

Product Folder Links: LDC5071-Q1

over operating free-air temperature range (unless otherwise noted) over recommended  $V_{cc}$  range (unless otherwise noted)

|                            | PARAMETER                                                                                                                                         | TEST CONDITIONS                                                       | MIN  | TYP  | MAX      | UNIT     |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------|------|----------|----------|

| Automatic Gain Conti       | rol                                                                                                                                               |                                                                       | •    |      | <u> </u> |          |

| V <sub>AGC_EN_AUTO</sub>   | Voltage on AGC_EN pin to set AGC in auto mode                                                                                                     |                                                                       |      |      | 2        | %VREG    |

| V <sub>AGC_EN_MANUAL</sub> | Voltage range on AGC_EN pin to manually set different AGC gains                                                                                   |                                                                       | 4.55 |      | 95.45    | 70 V NEG |

| R <sub>AGC_EN_MIN</sub>    | Minimum value of required external resistor on AGC_EN to ground to enable AGC mode (Information Only)                                             |                                                                       | 1    |      |          | ΚΩ       |

| R <sub>AGC_EN_MAX</sub>    | Maximum value of required external resistor on AGC_EN to ground to enable AGC mode (Information Only)                                             |                                                                       |      |      | 16.3     | ΚΩ       |

| R <sub>PU_AGC_EN</sub>     | Internal pull up resistor to VREG on AGC_EN                                                                                                       |                                                                       | 0.8  | 1    | 1.2      | ΜΩ       |

|                            |                                                                                                                                                   | V <sub>CC</sub> = V <sub>CC_33</sub> ; T <sub>A</sub> =25°C           | 54.5 | 59.5 | 64.5     |          |

| AGC_Target                 | Value of √(OUT0 <sup>2</sup> + OUT1 <sup>2</sup> )                                                                                                | V <sub>CC</sub> = V <sub>CC_33</sub> ;<br>-40°C≤T <sub>A</sub> ≤160°C | 53.5 |      | 65       | %VCC     |

| AGC_larget                 | get   Value of V(OUT02 + OUT12)                                                                                                                   | $V_{CC} = V_{CC_{50}}; T_A = 25^{\circ}C$                             | 55   | 60   | 65       | 70 V C C |

|                            |                                                                                                                                                   | $V_{CC} = V_{CC_{50}};$<br>-40°C $\leq T_A \leq 160$ °C               | 54   |      | 66       |          |

|                            |                                                                                                                                                   | V <sub>CC</sub> = V <sub>CC_33</sub> ; T <sub>A</sub> =25°C           | 75.5 | 78.9 | 83       |          |

| AGC_FH                     | Automatic gain control - fast regulation                                                                                                          | V <sub>CC</sub> = V <sub>CC_33</sub> ;<br>-40°C≤T <sub>A</sub> ≤160°C | 75   |      | 83.5     | %VCC     |

| AGC_FH                     | region high threshold.                                                                                                                            | V <sub>CC</sub> = V <sub>CC_50</sub> ; T <sub>A</sub> =25°C           | 77   | 80.1 | 84       |          |

|                            |                                                                                                                                                   | V <sub>CC</sub> = V <sub>CC_50</sub> ;<br>-40°C≤T <sub>A</sub> ≤160°C | 76   |      | 85       |          |

|                            |                                                                                                                                                   | V <sub>CC</sub> = V <sub>CC_33</sub> ; T <sub>A</sub> =25°C           | 66   | 68.8 | 73.5     |          |

| ACC 811                    | Automatic gain control - slow regulation                                                                                                          | V <sub>CC</sub> = V <sub>CC_33</sub> ;<br>-40°C≤T <sub>A</sub> ≤160°C | 65.5 |      | 74       | %VCC     |

| AGC_SH                     | region high threshold.                                                                                                                            | V <sub>CC</sub> = V <sub>CC_50</sub> ; T <sub>A</sub> =25°C           | 67   | 70   | 74       | %VCC     |

|                            |                                                                                                                                                   | V <sub>CC</sub> = V <sub>CC_50</sub> ;<br>-40°C≤T <sub>A</sub> ≤160°C | 66.5 |      | 74.8     |          |

|                            | Automatic gain control - slow regulation region low threshold.                                                                                    | V <sub>CC</sub> = V <sub>CC_33</sub> ; T <sub>A</sub> =25°C           | 45   | 48.6 | 52       |          |

| AGC_SL                     |                                                                                                                                                   | V <sub>CC</sub> = V <sub>CC_33</sub> ;<br>-40°C≤T <sub>A</sub> ≤160°C | 44.5 |      | 52.5     | %VCC     |

| AGC_SL                     |                                                                                                                                                   | $V_{CC} = V_{CC_{50}}; T_A = 25^{\circ}C$                             | 46.5 | 49.8 | 53       | /0000    |

|                            |                                                                                                                                                   | V <sub>CC</sub> = V <sub>CC_50</sub> ;<br>-40°C≤T <sub>A</sub> ≤160°C | 46   |      | 53.5     |          |

|                            |                                                                                                                                                   | $V_{CC} = V_{CC_33}; T_A = 25^{\circ}C$                               | 34.5 | 38.3 | 42.5     |          |

| AGC_FL                     | Automatic gain control - fast regulation                                                                                                          | V <sub>CC</sub> = V <sub>CC_33</sub> ;<br>-40°C≤T <sub>A</sub> ≤160°C | 34   |      | 43       | %VCC     |

| 7.00_i E                   | region low threshold.                                                                                                                             | $V_{CC} = V_{CC_{50}}; T_A = 25^{\circ}C$                             | 36.7 | 39.9 | 42.7     | 70 V O O |

|                            |                                                                                                                                                   | $V_{CC} = V_{CC_{50}};$<br>-40°C $\leq T_A \leq 160$ °C               | 36   |      | 43.5     |          |

| Output Stage               |                                                                                                                                                   |                                                                       |      |      |          |          |

| V <sub>OUT</sub>           | Output signal range                                                                                                                               | OUTxy pins single-ended measurement                                   | 7    |      | 93       | %VCC     |

| V <sub>REF_OUT</sub>       | Output reference voltage                                                                                                                          |                                                                       | 48   | 50   | 52       |          |

| I <sub>ILIM_OUT</sub>      | Current limit source or sink on output pins                                                                                                       |                                                                       | 3    |      | 20       | mA       |

| l <sub>OUT</sub>           | Load current on output pins                                                                                                                       |                                                                       |      |      | 1.5      |          |

| R <sub>PD_OUT</sub>        | Allowed range for resistor on OUT pins to GND for output pins during a detected fault condition. Refer to V <sub>OUT_FLT_LOW</sub> for error band |                                                                       | 4    |      | 20       | kΩ       |

| R <sub>PU_OUT</sub>        | Allowed range for resistor on OUT pins to VCC for output pin during a detected fault condition. Refer to V <sub>OUT_FLT_HIGH</sub> for error band |                                                                       | 4    |      | 20       | 1,32     |

over operating free-air temperature range (unless otherwise noted) over recommended V<sub>cc</sub> range (unless otherwise noted)

|                          | PARAMETER                                                                                            | TEST CONDITIONS                                                                                                                                                | MIN | TYP | MAX | UNIT   |

|--------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|--------|

| C <sub>OUT</sub>         | Capacitors on OUT pins (Information Only)                                                            | R <sub>PD_OUT</sub> = R <sub>PU_OUT</sub> = 10kΩ, 8kHz rotation speed                                                                                          | 1   |     | 8   | nF     |

| C <sub>OUT</sub>         | Capacitors on OUT pins (Information Only)                                                            | Maximum rotational speed limited                                                                                                                               | 8   |     | 200 | IIF    |

| I <sub>SCB_ОUТ</sub>     | Short circuit current into OUT pins when shorted to voltage higher than VCC                          | V <sub>OUT</sub> >8V; VCC=5V                                                                                                                                   |     |     | 5   | mA     |

|                          | Leakage current in to each OUT pin when VCC is lost; Outputs used in differential                    | VCC pin open; R <sub>PU_OUT</sub><br>=5K on each OUTx pin;<br>VCC=3.3V                                                                                         |     |     | 12  |        |

| OUT_NOVCC_DIFF           | mode.                                                                                                | VCC pin open; R <sub>PU_OUT</sub><br>=5K on each OUTx pin;<br>VCC=5.0V                                                                                         |     |     | 25  |        |

|                          | Leakage current in to each OUT pin when VCC is lost; Outputs used in single-ended                    | VCC pin open; R <sub>PU_OUT</sub><br>=5K on each OUTxP pins;<br>VCC=3.3V                                                                                       |     |     | 17  | μА     |

| OUT_NOVCC_SE             | mode.                                                                                                | VCC pin open; R <sub>PU_OUT</sub> =5K on each OUTxP̄ pins; VCC=5.0V                                                                                            |     |     | 35  |        |

|                          | Leakage current out of each OUT pin when GND is lost; Outputs used in differential mode.             | GND pin open; R <sub>PD_OUT</sub> = 5K on each OUTx pin; VCC=3.3V                                                                                              |     |     | 30  |        |

| OUT_NOGND_DIFF           |                                                                                                      | GND open; R <sub>PD_OUT</sub> = 5K on each OUTx pin; VCC=5.0V                                                                                                  |     |     | 50  |        |

|                          | Leakage current out of each OUT pin                                                                  | GND pin open; R <sub>PD_OUT</sub> = 5K on each OUTxP pin; VCC=3.3V                                                                                             |     |     | 35  | μА     |

| OUT_NOGND_SE             | when GND is lost; Outputs used in single-<br>ended mode.                                             | GND pin open; R <sub>PD_OUT</sub> = 5K on each OUTxP pin; VCC=5.0V                                                                                             |     |     | 60  |        |

| V <sub>OUT_FLT_LOW</sub> | Voltage on OUT pins in fault state with external pulldown resistors to ground on OUT pins            | $4K\Omega \leq R_{PD~OUT} \leq 20K\Omega$ on each OUTx pin; $VCC=3.3V;5.0V;$ $-40^{\circ}C \leq TA \leq 160^{\circ}C$                                          |     |     | 4   | %VCC   |

| .,                       | Voltage on OUT pins in fault state with                                                              | $4K\Omega \le R_{PU\_OUT} \le 5K\Omega$ on each OUTx pin; VCC=3.3V; $-40^{\circ}C \le T_A \le 160^{\circ}C$                                                    | 96  |     |     | 0/1/00 |

| Vout_flt_high            | external pullup resistors to VCC on OUT pins                                                         | $4K\Omega \le R_{PU\_OUT} \le 10K\Omega$ on each OUTx pin; VCC=5.0V; $-40^{\circ}C \le T_A \le 160^{\circ}C$                                                   | 96  |     |     | %VCC   |

|                          | Leakge current on OUT pins in fault state                                                            | $5K\Omega \le R_{PU\_OUT} \le 20K\Omega$ on each OUTx pin; VCC=3.3V; $-40^{\circ}C \le T_A \le 160^{\circ}C$                                                   |     |     | 30  |        |

| l <sub>out_lk_pu</sub>   | with external pullup resistors to VCC on OUT pins when V <sub>OUTx</sub> > V <sub>OUT_FLT_HIGH</sub> | $\begin{array}{l} 10K\Omega \leq R_{PU\ OUT} \leq 20K\Omega \\ \text{on each OUTx pin;} \\ VCC=5.0V; \\ -40^{\circ}C \leq T_{A} \leq 160^{\circ}C \end{array}$ |     |     | 20  | μА     |

- 1) Guaranteed by design

- (2) Not tested in production

- (3) This INL error is not same as INL error in calculated angle in the external MCU

# 5.6 Diagnostics

over operating free-air temperature range (unless otherwise noted)

|                           | PARAMETER                                                              | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|---------------------------|------------------------------------------------------------------------|-----------------|-----|-----|-----|------|

| I <sub>PD_INXN_BIST</sub> | Pull down current to GND during start-up on INxN pins for sensor BIST  |                 | 150 | 200 | 270 | ^    |

| I <sub>PU_INXP_BIST</sub> | Pull up current from VREG during start-up on INxP pins for sensor BIST |                 | 150 | 200 | 270 | μΑ   |

over operating free-air temperature range (unless otherwise noted)

|                                | PARAMETER                                                                                                                  | TEST CONDITIONS  | MIN  | TYP | MAX  | UNIT     |  |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------|------|-----|------|----------|--|

| V <sub>TH_FALL_INXP_BIST</sub> | Falling threshold of window comparator for sensor BIST on INxP pins                                                        |                  | 22.7 | 25  | 30   | %VREG    |  |

| V <sub>TH_FALL_INXN_BIST</sub> | Falling threshold of window comparator for sensor BIST on INxN pins                                                        |                  | 70   | 75  | 77.3 | 70 VREG  |  |

| I <sub>PU_AGC_EN_BIST</sub>    | Pull up current from VREG during start-up<br>BIST on AGC_EN pin to check short to<br>ground                                |                  | 200  | 250 | 350  | μΑ       |  |

| C <sub>LOSS_VREG</sub>         | VREG external capacitor loss check.<br>Capacitor values below this will trigger a<br>fault.                                | 5V VCC mode only | 1    |     |      | nF       |  |

| V <sub>OVUTH_VREG</sub> (1)    | VREG overvoltage upper threshold                                                                                           |                  |      |     | 4.2  | V        |  |

| V <sub>OVLTH_VREG</sub>        | VREG overvoltage lower threshold                                                                                           |                  | 3.6  |     |      | V        |  |

| V <sub>POR_VREG_uth</sub>      | VREG power-on upper threshold                                                                                              |                  |      |     | 3.15 | V        |  |

| V <sub>POR_VREG_lth</sub>      | VREG power-on lower threshold                                                                                              |                  | 2.91 |     |      | v        |  |

| I <sub>PU_LCx_BIST</sub>       | Pull up current from VREG during start-up on LCOUT and LCIN pins for sensor BIST                                           |                  | 1.7  | 2.6 | 4.0  | mA       |  |

| I <sub>PD_LCx_BIST</sub>       | Pull down current to GND during start-up on LCOUT and LCIN pins for sensor BIST                                            |                  | 1.7  | 2.6 | 4.0  | MA       |  |

| VAL <sub>AGC_INP_OOR_</sub> L  | AGC quantized step out of 256 (min to max gain) in auto gain mode to signal FAULT when input signal is very low amplitude  |                  | 251  |     |      | AGC code |  |

| VAL <sub>AGC_INP_OOR_</sub> H  | AGC quantized step out of 256 (min to max gain) in auto gain mode to signal FAULT when input signal is very high amplitude |                  |      |     | 4    | AGC code |  |

| V <sub>UV_DVDD</sub>           | Internal Digital Supply undervoltage check.                                                                                |                  | 1.2  |     | 1.3  | V        |  |

| V <sub>TOGGLE_AGC_EN</sub>     | Checks if the comparator on AGC_EN toggles after AGC_EN status determination                                               |                  | 50   |     | 200  | mV       |  |

<sup>(1)</sup> Device will continue normal operation until the over-voltage threshold on VREG triggered

# **5.7 Switching Characteristics**

over operating free-air temperature range (unless otherwise noted)

|                            | PARAMETER                                                                             | TEST CONDITIONS                     | MIN | TYP | MAX | UNIT |

|----------------------------|---------------------------------------------------------------------------------------|-------------------------------------|-----|-----|-----|------|

| t <sub>VREG_OV_DT</sub>    | Deglitch time for VREG over voltage detection                                         |                                     | 180 | 200 | 220 | μs   |

| t <sub>AGC_EN_DT</sub>     | Deglitch time for AGC_EN pin for AGC mode detection                                   |                                     | 2.7 | 3   | 3.3 | μs   |

| t <sub>AGC_EN_TGL_DT</sub> | Deglitch time on AGC_EN pin toggle fault after power up into normal state             |                                     | 450 | 500 | 550 | μs   |

| t <sub>AGC_CMP_DT</sub>    | Deglitch time to detect AGC fast/slow amplitude regulation threshold has been crossed |                                     | 180 | 200 | 220 | ns   |

| t <sub>AGC_VAL_DT</sub>    | Deglitch time for AGC OOR range faults                                                |                                     | 180 | 200 | 220 | μs   |

| t <sub>FLT_RECOV</sub>     | Fault recovery time once device tranistions from FAULT to DIAGNOSTIC state            | C <sub>EXT_VREG</sub> =680nF, 2.2μF | 12  |     | 16  | ms   |

| t <sub>PWR_ON</sub>        | From VREG power on until OUTx pins are released from HI-Z state.                      | C <sub>EXT_VREG</sub> =680nF, 2.2µF | 10  |     | 14  | ms   |

Product Folder Links: LDC5071-Q1

## 5.8 Typical Characteristics

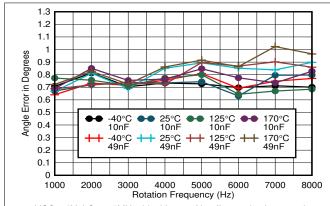

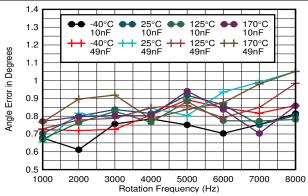

VCC = 5V,  $\rm LC_{freq} = 5MHz, \, Ideal \, Inputs, \, No \, offset \, and \, gain \, correction \, Signal \, path \, delay \, compensated$

Figure 5-1. Angle Error VCC = 5 V, C<sub>OUT</sub> < 50 nF

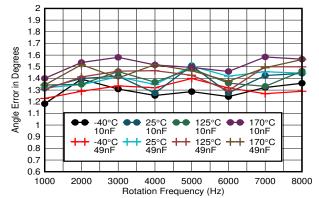

$\rm VCC=3.3V,\, LC_{freq}\text{=}5MHz,\, Ideal\, Inputs,\, No\, offset\, and\, gain\, correction\, Signal\, path\, delay\, compensated$

Figure 5-3. Angle Error VCC = 3.3 V,  $C_{OUT}$  < 50 nF

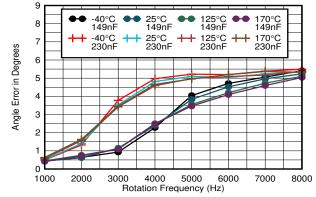

VCC = 5V, LCfreq=5MHz, Ideal Inputs, With offset and gain correction Signal path delay compensated

Figure 5-5. Angle Error VCC = 5 V, C<sub>OUT</sub> > 100 nF

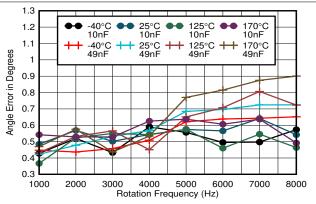

$\rm VCC=5V,\,LC_{freq}=5MHz,\, Ideal\,\,Inputs,\,With\,\,offset\,\,and\,\,gain\,\,correction\,\,Signal\,\,path\,\,delay\,\,compensated$

### Figure 5-2. Angle Error VCC = 5 V, $C_{OUT}$ < 50 nF

VCC = 3.3V,  $LC_{freq}=5MHz$ , Ideal Inputs, With offset and gain correction Signal path delay compensated

Figure 5-4. Angle Error VCC = 3.3 V, C<sub>OUT</sub> < 50 nF

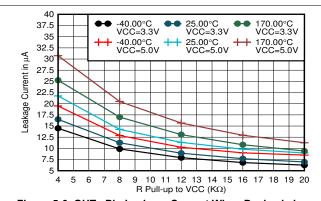

Figure 5-6. OUTx Pin Leakage Current When Device is in a SAFE State and Output Pulled to VCC With R Pull-up

# **6 Detailed Description**

### 6.1 Overview

The LDC5071-Q1 is an inductive position sensor front-end IC for use in automotive and industrial applications. The sensor typically consists of an excitation coil and a set of two receiver coils, all drawn on the same PCB. The sensor also has a metal target which is typically printed on another PCB. The coil PCB is mounted in a fixed position on the motor and the metal target is mounted on a rotating shaft. The device excites the excitation coil, which then couples to the receiver coils. The amount of coupling from the excitation to receiver coils depends on the relative position of the metal target to the receiver coils and also on the air gap between the coil PCB and the target. The LDC5071-Q1 has an LC oscillator driver that can drive an excitation coil with a constant amplitude and supports a wide range of LC combinations.

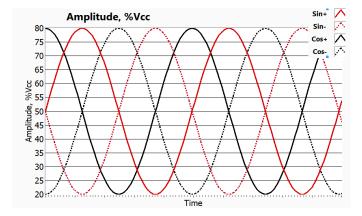

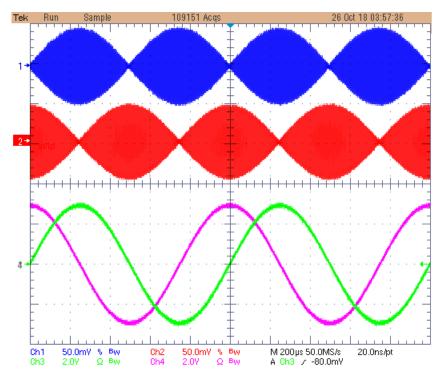

Two receiver coils are placed such that the LDC5071-Q1 outputs are shifted by 90°. These Sine and Cosine outputs are ratiometric to each other and can be used to calculate the angle at any given instant. The LDC5071-Q1 receiver filters out the out-of-band noise, demodulates, and amplifies the signal. The device has a gain block that can be either set manually or in automatic mode. In automatic mode, the LDC5071-Q1 will regulate output amplitude to a fixed band, which can remove sensor variability such as the lifetime variation of air gap. The device has two differential output drivers that can drive a wide range of capacitive loads. Typically these are digitized by an ADC of an MCU for further angle calculation, for motor control, or for linear position information extraction.

Figure 6-1. LDC5071-Q1 Typical Output

The LDC5071-Q1 implements a pin-level built-in self-test at power up to check for sensor pins open, shorts to supplies, and short between the coils. The device also has analog and digital built-in self-test to test internal safety mechanisms.

Product Folder Links: LDC5071-Q1

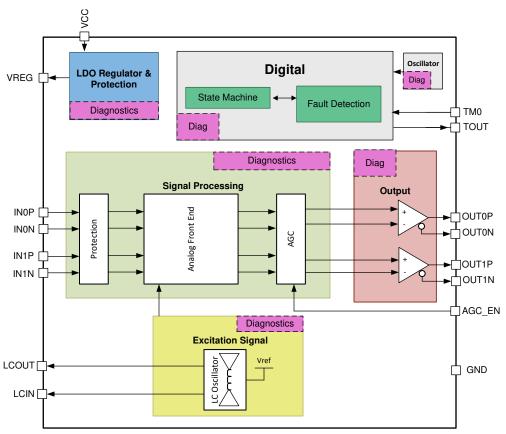

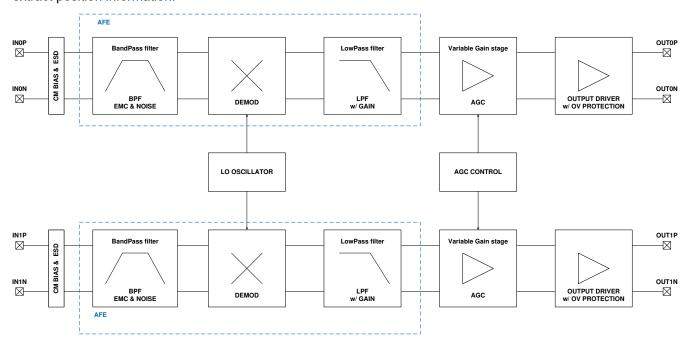

### 6.2 Functional Block Diagram

Copyright © 2018, Texas Instruments Incorporated

### **6.3 Feature Description**

### 6.3.1 Input Supply Voltage

The main voltage supply for this device is on the VCC pin. The VCC pin can be supplied either by a 3.3-V or 5-V regulator. This pin is protected internally from possible negative voltages on the pin and from possible back-feeding of current from the device to the regulator. The pin can also withstand voltages as high as 30 V. For 3.3-V mode, the VREG and VCC pins are shorted together on the PCB.

There is an internal 3.3-V regulator with a capacitor on the VREG pin. This regulator is the supply for all internal blocks, the LC oscillator, and the regulator is also used as a reference block for various sections of the signal chain. Additionally, an internal 1.5-V regulator supplies the digital logic. This device has two modes of operation: a 5-V supply mode and a 3.3-V supply mode. For 5-V supply mode, 5 V is required on the VCC pin that the internal regulator will use to generate voltage on VREG. For 3.3-V supply mode, the VREG and VCC pins must be connected externally and supplied with regulated 3.3 V. This will change the common-mode voltage on the device outputs, because this voltage is derived from half the value on the VCC pin. The device includes an automatic check to figure out which mode the device is in during power up.

### 6.3.2 Excitation Signal

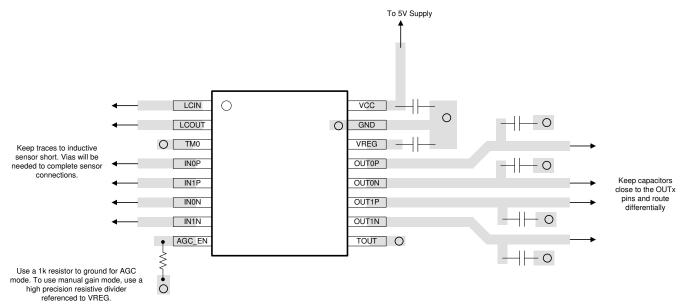

The excitation signal is generated by an LC oscillator. The LCIN and LCOUT pins will be connected to the excitation coil. The oscillator signal driver automatically regulates the signal to  $V_{AMP\_LC}$ . The user can adjust the external capacitors on LCIN and LCOUT to select the excitation frequency. For best performance, TI recommends to use two capacitors. Place one capacitor from LCIN to ground and place the other capacitor from LCOUT to ground ( $C_1$  and  $C_2$ ) instead of using only one capacitor between LCIN and LCOUT.

Use Equation 1 to calculate the excitation frequency.

$$f_{OSC\_LC} = \frac{1}{2\pi \times \sqrt{\left(L \times \left(\frac{C_1 \times C_2}{C_1 + C_2}\right)\right)}}$$

(1)

where

- · L is inductance of excitation coil

- C1, C2 are the external capacitors on LCIN and LCOUT, respectively

### 6.3.3 Signal Processing Block

The inputs to the signal processing block come from the outputs of the receiver coils of the position sensor. This block will demodulate the position signals, filter out noise, and amplify the signal in preparation for angle calculation by an external control unit. The first stage of the signal processing block contains ESD protection circuitry and sets the common-mode voltage. The second stage of this block is an EMC filter to eliminate noise. The next stage of this block is a demodulator for the input signals. This demodulation uses the frequency of the LC oscillator as a reference. The signals will then go through a low-pass filter with fixed gain. The last stage in the signal processing block is a gain stage where the gain is either set by an automatic gain control routine(AGC\_EN pin pulled to GND through an external resistor), or set to a fixed gain by the voltage on the AGC\_EN pin. The signal path gain for both channels is same and are matched very closely by careful design.

Figure 6-2 shows a block diagram of the analog front-end in the IC that demodulates the incoming signal to extract position information.

Figure 6-2. Signal Processing Block Diagram

Instruments

#### 6.3.3.1 Demodulation

The receive path for the sine path can be modeled by Equation 2 through Equation 5.

$$\mathsf{RXi}_{\mathsf{sin}} = \mathsf{V}_{\mathsf{AMP\_LC}} \times \eta \times \mathsf{sin} \big( 2 \times \pi \times \mathsf{f}_{\mathsf{OSC\_LC}} \times \mathsf{t} \big) \times \mathsf{sin} \big( \Theta \big) \tag{2}$$

### where

- RXi<sub>sin</sub>: Receiver path sine coil input

- V<sub>AMP LC</sub>: LC oscillator signal amplitude

- η: Coupling factor between exciter and receive coil

- f<sub>OSC LC</sub>: LC oscillator excitation frequency

- Θ: Instantaneous motor angle

$$\text{Demod}_{\text{sin}} = G_{\text{MIXER}} \times G_{\text{BPF}} \times V_{\text{AMP\_LC}} \times \eta \times \text{sin}(\Theta) \times \frac{1}{2} \times \left(1 + \text{sin}\left(2 \times \pi \times f_{\text{OSC\_LC}} \times t\right)\right) \tag{3}$$

#### where

- Demod<sub>sin</sub>: Demodulator sine path output

- V<sub>AMP LC</sub>: LC oscillator signal amplitude

- η: Coupling factor between exciter and receive coil

- f<sub>OSC LC</sub>: LC oscillator excitation frequency

- Θ: Instantaneous motor angle

- G<sub>MIXFR</sub>: Gain due to the mixer

- G<sub>BPF</sub>: Gain due to the band-pass filter

$$LPF_{sin} = \frac{1}{2} \times G_{MIXER} \times G_{BPF} \times G_{LPF} \times V_{AMP\_LC} \times \eta \times sin(\Theta)$$

(4)

#### where

- LPF<sub>sin</sub>: Low-pass filter sine path output

- V<sub>AMP LC</sub>: LC oscillator signal amplitude

- η: Coupling factor between exciter and receive coil

- Θ: Instantaneous motor angle

- G<sub>MIXER</sub>: Gain due to the mixer

- G<sub>BPF</sub>: Gain due to the band-pass filter

- G<sub>I PF</sub>: Gain due to the low-pass filter

$$V_{OUT\_SIN} = \frac{1}{2} \times G \times V_{AMP\_LC} \times \eta \times sin(\Theta)$$

(5)

### where

- Vout<sub>sin</sub>: Signal output at the end of sine path

- V<sub>AMP LC</sub>: LC oscillator signal amplitude

- η: Coupling factor between exciter and receive coil

- Θ: Instantaneous motor angle

- G: Total combined gain of the signal path

The cosine path can be modeled in the same way as sine path.

The total gain of the system is a combination of the gain control, mixer gain, and fixed gain. Use Equation 6 to calculate the total gain:

$$G = G_{FIXED} \times G_{MIXER} \times G_{GC}$$

(6)

#### where

- GFIXED is the fixed gain in the signal path, including GLPF and GBPF

- G<sub>FIXED</sub> = 43.2 for VCC = 5 V

- G<sub>FIXED</sub> = 28.8 for VCC = 3.3 V

- G<sub>MIXER</sub> is the gain due to the mixer. The typical value is 0.637.

- G<sub>GC</sub> is the variable gain in the signal path. This is either selected by the AGC or the Fixed Gain Control depending on the voltage on the AGC\_EN pin.

#### 6.3.3.2 Fixed Gain Control

To set the gain of the final gain stage, a voltage in the range of  $V_{AGC\_EN\_MANUAL}$  must be applied to the AGC\_EN pin. This gain setting will be set during the DIAGNOSTICS state. A change in the voltage on AGC\_EN affects the AGC gain the next time the device enters the DIAGNOSTICS state, either during the next power up of the device or during fault recovery. The nominal value of minimum gain of this stage is 0.375 and the maximum gain is 60.375. The gain is implemented as linear in dB scale with 256 steps. This gain is rotation frequency dependent. For higher rotation speeds, the gain value will fall off. Equation 7 shows the gain in linear scale is related to the voltage on AGC\_EN pin as a percentage of VREG:

$$Gain = 0.375 + 0.759 \times \left(10^{\left(\frac{1.903 \times \left(\frac{\% V Reg - 4.55}{90.9}\right)\right)}} - 1\right)$$

(7)

#### where

- · Gain is the effective gain set by gain control block.

- %VREG is the voltage on AGC\_EN pin expressed as percentage of voltage on the VREG pin.

Make sure the voltage applied on AGC\_EN pin falls within  $V_{AGC\ EN\ MANUAL}$  range.

### 6.3.3.3 Automatic Gain Control

When the voltage on the AGC\_EN pin is below V<sub>AGC\_EN\_AUTO</sub>, the manual gain control function is disabled and the Automatic Gain Control (AGC) is enabled.

In AGC mode, the device will change the gain of the last stage of the signal processing block to keep the final output within an appropriate voltage range on VOUT. The AGC block uses the square root of the sum of the squared amplitudes of the two channels to sense amplitude of output signals and set gain selection. Both channels will have the same gain. This means that the AGC block will set the gain for sine and cosine channels such that the quantity AGC TARGET as defined in Equation 8 is within the ranges listed in *Specifications*.

$$RADIUS = \frac{\sqrt{\left(OUT1P - OUT1N\right)^2 + \left(OUT0P - OUT0N\right)^2}}{VCC}$$

(8)

#### where

- OUTxx: Voltage on the output pins

- VCC: Voltage on the VCC pin

- AGC\_TARGET: Regulation target for the AGC block

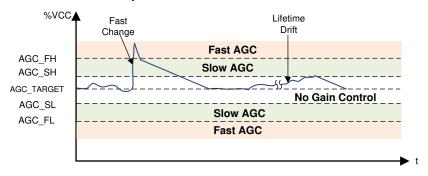

The AGC sets the gain in the DIAGNOSTICS state and then dynamically regulates the gain in NORMAL state. There are two regions of regulation, the slow AGC regulation region and the fast AGC regulation region. See Figure 6-3. The blue curve shows the ratio defined by Equation 8 as percentage of VCC. If the ratio rises above AGC\_FH or falls below AGC\_FL, fast regulation becomes active, and the gain is changed by four gain codes every nominal value of 819.2 µs. If the ratio falls between AGC\_SH and AGC\_FH, or between AGC\_FL and AGC\_SL, slow regulation is active, and the gain is changed by one code approximately every 840 mS. To allow

for faster settling of the output during power up in the diagnostic state, the device changes gain by one code every 3.2 µs in slow AGC region and eight codes every 3.2 µs in the fast AGC region. The thresholds are listed in Specifications. The gain step size is constant in dB scale and is approximately equal to 0.15 dB. Figure 6-3 shows the two cases: a fast change (for example, due to a transient), and a slow change due to lifetime drift.

The AGC block thus will try to compensate for changes in amplitude of the input signal or changes in VCC. If the ratio, after reaching AGC TARGET, stays between AGC SH and AGC SL, then AGC does not react and does not change the gain. The AGC block engages if one of the thresholds is crossed, and it will try to change the output amplitudes such that the ratio reaches AGC TARGET again. Hence, the No Gain Control region in Figure 6-3 causes the AGC block to have some hysteresis.

Figure 6-3. AGC Regulation Bands

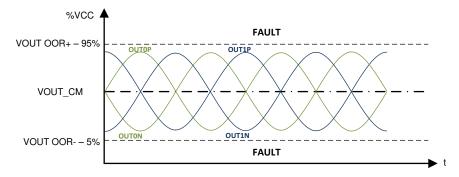

### 6.3.4 Output Stage

The output stage consists of buffers that drive each of the outputs differentially and maintain the output common mode at V<sub>RFF OUT</sub> as specified in *Specifications*. There are two output stages, one at the OUT0x pins and the other at the OUT1x pins, and each drive the pins in a push-pull manner. For a rotating input, one set of pins will represent the sine angle information and other set will represent cosine angle information. The output stages buffer the AGC output and outputs the final demodulated position information to be used by a microcontroller. The output stage can drive a large range of capacitive loads.

The output stage requires external capacitors as specified by C<sub>OUT</sub> and pullup or pulldown resistors as specified by RPD OUT and RPU OUT. The OUTx pins enter a high impedance state in the case of a fault, so the pullup and pulldown resistors are used to pull the voltage out of range for detection by the MCU. See External Diagnostics Required for Loss of VCC or GND for details about external diagnostics required for loss of VCC or GND conditions.

There is a possibility that wires connecting to OUT0 and OUT1 pins can be routed outside the sensor module, so the output stage has both negative and high voltage protection to prevent the part from getting damaged in the event of shorts. In the event of a fault, the output stages are put in Hi-Z mode and external pullup and pulldown resistors will drive OUTx pins to maximum and minimum signaling a fault to the microcontroller. See *Diagnostics* for details.

Figure 6-4. Out of Operation Fault Detection Range at the Output

#### Note

The voltage at the OUTx pins is not ratiometric to VCC. In AGC mode, the calculated RADIUS in Equation 8 will change. If the value of the RADIUS changes sufficiently to cross one of the thresholds (depending on change magnitude of VCC), then the gain of the AGC will be adjusted to bring the RADIUS value back to AGC\_TARGET. In fixed-gain mode, the gain will not be adjusted even if VCC change by large magnitude.

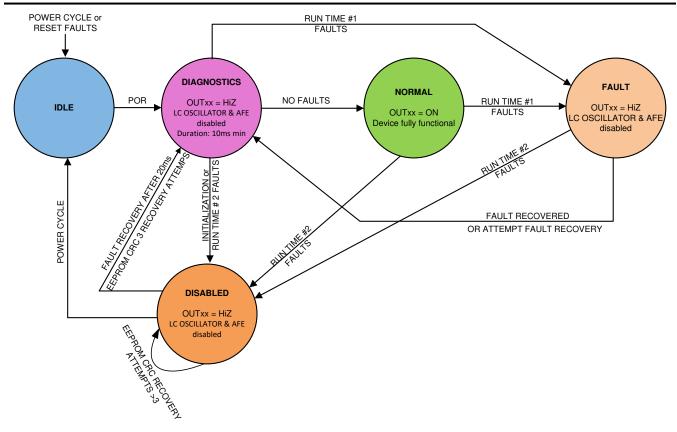

### 6.3.5 Diagnostics

The LDC5071-Q1 is equipped with diagnostics features to detect, monitor, and report failures that either existed before the power up or occurred during device operation. In the event of a failure, the LDC5071-Q1 is placed either in IDLE, DISABLED, or FAULT state (based on the failure nature), the LC oscillator is turned off, the AFE is disabled, and the output pins are tri-stated, and consequently, are pulled up or down by external resistors. From the FAULT state, the LDC5071-Q1 returns to DIAGNOSTICS state if the fault condition is removed. From the DISABLED state, the LDC5071-Q1 is moved to IDLE state after a power cycle (see *Device Functional Modes*).

The LDC5071-Q1 tri-states its output to signal a fault. As shown in *Application and Implementation*, it is expected that a combination of pullup or pulldown resistors are added on OUTx pins at the termination site (that is, at the microcontroller). The values of these resistors are specified as R<sub>PU\_OUT</sub> and R<sub>PD\_OUT</sub> in *Specifications*. The resistors are generally pulled up to a supply (typically VCC) and pulled down to ground such that the ADC code on the MCU is out of the expected range. This will signal a fault to the microcontroller.

#### 6.3.5.1 Undervoltage Diagnostics

The LDC5071-Q1 continuously monitors the VREG and DVDD voltage while in DIAGNOSTICS, NORMAL, FAULT, and DISABLED states. If the VREG or DVDD drops below the specified limits (see *Electrical Characteristics*), the LC oscillator is turned off, the AFE is disabled, and the output pins are tri-stated if neither were done so yet. Upon voltage recovery, the device transitions to the IDLE state and initiates a regular power-on reset (POR).

#### 6.3.5.2 Initialization Diagnostics

During power up in the DIAGNOSTICS state, the LDC5071-Q1 undergoes a number of self-diagnostics and checks (for fault thresholds refer to *Diagnostics* and for deglitch times refer to *Switching Characteristics*):

- EEPROM CRC check: the LDC5071-Q1 calculates the CRC value of the EEPROM register settings and compares that value to the recorded expected CRC value. In case of FAULT, the LDC5071-Q1 transitions to the DISABLED state.

- LBIST check: the LDC5071-Q1 undergoes automated self-testing pattern for the digital logic. In case of FAULT, the LDC5071-Q1 transitions to the DISABLED state.

- 3. ABIST check: the LDC5071-Q1 undergoes automated self-testing pattern for the fault-monitoring circuits. In case of FAULT, the LDC5071-Q1 transitions to the DISABLED state.

- 4. Sensor interface BIST check: the LDC5071-Q1 applies the automated test patterns to Sensor interface (LCIN, LCOUT, IN0P, IN0N, IN1P, and IN1N) pins to check that they are open or shorted to GND or battery. The sensor interface BIST check also checks if there is a short between the coils of the sensor and if any of the coils are open. The LDC5071-Q1 will also check if any impedance is present as specified by the R<sub>AGC EN AUTO</sub> or R<sub>PU AGC EN</sub> on the AGC\_EN pin and check if the AGC\_EN pin is not shorted to GND.

- 5. VREG capacitor loss check: the LDC5071-Q1 uses the VREG capacitor to compare the internal time constant with the external time constant (5-V VCC mode only). This check is only performed at power up and is not performed if the device transitions from FAULT state to DIAGNOSTICS state. The maximum capacitance on VREG pin that can trigger this fault is given by C<sub>LOSS VREG</sub>.

- 6. The LDC5071-Q1 enables the LC oscillator and checks that V<sub>UVL\_AMP\_LC</sub>, V<sub>OVH\_AMP\_LC</sub>, V<sub>UVL\_CM\_LC</sub>, and V<sub>OVH\_CM\_LC</sub> faults disappear within t<sub>LC\_FLT\_DT</sub>.

- 7. The LDC5071-Q1 enables the AFE, AGC, and Output stages in a staggered manner.

- 8. The LDC5071-Q1 the device resets all checks and faults for certain period of time to allow all internal signals to settle and then starts monitor faults

Product Folder Links: LDC5071-Q1

9. The LDC5071-Q1 transitions to the Normal state ensuring that t<sub>PRWR ON</sub> is met and no other faults are detected. In AUTO AGC mode, the LDC5071-Q1 also checks that the output of the AGC block is within AGC\_Target. If the AGC block is not within AGC\_Target, the devices transitions to the DISABLED state.

### 6.3.5.3 Normal State Diagnostics

During normal device operation, a number of parameters are continuously monitored

For the following parameters, if a fault condition is detected, the device is transferred to the FAULT state, Only if the fault condition is cleared then the part transitions to DIAGNOSTIC state (for fault thresholds refer to *Diagnostics* and for deglitch times refer to *Switching Characteristics*):

VREG overvoltage check: if the VREG voltage exceeds the V<sub>OVUTH VREG</sub>, fault condition is detected in the t<sub>VREG\_OV\_DT</sub>. This fault detection delay allows the LDC5071-Q1 to filter out short glitches on the VREG pin. After the voltage drops below the V<sub>OVLTH VREG</sub>, the fault condition is cleared.

For the following parameters, if a fault condition is detected, the device is transferred to the FAULT state and then to the DIAGNOSTICS state to attempt recovery and detect if the fault is still present. The zero-crossing mentioned in this section refers to crossing of the common voltage of a differential signal pair.

Output signal voltage check: this diagnostic compares the states of the zero-crossing comparators of OUT pins with the corresponding zero-crossing comparators of the AGC block outputs. A valid rotational signal must be present for this check, and the detection time, will depend on the rotational speed of the motor.

For the following parameters, if a fault condition is detected, the device is transferred to the DISABLED state and a recovery is attempted (see *DISABLED State*):

- Register CRC check: the LDC5071-Q1 calculates the CRC value of the safety-critical register settings and compares the CRC value to the recorded expected CRC value. In case of FAULT, the LDC5071-Q1 transitions to the DISABLED state. This check is performed continuously.

- Critical registers redundancy check: the device checks the validity of the critical registers versus its redundant copy. In case of a discrepancy, the device immediately transitions to the DISABLED state

- TM0 state check: the device checks if the TM0 pin state was changed after its state was determined during Initialization diagnostics.

- TOUT state check: the device checks if the TOUT pin state was changed after its state was determined during Initialization diagnostics.

- AGC\_EN toggle check: the device checks if the AGC\_EN state was changed after its state was determined during Initialization diagnostics. This check has a deglitch time of  $t_{AGC\ EN\ TGL\ DT}$

### 6.3.5.4 Fault State Diagnostics

While in the FAULT state, a number of parameters are continuously monitored.

For the following parameters, if a fault condition is detected, the device stays in FAULT state until and unless the fault condition is removed and then the device transitions to DIAGNOSTIC state:

The VREG overvoltage check as described in Normal State Diagnostics.