SNOSB43C - SEPTEMBER 2011 - REVISED NOVEMBER 2016

LM3560

# LM3560 Synchronous Boost Flash Driver With Dual 1-A High-Side Current Sources (2-A Total Flash Current)

#### **Features**

- Dual High-Side Current Sources Allow for **Grounded Cathode LED Operation**

- Accurate and Programmable LED Current from 31.25 mA to 2 A

- Independent LED Current Source Programmability

- Up to 90% Efficient

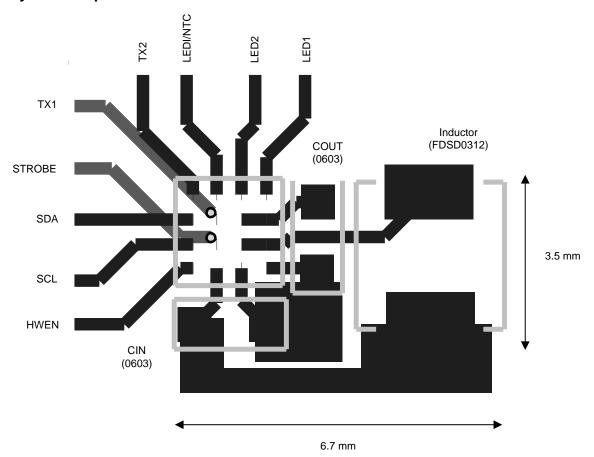

- Ultra-Small Solution Size: < 26 mm<sup>2</sup>

- Four Operating Modes: Torch, Flash, Privacy Indicate, and Message Indicator

- 4-Bit ADC for V<sub>LED</sub> Monitoring

- LED Thermal Sensing and Current Scale-Back

- Hardware Flash and Torch Enable

- Dual Synchronization Inputs for RF Power Amplifier Pulse Events

- LED and Output Disconnect During Shutdown

- Open and Short LED Detection

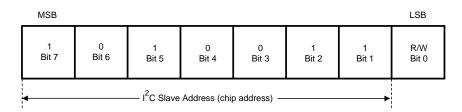

- 400-kHz I<sup>2</sup>C-Compatible Interface

- Active Low Hardware Reset

- -40°C to +85°C Ambient Temperature Range

## **Applications**

- Camera Phone LED Flash

- White LED Biasing

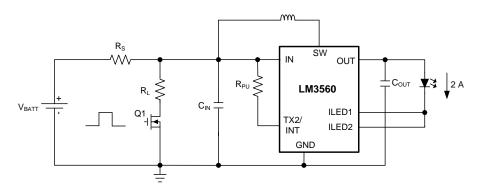

## 3 Description

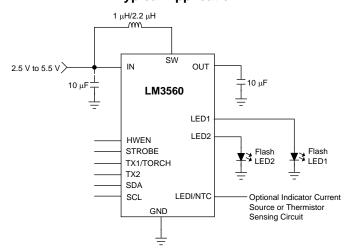

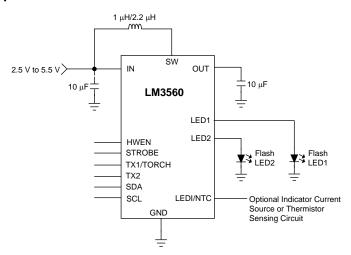

The LM3560 is a 2-MHz fixed frequency synchronous boost converter with two 1000-mA constant current drivers for high-current white LEDs. The dual highside current sources allow for grounded cathode LED operation and can be tied together for providing flash currents at up to 2 A through a single LED. An adaptive regulation method ensures the current for each LED remains in regulation and maximizes efficiency.

The LM3560 is controlled via an I<sup>2</sup>C-compatible interface. Features include an internal 4-bit ADC to monitor the LED voltage, independent LED current control, a hardware flash enable allowing a logic input to trigger the flash pulse, dual TX inputs which force the flash pulse into a low-current torch mode allowing for synchronization to RF power amplifier events or other high-current conditions, and an integrated comparator designed to monitor an NTC thermistor and provide an interrupt to the LED current. Additionally, an active high HWEN input provides a hardware shutdown during system software failures.

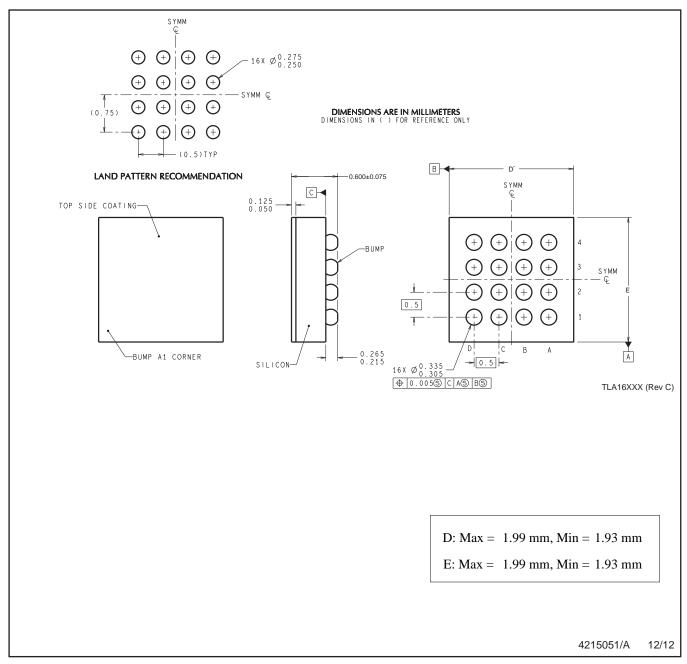

The device is available in an ultra-small 16-pin DSBGA package. The 2-MHz switching frequency, overvoltage protection and adjustable current limit allow for the use of tiny, low-profile (1-µH and 2.2-µH) inductors and ceramic (10-µF) capacitors.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |

|-------------|------------|-------------------|

| LM3560      | DSBGA (16) | 1.96 mm × 1.96 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

#### **Typical Application**

Copyright © 2016, Texas Instruments Incorporated

## **Table of Contents**

|   |                                                       | 7.5 I <sup>2</sup> O Composible Interfere               |

|---|-------------------------------------------------------|---------------------------------------------------------|

| 1 | Features 1                                            | 7.5 I <sup>2</sup> C-Compatible Interface               |

| 2 | Applications 1                                        | 7.6 Register Descriptions30                             |

| 3 | Description 1                                         | 8 Application and Implementation 39                     |

| 4 | Revision History2                                     | 8.1 Application Information                             |

| 5 | Pin Configuration and Functions3                      | 8.2 Typical Application                                 |

| 6 | Specifications                                        | 9 Power Supply Recommendations 43                       |

| • | 6.1 Absolute Maximum Ratings                          | 10 Layout 44                                            |

|   | 6.2 ESD Ratings                                       | 10.1 Layout Recommendations 44                          |

|   | 6.3 Recommended Operating Conditions                  | 10.2 Layout Example45                                   |

|   | 6.4 Thermal Information                               | 11 Device and Documentation Support 46                  |

|   | 6.5 Electrical Characteristics                        | 11.1 Device Support46                                   |

|   | 6.6 I <sup>2</sup> C Timing Specifications (SCL, SDA) | 11.2 Documentation Support 46                           |

|   | 6.7 Typical Characteristics                           | 11.3 Receiving Notification of Documentation Updates 46 |

| 7 | Detailed Description 12                               | 11.4 Community Resources46                              |

| - | 7.1 Overview                                          | 11.5 Trademarks46                                       |

|   | 7.2 Functional Block Diagram                          | 11.6 Electrostatic Discharge Caution                    |

|   | 7.3 Feature Description                               | 11.7 Glossary                                           |

|   | 7.4 Device Functional Modes                           | 12 Mechanical, Packaging, and Orderable Information46   |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

## Changes from Revision B (August 2013) to Revision C

Page

# 5 Pin Configuration and Functions

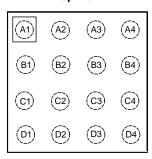

YZR Package 16-Pin DSBGA Top View

## **Pin Functions**

| PIN    |                     | TVDE         | DECODINE                                                                                                                                                                                   |  |

|--------|---------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO.    | NAME                | TYPE         | DESCRIPTION                                                                                                                                                                                |  |

| A1     | LED1                | Power        | High-side current source output for flash LED                                                                                                                                              |  |

| A2, B2 | OUT                 | Power        | Step-up DC-DC converter output. Connect a 10-µF ceramic capacitor between this pin and GND.                                                                                                |  |

| A3, B3 | SW                  | Power        | Drain connection for internal NMOS and synchronous PMOS switches.                                                                                                                          |  |

| A4, B4 | GND                 | Ground       | Ground                                                                                                                                                                                     |  |

| B1     | LED2                | Output       | High-side current source output for flash LED                                                                                                                                              |  |

| C1     | LEDI/NTC            | Power        | Configurable as a high-side current source output for indicator LED or comparator input for LED temperature sensing.                                                                       |  |

| C2     | TX1/TORCH/<br>GPIO1 | Input/Output | Configurable as a dual-polarity rf power amplifier synchronization input, an interrupt output, of as a general purpose logic I/O. This pin has an internal 300-k $\Omega$ pulldown to GND. |  |

| C3     | STROBE              | Input        | Active high hardware flash enable. Drive STROBE high to turn on the flash pulse. This pin has an internal $300$ -k $\Omega$ pulldown to GND.                                               |  |

| C4     | IN                  | Power        | Input voltage connection. Connect IN to the input supply, and bypass to GND with a minimum 10-µF ceramic capacitor.                                                                        |  |

| D1     | TX2/INT/GPIO2       | Input/Output | Configurable as a dual-polarity power amplifier synchronization Input, an Interrupt Output, or as a general purpose logic I/O. This pin has an internal 300-k $\Omega$ pulldown to GND.    |  |

| D2     | SDA                 | Input/Output | Serial data input/output. High impedance in shutdown or in power down.                                                                                                                     |  |

| D3     | SCL                 | Input        | Serial clock input. High impedance in shutdown or in power down.                                                                                                                           |  |

| D4     | HWEN                | Input        | Logic high hardware enable. HWEN is a high-impedance input and is normally connected with an external pullup resistor to a logic high voltage.                                             |  |

## 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                                                                                                                                                     | MIN                | MAX                                                         | UNIT |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------------------------------------|------|

| V <sub>IN</sub> , V <sub>SW</sub> , V <sub>OUT</sub>                                                                                                                                | -0.3               | 6                                                           | V    |

| V <sub>SCL</sub> , V <sub>SDA</sub> , V <sub>HWEN</sub> , V <sub>STROBE</sub> , V <sub>TX1</sub> , V <sub>TX2</sub> , V <sub>LED1</sub> , V <sub>LED2</sub> , V <sub>LEDI/NTC</sub> | -0.3               | to the lesser of (V <sub>IN</sub> + 0.3 V) with 6 V maximum | V    |

| Continuous power dissipation <sup>(2)</sup>                                                                                                                                         | Internally limited |                                                             |      |

| Junction temperature, T <sub>J-MAX</sub>                                                                                                                                            |                    | 150                                                         | °C   |

| Storage temperature, T <sub>stg</sub>                                                                                                                                               | -65                | 150                                                         | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |                         |                                                        | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1) | ±2000 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                                    | MIN | MAX | UNIT |

|----------------------------------------------------|-----|-----|------|

| Input voltage, V <sub>IN</sub>                     | 2.5 | 5.5 | V    |

| Junction temperature, T <sub>J</sub>               | -40 | 125 | °C   |

| Ambient temperature, T <sub>A</sub> <sup>(1)</sup> | -40 | 85  | °C   |

<sup>(1)</sup> In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX-OP</sub> = 125°C), the maximum power dissipation of the device in the application (P<sub>D-MAX</sub>), and the junction-to-ambient thermal resistance of the device package in the application (R<sub>θJA</sub>), as given by the following equation: T<sub>A-MAX</sub> = T<sub>J-MAX-OP</sub> - (R<sub>θJA</sub> × P<sub>D-MAX</sub>).

#### 6.4 Thermal Information

|                      | THERMAL METRIC <sup>(1)</sup>                |         |      |

|----------------------|----------------------------------------------|---------|------|

|                      |                                              |         | UNIT |

|                      |                                              | 16 PINS |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 71.4    | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 0.4     | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 12.4    | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.3     | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 12.6    | °C/W |

(1) For more information about traditional and new thermal metrics, see Semiconductor and IC Package Thermal Metrics.

<sup>(2)</sup> Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at T<sub>J</sub> = 150°C (typical) and disengages at T<sub>J</sub> = 135°C (typical). Thermal shutdown is ensured by design.

#### 6.5 Electrical Characteristics

Unless otherwise specified,  $V_{IN} = 3.6 \text{ V}$ ,  $V_{HWEN} = V_{IN}$ ,  $T_A = 25^{\circ}\text{C}$ . (1) (2)

| PA                                     | RAMETER                                      | Т                                                                          | EST CONDITIONS                                                                                    | MIN   | TYP  | MAX   | UNIT |

|----------------------------------------|----------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------|------|-------|------|

| CURRENT SOL                            | URCE SPECIFICATION                           | S                                                                          | <u>'</u>                                                                                          |       |      |       |      |

|                                        |                                              |                                                                            | 1000-mA flash current setting, per current source                                                 | -3.5% | 2000 | 3.5%  |      |

| ı                                      | Current source                               | I <sub>LED1</sub> + I <sub>LED2</sub><br>3 V ≤ V <sub>IN</sub> ≤ 4.2 V     | 1000-mA flash current setting, per current source<br>−40°C ≤ T <sub>A</sub> ≤ 85°C                | -5%   |      | 5%    | mA   |

| I <sub>LED</sub>                       | accuracy                                     | $V_{OUT} = 4.5 \text{ V}$                                                  | 31.25-mA torch current, per current source                                                        |       | 62.5 |       | ША   |

|                                        |                                              |                                                                            | 31.25-mA torch current, per<br>current source<br>−40°C ≤ T <sub>A</sub> ≤ 85°C                    | -10%  |      | 10%   |      |

| V <sub>OUT</sub> – V <sub>LED1/2</sub> | Current source regulation voltage            | I <sub>LED</sub> = 2 A (I <sub>LED1</sub> +                                | I <sub>LED2</sub> ), V <sub>OUT</sub> = 4.5 V                                                     |       | 300  |       | mV   |

|                                        |                                              | ON threshold                                                               |                                                                                                   |       | 5    |       |      |

| $V_{OVP}$                              | Output overvoltage protection trip point (3) | ON threshold, -40                                                          | 0°C ≤ T <sub>A</sub> ≤ 85°C                                                                       | 4.925 |      | 5.075 | V    |

|                                        | protocuon inp point                          | OFF threshold                                                              |                                                                                                   |       | 4.8  |       |      |

| STEP-UP DC-D                           | OC CONVERTER SPEC                            | IFICATIONS                                                                 |                                                                                                   |       |      |       |      |

| R <sub>PMOS</sub>                      | PMOS switch on-<br>resistance                | I <sub>PMOS</sub> = 1 A                                                    |                                                                                                   |       | 80   |       | mΩ   |

| R <sub>NMOS</sub>                      | NMOS switch on-<br>resistance                | I <sub>NMOS</sub> = 1 A                                                    |                                                                                                   |       | 65   |       | mΩ   |

|                                        |                                              | CL bits = 00                                                               |                                                                                                   |       | 1.6  |       |      |

|                                        |                                              | CL bits = 00, 3 V : $-40^{\circ}\text{C} \le T_{A} \le 85^{\circ}\text{C}$ | ≤ V <sub>IN</sub> ≤ 4.2 V                                                                         | 1.44  |      | 1.76  |      |

|                                        |                                              | CL bits = 01                                                               |                                                                                                   |       | 2.3  |       |      |

| 1                                      | O 1: 1 (4)                                   | CL bits = 01, 3 V : $-40^{\circ}$ C $\leq T_{A} \leq 85^{\circ}$ C         |                                                                                                   | 2.02  |      | 2.58  |      |

| I <sub>CL</sub>                        | Switch current limit <sup>(4)</sup>          | CL bits = 10                                                               |                                                                                                   |       | 3    |       | Α    |

|                                        |                                              | CL bits = 10, 3 V : $-40^{\circ}$ C $\leq T_{A} \leq 85^{\circ}$ C         |                                                                                                   | 2.64  |      | 3.36  |      |

|                                        |                                              | CL bits = 11                                                               |                                                                                                   |       | 3.6  |       |      |

|                                        |                                              | CL bits = 11, 3 V : $-40^{\circ}$ C $\leq T_{A} \leq 85^{\circ}$ C         |                                                                                                   | 3.17  |      | 4.03  |      |

| I <sub>OUT_SC</sub>                    | Output short-circuit current limit           | V <sub>OUT</sub> < 2.3 V                                                   |                                                                                                   |       | 300  |       | mA   |

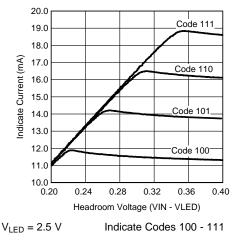

|                                        |                                              | Message indicator                                                          | r register, bits[2:0] = 111                                                                       |       | 18   |       |      |

| I <sub>LEDI/NTC</sub>                  | Indicator current                            | Message indicator<br>≤ 4.2 V<br>V <sub>LEDI/NTC</sub> = 2 V, —             | r register, bits[2:0] = 111, 3 V $\leq$ V <sub>IN</sub><br>40°C $\leq$ T <sub>A</sub> $\leq$ 85°C | 16    |      | 20    | mA   |

|                                        | Comparator trip                              | Configuration regi                                                         | ster 1, bit [4] = 1,                                                                              |       | 1    |       |      |

| $V_{TRIP}$                             | threshold                                    | Configuration regists 3 V ≤ V <sub>IN</sub> ≤ 4.2 V,                       | ster 1, bit [4] = 1,<br>-40°C ≤ T <sub>A</sub> ≤ 85°C                                             | 0.97  |      | 1.03  | V    |

<sup>(1)</sup> All voltages are with respect to the potential at the GND pin.

Copyright © 2011–2016, Texas Instruments Incorporated

<sup>(2)</sup> Minimum (MIN) and maximum (MAX) limits are specified by design, test, or statistical analysis. Typical (TYP) numbers represent the most likely norm. Unless otherwise stated, conditions for typical specifications are: V<sub>IN</sub> = 3.6 V and T<sub>A</sub> = 25°C.

<sup>(3)</sup> The typical curve for overvoltage protection (OVP) is measured in closed loop using Figure 41. The OVP value is found by forcing an open circuit in the LED1 and LED2 path and recording the peak value of V<sub>OUT</sub>. The value given in Electrical Characteristics is found in an open loop configuration by ramping the voltage at OUT until the OVP comparator trips. The closed loop data can appear higher due to the stored energy in the inductor being dumped into the output capacitor after the OVP comparator trips. Worst case is an open circuit condition where the output voltage can continue to rise after the OVP comparator trips by approximately I<sub>IN</sub> × sqrt(L/C<sub>OUT</sub>).

<sup>(4)</sup> The typical curve for current limit is measured in closed loop using *Figure 41*, and increasing I<sub>OUT</sub> until the peak inductor current stops increasing. The value given in *Electrical Characteristics* is measured open loop and is found by forcing current into SW until the current limit comparator threshold is reached. Closed loop data appears higher due to the delay between the comparator trip point and the NFET turning off. This delay allows the closed loop inductor current to ramp higher after the trip point by approximately 20 ns × V<sub>IN</sub>/L.

## **Electrical Characteristics (continued)**

Unless otherwise specified,  $V_{IN}$  = 3.6 V,  $V_{HWEN}$  =  $V_{IN}$ ,  $T_A$  = 25°C. (1) (2)

| P                         | ARAMETER                                             | TEST CONDITIONS                                                                                                                                       | MIN  | TYP  | MAX             | UNIT |

|---------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----------------|------|

| 6 Constraint on the const |                                                      |                                                                                                                                                       |      | 2    |                 |      |

| $f_{\sf SW}$              | Switching frequency                                  | 3 V ≤ V <sub>IN</sub> ≤ 4.2 V, −40°C ≤ T <sub>A</sub> ≤ 85°C                                                                                          | 1.8  |      | 2.2             | MHz  |

| t <sub>TIMEOUT</sub>      | Timeout duration (5)(6)                              | 3 V ≤ V <sub>IN</sub> ≤ 4.2 V                                                                                                                         | -10% |      | 10%             | ms   |

|                           |                                                      | Device not switching, V <sub>OUT</sub> = 3 V                                                                                                          |      | 900  |                 | μΑ   |

| I <sub>Q</sub>            | Quiescent supply                                     | Device switching, V <sub>OUT</sub> = 4.5 V                                                                                                            |      | 1.97 |                 | mA   |

| IQ                        | current                                              | Indicate mode, message indicator register bits [2:0] = 111                                                                                            |      | 590  |                 | μΑ   |

|                           | Shutdown supply                                      | $3 \text{ V} \leq \text{V}_{IN} \leq 4.2 \text{ V}$                                                                                                   |      | 0.02 |                 | ^    |

| I <sub>SHDN</sub>         | current                                              | 3 V ≤ V <sub>IN</sub> ≤ 4.2 V, −40°C ≤ T <sub>A</sub> ≤ 85°C                                                                                          |      |      | 1.25            | μΑ   |

|                           | Standby supply                                       |                                                                                                                                                       |      | 1.25 |                 |      |

| I <sub>STBY</sub>         | current                                              | 3 V ≤ V <sub>IN</sub> ≤ 4.2 V, −40°C ≤ T <sub>A</sub> ≤ 85°C                                                                                          |      |      | 2               | μΑ   |

| \/                        | \/INI                                                | V <sub>IN</sub> monitor register = 0x01                                                                                                               |      | 2.9  |                 | .,   |

| $V_{IN\_TH}$              | VIN monitor threshold                                | V <sub>IN</sub> monitor register = 0x01, −40°C ≤ T <sub>A</sub> ≤ 85°C                                                                                | 2.85 |      | 2.95            | V    |

| \/                        | VIN flash monitor                                    | V <sub>IN</sub> monitor register = 0x08                                                                                                               |      | 2.9  |                 |      |

| V <sub>IN_FLASH_TH</sub>  | threshold                                            | V <sub>IN</sub> monitor register = 0x08, −40°C ≤ T <sub>A</sub> ≤ 85°C                                                                                | 2.85 |      | 2.95            | V    |

|                           | Flash-to-torch LED current settling time             | TX_ Low to high<br>I <sub>LED1</sub> + I <sub>LED2</sub> = 2 A to 187.5 mA                                                                            |      | 2    |                 |      |

| t <sub>TX</sub>           | Torch-to-flash LED current Settling                  | TX_High to low $I_{LED1} + I_{LED2} = 187.5 \text{ mA}$ to 2 mA                                                                                       |      | 160  |                 | μs   |

|                           | Time from when I <sub>LED</sub>                      | ADC delay register bit [5] = 1                                                                                                                        |      | 16   |                 |      |

| t <sub>D</sub>            | hits target until V <sub>LED</sub> data is available | ADC delay register bit [5] = 0<br>ADC delay register bits [4:0] = 0000                                                                                |      | 250  |                 | μs   |

|                           |                                                      | V <sub>LED</sub> monitor register bits [3:0] = 1111                                                                                                   |      | 4.2  |                 |      |

| $V_{F\_ADC}$              | ADC threshold                                        | $V_{LED}$ monitor register bits [3:0] = 1111<br>3 V $\leq$ V <sub>IN</sub> $\leq$ 4.2 V, $-40^{\circ}$ C $\leq$ T <sub>A</sub> $\leq$ 85 $^{\circ}$ C | 4.05 |      | 4.35            | V    |

| HWEN, STRO                | BE, TX1/TORCH/GPIO1                                  | TX2/INT/GPIO2 VOLTAGE SPECIFICATIONS                                                                                                                  |      |      | ·               |      |

| V <sub>IL</sub>           | Input logic low                                      | 2.7 V ≤ V <sub>IN</sub> ≤ 4.2 V, −40°C ≤ T <sub>A</sub> ≤ 85°C                                                                                        | 0    |      | 0.4             | V    |

| V <sub>IH</sub>           | Input logic high                                     | $2.7 \text{ V} \le \text{V}_{\text{IN}} \le 4.2 \text{ V}, -40^{\circ}\text{C} \le \text{T}_{\text{A}} \le 85^{\circ}\text{C}$                        | 1.2  |      | $V_{IN}$        | V    |

| R <sub>PD</sub>           | Internal pulldown resistance on TX1, TX2, STROBE     |                                                                                                                                                       |      | 300  |                 | kΩ   |

| I <sup>2</sup> C-COMPATI  | BLE VOLTAGE SPECIF                                   | ICATIONS (SCL, SDA)                                                                                                                                   |      |      |                 |      |

| V <sub>IL</sub>           | Input logic low                                      | 2.7 V ≤ V <sub>IN</sub> ≤ 4.2 V, −40°C ≤ T <sub>A</sub> ≤ 85°C                                                                                        | 0    |      | 0.4             | V    |

| V <sub>IH</sub>           | Input logic high                                     | 2.7 V ≤ V <sub>IN</sub> ≤ 4.2 V, −40°C ≤ T <sub>A</sub> ≤ 85°C                                                                                        | 1.3  |      | V <sub>IN</sub> | V    |

| V <sub>OL</sub>           | Output logic low<br>(SDA)                            | $I_{LOAD} = 3 \text{ mA}$<br>2.7 V $\leq$ V <sub>IN</sub> $\leq$ 4.2 V, $-40^{\circ}\text{C} \leq$ T <sub>A</sub> $\leq$ 85°C                         |      |      | 0.4             | V    |

|                           |                                                      | 17                                                                                                                                                    |      |      |                 |      |

Submit Documentation Feedback

Copyright © 2011–2016, Texas Instruments Incorporated

Specified by design. Not production tested. The timeout period is a divided down representation of the 2-MHz clock; thus, the accuracy specification is the same as the switching frequency.

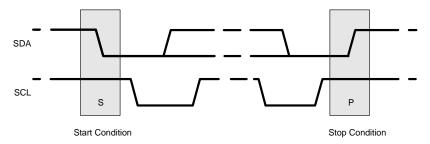

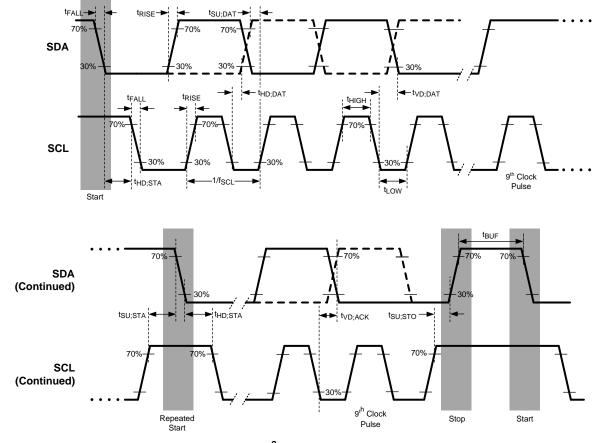

# 6.6 I<sup>2</sup>C Timing Specifications (SCL, SDA)

All minimum and maximum values apply over  $-40^{\circ}\text{C} \le T_A \le 85^{\circ}\text{C}$  and are specified by design (not production tested); see<sup>(1)</sup>

|                     |                                                   | MIN                            | MAX | UNIT |

|---------------------|---------------------------------------------------|--------------------------------|-----|------|

| $f_{SCL}$           | SCL (clock frequency)                             | 0                              | 400 | kHz  |

| t <sub>RISE</sub>   | Rise time of both SDA and SCL                     | 20 ns + 0.1 × C <sub>BUS</sub> | 300 | ns   |

| t <sub>FALL</sub>   | Fall time of both SDA and SCL                     | 20 ns + 0.1 × C <sub>BUS</sub> | 300 | ns   |

| t <sub>LOW</sub>    | Low period of SCL clock                           | 1.3                            |     | μs   |

| t <sub>HIGH</sub>   | High period of SCL clock                          | 600                            |     | ns   |

| t <sub>HD;STA</sub> | Hold time for start (or repeated start) condition | 600                            |     | ns   |

| t <sub>SU:STA</sub> | Set-up time for a repeated start                  | 600                            |     | ns   |

| t <sub>HD:DAT</sub> | Data hold time                                    | 0                              |     | ns   |

| t <sub>SU:DAT</sub> | Data set-up time                                  | 100                            |     | ns   |

| t <sub>SU:STO</sub> | Set-up time for stop condition                    | 600                            |     | ns   |

| t <sub>VD:DAT</sub> | Data valid time                                   |                                | 900 | ns   |

| t <sub>VD;ACK</sub> | Data valid acknowledge time                       |                                | 900 | ns   |

| t <sub>BUF</sub>    | Bus-free time between a start and stop condition  | 1.3                            |     | μs   |

<sup>(1)</sup> Specified by design, not production tested.

# TRUMENTS

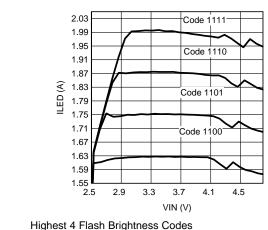

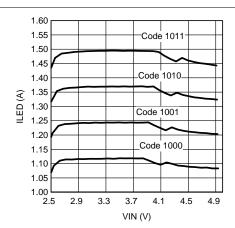

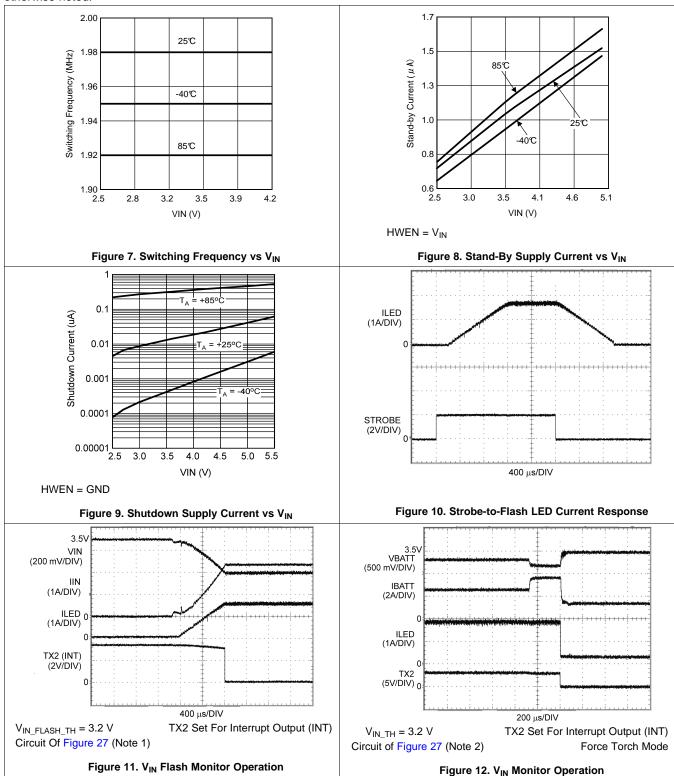

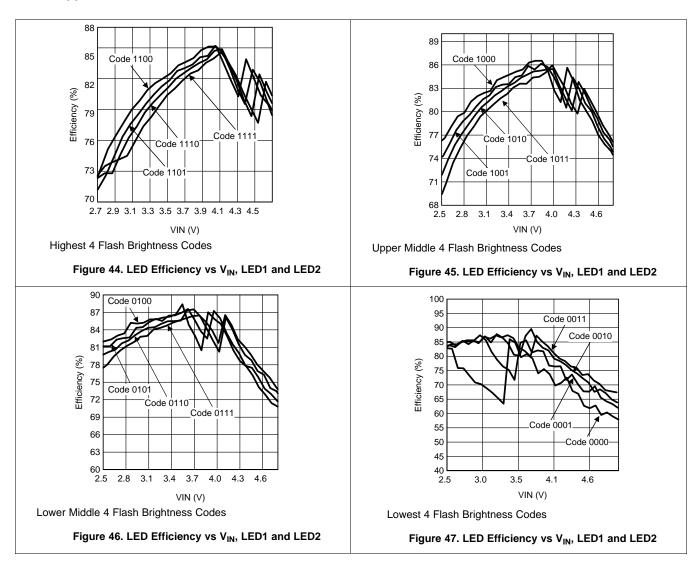

## 6.7 Typical Characteristics

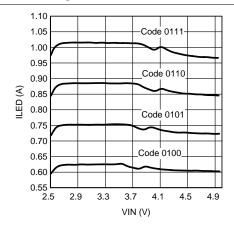

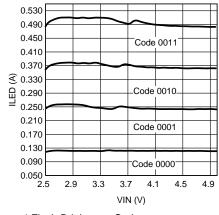

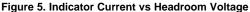

$V_{IN} = 3.6 \text{ V}, \ C_{OUT} = 10 \ \mu\text{F}, \ C_{IN} = 10 \ \mu\text{F}, \ L = 1 \ \mu\text{H} \ (TOKO \ FDSD0312-1R0, \ R_L = 43 \ m\Omega), \ T_A = 25^{\circ}\text{C}, \ I_{LED} = I_{LED1} + I_{LED2}, \ unless = 10 \ \mu\text{F}, \ L = 1 \ \mu\text{H} \ (TOKO \ FDSD0312-1R0, \ R_L = 43 \ m\Omega), \ T_A = 25^{\circ}\text{C}, \ I_{LED} = I_{LED1} + I_{LED2}, \ unless = 10 \ \mu\text{F}, \ L = 1 \ \mu\text{H} \ (TOKO \ FDSD0312-1R0, \ R_L = 43 \ m\Omega), \ T_A = 25^{\circ}\text{C}, \ I_{LED} = I_{LED1} + I_{LED2}, \ unless = 10 \ \mu\text{F}, \ L = 10$ otherwise noted.

Figure 1. I<sub>LED</sub> vs V<sub>IN</sub>, I<sub>LED1</sub> + I<sub>LED2</sub>

Upper Middle 4 Flash Brightness Codes

Figure 2. I<sub>LED</sub> vs V<sub>IN</sub>, I<sub>LED1</sub> + I<sub>LED2</sub>

Lower Middle 4 Flash Brightness Codes

Figure 3. I<sub>LED</sub> vs V<sub>IN</sub>, I<sub>LED1</sub> + I<sub>LED2</sub>

Lowest 4 Flash Brightness Codes

Figure 4.  $I_{LED}$  vs  $V_{IN}$ ,  $I_{LED1} + I_{LED2}$

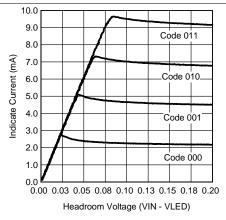

$V_{LED} = 2.5 V$ Indicate Codes 000 - 011

Figure 6. Indicator Currents vs Headroom Voltage

## **Typical Characteristics (continued)**

$V_{IN} = 3.6 \text{ V, } C_{OUT} = 10 \text{ } \mu\text{F, } C_{IN} = 10 \text{ } \mu\text{F, } L = 1 \text{ } \mu\text{H (TOKO FDSD0312-1R0, } R_L = 43 \text{ } m\Omega), T_A = 25^{\circ}\text{C, } I_{LED} = I_{LED1} + I_{LED2}, \text{ unless otherwise noted.}$

Copyright © 2011–2016, Texas Instruments Incorporated

# TEXAS INSTRUMENTS

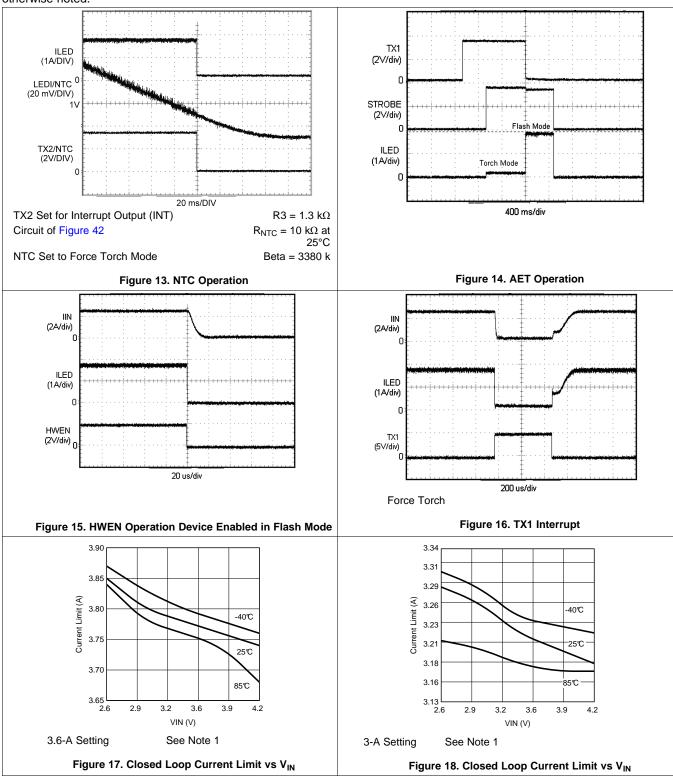

## **Typical Characteristics (continued)**

$V_{IN} = 3.6 \text{ V}, C_{OUT} = 10 \text{ } \mu\text{F}, C_{IN} = 10 \text{ } \mu\text{F}, L = 1 \text{ } \mu\text{H} \text{ (TOKO FDSD0312-1R0, } R_L = 43 \text{ } m\Omega), T_A = 25 ^{\circ}\text{C}, I_{LED} = I_{LED1} + I_{LED2}, unless otherwise noted.$

Submit Documentation Feedback

Copyright © 2011–2016, Texas Instruments Incorporated

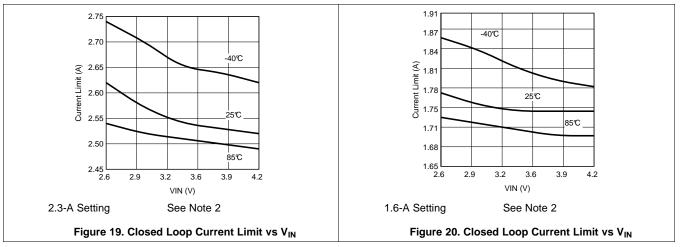

## **Typical Characteristics (continued)**

$V_{IN}=3.6~V,~C_{OUT}=10~\mu F,~C_{IN}=10~\mu F,~L=1~\mu H$  (TOKO FDSD0312-1R0,  $R_L=43~m\Omega$ ),  $T_A=25^{\circ}C,~I_{LED}=I_{LED1}+I_{LED2},~unless$  otherwise noted.

- (1) The typical curve for current limit is measured in closed loop using Figure 41, and increasing I<sub>OUT</sub> until the peak inductor current stops increasing. The value given in Electrical Characteristics is measured open loop and is found by forcing current into SW until the current limit comparator threshold is reached. Closed loop data appears higher due to the delay between the comparator trip point and the NFET turning off. This delay allows the closed loop inductor current to ramp higher after the trip point by approximately 20 ns x V<sub>IN</sub>/L.

- (2) The typical curve for overvoltage protection (OVP) is measured in closed loop using Figure 41. The OVP value is found by forcing an open circuit in the LED1 and LED2 path and recording the peak value of V<sub>OUT</sub>. The value given in Electrical Characteristics is found in an open loop configuration by ramping the voltage at OUT until the OVP comparator trips. The closed loop data can appear higher due to the stored energy in the inductor being dumped into the output capacitor after the OVP comparator trips. Worst case is an open circuit condition where the output voltage can continue to rise after the OVP comparator trips by approximately I<sub>IN</sub> × sqrt(L/C<sub>OUT</sub>).

Product Folder Links: LM3560

Copyright © 2011-2016, Texas Instruments Incorporated

## 7 Detailed Description

#### 7.1 Overview

The LM3560 is a high-power white-LED flash driver capable of delivering up to 2 A of LED current into a single LED or up to 1 A into two parallel LEDs. The device incorporates a 2-MHz constant frequency, a synchronous boost converter, and two high-side current sources to regulate the LED current over the 2.5-V to 5.5-V input voltage range.

During operation when the output voltage is greater than  $V_{IN}-150~\text{mV}$  the boost converter switches and maintains at least 300 mV across both current sources (LED1 and LED2). This minimum headroom voltage ensures that the current sources remain in regulation. When the input voltage rises above the LED voltage + current source headroom voltage, the device stops switching and turns the PFET on continuously (pass mode). In pass mode the difference between  $(V_{IN}-I_{LED}\times R_{ON\_P})$  and the voltage across the LEDs is dropped across the current sources.

Four hardware control pins provide control of the LM3560. These include a hardware flash enable (STROBE), dual flash Interrupt inputs (TX1 and TX2) designed to interrupt the flash pulse during high battery current conditions, and a logic high hardware enable (HWEN) that can be pulled low to rapidly place the device into shutdown. Additional features of the LM3560 include an internal 4-bit ADC for LED voltage monitoring, an internal comparator for LED thermal sensing via an external NTC thermistor, an input voltage monitor that can reduce the flash current during input undervoltage conditions, a low-power message indicator LED current source, and a mode for utilizing the flash LEDs as a privacy indicator.

Control of the LM3560 is done via an  $I^2C$ -compatible interface. This includes adjustment of the flash and torch current levels, adjustment of the indicator LED currents, changing the flash timeout duration, changing the switch current limit, and reading back the ADC results. Additionally, there are 8 flag bits that indicate flash current timeout, LED overtemperature, LED failure (LED short or output OVP condition), device thermal shutdown,  $V_{IN}$  undervoltage condition,  $V_{IN}$  flash monitor undervoltage condition, and the occurrence of a TX1 or TX2 interrupt.

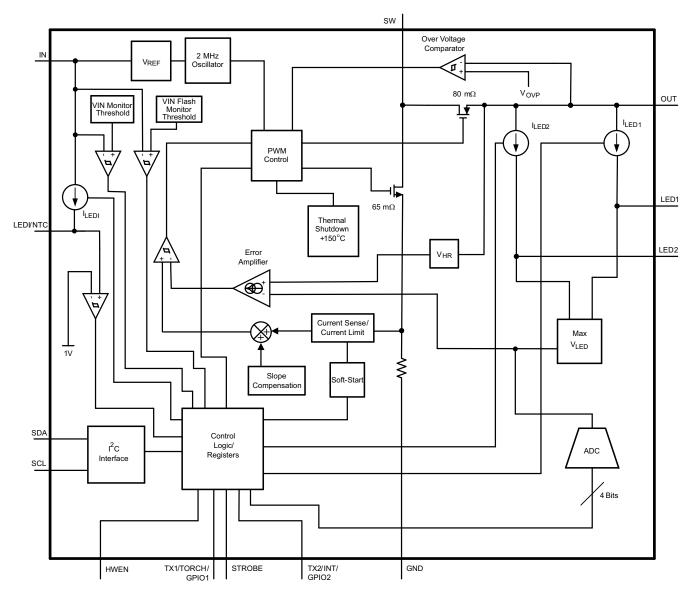

## 7.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

#### 7.3 Feature Description

## 7.3.1 Power Amplifier Synchronization (Tx1)

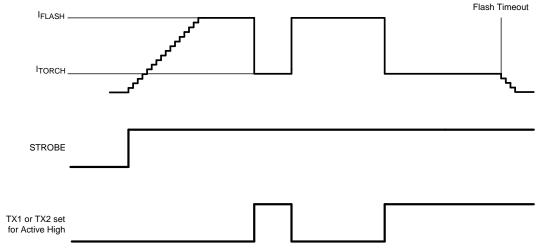

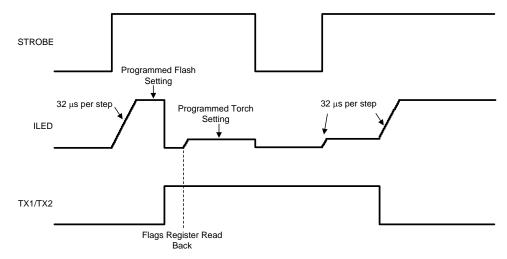

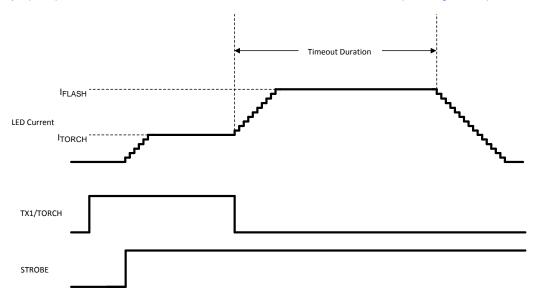

The TX1/TORCH/GPIO1 pin has a triple function. With configuration register 1 bit [7] = 0 (default) TX1/TORCH/GPIO1 is a power amplifier synchronization input (TX1 mode). This mode is designed to reduce the flash LED current when TX1 is driven high (active high polarity) or driven low (active low polarity). When the LM3560 is engaged in a flash event and TX1/TORCH is driven high, the active current sources (LED1 and/or LED2) are forced into torch mode at the programmed torch current setting. If TX1 is then pulled low before the flash pulse terminates, the LED current returns to the previous flash current level. At the end of the flash timeout, whether the TX1/TORCH pin is high or low, the LED current turns off.

The polarity of TX1 can be changed from active high to active low by writing a 0 to bit [5] of Configuration Register 1. With this bit set to 0 the LM3560 is forced into torch mode when TX1/TORCH is pulled low. Figure 21 details the functionality of the TX1 Interrupt.

#### 7.3.1.1 TX1 Shutdown

TX1 also has the capability to force shutdown. Bit [4] of configuration register 2 set to a 1, changes TX1 from a force torch when active to a force shutdown when active. For example, if TX1/TORCH/GPIO1 is configured for TX1 mode with active high polarity, and bit[4] of configuration register 2 is set to 1, then when TX1 is driven high, the active current sources (LED1 and/or LED2) is forced into shutdown. Once the active current sources are forced into shutdown by activating TX1, the current sources can only be re-enabled into flash mode if TX1 is pulled low and the flags register is read back. If only the flags register is read back and TX1 is kept high the device is re-enabled into torch mode and not shutdown. This occurs because the TX1 shutdown feature is an edge-triggered event. With active high polarity the TX1 shutdown requires a rising edge at TX1 in order to force the current source into shutdown. Once shut down, it takes a read back of the flags register and another rising edge at TX1 to force shutdown again. Figure 34 details the different responses of the TX1 shutdown mode.

Figure 21. TX1 or TX2 Interrupt (Force Torch) Response

## 7.3.2 Independent LED Control

Bits [4:3] of the eenable register provide for independent turnon and turnoff of the LED1 or LED2 current sources. Once enabled, the LED current is adjusted by writing to the torch brightness or flash brightness registers depending on whether flash or torch mode is selected. Both the torch brightness and the flash brightness registers provide for independent current programming for the LED currents in either LED1 or LED2. (See Torch Brightness Register Descriptions (Address 0xA0) and Flash Brightness Register (Address 0xB0).)

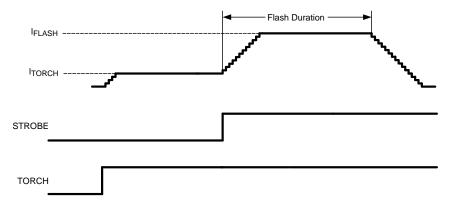

#### 7.3.3 Hardware Torch

With configuration register 1 Bit [7] = 1, TX1/TORCH/GPIO1 is configured as a hardware torch mode enable. In this mode, a high at TX1/TORCH turns on the LED current at the programmed torch current setting. The STROBE input and I<sup>2</sup>C-enabled flash takes precedence over torch mode. In hardware torch mode, both LED1 and LED2 current sources turn off after a flash event and configuration register 1 Bit [7] is reset to 0. In this situation, to re-enter torch mode via hardware torch, the hardware torch enable bit (configuration register 1 Bit [7]) must be reset to 1. Figure 22 details the functionality of hardware torch mode.

Figure 22. Hardware Torch Mode

#### 7.3.4 Fault Protections

#### 7.3.4.1 Overvoltage Protection

The output voltage is limited to typically 5 V (5.075 V maximum). In situations such as the current source open, the LM3560 raises the output voltage to try to keep the LED current at its target value. When  $V_{OUT}$  reaches 5 V, the overvoltage comparator trips and turns off both the internal NFET and PFET. When  $V_{OUT}$  falls below 4.8 V (typical), the LM3560 begins switching again.

#### 7.3.4.2 Current Limit

The LM3560 features 4 selectable current limits: 1.6 A, 2.3 A, 3 A, and 3.6 A. These are programmable through the I<sup>2</sup>C-compatible interface via bits [6:5] of the flash duration register. When the current limit is reached, the LM3560 stops switching for the remainder of the switching cycle.

Because the current limit is sensed in the NMOS switch there is no mechanism to limit the current when the device operates in pass mode. In situations where there could potentially be large load currents at OUT, and the LM3560 device is operating in pass mode, the load current must be limited to 3 A. In boost mode or pass mode if  $V_{OUT}$  falls below approximately 2.3 V, the device stops switching and the PFET operates as a current source, limiting the current to typically 350 mA. This prevents damage to the LM3560 and excessive current draw from the battery during output short-circuit conditions.

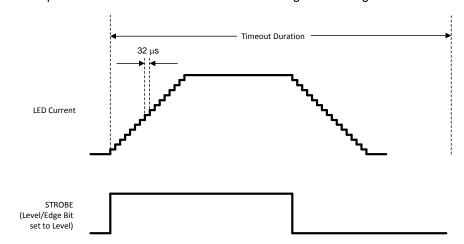

#### 7.3.4.3 Flash Timeout

The flash-timeout period sets the amount of time that the flash current is being sourced from current sources LED1 and LED2. Bits [4:0] of the flash duration register set the flash-timeout period. There are 32 different flash-timeout durations in steps of 32 ms giving a flash timeout range of 32 ms to 1024 ms (see Table 15).

#### 7.3.4.4 Indicator LED/Thermistor (LED1/NTC)

The LEDI/NTC pin serves a dual function: either as a programmable LED message indicator driver or as a comparator input for negative temperature coefficient (NTC) thermistors.

Product Folder Links: LM3560

Submit Documentati

## 7.3.4.4.1 Message Indicator Current Source (LEDI/NTC)

LEDI/NTC is configured as a message indicator current source by setting configuration register 1 bit [4] = (0) default. The indicator current source is enabled/disabled via the enable register bit [6] = (1). Bit [7] of the enable register enables the message Indicator in blink mode. If the message indicator is set for blinking mode, the pattern programmed into the indicator register, and indicator blinking register is output on the Indicator current source.

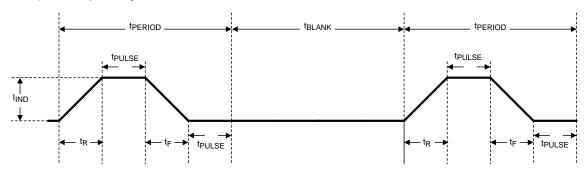

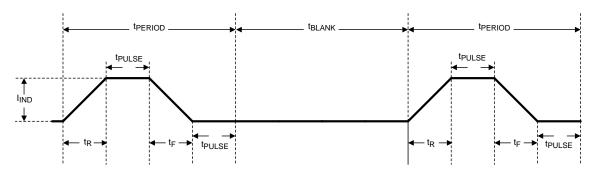

The indicator blinking register controls the following (see Table 6):

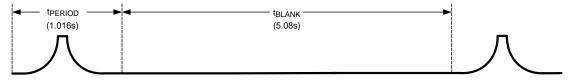

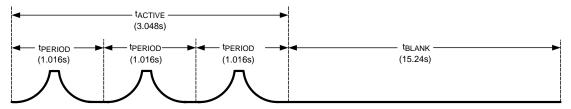

- 1. Number of blank periods (BLANK #). This has 16 settings.  $t_{BLANK} = t_{ACTIVE} \times BLANK\#$ , where  $t_{ACTIVE} = t_{PERIOD} \times PERIOD\#$

- 2. Pulse width (t<sub>PULSE</sub>) has 16 settings between 0 and 480 ms in steps of 32 ms. The pulse width is the duration that the indicator current is at its programmed set point at the end of the ramp-up time.

The indicator register controls the following (see Table 5):

- 1. Indicator current level (I<sub>IND</sub>). There are 8 indicator current levels from 2.25 mA to 18 mA in steps of 2.25 mA.

- 2. Number of periods (PERIOD #). This has 8 steps. A period ( $t_{PERIOD}$ ) is found by  $t_{PERIOD} = t_R + t_F + 2 \times t_{PULSE}$ . (see Figure 23 for indicator timing).

- 3. Ramp times ( $t_R$  or  $t_F$ ) for turnon and turnoff of the indicator current source. Four programmable times of 78 ms, 156 ms, 312 ms, and 624 ms are available. The ramp times apply for both ramp-up and ramp-down and are not independently changeable.

Figure 23. Message Indicator Timing Diagram

#### 7.3.4.4.1.1 Message Indicator Example 1 (Single Pulse With Dead Time):

As an example, to set up the message indicator for a 312-ms ramp-up and ramp-down, 192-ms pulse width, and 1 pulse followed by a 5-s delay. The indicator settings is as follows.  $t_R = t_F = 312$  ms,  $t_{WIDTH} = 192$  ms ( $t_{PERIOD} = 312$  ms × 2 + 192 ms × 2 = 1016 ms). BLANK# setting is: 5s/1016 ms × 1 (PERIOD# = 1). Giving a BLANK# setting of 5. The resulting waveform appears as:

Figure 24. Message Indicator Example 1

## 7.3.4.4.1.2 Message Indicator Example 2 (Multiple Pulses With Dead Time):

Another example has the same  $t_R$ ,  $t_F$ ,  $t_{PULSE}$ , and  $t_{BLANK}$  times as before, but this time the PERIOD# is set to 3. Now the  $t_{ACTIVE}$  time is  $t_{PERIOD} \times 3 = 1016$  ms  $\times 3 = 3048$  ms. This results in a blank time of  $t_{BLANK} = t_{ACTIVE} \times BLANK# = 3.048$  s  $\times 5 = 15.24$  s

Figure 25. Message Indicator Example 2

## 7.3.4.4.2 Updating The Message Indicator

The best way to update the message indicator is to disable the message indicator output via the enable register bit [6], then write the new sequence to the indicator register and/or indicator blinking register, and then re-enable the message indicator. Updating the indicator registers while it is active can lead to long delays between pattern changes. This is especially true if the PERIOD#, or BLANK# setting is changed from a high setting to a lower setting.

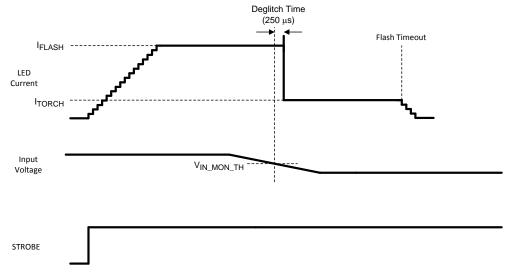

#### 7.3.5 Input Voltage Monitor

The LM3560 has an internal comparator at IN which monitors the input voltage and can force the LED current into torch mode or into shutdown if  $V_{IN}$  falls below the programmable  $V_{IN}$  monitor threshold. Bit 0 in the  $V_{IN}$  monitor register enables or disables this feature. When enabled, Bits [2:1] program the 4 adjustable thresholds of 2.9 V, 3 V, 3.1 V, and 3.2 V. Bit 3 in configuration register 2 selects whether a  $V_{IN}$  monitor event forces torch mode or forces LED1 and/or LED2 into shutdown. See Table 11 for additional information. When the input voltage monitor is active, and  $V_{IN}$  falls below the programmed  $V_{IN}$  monitor threshold, the LEDs turns off or is forced into the torch current setting. To reset the LED current to its previous level, two things must occur. First,  $V_{IN}$  must go above the  $V_{IN}$  monitor threshold, and the flags register must be read back. See Figure 26 for the  $V_{IN}$  monitor timing waveform.

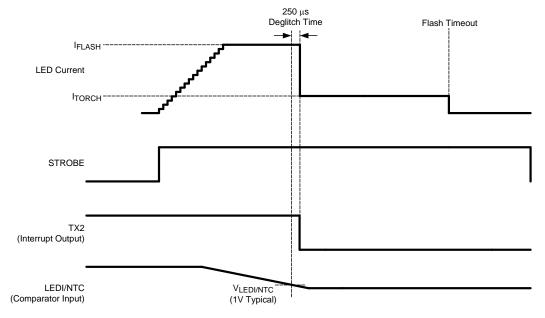

To avoid noise from falsely triggering the  $V_{IN}$  monitor, this mode incorporates a 250 µs de-glitch timer. With the  $V_{IN}$  monitor active,  $V_{IN}$  must go below the  $V_{IN}$  monitor threshold ( $V_{IN\_TH}$ ), and remain below it, for 250 µs before the LEDs are forced into torch mode (or shutdown) and the  $V_{IN}$  monitor flag is written.

Figure 26. V<sub>IN</sub> Monitor Waveform

Copyright © 2016, Texas Instruments Incorporated

- (1) For the V<sub>IN</sub> flash monitor test, when the 2-A flash starts up the voltage at IN begins to drop via the rising input current ramp and the source resistance RS As soon as the input voltage crosses the programmed V<sub>IN</sub> flash monitor threshold the flash current ramp is stopped, and the LM3560 flashes at the reduced current

- (2) For the  $V_{IN}$  monitor test, with a 2-A flash current the voltage at IN is  $V_{BATT} I_{BATT} \times R_S$ . When Q1 turns on the added load causes  $V_{IN}$  to drop by the additional current ( $V_{IN}$  / RL) which flows through  $R_S$ . When  $V_{IN}$  drops the programmed VIN monitor threshold is crossed, and the flash current pulse steps to the programmed torch current level causing  $V_{IN}$  to step up.

Figure 27. V<sub>IN</sub> Monitor/V<sub>IN</sub> Flash Monitor Test Circuit

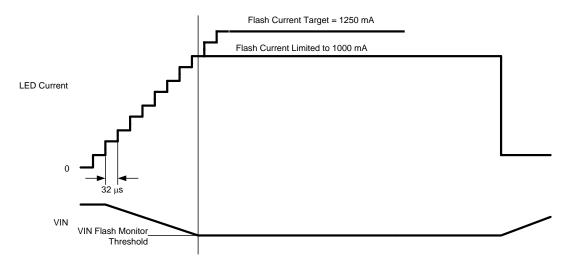

#### 7.3.5.1 Input Voltage Flash Monitor (Flash Current Rising)

A second comparator at the IN pin is available to monitor the input voltage during the flash current turnon (Input voltage flash monitor). Bit [3] of the  $V_{IN}$  monitor register enables/disables this feature. With this bit set to 1, the  $V_{IN}$  flash monitor is active, and bits [5:4] of the  $V_{IN}$  monitor register program the 4 selectable thresholds of (2.9 V, 3 V, 3.1 V, and 3.2 V). The  $V_{IN}$  flash monitor operates as follows: during flash current turnon the current sources transitions through each of the lower flash current levels until the target flash current is reached. With the input voltage flash monitor active, if during the flash current turnon the input voltage falls below the  $V_{IN}$  flash monitor threshold, the flash current is stopped at the level that the current ramp had risen to, at the time of the  $V_{IN}$  flash monitor event. The  $V_{IN}$  flash monitor only operates during the ramping up of the flash LED current.

The  $V_{IN}$  flash monitor ignores the first 2 flash codes during the flash current turnon. As a result, if the  $V_{IN}$  flash monitor is enabled and  $V_{IN}$  were to fall below the  $V_{IN}$  flash threshold as the LED current ramps up through either of the first two levels, then the flash pulse would not be halted until code number 3 (168.75 mA per current source).

To avoid noise from falsely triggering the  $V_{IN}$  flash monitor, this mode incorporates an 8µs de-glitch timer as well as an internal analog filter at the input of the VIN flash monitor comparator. With the  $V_{IN}$  flash monitor active,  $V_{IN}$  must go below the  $V_{IN}$  flash monitor threshold ( $V_{IN\_FLASH}$ ), and remain below it, for 8 µs before the flash current ramp is halted and the  $V_{IN}$  flash monitor flag is written.

## 7.3.6 Last Flash Register

Once the  $V_{IN}$  flash monitor is tripped, the flash code that corresponded to the LED current at which the flash current ramp was halted is written to the last flash register. The last flash register is a read-only register and has the lower 4 bits available to latch the code for LED1 and the upper 4 bits to latch the code for LED2.

For example, suppose that the LM3560 is set up for a single LED with a target flash current of 1250 mA and the  $V_{IN}$  flash monitor is enabled with the  $V_{IN}$  flash monitor threshold set to 3 V ( $V_{IN}$  monitor register bits [5:4] = 0, 1). When the STROBE input is brought high, the LED current begins ramping up through the torch and flash current codes at 32 µs/code. As the input current increases, the input voltage at the IN pin of the LM3560 device begins to fall due to the source impedance of the battery. By the time the LED current has reached 1000 mA (code 0x77 or 500 mA per current source),  $V_{IN}$  falls below 3 V. The  $V_{IN}$  flash monitor then stops the flash current ramp, and the LM3560 continues to proceed with the flash pulse, but at 1000 mA instead of 1250 mA. Figure 28 details this sequence.

Figure 28. V<sub>IN</sub> Flash Monitor Example

#### 7.3.7 LED Voltage Monitor

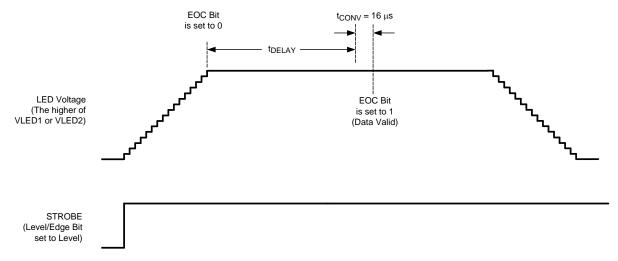

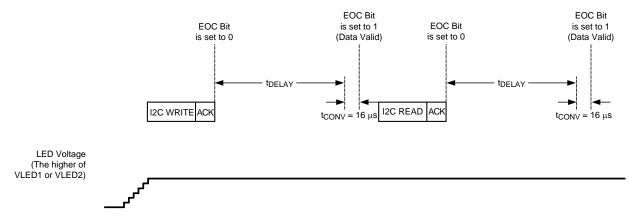

The LM3560 includes a 4-bit ADC which monitors the LED forward voltage ( $V_{LED}$ ) and stores the digitized value in bits [3:0] of the  $V_{LED}$  monitor register. The highest voltage of  $V_{LED1}$  or  $V_{LED2}$  is automatically sensed and that becomes the sample point for the ADC. Bit 5, the ADC shutdown bit, enables/disables the ADC with the default state set to enable (bit [5] = 0).

#### 7.3.8 ADC Delay

The ADC delay register provides for a programmable delay from 250  $\mu$ s to 8 ms in steps of 250  $\mu$ s. This delay is the delay from when the EOC bit goes low to when the V<sub>LED</sub> monitor samples the LED voltage. In automatic mode the EOC bit goes low when the flash LED current hits its target. In Manual mode the EOC bit goes low at the end of a read back of the V<sub>LED</sub> monitor register (or when the manual mode bit (bit 4) is re-written with a 1).

Figure 29. V<sub>LED</sub> Monitor Automatic Mode

Copyright © 2011–2016, Texas Instruments Incorporated

Figure 30. V<sub>LED</sub> Monitor Manual Mode

#### 7.3.9 Flags Register and Fault Indicators

Eight fault flags are available in the LM3560. These include a flash timeout, a thermal shutdown, an LED failure flag (LED shorted or output going OVP indicating LED open), an LED thermal flag (NTC threshold tripping), a  $V_{IN}$  monitor flag, and a  $V_{IN}$  flash monitor flag. Additionally, two LED interrupt flag bits (TX1 interrupt and TX2 interrupt) are set when the corresponding interrupt is activated. Reading back a 1 indicates the flagged event has happened. A read of the flags register resets these bits.

#### 7.3.9.1 Flash Timeout

The timeout (TO) flag, (bit [0] of the flags register) reads back a 1 if the LM3560 is active in flash mode and the timeout period expires before the flash pulse is terminated. The flash pulse can be terminated before the timeout period expires by pulling the STROBE pin low (with enable register bit [5] = 0), or by writing a (0,0) to bit [1:0] of the enable register. The TO flag is reset to 0 by pulling HWEN low, removing power to the LM3560, or reading the flags register.

#### 7.3.9.2 Thermal Shutdown

The LM3560 features a thermal shutdown threshold of typically 150°C. When the devices die temperature reaches 150°C the active current sources (LED1 and/or LED2) shuts down, and the TSD flag in the flags register is written high. The device cannot be started up again until the flags register is read back. Once the flags register is read back either current source can be re-enabled into privacy, torch, or flash mode. The thermal shutdown (TSD) circuitry has an internal 250 µs de-glitch timer which helps prevent unwanted noise from falsely triggering a TSD event. However, when the LM3560 is in boost mode at higher flash currents, the de-glitch timer can get reset by the high currents in the GND of the LM3560 device. As a result the internal de-glitch timer of the thermal shutdown can be reset before the TSD event can get latched in. This prevents a TSD event from being triggered until the flash pulse of the LM3560 reaches the end of the flash duration, when the noisy currents have dropped to a lower level. However, once the noise is lower, and a TSD event is triggered, the next flash pulse is not allowed until the flags register is read back. In pass mode the boost switcher is off and the lower noise environment allows the devices TSD circuitry to shut down immediately when the die temperature reaches 150°C.

#### 7.3.9.3 **LED Fault**

The LED fault flag (bit 2 of the flags register) reads back a 1 if the part is active in flash or torch mode and either LED1 or LED2 experience an open or short condition. An LED open condition is signaled if the OVP threshold is crossed at the OUT pin while the device is in flash, torch, or privacy mode. An LED short condition is signaled if the voltage at LED1 or LED2 goes below 500 mV while the device is in flash, torch, or privacy mode. In an LED open condition there is a 2-µs deglitch time from when the output voltage crosses the OVP threshold to when the LED fault flag is triggered. In an LED short condition there is a 250-µs deglitch time from when the LED voltage falls below 500 mV until the LED fault flag is set. The LED fault flag can only be reset to 0 by pulling HWEN low, cycling power, or by removing the fault condition and reading back the flags register.

#### 7.3.9.4 TX1 and TX2 Interrupt Flags

The TX1 and TX2 interrupt flags (bits [3] and [4]) indicate an interrupt event has occurred on the respective TX inputs. Bit 3 reads back a 1 if TX1 is in TX mode and there has been a TX1 event since the last read of the flags register. Bit 4 reads back a 1 if TX2 is in TX mode and there has been a TX2 event since the last read of the flags register. A read of the flags register automatically resets these bits. A TX event on TX1 or TX2, can be a high-to-low transition or a low-to-high transition depending on the setting of the TX1 and TX2 polarity bits (see Configuration Register 1 (Address 0xE0) bits [6:5]).

#### 7.3.9.5 LED Thermal Fault (NTC Flag)

The NTC flag (bit [5] of the flags register) reads back a 1 if the LM3560 is active in flash or torch mode, the device is in NTC mode, and the voltage at LEDI/NTC has fallen below  $V_{TRIP}$  (1V typical). When this has happened, and the LM3560 has been forced into torch mode or LED shutdown (depending on the state of configuration register 2 bit [1), the flags register must be read, and  $V_{LEDI/NTC}$  must go above 1 V in order to place the device back in normal operation. (see *NTC Mode* for more details).

## 7.3.9.6 V<sub>IN</sub> Flash Monitor Fault

The  $V_{IN}$  flash monitor flag (bit [6] of the flags register) reads back a 1 if the  $V_{IN}$  flash monitor is enabled and  $V_{IN}$  falls below the programmed  $V_{IN}$  flash monitor threshold. This flag must be read back in order to resume normal operation after the LED current has been forced to the lower flash current setting.

## 7.3.9.7 V<sub>IN</sub> Monitor Fault

The  $V_{IN}$  monitor flag (bit [7] of the flag register) reads back a 1 when the VIN monitor is enabled and  $V_{IN}$  falls below the programmed  $V_{IN}$  monitor threshold. This flag must be read back and  $V_{IN}$  must go above the  $V_{IN}$  monitor threshold in order to resume normal operation after the LED current has been forced to torch mode or turned off due to a  $V_{IN}$  monitor event.

#### 7.4 Device Functional Modes

## 7.4.1 Start-Up (Enabling the Device)

Turnon of the LM3560 is done through bits [1:0] of the enable register. These bits enable the device in torch mode, flash mode, or privacy Indicate mode. Additionally, bit 6 of the enable register enables the message indicator at the LEDI/NTC pin. On start-up, when  $V_{OUT}$  is less than  $V_{IN}$ , the internal synchronous PFET turns on as a current source and delivers 350 mA to the output capacitor. During this time both current sources (LED1, and LED2) are off. When the voltage across the output capacitor reaches 2.2 V the current sources can turn on. At turnon the current sources step through each FLASH and TORCH level until their target LED current is reached (32  $\mu$ s/step). This gives the device a controlled turnon and limits inrush current from the  $V_{IN}$  supply.

#### 7.4.2 Pass Mode

On turnon, when the output voltage charges up to  $V_{IN}$  – 150 mV, the LM3560 operates in either pass mode or boost mode. If the voltage difference between  $V_{OUT}$  and  $V_{LED}$  is less then 300 mV, the device operates in boost mode. If the difference between  $V_{OUT}$  and  $V_{LED}$  is greater then 300 mV, the device operates in pass mode. In pass mode the boost converter stops switching and the synchronous PFET turns fully on bringing  $V_{OUT}$  up to  $V_{IN}$  –  $I_{IN}$  ×  $R_{PMOS}$  where  $R_{PMOS}$  = 80 m $\Omega$ . In pass mode the inductor current is not limited by the peak current limit. In this situation the output current must be limited to 3 A.

#### 7.4.3 Flash Mode

In flash mode the LED current sources (LED1 and LED2) each provide 16 different current levels from typically 62.5 mA (total) to 2 A (total) in steps of 62.5 mA. The flash currents are adjusted via the flash brightness register. Flash mode is activated by writing a (1, 1) to bits [1:0] of the enable register or by enabling the hardware flash input (STROBE) via bit [2] of Configuration Register 1, and then pulling the STROBE pin high (high polarity). Once the flash sequence is activated the active current sources (LED1 and/or LED2) ramps up to their programmed flash current level by stepping through all torch and flash levels (32 µs/step) until the programmed current is reached.

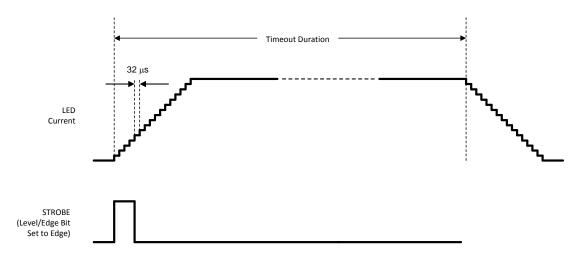

Bit [5] of the enable register (STROBE level/edge bit) determines how the flash pulse terminates after STROBE goes high. With the level/edge bit = 1, the flash current only terminates when it reaches the end of the flash timeout period. With the level/edge bit = 0, flash mode can be terminated by pulling STROBE low, programming bits [1:0] of the enable register with (0,0), or by allowing the flash timeout period to elapse. If the level/edge bit = 0 and STROBE is toggled before the end of the flash timeout period, the timeout period resets. Figure 31 and Figure 32 detail the flash pulse termination for the different level/edge bit settings.

Figure 31. LED Current for Strobe (Level Triggered, Enable Register Bit 5 = 0)

2 Submit Documentation Feedback

Copyright © 2011–2016, Texas Instruments Incorporated

## **Device Functional Modes (continued)**

Figure 32. LED Current for Strobe (Edge Triggered, Enable Register Bit 5 = 1)

After the flash pulse terminates, either by a flash timeout, pulling STROBE low, or disabling it via the  $I^2C$ -compatible interface, LED1 and LED2 turn completely off. This happens even when torch is enabled via the  $I^2C$ -compatible interface and the flash pulse is turned on by toggling STROBE. After a flash event ends, bits [1:0] of the enable register are automatically reset with (0, 0). The exception occurs when the privacy terminate bit is low (bit [3]) in the privacy register. In this case, the specific current source that is enabled for privacy mode turns back on after the flash pulse.

#### 7.4.4 Torch Mode

In torch mode the current sources LED1 and LED2 each provide 8 different current levels (*Torch Brightness Register Descriptions (Address 0xA0)*). Torch mode is activated by setting enable register bits [1:0] to (1, 0). Once torch mode is enabled, the current sources ramps up to the programmed torch current level by stepping through all of the torch currents at (32 µs/step) until the programmed torch current level is reached.

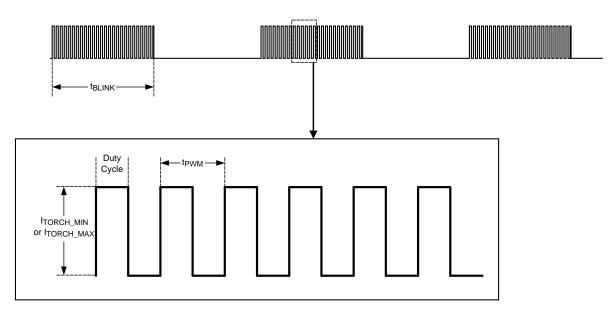

## 7.4.5 Privacy Indicator Mode

The current sources (LED1 and/or LED2) can also be used as a privacy indicator before and after flash mode. Privacy indicate mode is enabled by setting the enable register bit [1:0] to (0, 1). Privacy mode is configured via the privacy register. This allows the selection of which current source to use as the privacy indicator (either LED1, LED2, or both), whether or not the privacy indicate mode turns off at the end of the flash pulse, the 3 selectable privacy blink periods ( $t_{BLINK}$ ), and the 8 duty cycle settings for the privacy indicator average current.

The intensity of the LEDs in privacy indicate mode is set by PWM controlling either the lowest torch current level (31.25 mA per current source) or the highest torch current level (250 mA per current source). Bit [2] in the enable register selects between these two levels. Bits [2:0] in the privacy register select the 8 different duty cycles of 10%, 20%, 30%, 40%, 50%, 60%, 70%, and 80%. This enables privacy mode to have a PWM-controlled torch current with a wide number of values (see Table 1). The privacy blink options ( $t_{\rm BLINK}$ ) are set via bit [7:6] of the privacy register. Selectable options are 128 ms, 256 ms, 512 ms, or always on. The blink pulse period is set to 2 x  $t_{\rm BLINK}$ . Figure 33 details the timing for the privacy indicate mode timing on ILED1 or ILED2.

## **Device Functional Modes (continued)**

- t<sub>BLINK</sub> set via bits [7:6] of Privacy Register

- Duty cycle set via bits [2:0] of Privacy Register

- t<sub>PWM</sub> set via bits[2:0] of the Privacy PWM Register

Figure 33. Privacy Indicate Timing

Table 1. Privacy Indicate (With PWM Torch) Possible Current Settings<sup>(1)</sup>

| PRIVACY CURRENT SETTING<br>(ENABLE REGISTER BIT [2])<br>0 = 31.2 5mA peak<br>1 = 250 mA peak | PRIVACY INDICATE DUTY CYCLE PRIVACY REGISTER BITS [2:0] see (Table 4) | ILED1 or ILED2<br>(SINGLE LED) |

|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------|

| 0                                                                                            | 000                                                                   | 3.125 mA                       |

| 0                                                                                            | 001                                                                   | 6.25 mA                        |

| 0                                                                                            | 010                                                                   | 9.375 mA                       |

| 0                                                                                            | 011                                                                   | 12.5 mA                        |

| 0                                                                                            | 100                                                                   | 15.625 mA                      |

| 0                                                                                            | 101                                                                   | 18.75 mA                       |

| 0                                                                                            | 110                                                                   | 21.875 mA                      |

| 0                                                                                            | 111                                                                   | 25 mA                          |

| 1                                                                                            | 000                                                                   | 25 mA                          |

| 1                                                                                            | 001                                                                   | 50 mA                          |

| 1                                                                                            | 010                                                                   | 75 mA                          |

| 1                                                                                            | 011                                                                   | 100 mA                         |

| 1                                                                                            | 100                                                                   | 125 mA                         |

| 1                                                                                            | 101                                                                   | 150 mA                         |

| 1                                                                                            | 110                                                                   | 175 mA                         |

| 1                                                                                            | 111                                                                   | 200 mA                         |

(1) The listed current is with 1 current source active

#### 7.4.6 **GPIO1 Mode**

With bit [0] of the GPIO register set to 1, the TX1/TORCH/GPIO1 pin is configured as a logic I/O. In this mode the TX1/TORCH/GPIO1 pin is readable and writable as a logic input/output via bits [2:1] of the GPIO register (see GPIO Register (Address 0x20) for programming the GPIO1 output).

#### 7.4.7 TX2/INT/GPIO2

The TX2/INT/GPIO2 pin has a triple function. In TX2 mode (default) the TX2/INT/GPIO2 pin is an active high flash interrupt. With GPIO register bit [3] = 1 the TX2/INT/GPIO2 pin is configured as general purpose logic I/O. With GPIO register bit [6] = 1, and with the TX2/INT/GPIO2 pin configured as a GPIO2 output, the TX2/INT/GPIO2 pin is an interrupt output.

#### 7.4.8 TX2 Mode

In TX2 mode, when configuration register 1, bit [6] = 0, TX2 is an active low flash interrupt. Under this condition when the LM3560 is engaged in a flash event and TX2 is pulled low, the active current source (LED1 and/or LED2) are forced into torch mode. In TX2 mode with configuration register 1, bit [6] = 1, TX2 is configured for active high polarity. Under this condition, when the LM3560 is engaged in a flash event and TX2 is driven high, the active current source (LED1 and/or LED2) are forced into torch mode. During a TX2 interrupt event, if the TX2 input is disengaged, the LED current returns to the previous flash current level. Figure 21 details the functionality of the TX2 interrupt.

#### 7.4.8.1 TX2 Shutdown

TX2 also has the capability to force shutdown. When bit [0] of configuration register 2 is set to a 1, TX2 forces shutdown when active. For example, if TX2 is configured for TX2 mode with active high polarity, and bit [0] of Configuration Register 2 is set to 1 then when TX2 is driven high, the active current sources (LED1 and/or LED2) is forced into shutdown. Once the active current sources are forced into shutdown by activating TX2, the current sources can only be re-enabled in flash mode if TX2 is pulled low and the flags register is read back. If only the flags register is read back and TX2 is kept high, the device is re-enabled into torch mode and not shut down. This occurs because the TX2 shutdown feature is an edge-triggered event. With active high polarity the TX2 shutdown requires a rising edge at TX2 in order to force the current sources into shutdown. Once shut down, it takes a read back of the flags register and another rising edge at TX2 to force shutdown again. Figure 34 details TX2 shutdown mode.

Figure 34. TX1 or TX2 (Force Shutdown) Response

#### 7.4.9 **GPIO2 Mode**

With bit [3] of the GPIO fegister set to 1, the TX2/INT/GPIO2 pin is configured as a logic I/O. In this mode the TX2/INT/GPIO2 pin is readable and writable as a logic input/output via bits [5:4] of the GPIO register. See Table 8 for programming the GPIO2 output.

## 7.4.10 Interrupt Output (INT Mode)

The TX2/INT/GPIO2 pin can be reconfigured as an active low interrupt output by setting bit [6] in the GPIO register to 1 and configuring TX2/INT/GPIO2 as a GPIO2 output (bits [4:3] of GPIO register = 11). In this mode, TX2/INT/GPIO2 pulls low when any of these conditions exist:

- 1. The LM3560 is configured for NTC mode (configuration register 1 bit [4] = 1), and the voltage at LEDI/NTC has fallen below V<sub>TRIP</sub> (1 V typical).

- 2. The LM3560 is configured for  $V_{IN}$  monitor mode ( $V_{IN}$  monitor register bit [0] = 1), and  $V_{IN}$  falls below the programmed  $V_{IN}$  monitor threshold.

- 3. The LM3560 is configured for  $V_{IN}$  flash monitor mode ( $V_{IN}$  monitor register bit [3] = 1), and  $V_{IN}$  falls below the programmed  $V_{IN}$  flash monitor threshold.

Once INT is pulled low due to any of the above conditions having been met, INT only goes high again if any of the conditions are no longer true and the flags register is read.

Figure 35. TX2 as an Interrupt Output (During an NTC Event)

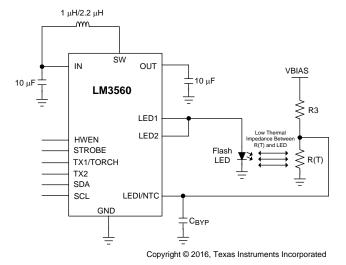

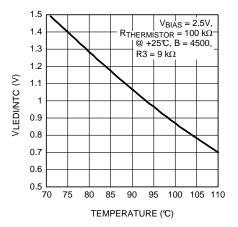

## 7.4.11 NTC Mode

Writing a (1) to configuration register 1 bit [4] configures the LEDI/NTC pin for NTC mode. In this mode the indicator current source is disabled, and LEDI/NTC becomes the positive input to the an internal comparator. NTC mode operates as a LED current interrupt that is triggered when the voltage at LEDI/NTC goes below 1 V.

Two actions can be taken when the NTC comparator is tripped. With configuration register 2 bit [1] set to 0 the NTC interrupt forces the LED current from flash mode into torch mode. with configuration register 2 bit [1] set to 1, the NTC interrupt forces the LED current into shutdown.

Whether in NTC force torch or NTC shutdown, in order to re-enter flash mode after an NTC event, two things must occur. First, the NTC input must be above the 1-V threshold. Secondly, the flags register must be read.

To avoid noise from falsely triggering the NTC comparator, this mode incorporates a 250  $\mu$ s de-glitch timer. With NTC mode active,  $V_{LEDI/NTC}$  must go below the trip point ( $V_{TRIP}$ ) and remain below it for 250  $\mu$ s before the LEDs are forced into torch mode (or shutdown) and the NTC flag is written.

## 7.4.12 Alternate External Torch (AET) Mode

With configuration register 2 bit [2] set to 1, the LM3560 is configured for AET mode, and the operation of TX1/TORCH becomes dependent on its occurrence relative to the STROBE input. In this mode, if TX1/TORCH goes high first, then STROBE goes high, the LEDs are forced into torch mode with no timeout. In this mode, if TX1/TORCH goes high after STROBE has gone high, then the TX1/TORCH pin operates as a normal LED current interrupt (TX1), and the LEDs turn off at the end of the timeout duration (see Figure 36).

Figure 36. AET Mode Timing

#### 7.4.13 Automatic Conversion Mode

With the ADC enabled, a conversion is performed each time a flash pulse is started. When a flash pulse is started bit [6] of the  $V_{LED}$  monitor register end-of-conversion (EOC) bit is automatically written with a 0. At the end of the conversion, bit [6] goes high signaling that the  $V_{LED}$  data is valid. A read back of the  $V_{LED}$  monitor register clears the EOC bit. Figure 26 shows the  $V_{LED}$  monitor automatic conversion.

#### 7.4.14 Manual Conversion Mode