LMK3H0102 SNAS847 – NOVEMBER 2023

# LMK3H0102 Reference-Less 2-Differential or 5-Single-Ended Output PCIe Gen 1-6 Compliant Programmable BAW Clock Generator

# 1 Features

TEXAS

INSTRUMENTS

- Integrated BAW resonator, no need for external reference

- Flexible frequency generation:

- Two channel dividers: up to three unique output frequencies from 2.5 MHz to 400 MHz

- LVCMOS outputs supported up to 200 MHz: 1.8

V, 2.5 V, or 3.3 V

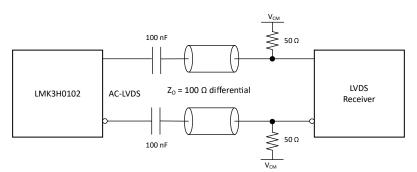

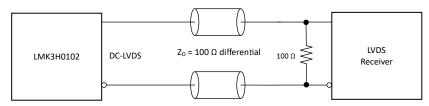

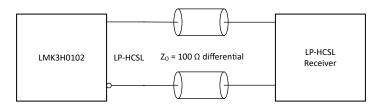

- Combination of AC-LVDS, DC-LVDS, LP-HCSL, and LVCMOS on OUT0 and OUT1 pins

- Additional LVCMOS output for generation of up to 5 LVCMOS clocks

- Total output frequency stability: ±25 ppm

- 2 functional modes: I<sup>2</sup>C or preprogrammed OTP

Fully configurable I<sup>2</sup>C address

- Ambient temperature: -40 °C to 85 °C

- PCIe Gen 1 to Gen 6 compliant: Common Clock with or without SSC, SRNS, and SRIS

- Very low PCIe jitter with SSC:

- PCIe Gen 3 Common Clock jitter: 110 fs maximum (PCIe limit is 1 ps)

- PCIe Gen 4 Common Clock jitter: 110 fs maximum (PCIe limit is 500 fs)

- PCIe Gen 5 Common Clock jitter: 47 fs maximum (PCIe limit is 150 fs)

- PCIe Gen 6 Common Clock jitter: 28 fs maximum (PCIe limit is 100 fs)

- Programmable SSC modulation depth

- Preprogrammed: -0.1%, -0.25%, -0.3%, and -0.5% down spread

- Register programmable: -0.1% to -3% down spread or ±0.05% to ±1.5% center spread

- 1.8 V to 3.3 V supply voltage

- Typical 65 mA current consumption for dual 100-MHz LP-HCSL outputs

- Internal LDOs with –93.1 dBc PSNR at 500 kHz switching noise for LP-HCSL outputs

- Start-up time: <1.5 ms</li>

- Output-to-output skew: <50 ps</li>

- Fail-safe digital input pins

# 2 Applications

- PCle Gen 1 to Gen 6 clock generation

- Server Motherboard

- NIC, SmartNIC

- Hardware Accelerator

- PCle SSD

- Add-In Card, PCIe Expansion Card

- Multifunction Printer

# **3 Description**

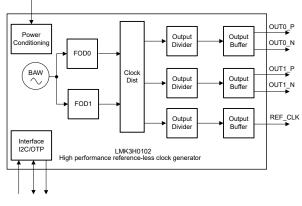

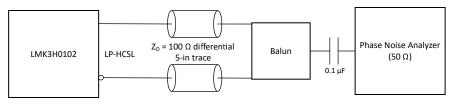

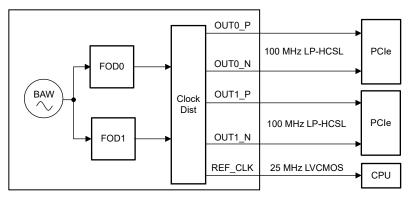

The LMK3H0102 is a 2-output PCIe Gen 1 to Gen 6 compliant reference-less clock generator with Spread Spectrum Clocking (SSC) support. The part is based on TI proprietary Bulk Acoustic Wave (BAW) technology and provides ±25-ppm clock outputs without any crystal or external clock reference. The device can provide two SSC clocks, two non-SSC clocks, or one SSC clock and one non-SSC clock at the same time. The device meets the full PCIe compliance from Gen 1 to Gen 6, including Common Clock with or without SSC, Separate Reference No Spread (SRNS), and Separate Reference Independent Spread (SRIS).

The device can be easily configured through either GPIO pins or I<sup>2</sup>C interface. An external DC/DC can be used to power the device. Refer to *Power Supply Recommendations* for detailed guidelines on power supply filtering and sourcing from DC/DC.

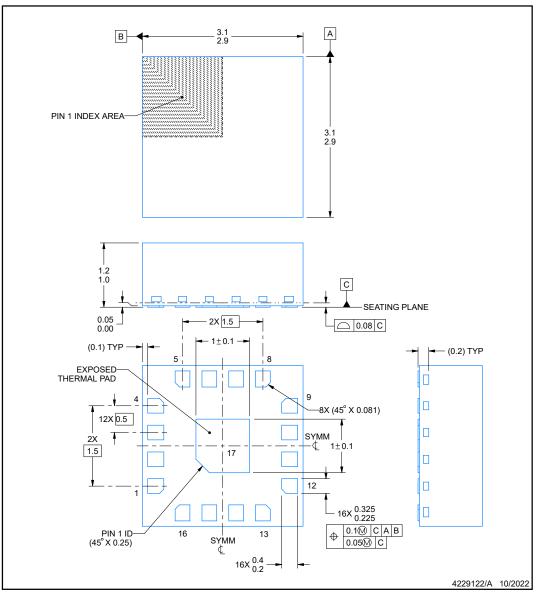

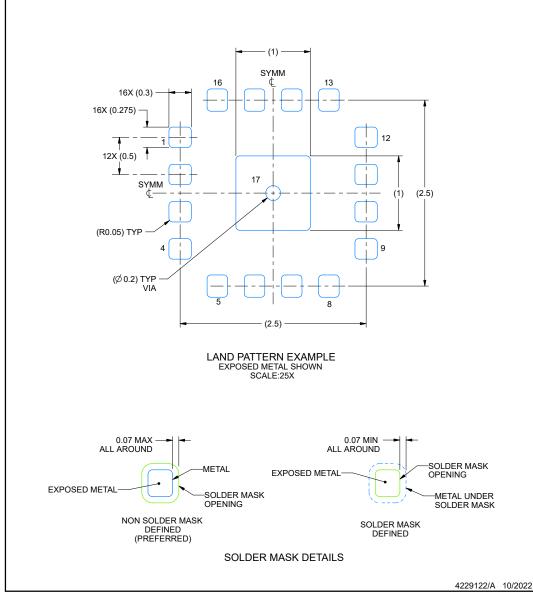

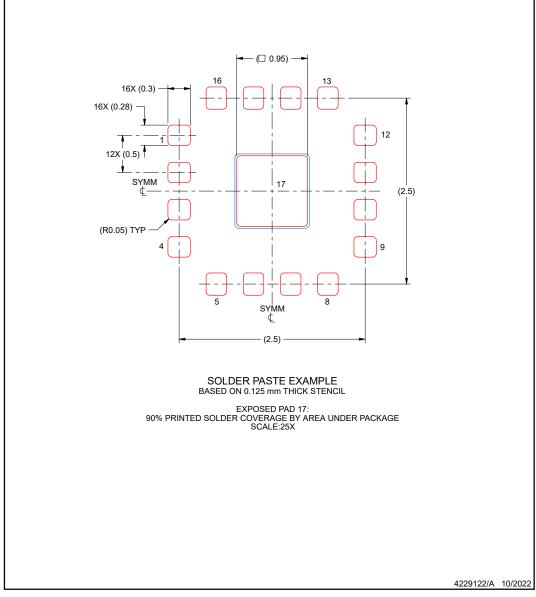

## Package Information

| PART NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup> |

|-------------|------------------------|-----------------------------|

| LMK3H0102   | RER (VQFN, 16)         | 3.0 mm × 3.0 mm             |

(1) For all available packages, see Section 13.

(2) The package size (length × width) is a nominal value and includes pins, where applicable.

# Simplified Block Diagram

# **Table of Contents**

| 1 Features       1         2 Applications       1         3 Description       1 |

|---------------------------------------------------------------------------------|

| 4 Pin Configuration and Functions                                               |

| 5 Specifications5                                                               |

| 5.1 Absolute Maximum Ratings5                                                   |

| 5.2 ESD Ratings5                                                                |

| 5.3 Recommended Operating Conditions5                                           |

| 5.4 Thermal Information5                                                        |

| 5.5 Electrical Characteristics6                                                 |

| 5.6 I2C Interface Specification12                                               |

| 6 Differential Voltage Measurement Terminology14                                |

| 7 Parameter Measurement Information15                                           |

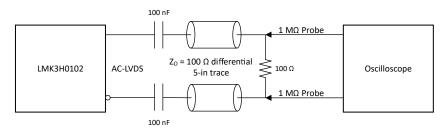

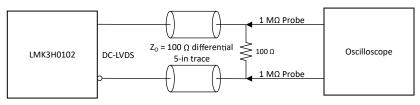

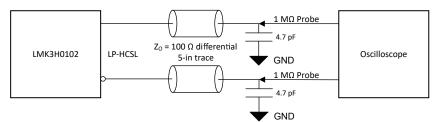

| 7.1 Output Format Configurations15                                              |

| 8 Detailed Description                                                          |

| 8.1 Overview                                                                    |

| 8.2 Functional Block Diagram18                                                  |

| 8.3 Feature Description                                                         |

| 8.4 Device Functional Modes23                                                   |

| 8.5 Programming                                                                 |

| 9 Application and Implementation                      | .33 |

|-------------------------------------------------------|-----|

| 9.1 Application Information                           |     |

| 9.2 Typical Applications                              |     |

| 9.3 Power Supply Recommendations                      |     |

| 9.4 Layout                                            |     |

| 10 Device Registers                                   |     |

| 10.1 Register Maps                                    |     |

| 11 Device and Documentation Support                   |     |

| 11.1 Documentation Support                            |     |

| 11.2 Receiving Notification of Documentation Updates. |     |

| 11.3 Support Resources                                |     |

| 11.4 Trademarks                                       |     |

| 11.5 Electrostatic Discharge Caution                  |     |

| 11.6 Glossary                                         |     |

| 12 Revision History                                   |     |

| 13 Mechanical, Packaging, and Orderable               |     |

| Information                                           | .53 |

| 13.1 Package Option Addendum                          |     |

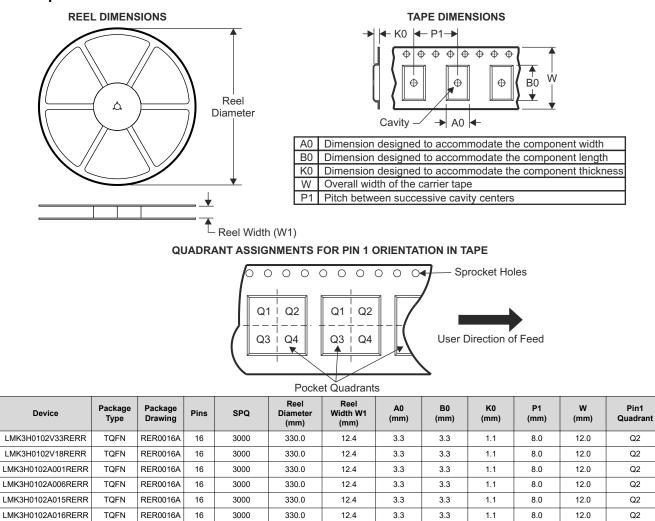

| 13.2 Tape and Reel Information                        |     |

| 1                                                     |     |

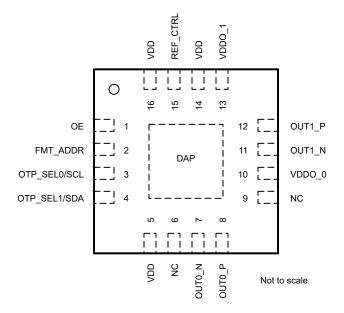

# **4** Pin Configuration and Functions

## Table 4-1. Pin Functions

| PIN                   |        | TYPE <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|-----------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME NO.              |        |                                                                                                                                                                                                                                                                                                                                                                                                                                               | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| OUT0_P, OUT0_N        | 8, 7   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                             | Clock output 0. Supports LP-HCSL (85 $\Omega$ or 100 $\Omega$ ), LVDS or 1.8-V/2.5-V/3.3-V LVCMOS.                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| OUT1_P, OUT1_N        | 12, 11 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                             | Clock output 1. Supports LP-HCSL (85 $\Omega$ or 100 $\Omega$ ), LVDS or 1.8-V/2.5-V/3.3-V LVCMOS.                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| REF_CTRL<br>(REF_CLK) | 15     | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                           | Multifunctional pin. At power up, the state of this pin is latched to select the functionality of Pin 2, Pin 3 and Pin 4. Pull low or leave floating for I2C mode or high for OTP mode prior to power-up. After power-up, this pin can be programmed as an additional LVCMOS output (REF_CLK), active-high CLK_READY signal, or disabled (default). See REF_CTRL Operation for more details. This pin has an 880-kΩ internal pulldown resistor. |  |  |  |

| OE                    | 1      | I                                                                                                                                                                                                                                                                                                                                                                                                                                             | <ul> <li>Output Enable. Active low. 2-state logic input pin.</li> <li>This pin has a 75-kΩ internal pulldown resistor.</li> <li>This pin can control either OUT0 alone or OUT0 and OUT1. See Output Enable for more details.</li> <li>Low/Floating: OUT0 and OUT1 enabled</li> <li>High: OUT0 and OUT1 disabled</li> </ul>                                                                                                                      |  |  |  |

| FMT_ADDR              | 2      | <ul> <li>Multifunctional pin. Functionality is determined by REF_CTRL (pin 15) at power up. OTP Mode and I2C Mode for more details.</li> <li>This pin has an 880-kΩ internal pulldown resistor.</li> <li>I2C Mode: This pin can select the I2C address, function as the output enable for OUT1, or have no function.</li> <li>OTP Mode: This pin can set the output format, function as the output enable for or have no function.</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

#### Table 4-1. Pin Functions (continued)

| PIN<br>NAME NO. |        |        | DESCRIPTION                                                                                                                                                                                                  |

|-----------------|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 |        |        | DESCRIPTION                                                                                                                                                                                                  |

| OTP SEL0/SCL,   |        |        | Multifunctional pin. Functionality is determined by REF_CTRL (pin 15) at power up. See OTP Mode and I2C Mode for details. These pins have $880$ -k $\Omega$ internal pulldown resistors.                     |

| OTP_SEL1/SDA    | 3, 4   | I, I/O | <ul> <li>I2C Mode: These pins are the I2C clock and data connections.</li> </ul>                                                                                                                             |

| _               |        |        | OTP Mode: These pins select the OTP page.                                                                                                                                                                    |

| VDD 5, 14, 16   |        | Р      | 1.8-V, 2.5-V or 3.3-V device power supply. A 0.1-µF capacitor must be placed as close to each of the pins as possible. For LMK3H0102V18, only provide 1.8 V to this pin.                                     |

| VDDO_0, VDDO_1  | 10, 13 | Р      | 1.8-V, 2.5-V or 3.3-V OUT0 and OUT1 power supply. If VDD is 1.8 V or 2.5 V, the VDDO pins must be the same voltage as VDD. A 0.1- $\mu$ F capacitor must be placed as close to each of the pins as possible. |

| NC 6, 9         |        | N/A    | No connect. Pins can be connected to GND, VDD, or otherwise tied to any potential within the Supply Voltage range stated in the <i>Absolute Maximum Ratings</i> .                                            |

| DAP             | DAP 17 |        | GND                                                                                                                                                                                                          |

(1) I = Input, O = Output, I/O = Input or Output, G = Ground, P = Power.

# **5** Specifications

## 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                  |                                                                                        | MIN  | MAX                      | UNIT |

|------------------|----------------------------------------------------------------------------------------|------|--------------------------|------|

| V <sub>DD</sub>  | Device supply voltage                                                                  | -0.3 | 3.9                      | V    |

| V <sub>DDO</sub> | Output supply voltage                                                                  | -0.3 | 3.9                      | V    |

| V <sub>IN</sub>  | Logic input voltage ( $V_{DD} = V_{DDO} = -0.3$ to 3.9 V)                              | -0.3 | 3.9                      | V    |

|                  | Voltage applied to OUTx_P and OUTx_N pins (when outputs are high or low)               | -0.3 | V <sub>DDO_x</sub> + 0.3 | V    |

| V <sub>OUT</sub> | Voltage applied to OUTx_P and OUTx_N pins (when outputs are LVCMOS tri-state)          | -0.3 | 1.89                     | V    |

|                  | Voltage applied to OUTx_P and OUTx_N pins (when outputs are LP-HCSL or LVDS tri-state) | -0.3 | 1.5                      | V    |

| TJ               | Junction temperature                                                                   |      | 105                      | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

## 5.2 ESD Ratings

|                  |     |                         |                                                                                     | VALUE | UNIT |

|------------------|-----|-------------------------|-------------------------------------------------------------------------------------|-------|------|

| V                |     | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001, all pins <sup>(1)</sup>     | ±2000 | V    |

| V <sub>(ES</sub> | SD) | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JS-002, all pins <sup>(2)</sup> | ±500  | v    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### **5.3 Recommended Operating Conditions**

$V_{DD}$  =  $V_{DDO}$  = 1.8 V, 2.5 V or 3.3 V ± 5%, T<sub>A</sub> = T<sub>A,min</sub> to T<sub>A,max</sub>

|                   |                                                   | MIN   | NOM | MAX   | UNIT |

|-------------------|---------------------------------------------------|-------|-----|-------|------|

|                   |                                                   | 1.71  | 1.8 | 1.89  | V    |

| V <sub>DD</sub>   | Device supply voltage                             | 2.375 | 2.5 | 2.625 | V    |

|                   |                                                   | 3.135 | 3.3 | 3.465 | V    |

|                   |                                                   | 1.71  | 1.8 | 1.89  | V    |

| V <sub>DDO</sub>  | Output supply voltage                             | 2.375 | 2.5 | 2.625 | V    |

|                   |                                                   | 3.135 | 3.3 | 3.465 | V    |

| T <sub>A</sub>    | Ambient temperature                               | -40   |     | 85    | °C   |

| TJ                | Junction temperature                              | -40   |     | 105   | °C   |

| t <sub>ramp</sub> | Power supply ramp time. V <sub>DD</sub> = 1.8 V   | 0.05  |     | 5     | ms   |

| t <sub>ramp</sub> | Power supply ramp time. $V_{DD}$ = 2.5 V or 3.3 V | 0.05  |     | 5     | ms   |

## **5.4 Thermal Information**

|                       |                                           | LMK3H0102 |      |

|-----------------------|-------------------------------------------|-----------|------|

|                       | THERMAL METRIC <sup>(1)</sup>             | RER (QFN) | UNIT |

|                       |                                           | 16 PINS   |      |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance    | 69.8      | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance | 56.5      | °C/W |

|                       |                                              | LMK3H0102 |      |

|-----------------------|----------------------------------------------|-----------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RER (QFN) | UNIT |

|                       |                                              | 16 PINS   |      |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 38.6      | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 2.1       | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 38.5      | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 10.3      | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## **5.5 Electrical Characteristics**

$V_{DD}$  =  $V_{DDO}$  = 1.8 V, 2.5 V or 3.3 V ± 5%, T<sub>A</sub> = T<sub>A,min</sub> to T<sub>A,max</sub>

|                        | PARAMETER                                             | TEST CONDITIONS                                                                                                           | MIN | TYP | MAX | UNIT |

|------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| FREQUE                 | NCY STABILITY                                         | 1                                                                                                                         |     |     |     |      |

| $\Delta f_{total}$     | Total frequency stability                             | All factors included: temperature<br>variation, 10-year aging, solder shift,<br>hysteresis and initial frequency accuracy | -25 |     | 25  | ppm  |

| LP-HCSL                | CLOCK OUTPUT CHARACTERISTICS                          |                                                                                                                           |     |     |     |      |

| f <sub>out</sub>       | Output frequency                                      |                                                                                                                           | 2.5 |     | 400 | MHz  |

| V <sub>min</sub>       | Output low voltage (undershoot included)              |                                                                                                                           | -60 |     | 25  | mV   |

| Vovershoot             | Overshoot voltage. V <sub>max</sub> - V <sub>OH</sub> |                                                                                                                           |     |     | 150 | mV   |

|                        |                                                       | code = 0                                                                                                                  | 594 | 625 | 656 | mV   |

|                        | Output high voltage. VDD = 2.5 V or 3.3 V             | code = 1                                                                                                                  | 614 | 647 | 679 | mV   |

|                        |                                                       | code = 2                                                                                                                  | 635 | 668 | 702 | mV   |

|                        |                                                       | code = 3                                                                                                                  | 656 | 690 | 725 | mV   |

|                        |                                                       | code = 4                                                                                                                  | 676 | 712 | 747 | mV   |

|                        |                                                       | code = 5                                                                                                                  | 697 | 733 | 770 | mV   |

|                        |                                                       | code = 6 (default)                                                                                                        | 717 | 755 | 793 | mV   |

| V <sub>OH,2.5/3.</sub> |                                                       | code = 7                                                                                                                  | 738 | 777 | 816 | mV   |

| 3                      |                                                       | code = 8                                                                                                                  | 758 | 798 | 838 | mV   |

|                        |                                                       | code = 9                                                                                                                  | 779 | 820 | 861 | mV   |

|                        |                                                       | code = 10                                                                                                                 | 800 | 842 | 884 | mV   |

|                        |                                                       | code = 11                                                                                                                 | 820 | 863 | 907 | mV   |

|                        |                                                       | code = 12                                                                                                                 | 841 | 885 | 929 | mV   |

|                        | c                                                     | code = 13                                                                                                                 | 861 | 907 | 952 | mV   |

|                        |                                                       | code = 14                                                                                                                 | 882 | 928 | 975 | mV   |

|                        |                                                       | code = 15                                                                                                                 | 903 | 950 | 998 | mV   |

|                        |                                                       | 1                                                                                                                         |     |     |     |      |

#### $V_{DD}$ = $V_{DDO}$ = 1.8 V, 2.5 V or 3.3 V ± 5%, T<sub>A</sub> = T<sub>A,min</sub> to T<sub>A,max</sub>

|                                 | PARAMETER                                            | TEST CONDITIONS                                                                                                                                             | MIN   | TYP | MAX   | UNIT |

|---------------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|------|

|                                 |                                                      | code = 0                                                                                                                                                    | 563   | 625 | 688   | mV   |

|                                 |                                                      | code = 1                                                                                                                                                    | 582   | 647 | 712   | mV   |

|                                 |                                                      | code = 2                                                                                                                                                    | 601   | 668 | 735   | mV   |

|                                 |                                                      | code = 3                                                                                                                                                    | 621   | 690 | 759   | mV   |

|                                 |                                                      | code = 4                                                                                                                                                    | 641   | 712 | 783   | mV   |

|                                 |                                                      | code = 5                                                                                                                                                    | 660   | 733 | 806   | mV   |

|                                 |                                                      | code = 6 (default)                                                                                                                                          | 680   | 755 | 831   | mV   |

|                                 |                                                      | code = 7                                                                                                                                                    | 699   | 777 | 855   | mV   |

| V <sub>OH,1.8</sub>             | Output high voltage. VDD = 1.8 V                     | code = 8                                                                                                                                                    | 718   | 798 | 878   | mV   |

|                                 |                                                      | code = 9                                                                                                                                                    | 738   | 820 | 902   | mV   |

|                                 |                                                      | code = 10                                                                                                                                                   | 758   | 842 | 926   | mV   |

|                                 |                                                      | code = 11                                                                                                                                                   | 777   | 863 | 949   | mV   |

|                                 |                                                      | code = 12                                                                                                                                                   | 797   | 885 | 974   | mV   |

|                                 |                                                      | code = 12                                                                                                                                                   | 816   | 907 | 974   | mV   |

|                                 |                                                      | code = 13                                                                                                                                                   |       |     |       |      |

|                                 |                                                      | code = 14<br>code = 15                                                                                                                                      | 835   | 928 | 1021  | mV   |

|                                 |                                                      |                                                                                                                                                             | 855   | 950 | 1045  | mV   |

| Z <sub>diff</sub>               | LP-HCSL static differential impedance                |                                                                                                                                                             | 80.75 | 85  | 91.25 | Ω    |

|                                 |                                                      |                                                                                                                                                             | 95    | 100 | 105   | Ω    |

|                                 | Output slew rate (rising and falling edge)           | Measured from $-150 \text{ mV}$ to $+150 \text{ mV}$ on<br>the differential waveform, centered on the<br>zero crossing point. OUTx_SLEW_RATE<br>= $0^{(1)}$ | 2.1   |     | 3.1   | V/ns |

|                                 |                                                      | Measured from –150 mV to +150 mV on<br>the differential waveform, centered on the<br>zero crossing point. OUTx_SLEW_RATE<br>= 0                             | 2.3   |     | 3.5   | V/ns |

| dV/dt                           |                                                      | Measured from –150 mV to +150 mV on<br>the differential waveform, centered on the<br>zero crossing point. OUTx_SLEW_RATE<br>= 1                             | 2     |     | 3.2   | V/ns |

|                                 |                                                      | Measured from –150 mV to +150 mV on<br>the differential waveform, centered on the<br>zero crossing point. OUTx_SLEW_RATE<br>= 2                             | 1.7   |     | 2.8   | V/ns |

|                                 |                                                      | Measured from –150 mV to +150 mV on<br>the differential waveform, centered on the<br>zero crossing point. OUTx_SLEW_RATE<br>= 3                             | 1.4   |     | 2.7   | V/ns |

| ∆dV/dt                          | Rising edge rate to falling edge rate matching       | See <sup>(1)</sup>                                                                                                                                          |       |     | 3     | %    |

|                                 |                                                      | See <sup>(1)</sup>                                                                                                                                          | 49.9  |     | 50.3  | %    |

| DDC                             | Output duty cycle                                    | f <sub>out</sub> ≤ 325 MHz                                                                                                                                  | 48.8  |     | 50.8  | %    |

|                                 |                                                      | 325 MHz < f <sub>out</sub> ≤ 400 MHz                                                                                                                        | 48.6  |     | 51.8  | %    |

| skew                            | Output to output skew                                | Same FOD, LP-HCSL output                                                                                                                                    |       |     | 50    | ps   |

| / <sub>cross</sub>              | Absolute crossing point voltage                      | See <sup>(1)</sup>                                                                                                                                          | 280   |     | 480   | mV   |

| ∆V <sub>cross</sub>             | Variation of V <sub>cross</sub> over all clock edges | See <sup>(1)</sup>                                                                                                                                          |       |     | 30    | mV   |

| V <sub>RB</sub>                 | Absolute value of ring back voltage                  | See <sup>(1)</sup>                                                                                                                                          | 100   |     |       | mV   |

| stable                          | Time before $V_{RB}$ is allowed                      | See <sup>(1)</sup>                                                                                                                                          | 500   |     |       | ps   |

|                                 | Cycle to cycle jitter, Common Clock no               |                                                                                                                                                             | 000   |     |       | 69   |

| J <sub>cycle-to-</sub><br>cycle | SSC                                                  | See <sup>(1)</sup>                                                                                                                                          |       |     | 150   | ps   |

Copyright © 2024 Texas Instruments Incorporated

| LMK3H0102               |

|-------------------------|

| SNAS847 - NOVEMBER 2023 |

|                                   | <sub>DO</sub> = 1.8 V, 2.5 V or 3.3 V ± 5%, T <sub>A</sub> = T<br><b>PARAMETER</b>                                              | TEST CONDITIONS                                                     | MIN                       | TYP | MAX              | UNIT |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------|-----|------------------|------|

| J <sub>cycle-to-</sub><br>cycle   | Cycle to cycle jitter, Common Clock,<br>-0.5% SSC                                                                               | See <sup>(1)</sup>                                                  |                           |     | 150              | ps   |

| t <sub>period_abs</sub>           | Absolute period including jitter and SSC                                                                                        | See <sup>(1)</sup>                                                  | 9.949                     | 10  | 10.101           | ns   |

| t <sub>period_avg</sub><br>_CC    | Average clock period accuracy, Common<br>Clock                                                                                  | See <sup>(1)</sup>                                                  | -100                      |     | 2600             | ppm  |

| t <sub>period_avg</sub><br>_SRIS  | Average clock period accuracy, SRIS                                                                                             | See <sup>(1)</sup>                                                  | -100                      |     | 1600             | ppm  |

| LVDS CLO                          | OCK OUTPUT CHARACTERISTICS                                                                                                      |                                                                     |                           |     |                  |      |

| f <sub>out</sub>                  | Output frequency                                                                                                                |                                                                     | 2.5                       |     | 400              | MHz  |

| V <sub>OD</sub>                   | Steady-state magnitude of the differential output voltage  V <sub>OUTP</sub> - V <sub>OUTN</sub>                                | 100 $\Omega$ external termination                                   | 250                       | 350 | 450              | mV   |

| $\Delta V_{pp-diff}$              | Change in differential output voltage<br>swing between complementary output<br>states                                           | 100 $\Omega$ external termination                                   |                           |     | 50               | mV   |

|                                   |                                                                                                                                 | $V_{DDO}$ = 3.3 V, 100 $\Omega$ external termination                | 1.12                      | 1.2 | 1.365            | V    |

| V <sub>OS</sub>                   | Output offset voltage (common mode voltage)                                                                                     | $V_{DDO}$ = 2.5 V, 100 $\Omega$ external termination                | 1.1                       | 1.2 | 1.345            | V    |

|                                   |                                                                                                                                 | $V_{DDO}$ = 1.8 V, 100 $\Omega$ external termination                | 0.8                       |     | 0.97             | V    |

| ΔV <sub>OS</sub>                  | Change in V <sub>OS</sub> between complementary output states                                                                   |                                                                     |                           |     | 50               | mV   |

| I <sub>SA</sub> , I <sub>SB</sub> | Short-circuit current. Magnitude of current with the generator output terminals short-circuited to the generator circuit common |                                                                     | -24                       |     | 24               | mA   |

| SAB                               | Short-circuit current. Magnitude of current with generator output terminals short-<br>circuited to each other                   |                                                                     | -12                       |     | 12               | mA   |

|                                   | 20% to 80% differential rise/fall time                                                                                          | PADCAP_CHx = 0                                                      | 195                       |     | 315              | ps   |

|                                   |                                                                                                                                 | PADCAP_CHx = 1                                                      | 250                       |     | 440              | ps   |

| t <sub>R</sub> , t <sub>F</sub>   |                                                                                                                                 | PADCAP_CHx = 2                                                      | 270                       |     | 610              | ps   |

|                                   |                                                                                                                                 | PADCAP_CHx = 3                                                      | 280                       |     | 800              | ps   |

| t <sub>skew</sub>                 | Output to output skew                                                                                                           | Same FOD, LVDS output                                               |                           |     | 50               | ps   |

| ODC                               | Output duty cycle                                                                                                               |                                                                     | 49                        |     | 51.1             | %    |

| LVCMOS                            | CLOCK OUTPUT CHARACTERISTICS                                                                                                    |                                                                     |                           |     |                  |      |

| f <sub>out</sub>                  | Output frequency                                                                                                                |                                                                     | 2.5                       |     | 200              | MHz  |

|                                   |                                                                                                                                 | $V_{DDO}$ = 3.3 V ± 5%, measured from 20% to 80%, 4.7 pF load       | 2.6                       |     | 4.7              | V/ns |

| dV/dt                             | Output slew rate                                                                                                                | $V_{DDO}$ = 2.5 V ± 5%, measured from 20% to 80%, 4.7 pF load       | 2.6                       |     | 3.7              | V/ns |

|                                   |                                                                                                                                 | $V_{DDO}$ = 1.8 V ± 5%, measured from 20% to 80%, 4.7 pF load       | 1                         |     | 3.2              | V/ns |

|                                   |                                                                                                                                 | I <sub>OH</sub> = –15 mA at 3.3 V                                   | 0.0.4                     |     |                  |      |

| V <sub>OH</sub>                   | Output high voltage                                                                                                             | I <sub>OH</sub> = –12 mA at 2.5 V                                   | 0.8 x<br>V <sub>DDO</sub> |     | $V_{\text{DDO}}$ | V    |

|                                   |                                                                                                                                 | I <sub>OH</sub> = –8 mA at 1.8 V                                    | 200                       |     |                  |      |

|                                   |                                                                                                                                 | I <sub>OL</sub> = 15 mA at 3.3 V                                    |                           |     |                  |      |

| V <sub>OL</sub>                   | Output low voltage                                                                                                              | I <sub>OL</sub> = 12 mA at 2.5 V<br>I <sub>OL</sub> = 8 mA at 1.8 V |                           |     | 0.4              | V    |

| leak                              | Output leakage current                                                                                                          | Output tri-stated. V <sub>DD</sub> = V <sub>DDO</sub> = 3.465 V     | -5                        | 0   | 5                | μA   |

| R <sub>out</sub>                  | Output impedance                                                                                                                |                                                                     |                           | 17  |                  | Ω    |

|                                   |                                                                                                                                 | f <sub>out</sub> ≤ 156.25 MHz                                       | 45                        |     | 55               | %    |

| ODC                               | Output duty cycle                                                                                                               | f <sub>out</sub> > 156.25 MHz                                       | 40                        |     | 60               | %    |

| t <sub>skew</sub>                 | Output-to-output skew                                                                                                           | Same FOD, LVCMOS output                                             |                           |     | 50               | ps   |

8 Submit Document Feedback Copyright © 2024 Texas Instruments Incorporated

## $V_{DD}$ = $V_{DDO}$ = 1.8 V, 2.5 V or 3.3 V ± 5%, T<sub>A</sub> = T<sub>A,min</sub> to T<sub>A,max</sub>

|                                   | PARAMETER                                                                  | TEST CONDITIONS                                                                  | MIN                   | TYP   | MAX  | UNIT   |

|-----------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------|-------|------|--------|

| C <sub>load</sub>                 | Maximum load capacitance                                                   |                                                                                  |                       |       | 15   | pF     |

| LVCMOS                            | REFCLK CHARATERISTICS                                                      |                                                                                  |                       |       |      |        |

| f <sub>out</sub>                  | Output frequency                                                           | See <sup>(2)</sup>                                                               | 12.5 <mark>(3)</mark> |       | 200  | MHz    |

|                                   |                                                                            | $V_{DDO}$ = 3.3 V ± 5%, measured from 20% to 80%, 4.7 pF load <sup>(2)</sup>     | 2.6                   |       | 6.7  | V/ns   |

| dV/dt                             | Output slew rate                                                           | $V_{DDO}$ = 2.5 V ± 5%, measured from 20% to 80%, 4.7 pF load <sup>(2) (4)</sup> | 1.8                   |       | 4.5  | V/ns   |

|                                   |                                                                            | $V_{DDO}$ = 1.8 V ± 5%, measured from 20% to 80%, 4.7 pF load <sup>(2) (4)</sup> | 1                     |       | 3.2  | V/ns   |

| I <sub>leak</sub>                 | Output leakage current                                                     | Output tri-stated. $V_{DD} = V_{DDO} = 3.465 V^{(2)}$                            | -5                    |       | 5    | μA     |

| R <sub>out</sub>                  | Output impedance                                                           |                                                                                  |                       | 17    |      | Ω      |

| ODC                               | Output duty cycle                                                          | f <sub>out</sub> ≤ 156.25 MHz <sup>(2)</sup>                                     | 45                    |       | 55   | %      |

| ODC                               | Output duty cycle                                                          | f <sub>out</sub> > 156.25 MHz <sup>(2)</sup>                                     | 40                    |       | 60   | %      |

| Cload                             | Maximum load capacitance                                                   | See <sup>(2)</sup>                                                               |                       |       | 15   | pF     |

| RJ                                | Random jitter                                                              | 12 kHz to 20 MHz integrated jitter at 50 $\rm MHz^{(2)}$                         |                       |       | 0.5  | ps     |

| SSC CHA                           | ARACTERISTICS                                                              |                                                                                  |                       |       |      |        |

| f <sub>out</sub>                  | Output frequency range that supports SSC (any output format)               |                                                                                  | 2.5                   |       | 200  | MHz    |

| f <sub>SSC</sub>                  | SSC modulation frequency                                                   |                                                                                  | 30                    | 31.5  | 33   | kHz    |

| f <sub>SSC-</sub>                 | SSC deviation (modulation depth)                                           | Down spread (programmable)                                                       | -3                    |       | -0.1 | %      |

| deviation                         |                                                                            | Center spread (programmable)                                                     | ±0.05                 |       | ±1.5 | %      |

|                                   |                                                                            | f <sub>out</sub> ≤ 100 MHz, down spread                                          | 0                     |       | 0.01 | %      |

| f <sub>SSC-</sub>                 | SSC deviation accuracy                                                     | 100 MHz < $f_{out} \le$ 200 MHz, down spread                                     | 0                     |       | 0.05 | %      |

| deviation-<br>accuracy            |                                                                            | $f_{out} \le 100 \text{ MHz}$ , center spread                                    | 0                     |       | 0.01 | %      |

|                                   |                                                                            | 100 MHz < $f_{out} \le$ 200 MHz, center spread                                   | 0                     |       | 0.05 | %      |

| df/dt                             | max SSC frequency slew rate                                                | $0 < f_{SSC-deviation} \le -0.5\%$                                               |                       |       | 1250 | ppm/us |

| JITTER C                          | HARACTERISTICS                                                             |                                                                                  |                       |       |      |        |

| J <sub>PCle1-cc-</sub><br>SSC_off | PCIe Gen 1 Common Clock jitter, SSC is off (jitter limit = 86 ps)          | SSC disabled on both outputs                                                     |                       |       | 0.4  | ps     |

| J <sub>PCle1-cc-</sub><br>SSC_on  | PCIe Gen 1 Common Clock jitter, –0.5%<br>≤ SSC < 0% (jitter limit = 86 ps) | SSC enabled on both outputs                                                      |                       |       | 0.7  | ps     |

| J <sub>PCle2-cc-</sub><br>SSC_off | PCIe Gen 2 Common Clock jitter, SSC is off (jitter limit = 3 ps)           | SSC disabled on both outputs                                                     |                       | 0.1   | 0.2  | ps     |

| J <sub>PCle2-cc-</sub><br>SSC_on  | PCIe Gen 2 Common Clock jitter, –0.5%<br>≤ SSC < 0% (jitter limit = 3 ps)  | SSC enabled on both outputs                                                      |                       | 0.2   | 0.35 | ps     |

| J <sub>PCle2-</sub><br>srns       | PCIe Gen 2 SRNS jitter                                                     | SSC disabled on both outputs                                                     |                       | 0.1   | 0.26 | ps     |

| J <sub>PCle2-</sub><br>SRIS       | PCIe Gen 2 SRIS jitter, –0.3% ≤ SSC <<br>0%                                | SSC enabled on both outputs                                                      |                       | 0.2   | 0.36 | ps     |

| J <sub>PCle3-cc-</sub><br>SSC_off | PCIe Gen 3 Common Clock jitter, SSC is<br>off (jitter limit = 1 ps)        | SSC disabled on both outputs                                                     |                       | 32.8  | 60   | fs     |

| J <sub>PCle3-cc-</sub><br>SSC_on  | PCIe Gen 3 Common Clock jitter, –0.5%<br>≤ SSC < 0% (jitter limit = 1 ps)  | SSC enabled on both outputs                                                      |                       | 55.4  | 110  | fs     |

| J <sub>PCle3-</sub><br>srns       | PCIe Gen 3 SRNS jitter                                                     | SSC disabled on both outputs                                                     |                       | 35.9  | 67   | fs     |

| J <sub>PCle3-</sub><br>sris       | PCIe Gen 3 SRIS jitter, –0.3% ≤ SSC <<br>0%                                | SSC enabled on both outputs                                                      |                       | 155.6 | 317  | fs     |

| J <sub>PCle4-cc-</sub><br>SSC_off | PCIe Gen 4 Common Clock jitter, SSC is off (jitter limit = 500 fs)         | SSC disabled on both outputs                                                     |                       | 32.8  | 60   | fs     |

| LMK3H0102               |

|-------------------------|

| SNAS847 - NOVEMBER 2023 |

|                                   | PARAMETER                                                                   | TEST CONDITIONS                                                                                                                                                       | MIN TYP | MAX  | UNIT                     |

|-----------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|--------------------------|

| J <sub>PCle4-cc-</sub><br>SSC_on  | PCIe Gen 4 Common Clock jitter, –0.5%<br>≤ SSC < 0% (jitter limit = 500 fs) | SSC enabled on both outputs                                                                                                                                           | 55.4    | 110  | fs                       |

| J <sub>PCle4-</sub><br>srns       | PCIe Gen 4 SRNS jitter                                                      | SSC disabled on both outputs                                                                                                                                          | 35.9    | 68   | fs                       |

| J <sub>PCle4-</sub><br>sris       | PCIe Gen 4 SRIS jitter, –0.3% ≤ SSC <<br>0%                                 | SSC enabled on both outputs                                                                                                                                           | 86.4    | 164  | fs                       |

| J <sub>PCle5-cc-</sub><br>SSC_off | PCIe Gen 5 Common Clock jitter, SSC is off (jitter limit = 150 fs)          | SSC disabled on both outputs                                                                                                                                          | 11.1    | 26   | fs                       |

| J <sub>PCle5-cc-</sub><br>SSC_on  | PCle Gen 5 Common Clock jitter, –0.5%<br>≤ SSC < 0% (jitter limit = 150 fs) | SSC enabled on both outputs                                                                                                                                           | 20.3    | 47   | fs                       |

| J <sub>PCle5-</sub><br>srns       | PCIe Gen 5 SRNS jitter                                                      | SSC disabled on both outputs                                                                                                                                          | 12.7    | 30   | fs                       |

| J <sub>PCle5-</sub><br>sris       | PCIe Gen 5 SRIS jitter, –0.3% ≤ SSC <<br>0%                                 | SSC enabled on both outputs                                                                                                                                           | 22.9    | 51   | fs                       |

| J <sub>PCle6-cc-</sub><br>SSC_off | PCIe Gen 6 Common Clock jitter, SSC is off (jitter limit = 100 fs)          | SSC disabled on both outputs                                                                                                                                          | 7.9     | 16   | fs                       |

| J <sub>PCle6-cc-</sub><br>SSC_on  | PCIe Gen 6 Common Clock jitter, –0.5%<br>≤ SSC < 0% (jitter limit = 100 fs) | SSC enabled on both outputs                                                                                                                                           | 13.5    | 28   | fs                       |

| J <sub>PCle6-</sub><br>srns       | PCIe Gen 6 SRNS jitter                                                      | SSC disabled on both outputs                                                                                                                                          | 11.2    | 24   | fs                       |

| J <sub>PCle6-</sub><br>SRIS       | PCIe Gen 6 SRIS jitter, –0.3% ≤ SSC <<br>0%                                 | SSC enabled on both outputs                                                                                                                                           | 17.7    | 36   | fs                       |

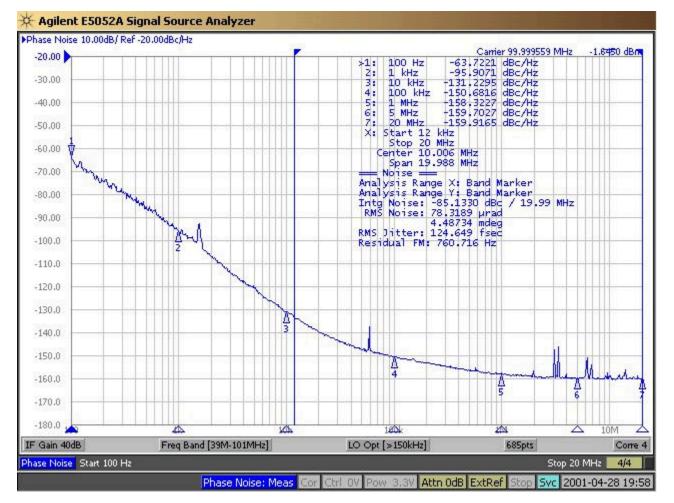

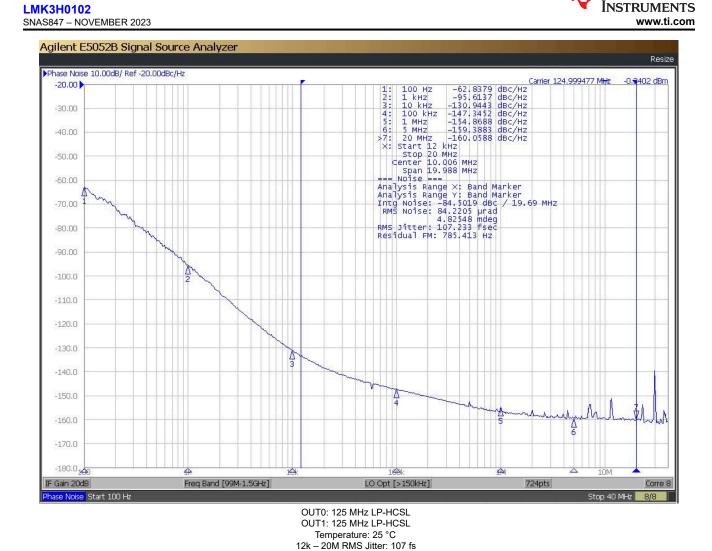

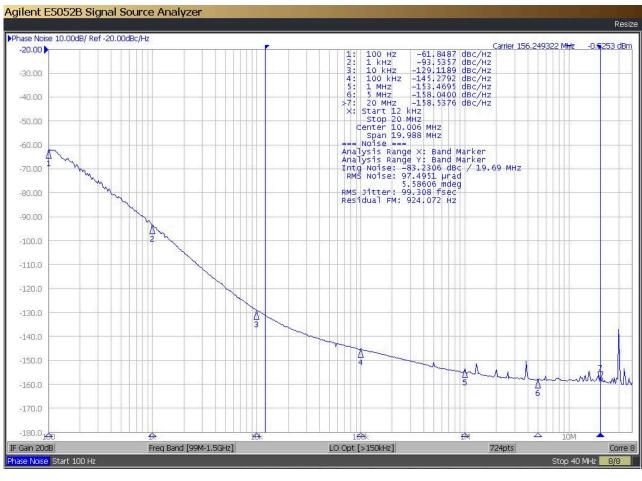

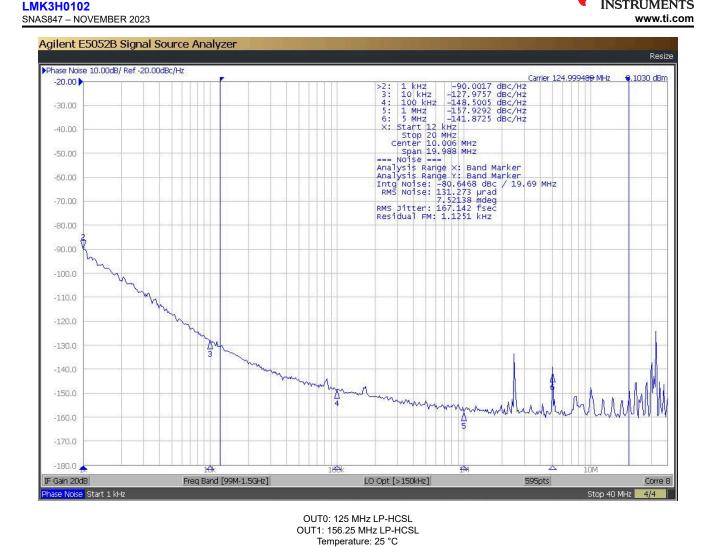

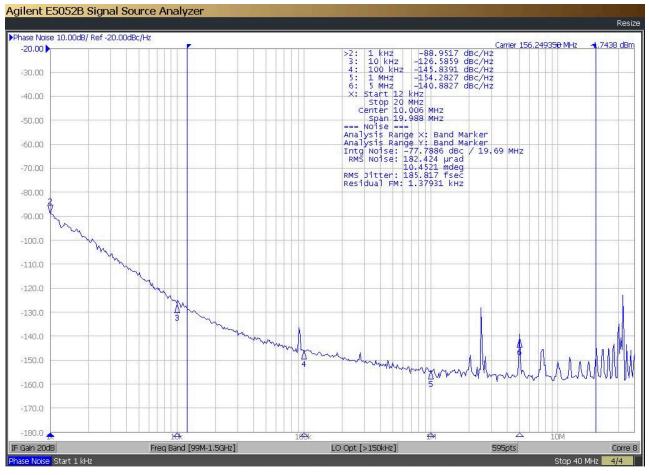

| RJ <sub>RMS</sub>                 | 12 kHz to 20 MHz RMS jitter                                                 | f <sub>out</sub> = 156.25MHz. Optimized for best performance <sup>(5)</sup>                                                                                           |         | 125  | fs                       |

| TIMING C                          | HARACTERISTICS                                                              |                                                                                                                                                                       |         |      |                          |

|                                   |                                                                             | $V_{DD}$ = 2.5 V or 3.3 V. Time elapsed from<br>all $V_{DD}$ pins reach 2.1 V until first output<br>clock rising edge. Output clock is always<br>within specification |         | 1    | ms                       |

| t <sub>startup</sub>              | Start-up time                                                               | $V_{DD}$ = 1.8 V. Time elapsed from all $V_{DD}$<br>pins reach 1.6 V until first output clock<br>rising edge. Output clock is always within<br>specification          |         | 1.5  | ms                       |

| t <sub>OE</sub>                   | Output enable time.                                                         | After CLOCK_READY status is '1', time<br>elapsed between OE assertion and first<br>output clock rising edge. Output is not<br>tristated when disabled.                |         | 7    | outpu<br>clock<br>cycles |

| t <sub>OD</sub>                   | Output disable time.                                                        | Time elapsed between OE deassertion and last output clock falling edge.                                                                                               |         | 7    | outpu<br>clock<br>cycles |

| POWER                             | CONSUMPTION CHARACTERISTICS                                                 | 11                                                                                                                                                                    |         |      |                          |

|                                   |                                                                             | One FOD enabled, 100 MHz $\leq f_{FOD} \leq 200$ MHz                                                                                                                  | 42.9    | 52   | mA                       |

|                                   | Core supply current, not including output                                   | One FOD enabled, 200 MHz < f <sub>FOD</sub> ≤ 400<br>MHz                                                                                                              | 50      | 59.5 | mA                       |

| I <sub>DD</sub>                   | drivers                                                                     | Two FODs enabled, 100 MHz ≤ f <sub>FOD</sub> ≤ 200 MHz                                                                                                                | 62.5    | 72.6 | mA                       |

|                                   |                                                                             | Two FODs enabled, 200 MHz < f <sub>FOD</sub> ≤ 400 MHz                                                                                                                | 75.2    | 86.1 | mA                       |

|                                   | 1                                                                           |                                                                                                                                                                       |         |      |                          |

#### $V_{DD} = V_{DDO} = 1.8 \text{ V}, 2.5 \text{ V} \text{ or } 3.3 \text{ V} \pm 5\%, T_A = T_{A,min} \text{ to } T_{A,max}$

|                      | PARAMETER                                                         | TEST CONDITIONS                               | MIN TYP           | MAX                      | UNIT |

|----------------------|-------------------------------------------------------------------|-----------------------------------------------|-------------------|--------------------------|------|

|                      |                                                                   | LP-HCSL. f <sub>out</sub> ≤ 100 MHz           | 10.1              | 10.8                     | mA   |

|                      |                                                                   | LP-HCSL. 100 MHz < f <sub>out</sub> ≤ 200 MHz | 13.2              | 14.1                     | mA   |

|                      |                                                                   | LP-HCSL. 200 MHz < f <sub>out</sub> ≤ 300 MHz | 13.7              | 15.1                     | mA   |

|                      |                                                                   | LP-HCSL. 300 MHz < f <sub>out</sub> ≤ 400 MHz | 14.4              | 16.4                     | mA   |

|                      |                                                                   | LVDS. f <sub>out</sub> ≤ 100 MHz              | 6                 | 8                        | mA   |

|                      |                                                                   | LVDS. 100 MHz < f <sub>out</sub> ≤ 200 MHz    | 6.8               | 9.2                      | mA   |

|                      |                                                                   | LVDS. 200 MHz < f <sub>out</sub> ≤ 300 MHz    | 7.6               | 10.2                     | mA   |

| DDO                  | Output supply current, per output channel                         | LVDS. 300 MHz < f <sub>out</sub> ≤ 400 MHz    | 8.4               | 11.3                     | mA   |

|                      |                                                                   | 1.8 V LVCMOS. f <sub>out</sub> = 50 MHz       | 4.2               | 5                        | mA   |

|                      |                                                                   | 1.8 V LVCMOS. f <sub>out</sub> = 200 MHz      | 11.7              | 13.4                     | mA   |

|                      |                                                                   | 2.5 V LVCMOS. f <sub>out</sub> = 50 MHz       | 5.6               | 6.4                      | mA   |

|                      |                                                                   | 2.5 V LVCMOS. f <sub>out</sub> = 200 MHz      | 15.3              | 17.3                     | mA   |

|                      |                                                                   | 3.3 V LVCMOS. f <sub>out</sub> = 50 MHz       | 6.8               | 7.7                      | mA   |

|                      |                                                                   | 3.3 V LVCMOS. f <sub>out</sub> = 200 MHz      | 19.2              | 21.7                     | mA   |

|                      |                                                                   | 1.8 V LVCMOS. f <sub>out</sub> = 50 MHz       | 3.4               | 3.9                      | mA   |

|                      | REFCLK supply current                                             | 1.8 V LVCMOS. f <sub>out</sub> = 200 MHz      | 9.5               |                          | mA   |

|                      |                                                                   | 2.5 V LVCMOS. f <sub>out</sub> = 50 MHz       | 4.7               | 5.3                      | mA   |

| DDREF                |                                                                   | 2.5 V LVCMOS. f <sub>out</sub> = 200 MHz      | 12.8              | 15.8                     | mA   |

|                      |                                                                   | 3.3 V LVCMOS. f <sub>out</sub> = 50 MHz       | 5.9               |                          | mA   |

|                      |                                                                   | 3.3 V LVCMOS. f <sub>out</sub> = 200 MHz      | 16.6              | 20.2                     | mA   |

| SNR CH               | ARACTERISTICS                                                     |                                               |                   |                          |      |

|                      | Power Supply Noise Rejection for<br>LVCMOS outputs <sup>(4)</sup> | 10 kHz                                        | -76.7             | -61.2                    | dBc  |

|                      |                                                                   | 50 kHz                                        | -80.9             | -60.9                    | dBc  |

|                      |                                                                   | 100 kHz                                       | -81.8             |                          | dBc  |

| PSNR <sub>LVC</sub>  |                                                                   | 500 kHz                                       | -84.3             |                          | dBc  |

| IOS                  |                                                                   | 1 MHz                                         | -97.6             |                          | dBc  |

|                      |                                                                   | 5 MHz                                         | -104.3            |                          | dBc  |

|                      |                                                                   | 10 MHz                                        | -108.7            |                          | dBc  |

|                      |                                                                   | 10 kHz                                        | -79.5             |                          | dBc  |

|                      |                                                                   | 50 kHz                                        | -83.5             |                          | dBc  |

|                      |                                                                   | 100 kHz                                       | -83               |                          | dBc  |

| PSNR <sub>LVD</sub>  | Power Supply Noise Rejection for LVDS                             | 500 kHz                                       | -88.3             |                          | dBc  |

| 6                    | outputs <sup>(4)</sup>                                            | 1 MHz                                         | -123.4            | -106.6                   | dBc  |

|                      |                                                                   | 5 MHz                                         | -115              |                          | dBc  |

|                      |                                                                   | 10 MHz                                        | -123.7            | -108.9                   | dBc  |

|                      |                                                                   | 10 kHz                                        | -80.1             | -74.5                    | dBc  |

|                      |                                                                   | 50 kHz                                        | -84.7             | -76.7                    | dBc  |

|                      |                                                                   | 100 kHz                                       | -84.6             | -73.7                    | dBc  |

| SNR <sub>LP-</sub>   | Power Supply Noise Rejection for LP-                              | 500 kHz                                       | -93.1             | -82.9                    | dBc  |

| CSL                  | HCSL outputs <sup>(4)</sup>                                       | 1 MHz                                         | -124.6            | -106.8                   | dBc  |

|                      |                                                                   | 5 MHz                                         | -124.0            |                          | dBc  |

|                      |                                                                   | 10 MHz                                        | -114.3            | -109.2                   | dBc  |

|                      | LOGIC INPUT CHARACTERISTICS                                       |                                               | -123              | -109.2                   | ubu  |

|                      | LOGIC INFUT CHARACTERISTICS                                       |                                               | 0.7               | \/ ·                     |      |

| / <sub>IH-Pin2</sub> | Input high voltage for Pin 2                                      |                                               | × V <sub>DD</sub> | V <sub>DD</sub> +<br>0.3 | V    |

11

| $V_{DD} = V_{DDO} = C$ | 1.8 V. 2.5 V or 3. | .3 V ± 5%. T₄ = | $T_{A,min}$ to $T_{A,max}$ |

|------------------------|--------------------|-----------------|----------------------------|

| .00 .000               |                    |                 | · A.IIIIII · · · A.IIIAX   |

|                                            | PARAMETER                                                         | TEST CONDITIONS | MIN                       | TYP | MAX                      | UNIT |

|--------------------------------------------|-------------------------------------------------------------------|-----------------|---------------------------|-----|--------------------------|------|

| V <sub>IL-Pin2</sub>                       | Input low voltage for Pin 2                                       |                 | GND –<br>0.3              |     | 0.3<br>× V <sub>DD</sub> | V    |

| V <sub>IH-Pin1</sub>                       | Input high voltage for Pin 1                                      |                 | 1.15                      |     | V <sub>DD</sub> +<br>0.3 | V    |

| V <sub>IL-Pin1</sub>                       | Input low voltage for Pin 1                                       |                 | -0.3                      |     | 0.65                     | V    |

| V <sub>IH-Pin3,4</sub>                     | Input voltage high for OTP_SEL[1:0]                               |                 | 0.7 ×<br>V <sub>DD</sub>  |     | V <sub>DD</sub> +<br>0.3 | V    |

| V <sub>IL-Pin3,4</sub>                     | Input voltage low for OTP_SEL[1:0]                                |                 | GND -<br>0.3              |     | 0.8                      | V    |

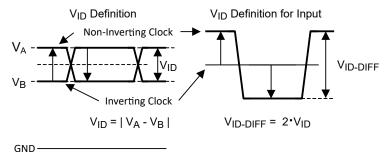

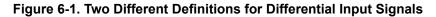

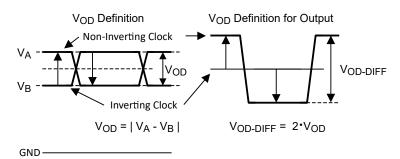

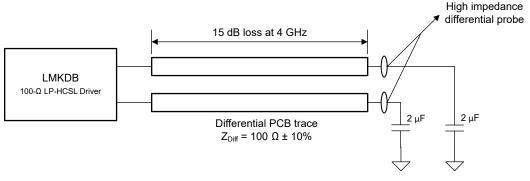

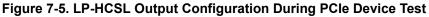

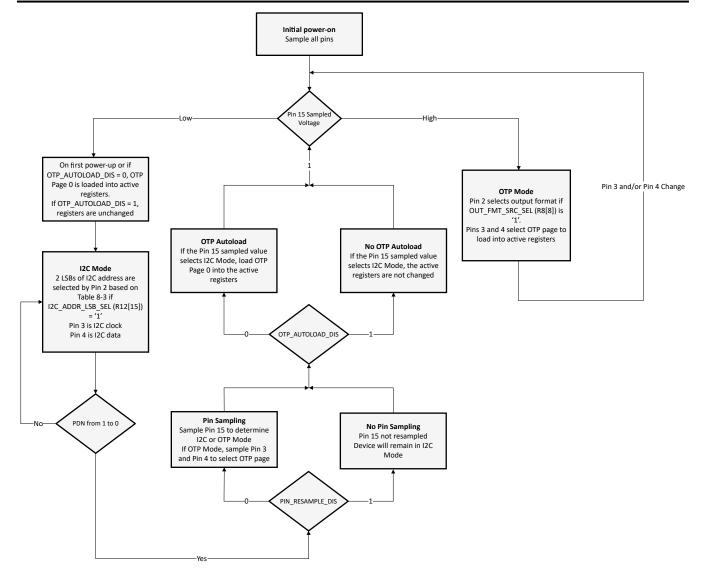

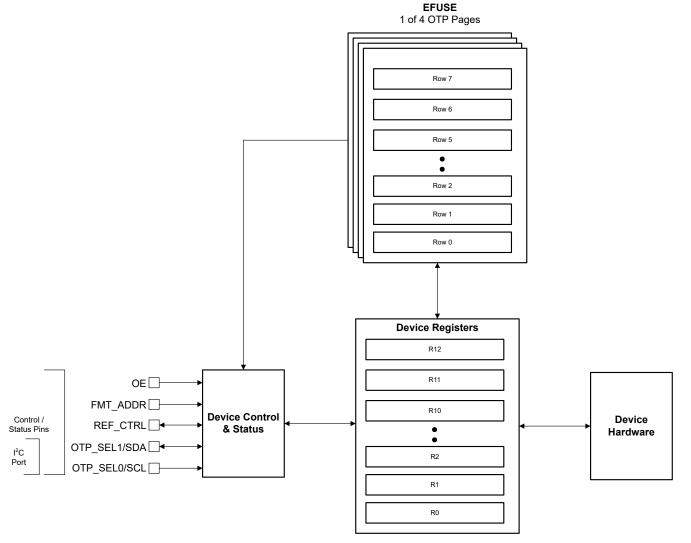

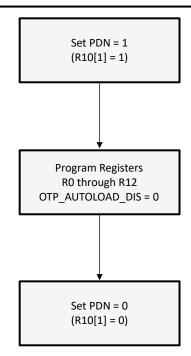

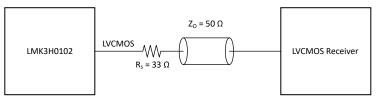

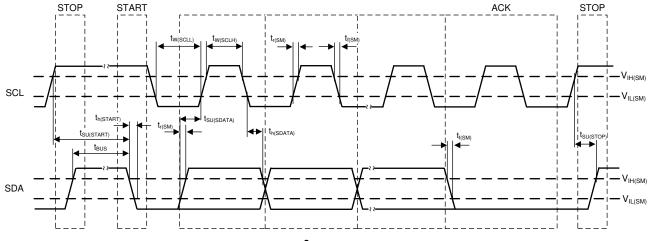

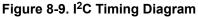

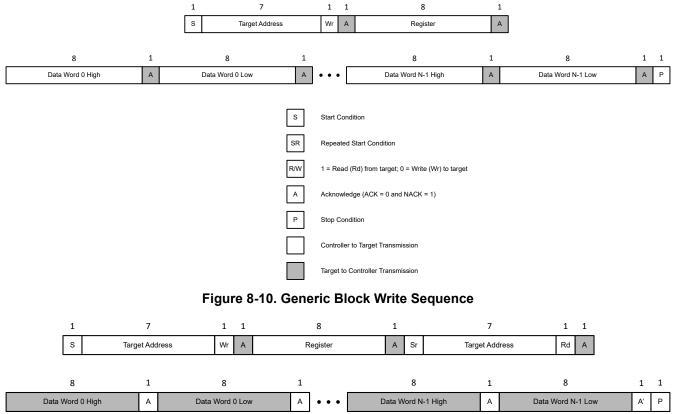

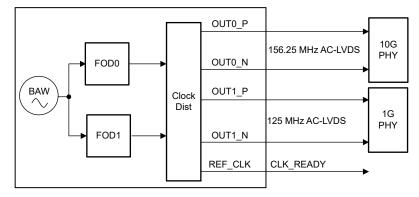

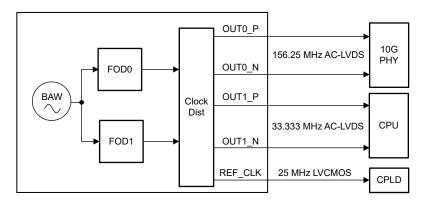

| V <sub>IH-Pin15</sub>                      | Input voltage high for Pin 15                                     |                 | 0.65 ×<br>V <sub>DD</sub> |     | V <sub>DD</sub> +<br>0.3 | V    |