# LP3950 Color LED Driver with Audio Synchronizer

Check for Samples: LP3950

### **FEATURES**

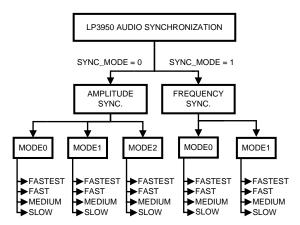

- Audio Synchronization for Color LEDs with Two Modes: Amplitude and Frequency

- Programmable Frequency and Amplitude Response with Tracking Speed Control

- Automatic Gain Control or Selectable Gain for Input Signal Optimization

- RGB Pattern Generator Similar to LP3933/LP3936

- Magnetic DC-DC Boost Converter with Programmable Boost Output Voltage

- Selectable SPI or I<sup>2</sup>C Compatible Interface

- One Pin Default Enable for Non-Serial Interface Users. One Pin Selector for Synchronization Mode

- Space Efficient 32-Pin TLGA Package

### **APPLICATIONS**

- Cellular Phones

- MP3/CD/Minidisc Players

- Tovs

### **DESCRIPTION**

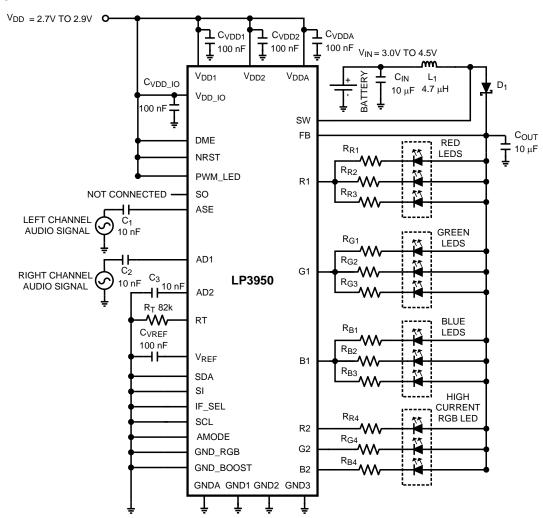

The LP3950 is a color LED driver with a built-in audio synchronization feature for any analog audio input such as polyphonic ring tones and MP3 music. LEDs can be synchronized to an audio signal with two methods - amplitude and frequency. Also several fine tuning options are available for differentiation purposes. The chip also has an unique AGC (Automatic Gain Control) feature which tracks the input signal level and automatically adjusts the gain to an optimal value.

The LP3950 has a high efficiency magnetic DC/DC converter with programmable output voltage and switching frequency. The converter has high output current capability so it is also able to drive flash LEDs in camera phone applications.

The LP3950 is similar to LP3933 and LP3936 in that the color LEDs (or RGB LEDs) can also be programmed to generate light patterns (programmable color, intensity, on/off timing, slope and blinking cycle).

All functions are software controllable through a SPI or I<sup>2</sup>C compatible interface but the device also supports one pin control for enabling predefined (default) audio synchronization mode.

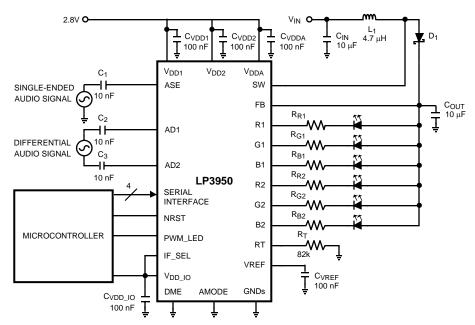

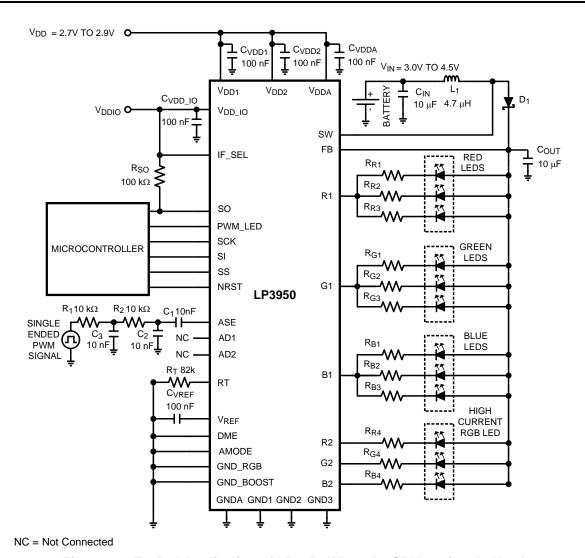

### **Typical Application**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

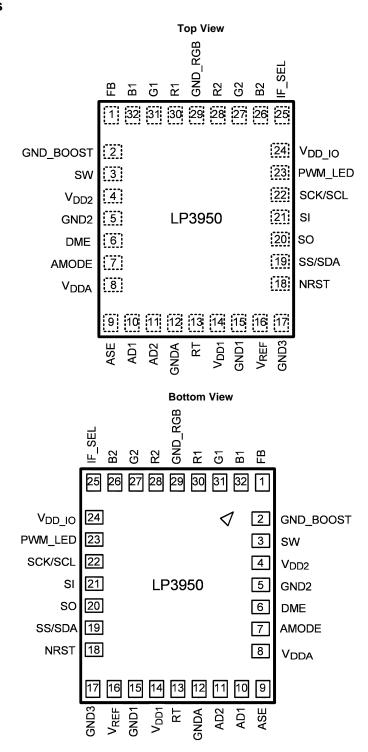

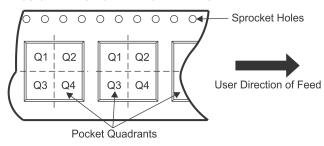

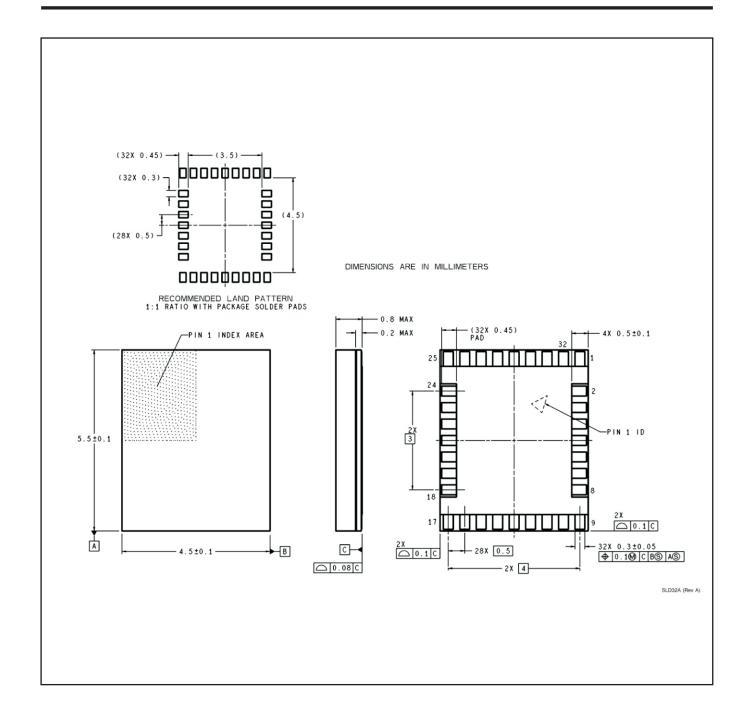

## **Connection Diagrams**

Figure 1. 32-Lead TLGA Package 4.5 x 5.5 x 0.8 mm, 0.5 mm Pitch, See Package Number NPC0032A

## **PIN DESCRIPTIONS**

| Pin# | Name             | Туре         | PIN DESCRIPTIONS  Description                           |  |

|------|------------------|--------------|---------------------------------------------------------|--|

| 1    | FB               | Input        | Boost converter feedback.                               |  |

| 2    | GND_BOOST        | Ground       | Power switch ground.                                    |  |

| 3    | SW               | Output       | Open drain, boost converter power switch.               |  |

| 4    | V <sub>DD2</sub> | Power        | Supply voltage for internal digital circuits.           |  |

| 5    | GND2             | Ground       | Ground return for V <sub>DD2</sub> (internal digital).  |  |

| 6    | DME              | Logic Input  | Default mode enable (internal pull down 1 M $\Omega$ ). |  |

| 7    | AMODE            | Logic Input  | Audio mode selection (internal pull down 1 MΩ).         |  |

| 8    | $V_{DDA}$        | Power        | Supply voltage for audio circuits.                      |  |

| 9    | ASE              | Input        | Analog audio input, single-ended.                       |  |

| 10   | AD1              | Input        | Analog audio input, differential.                       |  |

| 11   | AD2              | Input        | Analog audio input, differential.                       |  |

| 12   | GNDA             | Ground       | Ground for analog audio inputs.                         |  |

| 13   | RT               | Input        | Oscillator resistor.                                    |  |

| 14   | $V_{DD1}$        | Power        | Supply voltage for internal analog circuits.            |  |

| 15   | GND1             | Ground       | Ground.  Internal reference bypass capacitor.           |  |

| 16   | $V_{REF}$        | Output       | Internal reference bypass capacitor.                    |  |

| 17   | GND3             | Ground       | Ground.                                                 |  |

| 18   | NRST             | Logic Input  | Low active reset input.                                 |  |

| 19   | SS/SDA           | Logic I/O    | SPI slave select/ I <sup>2</sup> C data line.           |  |

| 20   | SO               | Logic Output | SPI serial data output.                                 |  |

| 21   | SI               | Logic Input  | SPI serial data input.                                  |  |

| 22   | SCK/SCL          | Logic Input  | SPI/ I <sup>2</sup> C clock.                            |  |

| 23   | PWM_LED          | Logic Input  | Direct PWM control for LEDs.                            |  |

| 24   | $V_{DDIO}$       | Power        | Supply voltage for logic IO signals.                    |  |

| 25   | IF_SEL           | Logic Input  | SPI/I <sup>2</sup> C select (IF_SEL = 1 in SPI mode).   |  |

| 26   | B2               | Output       | Open drain output, blue LED2.                           |  |

| 27   | G2               | Output       | Open drain output, green LED2.                          |  |

| 28   | R2               | Output       | Open drain output, red LED2.                            |  |

| 29   | GND_RGB          | Ground       | RGB driver ground.                                      |  |

| 30   | R1               | Output       | Open drain output, red LED1.                            |  |

| 31   | G1               | Output       | Open drain output, green LED1.                          |  |

| 32   | B1               | Output       | Open drain output, blue LED1.                           |  |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# Absolute Maximum Ratings (1)(2)(3)

| -0.3V to +7.2V                                |

|-----------------------------------------------|

| -0.3V to +6.0V                                |

| -0.3V to V <sub>DD1</sub> +0.3V with 6.0V max |

| -0.3V to $V_{DD\_IO}$ +0.3V with 6.0V max     |

| 150 mA                                        |

| 10 μΑ                                         |

| Internally Limited                            |

| 125°C                                         |

| −65°C to +150°C                               |

| 260°C                                         |

|                                               |

|                                               |

| 2 kV                                          |

| 200V                                          |

|                                               |

- All voltages are with respect to the potential at the GND pins (GND1-3, GND\_BOOST, GND\_RGB, GNDA).

- (2) Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under which operation of the device is guaranteed. Operating Ratings do not imply guaranteed performance limits. For guaranteed performance limits and associated test conditions, see the Electrical Characteristics tables.

- (3) If Military/Aerospace specified devices are required, please contact the TI Sales Office/Distributors for availability and specifications.

- (4) Battery/Charger voltage should be above 6.0V no more than 10% of the operational lifetime.

- (5) Voltage tolerance of LP3950 above 6.0V relies on fact that V<sub>DD1</sub>, V<sub>DD2</sub> and V<sub>DDA</sub> (2.8V) are available (ON) at all conditions. If V<sub>DD1</sub>, V<sub>DD2</sub> and V<sub>DDA</sub> are not available (ON) at all conditions, Texas Instruments does not guarantee any parameters or reliability for this device. Also, V<sub>DD1</sub>, V<sub>DD2</sub> and V<sub>DDA</sub> must be at the same electric potential.

- (6) The total load current of the boost converter should be limited to 300 mA.

- (7) Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at T<sub>J</sub> = 160°C (typ.) and disengages at T<sub>J</sub> = 140°C (typ.).

- (8) For detailed package and soldering specifications and information, please refer to Texas Instruments Application Note 1125 (SNAA002): Laminate CSP/FBGA.

- (9) The Human body model is a 100 pF capacitor discharged through a 1.5 kΩ resistor into each pin. The machine model is a 200 pF capacitor discharged directly into each pin. MIL-STD-883 3015.7

# Operating Ratings<sup>(1)(2)</sup>

| V (SW, FB, R1-2, G1-2, B1-2)                               | 0V to 6.0V                      |

|------------------------------------------------------------|---------------------------------|

| $V_{DD1}, V_{DD2}, V_{DDA}^{(3)}$                          | 2.7V to 2.9V                    |

| $V_{DDIO}$                                                 | 1.65V to V <sub>DD1,2</sub> V   |

| Voltage on ASE, AD1, AD2                                   | 0.1V to V <sub>DD1</sub> - 0.1V |

| Recommended Load Current                                   | 0 mA to 300 mA                  |

| Junction Temperature (T <sub>J</sub> ) Range               | -40°C to +125°C                 |

| Ambient Temperature (T <sub>A</sub> ) Range <sup>(4)</sup> | −40°C to +85°C                  |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under which operation of the device is guaranteed. Operating Ratings do not imply guaranteed performance limits. For guaranteed performance limits and associated test conditions, see the Electrical Characteristics tables.

- (2) All voltages are with respect to the potential at the GND pins (GND1-3, GND\_BOOST, GND\_RGB, GNDA).

- (3) Voltage tolerance of LP3950 above 6.0V relies on fact that V<sub>DD1</sub>, V<sub>DD2</sub> and V<sub>DDA</sub> (2.8V) are available (ON) at all conditions. If V<sub>DD1</sub>, V<sub>DD2</sub> and V<sub>DDA</sub> are not available (ON) at all conditions, Texas Instruments does not guarantee any parameters or reliability for this device. Also, V<sub>DD1</sub>, V<sub>DD2</sub> and V<sub>DDA</sub> must be at the same electric potential.

- (4) In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX-OP</sub> = 125°C), the maximum power dissipation of the device in the application (P<sub>D-MAX</sub>), and the junction-to ambient thermal resistance of the part/package in the application (θ<sub>JA</sub>), as given by the following equation: T<sub>A-MAX</sub> = T<sub>J-MAX-OP</sub> (θ<sub>JA</sub> x P<sub>D-MAX</sub>).

Product Folder Links: LP3950

### **Thermal Properties**

| Junction-to-Ambient Thermal Resistance              | 72°C/W |

|-----------------------------------------------------|--------|

| (θ <sub>JA</sub> ), NPC0032A Package <sup>(1)</sup> |        |

Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design.

# Electrical Characteristics (1)(2)

Limits in standard typeface are for  $T_J$  = +25°C. Limits in **boldface** type apply over the operating ambient temperature range (-40°C  $\le T_A \le +85$ °C). Unless otherwise noted, specifications apply to Figure 2 with:  $V_{DD1} = V_{DD2} = V_{DDA} = 2.8V$ ,  $C_{VDD1} = C_{VDD2} = C_{VDDA} = C_{VDD0} = 100$  nF,  $C_{OUT} = C_{IN} = 10$  µF,  $C_{VREF} = 100$  nF,  $C_{I} = 4.7$  µH and  $C_{I} =$

| Symbol             | Parameter                                                                                                          | Condition                                                                              | Min | Тур   | Max | Units |

|--------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----|-------|-----|-------|

| I <sub>VDD</sub>   | Standby Supply Current (V <sub>DD1</sub> + V <sub>DD2</sub> + V <sub>DDA</sub> current)                            | NSTBY = L (register)<br>SCK, SS, SI, NRST = H                                          |     | 1     | 5   | μΑ    |

|                    | No-Load Supply Current<br>(V <sub>DD1</sub> + V <sub>DD2</sub> + V <sub>DDA</sub> current, boost off)              | NSTBY = H (reg.)<br>EN_BOOST = L (reg.)<br>SCK, SS, SI, NRST = H                       |     | 300   | 400 | μΑ    |

|                    | Full Load Supply Current (V <sub>DD1</sub> + V <sub>DD2</sub> + V <sub>DDA</sub> current, boost on) <sup>(4)</sup> | NSTBY = H (reg.)<br>EN_BOOST = H (reg.)<br>SCK, SS, SI, NRST = H<br>All Outputs Active |     | 850   |     | μА    |

| I <sub>VDDIO</sub> | V <sub>DDIO</sub> Supply Current                                                                                   | 1.0 MHz SCK Frequency<br>C <sub>L</sub> = 50 pF at SO Pin                              |     | 20    |     | μΑ    |

| I <sub>VDDA</sub>  | Audio Circuitry Supply Current <sup>(5)</sup>                                                                      | INPUT_SEL = [10] (register)                                                            |     | 550   |     | μΑ    |

| $V_{REF}$          | Reference Voltage <sup>(6)</sup>                                                                                   | I <sub>REF</sub> ≤ 1.0 nA Only for Test Purpose                                        |     | 1.230 |     | V     |

- (1) All voltages are with respect to the potential at the GND pins (GND1-3, GND\_BOOST, GND\_RGB, GNDA).

- (2) Min and Max limits are guaranteed by design, test, or statistical analysis. Typical numbers are not guaranteed, but do represent the most likely norm.

- (3) Low-ESR Surface-Mount Ceramic Capacitors are used in setting electrical characteristics.

- (4) Audio block inactive.

- (5) In single-ended and in differential mode one audio buffer only is active and I<sub>VDDA</sub> will be reduced by 90 μA (typ).

- (6) V<sub>REF</sub> pin (Bandgap reference output) is for internal use only. A capacitor should always be placed between V<sub>REF</sub> and GND1.

Product Folder Links: LP3950

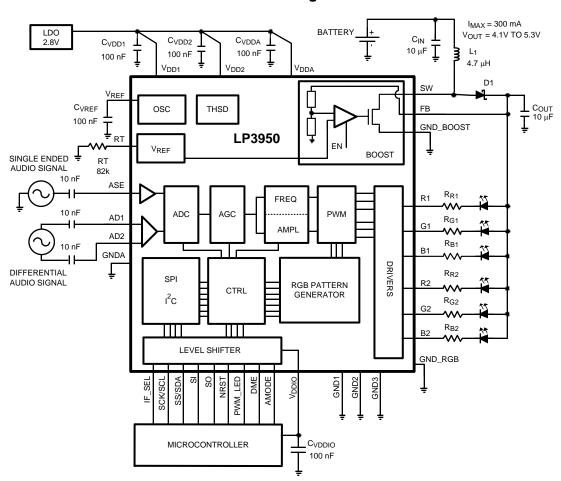

### **Block Diagram**

Figure 2. LP3950 Block Diagram

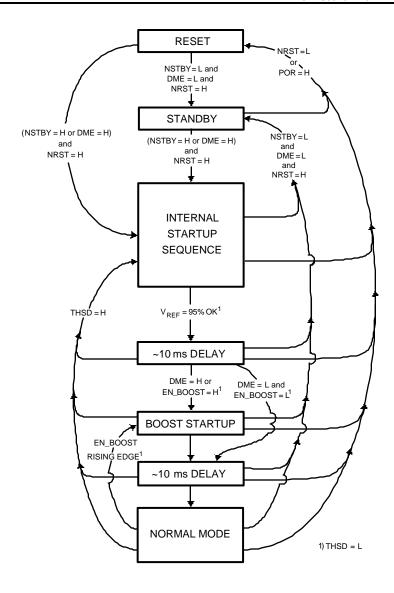

### **Modes of Operation**

**RESET:** In the RESET mode all the internal registers are reset to the default values. RESET is entered always if input NRST is LOW or internal Power On Reset is active.

**STANDBY:** The STANDBY mode is entered if the register bit NSTBY is LOW and RESET is not active. This is the low power consumption mode, when all the circuit functions are disabled. Registers can be written in this mode and the control bits are effective immediately after start up.

**STARTUP:** INTERNAL STARTUP SEQUENCE powers up all the needed internal blocks (V<sub>REF</sub>, oscillator, etc.). To ensure the correct oscillator initialization, a 10 ms delay is generated by the internal state-machine. Thermal shutdown (THSD) disables the chip operation and Startup mode is entered until no thermal shutdown event is present.

**BOOST STARTUP:** Soft start for boost output is generated in the BOOST STARTUP mode. In this mode the boost output is raised in PFM mode during the 10 ms delay generated by the state-machine. All RGB outputs are off during the 10 ms delay to ensure smooth startup. The Boost startup is entered from Internal Startup Sequence if EN\_BOOST is HIGH or from Normal mode when EN\_BOOST is written HIGH.

**NORMAL:** During the NORMAL mode the user controls the chip using the control registers. Registers can be written in any sequence and any number of bits can be altered in a register within one write cycle. If the default mode is selected, default control register values are used.

# Logic Interface Characteristics(1)

| Symbol           | Parameter                 | Conditions                 | Min                     | Тур                     | Max | Units |

|------------------|---------------------------|----------------------------|-------------------------|-------------------------|-----|-------|

| LOGIC INPU       | TS SS, SI, SCK/SCL, PWM_  | LED, IF_SEL                | -                       |                         | *   | *     |

| V <sub>IL</sub>  | Input Low Level           |                            |                         |                         | 0.5 | V     |

| V <sub>IH</sub>  | Input High Level          |                            | V <sub>DDIO</sub> - 0.5 |                         |     | V     |

| I <sub>I</sub>   | Logic Input Current       |                            | -1.0                    |                         | 1.0 | μΑ    |

| f <sub>SCL</sub> | Clock Frequency           | I <sup>2</sup> C Mode      |                         |                         | 400 | kHz   |

|                  |                           | SPI Mode                   |                         |                         | 8   | MHz   |

| LOGIC OUTI       | PUT SO                    |                            |                         |                         | -   | *     |

| V <sub>OL</sub>  | Output Low Level          | I <sub>SO</sub> = 3.0 mA   |                         | 0.3                     | 0.5 | V     |

| V <sub>OH</sub>  | Output High Level         | $I_{SO} = -3.0 \text{ mA}$ | V <sub>DDIO</sub> - 0.5 | V <sub>DDIO</sub> - 0.3 |     | V     |

| IL               | Output Leakage Current    | V <sub>SO</sub> = 2.8V     |                         |                         | 1.0 | μΑ    |

| LOGIC I/O S      | DA                        | •                          | •                       | •                       | •   | •     |

| V <sub>OL</sub>  | Output Low Level          | $I_{SDA} = 3.0 \text{ mA}$ |                         | 0.3                     | 0.5 | V     |

| LOGIC INPU       | TS DME, AMODE (Internal p | ull down 1 MΩ)             |                         |                         |     |       |

| V <sub>IL</sub>  | Input Low Level           |                            |                         |                         | 0.5 | V     |

| V <sub>IH</sub>  | Input High Level          |                            | V <sub>DDIO</sub> - 0.5 |                         |     | V     |

| l <sub>l</sub>   | Logic Input Current       |                            | -1.0                    |                         | 6.0 | μA    |

<sup>(1)</sup>  $(1.80 \text{V} \le \text{V}_{DDIO} \le \text{V}_{DD1,2} \text{V})$ . Limits in standard typeface are for  $T_J = +25^{\circ}\text{C}$ . Limits in **boldface** type apply over the operating ambient temperature range  $(-40^{\circ}\text{C} \le T_A \le +85^{\circ}\text{C})$ .

# Logic Interface Characteristics, Low I/O Voltage<sup>(1)</sup>

| Symbol           | Parameter              | Conditions                | Min                      | Тур | Max  | Units |

|------------------|------------------------|---------------------------|--------------------------|-----|------|-------|

| LOGIC INPU       | TS SCL, PWM_LED, IF_S  | EL                        |                          |     | ·    | •     |

| V <sub>IL</sub>  | Input Low Level        |                           |                          |     | 0.35 | V     |

| V <sub>IH</sub>  | Input High Level       |                           | V <sub>DDIO</sub> - 0.35 |     |      | V     |

| I <sub>I</sub>   | Logic Input Current    |                           | -1.0                     |     | 1.0  | μA    |

| f <sub>SCL</sub> | Clock Frequency        | I <sup>2</sup> C Mode     |                          |     | 200  | kHz   |

| LOGIC I/O SI     | DA .                   |                           |                          |     | *    | !     |

| V <sub>OL</sub>  | Output Low Level       | I <sub>SDA</sub> = 3.0 mA |                          | 0.3 | 0.5  | V     |

| LOGIC INPU       | TS DME, AMODE (Interna | l pull down 1 MΩ)         | 1                        |     | ,    |       |

| V <sub>IL</sub>  | Input Low Level        |                           |                          |     | 0.35 | V     |

| V <sub>IH</sub>  | Input High Level       |                           | V <sub>DDIO</sub> - 0.35 |     |      | V     |

| l <sub>l</sub>   | Logic Input Current    |                           | -1.0                     |     | 6.0  | μA    |

<sup>(1)</sup>  $(1.65V \le V_{DDIO} < 1.80V)$ .  $I^2C$  compatible interface only.

# Logic Input NRST Characteristics(1)

| Symbol            | Parameter           | Conditions                 | Min  | Тур | Max | Units |

|-------------------|---------------------|----------------------------|------|-----|-----|-------|

| V <sub>IL</sub>   | Input Low Level     |                            |      |     | 0.5 | V     |

| V <sub>IH</sub>   | Input High Level    |                            | 1.3  |     |     | V     |

| I <sub>I</sub>    | Logic Input Current |                            | -1.0 |     | 1.0 | μΑ    |

| t <sub>NRST</sub> | Reset Pulse Width   | Note: Guaranteed by design | 10   |     |     | μs    |

(1)  $(1.65V \le V_{DDIO} \le V_{DD1,2}V)$ .

#### **Control Interface**

The LP3950 supports three different interface modes:

- 1. SPI interface (4 wire, serial)

- 2. I<sup>2</sup>C compatible interface (2 wire, serial)

- 3. Direct enable (2 wire, enable lines)

User can define the serial interface by the IF\_SEL pin. The following table shows the pin configuration for both interface modes. Note that the pin configurations will be based on the status of the IF\_SEL pin.

| IF_SEL | Interface                   | Pin Con                | figuration                                                   | Comment                                                                                                                                                 |

|--------|-----------------------------|------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| HIGH   | SPI                         | SCK<br>SI<br>SO<br>SS  | (clock)<br>(data in)<br>(data out)<br>(chip select)          |                                                                                                                                                         |

| LOW    | I <sup>2</sup> C Compatible | SCL<br>SDA<br>SI<br>SO | (clock)<br>(data in/out)<br>(l <sup>2</sup> address)<br>(NC) | Use pull up resistor for SCL. Use pull up resistor for SDA. SI HIGH → address is 51'h; SI LOW → address is 50'h; Unused pin SO can be left unconnected. |

### **SPI Interface**

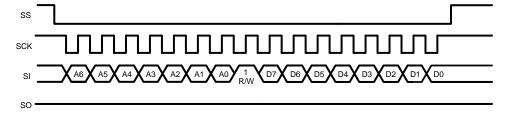

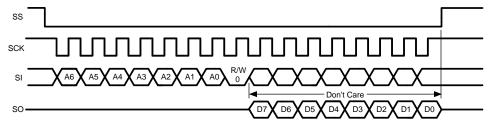

The transmission consists of 16-bit write and read cycles. One cycle consists of seven address bits, one read/write (R/W) bit and eight data bits. R/W bit high state defines a write cycle and low defines a read cycle. SO output is normally in high-impedance state and it is active only during when data is sent out during a read cycle. A pull-up or pull-down resistor may be needed for SO line if a floating logic signal can cause unintended current consumption in the circuitry.

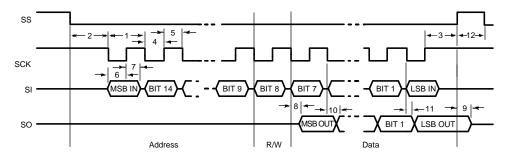

The address and data are transmitted Most Significant Byte (MSB) first. The Slave Select signal (SS) must be low during the cycle transmission. SS resets the interface when high and it has to be taken high between successive cycles. Data is clocked in on the rising edge of the SCK clock signal, while data is clocked out on the falling edge of SCK.

Figure 3. SPI Write Cycle

Figure 4. SPI Read Cycle

Copyright © 2004–2013, Texas Instruments Incorporated

Figure 5. SPI Timing Diagram

Table 1. SPI Timing Parameters<sup>(1)</sup>

| Cumbal | Parameter             | Li  | mit | Units |

|--------|-----------------------|-----|-----|-------|

| Symbol | Parameter             | Min | Max | Units |

| 1      | Cycle Time            | 80  |     | ns    |

| 2      | Enable Lead Time      | 40  |     | ns    |

| 3      | Enable Lag Time       | 40  |     | ns    |

| 4      | Clock Low Time        | 40  |     | ns    |

| 5      | Clock High Time       | 40  |     | ns    |

| 6      | Data Setup Time       | 0   |     | ns    |

| 7      | Data Hold Time        | 20  |     | ns    |

| 8      | Data Access Time      |     | 27  | ns    |

| 9      | Output Disable Time   |     | 27  | ns    |

| 10     | Output Data Valid     | -   | 37  | ns    |

| 11     | Output Data Hold Time | 0   |     | ns    |

| 12     | SS Inactive Time      | 15  |     | ns    |

<sup>(1)</sup> Data guaranteed by design.

# I<sup>2</sup>C Compatible Interface

### I<sup>2</sup>C SIGNALS

In I $^2$ C compatible mode, the LP3950 pin SCL is used for the I $^2$ C clock and the SDA pin is used for the I $^2$ C data. Both these signals need a pull-up resistor according to I $^2$ C specification. The values of the pull-up resistors are determined by the capacitance of the bus (typ. 1.8k). Signal timing specifications are shown in Table 2. Unused pin SO can be left unconnected and pin SI must be connected to  $V_{DDIO}$  or GND (address selector). Maximum bit rate is 400 kbit/s ( $V_{DDIO}$  1.80V to  $V_{DD1,2}$ V). I $^2$ C compatible interface can be used down to 1.65  $V_{DDIO}$  with maximum bit rate of 200 kbit/s.

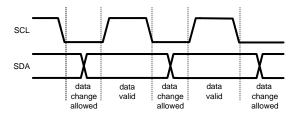

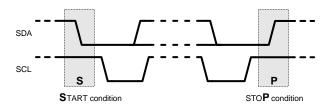

### I<sup>2</sup>C DATA VALIDITY

The data on the SDA line must be stable during the HIGH period of the clock signal (SCL). In other words, state of the data line can only be changed when CLK is LOW.

Figure 6. I<sup>2</sup>C Signals: Data Validity

#### I<sup>2</sup>C START AND STOP CONDITIONS

START and STOP bits classify the beginning and the end of the I<sup>2</sup>C session. START condition is defined as SDA signal transition from HIGH to LOW while SCL line is HIGH. STOP condition is defined as the SDA transition from LOW to HIGH while SCL is HIGH. The I<sup>2</sup>C master always generates START and STOP bits. The I<sup>2</sup>C bus is considered to be busy after START condition and free after STOP condition. During data transmission, the I<sup>2</sup>C master can generate repeated START conditions. First START and repeated START conditions are equivalent, function-wise.

Figure 7. Start and Stop Conditions

### TRANSFERRING DATA

Every byte put on the SDA line must be eight bits long, with the most significant bit (MSB) being transferred first. Each byte of data has to be followed by an acknowledge bit. The acknowledge related clock pulse is generated by the master. The transmitter releases the SDA line (HIGH) during the acknowledge clock pulse. The receiver must pull down the SDA line during the 9th clock pulse, signifying an acknowledge. A receiver which has been addressed must generate an acknowledge after each byte has been received.

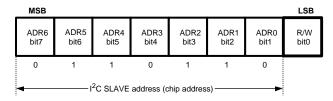

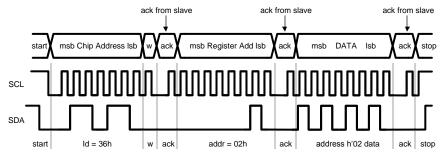

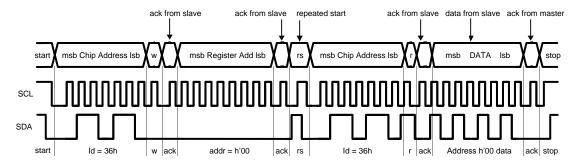

After the START condition, the  $I^2C$  master sends a chip address. This address is seven bits long followed by an eighth bit which is a data direction bit (R/W). The LP3950 address is 50'h or 51'h. The selection of the address is done by connecting SI pin to  $V_{DDIO}$  (51 hex) or GND (50 hex). For the eighth bit, a "0" indicates a WRITE and a "1" indicates a READ. The second byte selects the register to which the data will be written. The third byte contains data to write to the selected register.

Figure 8. I<sup>2</sup>C Chip Address

w = write (SDA = "0")

r = read (SDA = "1")

ack = acknowledge (SDA pulled down by either master or slave)

rs = repeated start

id = chip address, 50'h or 51'h for LP3950.

Figure 9. I<sup>2</sup>C Write Cycle

When a READ function is to be accomplished, a WRITE function must precede the READ function, as shown in Figure 10.

Figure 10. I<sup>2</sup>C Read Cycle

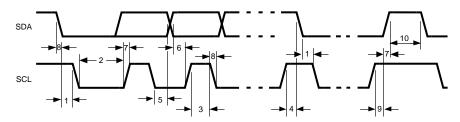

Figure 11. I<sup>2</sup>C Timing Diagram

Table 2. I<sup>2</sup>C Timing Parameters<sup>(1)</sup>

| Symbol         | Parameter                                                                                         | Lim                  | nit | Units |

|----------------|---------------------------------------------------------------------------------------------------|----------------------|-----|-------|

|                |                                                                                                   | Min                  | Max |       |

| 1              | Hold Time (repeated) START Condition                                                              | 0.6                  |     | μs    |

| 2              | Clock Low Time (1.65V ≤ V <sub>DDIO</sub> < 1.80V)                                                | 3.2                  |     | μs    |

| 2              | Clock Low Time (1.80V $\leq$ V <sub>DDIO</sub> $\leq$ V <sub>DD1,2</sub> V)                       | 1.3                  |     | μs    |

| 3              | Clock High Time (1.65V ≤ V <sub>DDIO</sub> < 1.80V)                                               | 1200                 |     | ns    |

| 3              | Clock High Time (1.80V $\leq$ V <sub>DDIO</sub> $\leq$ V <sub>DD1,2</sub> V)                      | 600                  |     | ns    |

| 4              | Setup Time for a Repeated START Condition                                                         | 600                  |     | ns    |

| 5              | Data Hold Time (data output, delay generated by LP3950)                                           | 300                  | 900 | ns    |

| 5              | Data Hold Time (data input)                                                                       | 0                    | 900 | ns    |

| 6              | Data Setup Time                                                                                   | 100                  |     | ns    |

| 7              | Rise Time of SDA and SCL                                                                          | 20+0.1C <sub>b</sub> | 300 | ns    |

| 8              | Fall Time of SDA and SCL                                                                          | 15+0.1C <sub>b</sub> | 300 | ns    |

| 9              | Set-up Time for STOP condition                                                                    | 600                  |     | ns    |

| 10             | Bus Free Time between a STOP and a START Condition                                                | 1.3                  |     | μs    |

| C <sub>b</sub> | Capacitive Load Parameter for Each Bus Line. Load of One Picofarad Corresponds to One Nanosecond. | 10                   | 200 | ns    |

(1) Data guaranteed by design

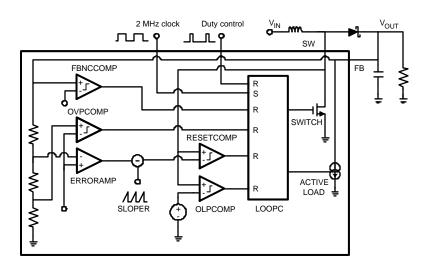

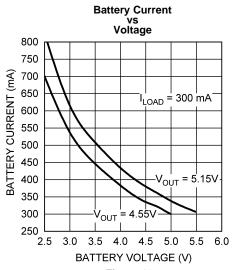

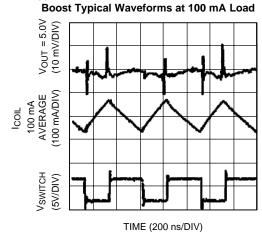

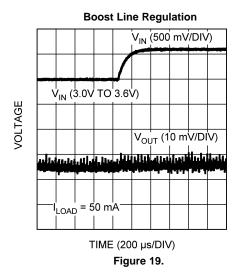

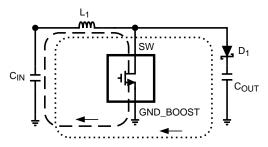

### Magnetic Boost DC/DC Converter

The boost DC/DC converter generates a 4.1V-5.3V output voltage to drive LEDs from a single Li-lon battery (3.0V to 4.5V). The output voltage is controlled with an eight-bit register in nine steps. The converter is a magnetic switching PWM mode DC/DC converter with a current limit. The converter has three options for switching frequency, 1.0 MHz, 1.67 MHz and 2.0 MHz (default), when the timing resistor RT is 82 k $\Omega$ .

The LP3950 boost converter uses an unique pulse-skipping elimination method to stabilize the noise spectrum. Even with light load or no load a minimum length current pulse is fed to the inductor. An internal active load is used to remove the excess charge from the output capacitor when needed (see **NOTE** below). The boost converter should be disabled when there is no load to avoid idle current consumption.

The topology of the magnetic boost converter is called CPM control, current programmed mode, where the inductor current is measured and controlled with the feedback. The output voltage control changes the resistor divider in the feedback loop.

Figure 12 shows the boost topology with the protection circuitry. Four different protection schemes are implemented:

- 1. Over voltage protection, limits the maximum output voltage

- Keeps the output below breakdown voltage

- Prevents boost operation if the battery voltage is much higher than desired output

- 2. Over current protection, limits the maximum inductor current

- Voltage over switching NMOS is monitored; too high voltages turn the switch off

- 3. Feedback (FB) protection for no connection

- 4. Duty cycle limit function, done with digital control

#### NOTE

When the battery voltage is close to the output voltage, the output voltage may rise slightly over programmed value if the load on output is small and pulse-skipping elimination is active.

Figure 12. Boost Converter Functional Block Diagram

# Magnetic Boost DC/DC Converter Electrical Characteristics (1)(2)

| Symbol               | Parameter                        | Conditions                                                                                                                                       | Min | Тур                                      | Max  | Units |

|----------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------------------------|------|-------|

| I <sub>LOAD</sub>    | Load Current                     | $3.0V \le V_{ N} \le 4.5V$ $V_{OUT} = 5.0V$                                                                                                      | 0   |                                          | 300  | mA    |

| V <sub>OUT</sub>     | Output Voltage Accuracy (FB Pin) | 1.0 mA $\leq$ I <sub>LOAD</sub> $\leq$ 300 mA<br>3.0V $\leq$ V <sub>IN</sub> $\leq$ 4.5V<br>V <sub>OUT</sub> = 5.0V (target value), autoload OFF | -5  |                                          | +5   | %     |

|                      | Output Voltage<br>(FB Pin)       | 1.0 mA $\leq$ I <sub>LOAD</sub> $\leq$ 300 mA<br>3.0V $<$ V <sub>IN</sub> $<$ 5.0V + V <sub>(SCHOTTKY)</sub> ,<br>autoload OFF                   |     | 5.0                                      |      | V     |

|                      |                                  | $1.0 \text{ mA} \le I_{LOAD} \le 300 \text{ mA}$ $V_{IN} > 5V + V_{(SCHOTTKY)}$                                                                  |     | V <sub>IN</sub> -V <sub>(SCHOTTKY)</sub> |      | V     |

| $RDS_{ON}$           | Switch ON Resistance             | $V_{DD1,2} = 2.8V$ , $I_{SW} = 0.5A$                                                                                                             |     | 0.4                                      | 0.7  | Ω     |

| $f_{\text{PWF}}$     | PWM Mode Switching Frequency     | RT = $82 \text{ k}\Omega$<br>freq_sel[2:0] = $1XX$                                                                                               |     | 2.0                                      |      | MHz   |

|                      | Frequency Accuracy               | $2.7 \le VDD_{1,2} \le 2.9$                                                                                                                      | -6  | ±3                                       | +6   | %     |

|                      |                                  | $RT = 82 k\Omega$                                                                                                                                | -9  |                                          | +9   | 70    |

| t <sub>PULSE</sub>   | Switch Pulse Minimum<br>Width    | No Load                                                                                                                                          |     | 25                                       |      | ns    |

| t <sub>STARTUP</sub> | Startup Time                     |                                                                                                                                                  |     | 15                                       |      | ms    |

| I <sub>CL_OUT</sub>  | SW Pin Current Limit             |                                                                                                                                                  | 700 | 800                                      | 900  | A     |

|                      |                                  |                                                                                                                                                  | 500 |                                          | 1000 | mA    |

<sup>(1)</sup> Limits in standard typeface are for  $T_J = +25^{\circ}C$ . Limits in **boldface** type apply over the operating ambient temperature range ( $-40^{\circ}C \le T_A$ Elmits in standard typerace are for T<sub>J</sub> = +25 C. Limits in **boldrace** type apply over the operating ambient temperature range (-40 C S T<sub>A</sub> S +85°C). Unless otherwise noted, specifications apply to Figure 2 with: V<sub>DD1</sub> = V<sub>DD2</sub> = V<sub>DDA</sub> = 2.8V, C<sub>VDD1</sub> = C<sub>VDD2</sub> = C<sub>VDDA</sub> = C<sub>VDDI0</sub> = 100 nF, C<sub>OUT</sub> = C<sub>IN</sub> = 10 μF, C<sub>VREF</sub> = 100 nF, L<sub>1</sub> = 4.7 μH and f<sub>BOOST</sub> = 2.0 MHz.

(2) Low-ESR Surface-Mount Ceramic Capacitors are used in setting electrical characteristics.

# **Boost Standby Mode**

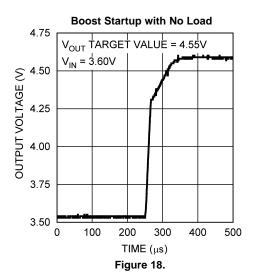

User can set the boost converter to STANDBY mode by writing the register bit EN BOOST low when there is no load to avoid idle current consumption. When EN BOOST is written high, the converter starts in PFM (Pulse Frequency Modulation) mode for 10 ms and then goes to PWM (Pulse Width Modulation ) mode. All RGB outputs are off during the 10 ms delay.

### **Boost Output Voltage Control**

User can control the boost output voltage by eight-bit boost output voltage register according to the following table.

| BOOST[7:0]<br>Register 0D'h |     | BOOST Output Voltage<br>(typical) |

|-----------------------------|-----|-----------------------------------|

| Binary                      | Hex |                                   |

| 0000 0000                   | 00  | 4.10                              |

| 0000 0001                   | 01  | 4.25                              |

| 0000 0011                   | 03  | 4.40                              |

| 0000 0111                   | 07  | 4.55                              |

| 0000 1111                   | 0F  | 4.70                              |

| 0001 1111                   | 1F  | 4.85                              |

| 0011 1111                   | 3F  | 5.00 Default                      |

| 0111 1111                   | 7F  | 5.15                              |

| 1111 1111                   | FF  | 5.30                              |

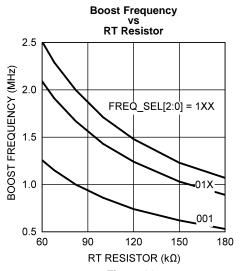

# **Boost Frequency Control**

The register 'boost frequency' has address 0C'h. The default value after reset is 07'h. 'x' means don't care.

| FREQ_SEL[2:0] | Frequency |

|---------------|-----------|

| 1xx           | 2.00 MHz  |

| 01x           | 1.67 MHz  |

| 001           | 1.00 MHz  |

Copyright © 2004–2013, Texas Instruments Incorporated

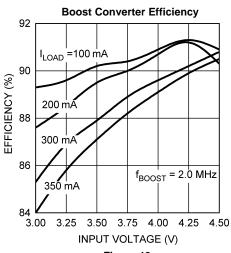

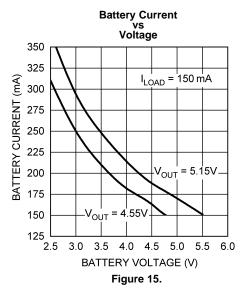

# **Boost Converter Typical Performance Characteristics**

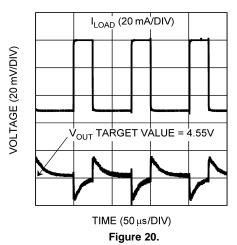

$V_{IN}$  = 3.6V,  $V_{OUT}$  = 5.0V if not otherwise stated.

Figure 14.

Figure 16.

# **Boost Converter Typical Performance Characteristics (continued)**

$V_{IN} = 3.6V$ ,  $V_{OUT} = 5.0V$  if not otherwise stated.

Figure 17.

Boost Load Transient Response, 50 mA to 100 mA

#### **RGB LED Pattern Generator**

The LP3950 RGB outputs can be controlled either with audio synchronization or with RGB pattern generator.

The pattern generator of LP3950 drives three independently controlled LED outputs (for example, R1, G1 and B1). The functionality is similar compared to RGB functionality of LP3936 and LP3933.

The output of RGB pattern generator can be selected to drive RGB1 (R1-G1-B1), RGB2 (R2-G2-B2) or RGB1 and RGB2 (R1&R2 – G1&G2 – B1&B2) outputs.

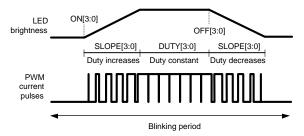

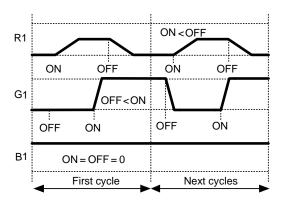

### **Programmable Pattern Mode**

User has control over the following parameters separately for each LED:

ON and OFF (start and stop time in blinking cycle)

**DUTY** (PWM brightness control)

**SLOPE** (dimming slope)

**ENABLE** (output enable control)

The main blinking cycle is controlled with three-bit CYCLE control (0.25 / 0.5 / 1.0 / 2.0 / 4.0s).

Figure 21. RGB PWM Operating Principle

RGB\_START is the master control for the whole RGB function. The internal PWM and blinking control can be disabled by setting the RGB\_PWM control LOW. In this case the individual enable controls can be used to switch outputs on and off. PWM\_EN input can be used for external hardware PWM control.

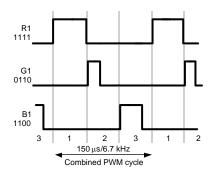

In the normal PWM mode the R, G and B switches are controlled in 3 phases (one phase per driver). During each phase the peak current set by an external ballast resistor is driven through the LED for the time defined by DUTY setting (0  $\mu$ s to 50  $\mu$ s). As a time averaged current this means 0% to 33% of the peak current. The PWM period is 150  $\mu$ s and the pulse frequency is 6.67 kHz in normal mode.

Figure 22. Normal Mode PWM Waveforms at Different Duty Settings

In the FLASH mode all the outputs are controlled in one phase and the PWM period is 50 µs. The time averaged FLASH mode current is three times the normal mode current at the same DUTY value.

Product Folder Links: LP3950

Figure 23. Example Blinking Waveforms

## **RGB Driver Characteristics**

(R1, G1, B1, R2, G2, B2 outputs). Limits in standard typeface are for  $T_J = +25^{\circ}C$ . Limits in **boldface** type apply over the operating ambient temperature range ( $-40^{\circ}C \le T_A \le +85^{\circ}C$ ).

| Symbol                  | Parameter                 | Conditions                             | Min | Тур  | Max  | Units |

|-------------------------|---------------------------|----------------------------------------|-----|------|------|-------|

| R <sub>DS-ON</sub>      | ON Resistance             |                                        |     | 3.5  | 6.0  | Ω     |

| I <sub>LEAKAGE</sub>    | Off State Leakage Current | V <sub>FB</sub> = 5.0V, LED driver off |     | 0.03 | 1.0  | μΑ    |

| t <sub>SMAX</sub>       | Maximum Slope Period      | At Maximum Duty Setting                |     | 0.93 |      | s     |

| t <sub>SMIN</sub>       | Minimum Slope Period      | At Maximum Duty Setting                |     | 31   |      | ms    |

| t <sub>SRES</sub>       | Slope Resolution          | At Maximum Duty Setting                |     | 62   |      | ms    |

| t <sub>START/STOP</sub> | Start/Stop Resolution     | Cycle 1.0s                             |     | 1/16 |      | S     |

| Duty                    | Duty Step Size            |                                        |     | 1/16 |      |       |

| t <sub>BLINK</sub>      | Blinking Cycle Accuracy   |                                        | -6  | ±3   | +6   | %     |

| D <sub>CYCF</sub>       | Duty Cycle Range          | EN_FLASH = 1                           | 0   |      | 99.6 | %     |

| D <sub>CYC</sub>        | Duty Cycle Range          | EN_FLASH = 0                           | 0   |      | 33.2 | %     |

| D <sub>RESF</sub>       | Duty Resolution           | EN_FLASH = 1 (4-bit)                   |     | 6.64 |      | %     |

| D <sub>RES</sub>        | Duty Resolution           | EN_FLASH = 0 (4-bit)                   |     | 2.21 |      | %     |

| f <sub>PWMF</sub>       | PWM Frequency             | EN_FLASH = 1                           |     | 20   |      | kHz   |

| f <sub>PWM</sub>        | PWM Frequency             | EN_FLASH = 0                           |     | 6.67 |      | kHz   |

# Table 3. RGB LED PWM Control (1)

| RDUTY[3:0]<br>GDUTY[3:0]<br>BDUTY[3:0]                                     | DUTY sets the brightness of the LED by adjusting the duty cycle of the PWM driver. The minimum DUTY cycle is 0% [0000] and the maximum in the flash mode is 100% [1111]. The peak pulse current is determined by the external resistor, LED forward voltage drop and the boost voltage. In the normal mode the maximum duty cycle is 33%.                                                                                                                                                                                                    |

|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSLOPE[3:0]<br>GSLOPE[3:0]<br>BSLOPE[3:0]                                  | SLOPE sets the turn-on and turn-off slopes. Fastest slope is set by [0000] and slowest by [1111]. SLOPE changes the duty cycle at constant, programmable rate. For each slope setting the maximum slope time appears at maximum DUTY setting. When DUTY is reduced, the slope time decreases proportionally. For example, in case of maximum DUTY, the sloping time can be adjusted from 31 ms [0000] to 930 ms [1111]. For DUTY [0111] the sloping time is 14 ms [0000] to 434 ms [1111]. The blinking cycle has <b>no</b> effect on SLOPE. |

| RON[3:0]<br>GON[3:0]<br>BON[3:0]                                           | ON sets the beginning time of the turn-on slope. The on-time is relative to the selected blinking cycle length. On-setting N (N = 0–15) sets the on-time to N/16 $^{\star}$ cycle length.                                                                                                                                                                                                                                                                                                                                                    |

| ROFF[3:0]<br>GOFF[3:0]<br>BOFF[3:0]<br>ROFF[3:0]<br>GOFF[3:0]<br>BOFF[3:0] | OFF sets the beginning time of the turn-off slope. Off-time is relative to blinking cycle length in the same way as on-time.                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                            | If ON = 0, OFF = 0 and RGB_PWM = 1, then RGB outputs are continuously on (no blinking), the DUTY setting controls the brightness and the SLOPE control is ignored.  If ON and OFF are the same, but not 0, RGB outputs are turned off.                                                                                                                                                                                                                                                                                                       |

| CYCLE[2:0]                                                                 | CYCLE sets the blinking cycle: [000] for 0.25s, [001] for 0.5s, [010] for 1.0s, [011] for 2.0s. and [1XX] for 4.0s CYCLE effects to all RGB LEDs.                                                                                                                                                                                                                                                                                                                                                                                            |

| RSW1<br>GSW1<br>BSW1<br>RSW2<br>GSW2<br>BSW2                               | Enable for R1 switch Enable for G1 switch Enable for B1 switch Enable for R2 switch Enable for G2 switch Enable for B2 switch                                                                                                                                                                                                                                                                                                                                                                                                                |

| RGB_START                                                                  | Master Switch for both RGB drivers:  RGB_START = 0 → RGB OFF  RGB_START = 1 → RGB ON, starts the new cycle from t = 0                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RGB_PWM                                                                    | RGB_PWM = 0 → RSW, GWS and BSW control directly the RGB outputs (on/off control only) RGB_PWM = 1 → Normal PWM RGB functionality (duty, slope, on/off times, cycle)                                                                                                                                                                                                                                                                                                                                                                          |

| EN_FLASH                                                                   | Flash mode enable control for RGB1 and RGB2. In the flash mode (EN_FLASH = 1) RGB outputs are PWM controlled simultaneously, not in 3-phase system as in the normal mode.                                                                                                                                                                                                                                                                                                                                                                    |

| R1_PWM<br>G1_PWM<br>B1_PWM<br>R2_PWM<br>G2_PWM<br>B2_PWM                   | xx_PWM = 0 → External PWM control from PWM_LED pin is disabled xx_PWM = 1 → External PWM control from PWM_LED pin is enabled Internal PWM control (DUTY) can be used independently of external PWM control. External PWM has the same effect on all enabled outputs.                                                                                                                                                                                                                                                                         |

<sup>(1)</sup> The LP3933 shares the same pattern generator. Application Note AN-1291 (SNVA069), "Driving RGB LEDs Using LP3933 Lighting Management System" contains a thorough description of the RGB driver functionality including programming examples.

PWM\_LED input can be used as a direct on/off or PWM brightness control for selected RGB outputs. For example it can trigger the flash using a flash signal from the camera. If  $PWM_LED$  input is not used, it must be tied to  $V_{DDIO}$ .

#### **AUDIO SYNCHRONIZATION**

The LEDs connected to the RGB outputs can be synchronized to incoming audio signal with Audio Synchronization feature. Audio Synchronization has two modes. **Amplitude mode** synchronizes LEDs based on the peak amplitude of the input signal. In the amplitude mode the user can select one of three amplitude mapping options. The **frequency mode** synchronizes the LEDs based on bass, middle and treble amplitudes (= low pass, band pass and high pass filters). The user can select between two different responses of frequency for best audio-visual user experience. Both of the modes provide a control for speed of the mapping with four different speed configurations. Programmable gain and AGC (Automatic Gain Control) function are also available for adjustment of the optimum audio signal mapping. The Audio Synchronization functionality is described more closely below.

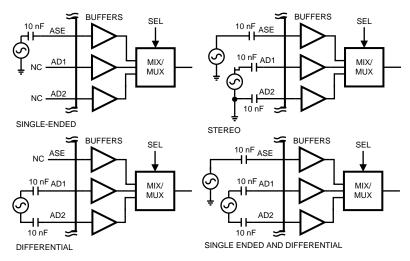

#### **INPUT SIGNAL TYPE**

The LP3950 support four types of analog audio input signals for audio synchronization

- 1. Single ended audio

- 2. Differential audio

- 3. Stereo

- 4. Single ended and differential audio.

Figure 24 shows how to wire the LP3950 audio inputs case by case (NC = Not Connected).

### USING A DIGITAL PWM AUDIO SIGNAL AS AN AUDIO SYNCHRONIZATION SOURCE

If the input signal is a PWM signal, use a first or second order low pass filter to convert the digital PWM audio signal into an analog waveform. There are two parameters that need to be known to get the filter to work successfully: frequency of the PWM signal and the voltage level of the PWM signal. Suggested cut-off frequency (-3dB) should be around 2 kHz to 4 kHz and the stop-band attenuation at sampling frequency should be around -48dB or better. Use a resistor divider to reduce the digital signal amplitude to meet the specification of the analog audio input. Because a low-order low-pass filter attenuates the high-frequency components from audio signal, MODE\_CONTROL=[01] selection is recommended when frequency synchronization mode is enabled. Figure 33 shows an example of a second order RC-filter for 29 kHz PWM signal with 3.3V amplitude. Active filters, such as a Sallen-Key filter, may also be applied. An active filter gives better stop-band attenuation and cut-off frequency can be higher than for a RC-filter.

To make sure that the filter rolls off sufficiently quickly, connect your filter circuit to the audio input(s), turn on the audio synchronization feature, set manual gain to maximum, apply the PWM signal to the filter input and keep an eye on LEDs. If they are blinking without an audio signal (modulation), a sharper roll-off after the cut-off frequency, more stop-band attenuation, or smaller amplitude of the PWM signal is required.

Figure 24. Wiring Diagram for LP3950 Audio Inputs

Product Folder Links: *LP*3950

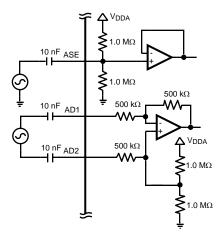

### **INPUT BUFFERING**

Figure 25 describes the LP3950 audio input buffering structure in high level. The electric parameters of the buffers are described in Table 4. Operational amplifiers for both buffers are rail-to-rail input opamps. The single ended buffer is simply a voltage follower. DC level of the input signal is generated by a resistor divider. The differential amplifier is a basic differential-to-single-ended converter.

Figure 25. Audio Input Buffer Structure

### **AUDIO SYNCHRONIZATION SIGNAL PATH**

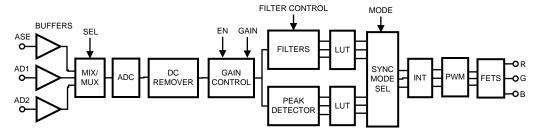

LP3950 audio synchronization is mainly done digitally and it consists of the following signal path blocks (see Figure 26):

- Input buffers

- Multiplexer

- AD converter

- DC remover

- Automatic gain control (AGC) / programmable gain

- · 3 band digital filter

- Peak detector

- Look-up tables (LUT)

- Mode selector

- Integrators

- PWM generator

### **Functional Block Diagram**

Figure 26. Signal Path Block Diagram

Copyright © 2004–2013, Texas Instruments Incorporated

The digitized input signal has a DC component that is removed by the digital **DC REMOVER** (-3 dB @ 400 Hz). The automatic **GAIN CONTROL** adjusts the input signal to suitable range automatically. User can disable AGC and the gain can be set manually with **PROGRAMMABLE GAIN**. The LP3950 has two audio synchronization modes: amplitude and frequency. For amplitude based synchronization the **PEAK DETECTION** method is used. For frequency based synchronization the three-way crossover **FILTER** separates high pass, low pass and band pass signals. For both modes, a predefined lookup table (LUT) is used to match the audio visual effect. The **MODE SELECTOR** selects the synchronization mode. Reaction speed can be selected using **INTEGRATOR** speed variables. Finally **PWM GENERATOR** sets the driver FETs duty cycles.

**Table 4. Audio Synchronization Characteristics**

| Symbol                 | Parameter                                                     | Conditions                         | Min | Тур                       | Max                   | Units |

|------------------------|---------------------------------------------------------------|------------------------------------|-----|---------------------------|-----------------------|-------|

| Zin                    | Input Impedance of AD1, AD2, ASE pins                         |                                    | 200 | 500                       |                       | kΩ    |

| A <sub>IN_SINGLE</sub> | Audio Input Level Range (peak-to-peak),<br>Single Ended Audio |                                    | 0.1 |                           | V <sub>DDA</sub> -0.1 | V     |

| A <sub>IN_DIFF</sub>   | Audio Input Level Range (peak-to-peak),<br>Differential Audio |                                    | 0.1 |                           | V <sub>DDA</sub> -0.1 | V     |

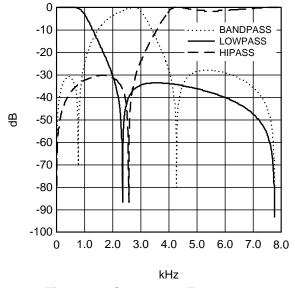

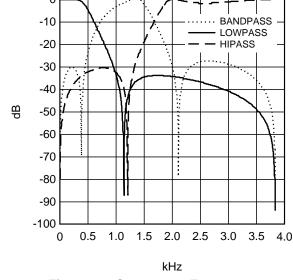

| f <sub>3 dB</sub>      | Crossover Frequencies (-3 dB)                                 |                                    |     |                           |                       |       |

|                        | Narrow Frequency Response                                     | Low Pass<br>Band Pass<br>High Pass |     | 0.5<br>1.0 and 1.5<br>2.0 |                       | kHz   |

|                        | Wide Frequency Response                                       | Low Pass<br>Band Pass<br>High Pass |     | 1.0<br>2.0 and 3.0<br>4.0 |                       |       |

### **CONTROL OF AUDIO SYNCHRONIZATION**

The following table describes the controls required for audio synchronization. Note that these controls are functional when using serial interface (I<sup>2</sup>C or SPI) for device control. Also LP3950 audio synchronization functionality is illustrated in Figure 27.

**Table 5. Audio Synchronization Control**

| EN_SYNC         | Audio synchronization ena                                                                                                                                    | Audio synchronization enabled. Set EN_SYNC = 1 to enable audio synchronization or 0 to disable.                                                                        |                                     |                             |  |  |  |  |  |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------------------|--|--|--|--|--|--|--|

| SYNC_MODE       | Synchronization mode selector. Set SYNC_MODE = 0 for amplitude synchronization. Set SYNC_MODE = 1 for frequency synchronization.                             |                                                                                                                                                                        |                                     |                             |  |  |  |  |  |  |  |

| MODE_CTRL[1:0]  | See below: Mode control                                                                                                                                      | See below: Mode control                                                                                                                                                |                                     |                             |  |  |  |  |  |  |  |

| EN_AGC          |                                                                                                                                                              | Automatic gain control. Set EN_AGC = 1 to enable automatic control or 0 to disable. When EN_AGC is disabled, the audio input signal gain value is defined by GAIN_SEL. |                                     |                             |  |  |  |  |  |  |  |

| GAIN_SEL[2:0]   | Input signal gain control.                                                                                                                                   | Gain has a range from 0 dl                                                                                                                                             | B to 21 dB with 3 dB steps:         |                             |  |  |  |  |  |  |  |

|                 | [000] 0 dB                                                                                                                                                   | [011] 9 dB                                                                                                                                                             | [110] 18 dB                         |                             |  |  |  |  |  |  |  |

|                 | [001] 3 dB                                                                                                                                                   | [111] 21 dB                                                                                                                                                            |                                     |                             |  |  |  |  |  |  |  |

|                 | [010] 6 dB                                                                                                                                                   | [101] 15 dB                                                                                                                                                            |                                     |                             |  |  |  |  |  |  |  |

| INPUT_SEL[1:0]  | [00] Single ended input<br>[01] Differential input si<br>[10] Stereo input or sin<br>Note: Sum of input signal:<br>[11] No input<br>Please see Figure 24 for | gnal, AD1 and AD2.<br>gle ended and differential i<br>s divided by 2.                                                                                                  | input signal.                       |                             |  |  |  |  |  |  |  |

| SPEED_CTRL[1:0] | Control for speed of the m                                                                                                                                   | napping. Sets the reaction                                                                                                                                             | speed (or "sampling rate")          | for the audio input signal: |  |  |  |  |  |  |  |

|                 | [00] FASTEST [01] FAST [10] MEDIUM                                                                                                                           |                                                                                                                                                                        |                                     |                             |  |  |  |  |  |  |  |

|                 | [11] SLOW                                                                                                                                                    |                                                                                                                                                                        |                                     |                             |  |  |  |  |  |  |  |

|                 | In the amplitude mode f <sub>MA</sub>                                                                                                                        | $A_{X} = 3.8 \text{ Hz}$ , in the frequence                                                                                                                            | cy mode $f_{MAX} = 7.6 \text{ Hz}.$ |                             |  |  |  |  |  |  |  |

Product Folder Links: LP3950

Figure 27. LP3950 Audio Synchronization Functionality

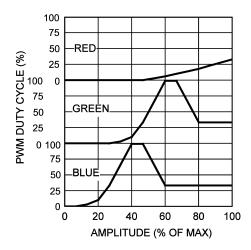

### MODE CONTROL IN THE FREQUENCY MODE

During the frequency mode (SYNC\_MODE = 1) the user can select between two filter options by MODE\_CTRL[1:0] as shown below (Figure 29). User can select the filters based on the music type and light effect requirements. Filter options: Left figure, wide frequency response; MODE\_CTRL[1:0] is set to [00], [10] or [11]. Right figure, narrow frequency response: MODE\_CTRL[1:0] set to [01]. Signal passed through the lowpass filter is used to control the duty cycle of red LEDs (R1 and/or R2 PWM outputs), the signal passed through the bandpass filter is used to control green LEDs (G1 and/or G2 PWM outputs) and high pass signal controls blue LEDs (B1 and/or B2 PWM outputs). Finally, the user can select the desired mapping speed by SPEED\_CTRL[1:0]. Of course, the user can connect any color LED to any output in his/her own application (i.e. the red output does not need to drive a red LED). Maximum duty cycle is 100% as in the Flash mode (not 33% as in the normal mode of the pattern generator, which is described in Table 3).

Figure 28. Cross-over Frequency Left: Wide Frequency Response

Figure 29. Cross-over Frequency Right: Narrow Frequency Response

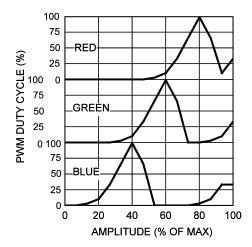

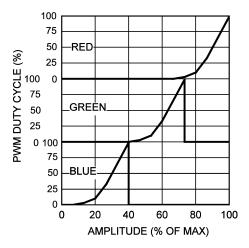

### MODE CONTROL IN THE AMPLITUDE MODE

During the amplitude synchronization mode (SYNC\_MODE = 0) the user can select between three different amplitude mappings by using MODE\_CTRL[1:0] select. These three mapping options give different light responses as shown in Figure 30. Again, the user can select the desired mapping speed by SPEED\_CTRL[1:0]. Maximum duty cycle is 100%. If MODE\_CTRL[1:0] = 11 and SYNC\_MODE = 0, audio synchronization is inactive.

$MODE\_CTRL[1:0] = [00] = MODE0$

MODE\_CTRL[1:0] = [01] = MODE1

$MODE\_CTRL[1:0] = [10] = MODE2$

This figure is for illustrating purpose only and does not necessarily represent the accurate function of the circuit.

Figure 30. Amplitude Synchronization Mapping Options

#### MODE CONTROL IN THE DEFAULT MODE

One of the main benefits of LP3950 is the default mode, which enables user to build applications without I<sup>2</sup>C or SPI control. The LP3950 is set to the default mode when DME pin is high. DME pin high –state forces registers NSTBY and EN\_SYNC to the high [1] state so that the start-up sequence get started (see start-up sequence on Modes of Operation). Function of LP3950 in the default mode of operation is controlled by AMODE pin. If AMODE is pulled low the LP3950 is in the amplitude synchronization mode. If the AMODE pin is pulled high the LP3950 is in the frequency synchronization mode. In the default mode default control register values are used, see Table 8. Please refer to Figure 32 in Typical Applications for wiring.

### **RGB OUTPUT SELECTOR**

The usage of RGB outputs (RGB1 and RGB2) can be selected with RGB\_SEL[1:0] control bits. Audio synchronization and RGB pattern generator output can be connected to RGB ports as shown in the following table.

RGB\_SEL[0] RGB\_SEL[1] **RGB1 Output Control RGB2 Output Control** Pattern Generator Pattern Generator 1 0 Audio Sync Pattern Generator 0 Pattern Generator Audio Sync 1 1 Audio Sync Audio Sync

**Table 6. RGB Output Control**

### **Recommended External Components**

### **OUTPUT CAPACITOR, COUT**

The output capacitor  $C_{OUT}$  directly affects the magnitude of the output ripple voltage. In general, the higher the value of  $C_{OUT}$ , the lower the output ripple magnitude. Multilayer ceramic capacitors with low ESR (Equivalent Series Resistance) are the best choice. At the lighter loads, the low ESR ceramics offer a much lower  $V_{OUT}$  ripple than the higher ESR tantalums of the same value. At the higher loads, the ceramics offer a slightly lower  $V_{OUT}$  ripple magnitude than the tantalums of the same value. However, the dv/dt of the  $V_{OUT}$  ripple with the ceramics is much lower that the tantalums under all load conditions. Capacitor voltage rating must be sufficient, 10V is recommended.

Some ceramic capacitors, especially those in small packages, exhibit a strong capacitance reduction with the increased applied voltage. The capacitance value can fall to below half of the nominal capacitance. Too low output capacitance can make the boost converter unstable.

### INPUT CAPACITOR, CIN

The input capacitor  $C_{IN}$  directly affects the magnitude of the input ripple voltage and to a lesser degree the  $V_{OUT}$  ripple. A higher value  $C_{IN}$  will give a lower  $V_{IN}$  ripple. Capacitor voltage rating must be sufficient, 10V is recommended.

### OUTPUT DIODE, D<sub>1</sub>

A Schottky diode should be used for the output diode. To maintain high efficiency the average current rating of the schottky diode should be larger than the peak inductor current (1.0A). Schottky diodes with a low forward drop and fast switching speeds are ideal for increasing efficiency in portable applications. Choose a reverse breakdown of the schottky diode larger than the output voltage. Do not use ordinary rectifier diodes, since slow switching speeds and long recovery times cause the efficiency and the load regulation to suffer.

#### INDUCTOR, L<sub>1</sub>

LP3950's high switching frequency enables the use of a small surface mount inductor. A 4.7  $\mu$ H shielded inductor is suggested for 2.0 MHz switching frequency. Values below 2.2  $\mu$ H should not be used at 2.0 MHz. At lower switching frequencies 4.7  $\mu$ H inductors should always be used. The inductor should have a saturation current rating higher than the peak current it will experience during circuit operation (1.0A). Less than 300 m $\Omega$  ESR is suggested for high efficiency. Open core inductors cause flux linkage with circuit components and, thus, may interfere with the normal operation of the circuit. This should be avoided. For high efficiency, choose an inductor with a high frequency core material such as ferrite to reduce the core losses. To minimize radiated noise, use a toroid, pot core or shielded core inductor. The inductor should be connected to the SW pin as close to the IC as possible. Examples of suitable inductors are TDK type VLF4012AT- 4R7M1R1 and Coilcraft type MSS4020-472MLD.

**Table 7. List of Recommended External Components**

| Symbol                                              | Symbol Explanation                                                        | Value    | Unit   | Туре                                        |

|-----------------------------------------------------|---------------------------------------------------------------------------|----------|--------|---------------------------------------------|

| C <sub>VDD1</sub>                                   | V <sub>DD1</sub> Bypass Capacitor                                         | 100      | nF     | Ceramic, X5R                                |

| C <sub>VDD2</sub>                                   | V <sub>DD2</sub> Bypass Capacitor                                         | 100      | nF     | Ceramic, X5R                                |

| C <sub>OUT</sub>                                    | Output Capacitor from FB to GND                                           | 10 ± 10% | μF     | Ceramic, X5R                                |

| C <sub>IN</sub>                                     | Input Capacitor from Battery Voltage to GND                               | 10 ± 10% | μF     | Ceramic, X5R                                |

| C <sub>VDDIO</sub>                                  | V <sub>DD_IO</sub> Bypass Capacitor                                       | 100      | nF     | Ceramic, X5R                                |

| C <sub>VDDA</sub>                                   | V <sub>DDA</sub> Bypass Capacitor                                         | 100      | nF     | Ceramic, X5R                                |

| C <sub>1,2,3</sub>                                  | Audio Input Capacitors                                                    | 10       | nF     | Ceramic, X5R                                |

| R <sub>T</sub>                                      | Oscillator Frequency Bias Resistor                                        | 82       | kΩ     | 1% <sup>(1)</sup>                           |

| R <sub>SO</sub>                                     | SO Output Pull-up Resistor                                                | 100      | kΩ     |                                             |

| C <sub>VREF</sub>                                   | Reference Voltage Capacitor, between $V_{\mbox{\scriptsize REF}}$ and GND | 100      | nF     | Ceramic, X5R                                |

| L <sub>1</sub>                                      | Boost Converter Inductor                                                  | 4.7      | μΗ     | Shielded, Low ESR,<br>I <sub>SAT</sub> 1.0A |

| D <sub>1</sub>                                      | Rectifying Diode, V <sub>F</sub> @ Maxload                                | 0.3      | V      | Schottky Diode                              |

|                                                     | RGB LED                                                                   |          |        |                                             |

|                                                     | Red, Green, Blue or White LEDs                                            |          | User D | Defined                                     |

| R <sub>RX</sub> , R <sub>GX</sub> , R <sub>BX</sub> | Current Limit Resistors                                                   |          |        |                                             |

<sup>(1)</sup> Resistor RT tolerance change will change the timing accuracy of RGB block. Also the boost converter switching frequency will be affected.

### **PCB Design Guidelines**

Printed circuit board layout is critical to low noise operation and good performance of the LP3950. Bypass capacitors should be close to the  $V_{DD}$  pins of the integrated circuit. Special attention must be given to the routing of the switching loops. Lengths of these loops should be minimized. It is essential to place the input capacitor, the output capacitor, the inductor and the schottky diode very close to the integrated circuit and use wide routings for those components. Sensitive components should be placed far from those components with high pulsating current. A ground plane is recommended.

The power switch loop (the switch is on) has the greatest affect on noise generation. The loop is formed by the input capacitor, the inductor, the SW pin, the GND\_BOOST pin and the ground plane, as shown by the dashed line in Figure 31. The other switching loop, the rectifier loop, is formed by the input capacitor, the inductor, the diode, the output capacitor and the ground plane, as shown by the dotted line. Arrange the components so that the switching current loops curl in the same direction (see arrows in Figure 31). See also Application Note AN 1149, Layout Guidelines for Switching Mode Power Supplies.

Product Folder Links: *LP*3950

Figure 31. The Current Loops

# **Typical Applications**

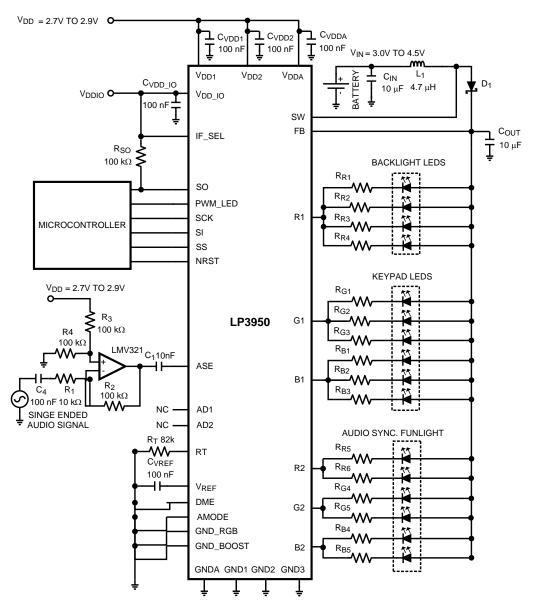

Figure 32. The LP3950 Set to the Default Mode

Figure 33. Typical Application of LP3950 When the SPI Interface Is Used

Here, a second order RC-filter is used on the ASE input to convert a PWM signal to an analog waveform.

Figure 34. Backlight and Keypad LEDs Controlled by the Pattern Generator Funlight LEDs Controlled by Audio Synchronization

There may be cases where the audio input signal going into the LP3950 is too weak for audio synchronization. This figure presents a single-supply inverting amplifier connected to the ASE input for audio signal amplification. The amplification is +20 dB, which is well enough for 20 mV<sub>p-p</sub> audio signal. Because the amplifier (LMV321) is operating in single supply voltage, a voltage divider using  $R_3$  and  $R_4$  is implemented to bias the amplifier so the input signal is within the input common-mode voltage range of the amplifier. The capacitor  $C_4$  is placed between the inverting input and resistor  $R_1$  to block the DC signal going into the audio signal source. The values of  $R_1$  and  $C_4$  affect the cutoff frequency,  $f_c = 1/(2^*Pi^*R_1^*C_4)$ , in this case it is around 160 Hz. As a result, the LMV321 output signal is centered around mid-supply, that is  $V_{DD}/2$ . The output can swing to both rails, maximizing the signal-to-noise ratio in a low voltage system

# Table 8. LP3950 Control Register Names and Default Values

| ADDR<br>(HEX) | SETUP                                         | D7                   | D6                          | D5                   | D4                        | D3                           | D2                    | D1                     | D0                     |