LP5812 SNVSCC9 - NOVEMBER 2023

# LP5812 4 × 3 Matrix RGB LED Driver with Autonomous Control

#### 1 Features

- Operating voltage range:

- V<sub>CC</sub> range: 2.7 V to 5.5 V

- Logic pins compatible with 1.8 V, 3.3 V, and 5 V

- Time-cross-multiplexing (TCM) topology:

- Drives up to 12 LEDs or 4 RGB LEDs

- $-\frac{1}{4}, \frac{1}{3}, \frac{1}{2}, 1$  multiplexing ratio

- Supports direct, TCM, and mix-drive modes

- 4 constant current sinks with high precision:

- 0.1-mA to 51-mA per current sink

- Device-to-device error: max ±5%

- Channel-to-channel error: max ±5%

- Ultra-low headroom voltage: 110 mV (typ.) at 25.5 mA; 210 mV (typ.) at 51 mA

- PWM phase shift configurable for each LED

- Ultra-low power consumption:

- Standby: I<sub>STB</sub> = 26 μA (typical) when CHIP\_EN = 0 (data retained)

- Active: I<sub>NOR</sub> = 0.4 mA (typical) when LED current = 25.5 mA

- Analog dimming (current gain control)

- Global 1-bit Maximum Current (MC): 25.5 mA or 51 mA

- Individual 8-bit Dot Current (DC) setting

- PWM dimming up to audible-noise-free 24 kHz

- Individual 8-bit PWM dimming resolution

- Linear or exponential dimming curves

- Autonomous animation engine control

- Individual LED dot open/short detection

- Integrated de-ghosting function

- 1-MHz (max.) I<sup>2</sup>C interface

- -40°C to 85°C operating temperature range

## 2 Applications

LED animation and indication for:

- Portable and wearable electronics earbud and charging case, E-cigarette, smart watch

- Gaming and home entertainment smart speaker, RGB mouse, VR headset, and controller

- Internet-of-Things (IOT) E-tag, video doorbell

- Networkings router, access point

- Industrial HMI EV charger, factory automation

## 3 Description

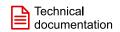

The LP5812 is a 4 × 3 matrix RGB LED driver with autonomous animation engine control. The device has ultra-low normal operation current with 0.4-mA (typical) when illuminate LEDs.

The time-cross-multiplexing (TCM) structure is adopted, which uses 4 output pins to control 12 LED dots individually. Both high-side scan switch and lowside current sink are contained in one output. The total solution size are minimized for space limited system.

The autonomous animation engine can significantly reduce the real-time loading of controller. Each LED can be configured through the related registers to realize vivid and fancy lighting effects. The device can generate 6-MHz clock signal and use it for synchronizing the lighting effects among multiple devices.

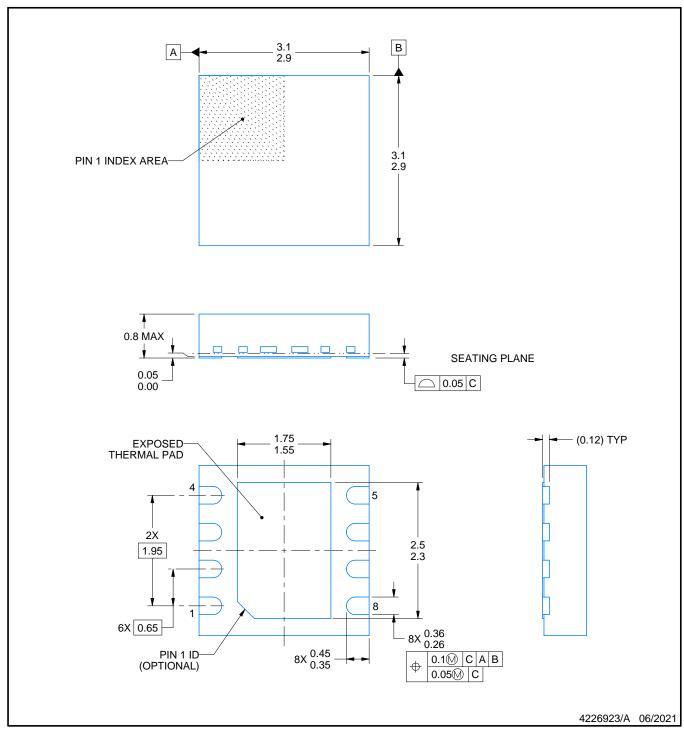

## **Package Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> BODY SIZE ( |                   |

|-------------|------------------------------------|-------------------|

| LP5812      | DSBGA (9)                          | 1.43 mm × 1.43 mm |

|             | WSON (8)                           | 3 mm × 3 mm       |

#### **Product Preview**

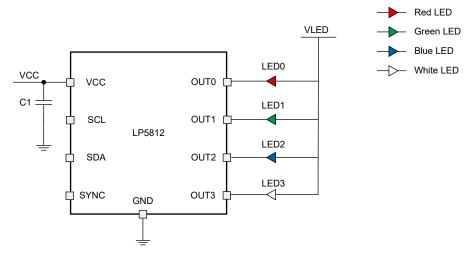

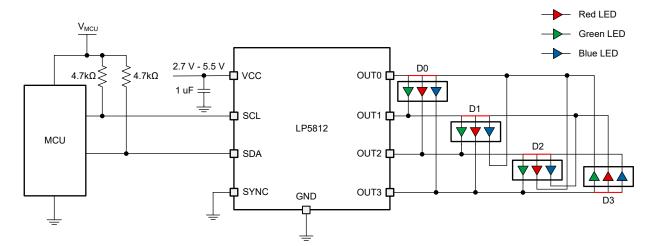

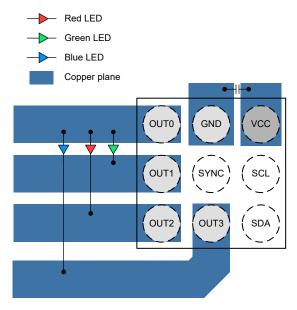

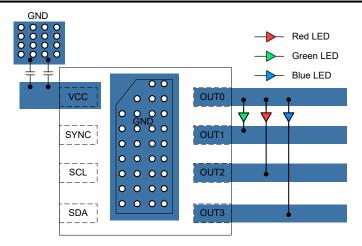

Simplified Schematic

# **Table of Contents**

| 1 Features1                           | 8.5 Programmin    |

|---------------------------------------|-------------------|

| 2 Applications1                       | 8.6 Register Ma   |

| 3 Description1                        | 9 Application and |

| 4 Device Comparison3                  | 9.1 Application I |

| 5 Pin Configuration and Functions4    | 9.2 Typical Appl  |

| 6 Specifications5                     | 9.3 Power Supp    |

| 6.1 Absolute Maximum Ratings5         | 9.4 Layout        |

| 6.2 ESD Ratings5                      | 10 Device and Do  |

| 6.3 Recommended Operating Conditions5 | 10.1 Documenta    |

| 6.4 Thermal Information5              | 10.2 Receiving I  |

| 6.5 Electrical Characteristics6       | 10.3 Support Re   |

| 6.6 Timing Requirements8              | 10.4 Trademark    |

| 7 Typical Characteristics10           | 10.5 Electrostati |

| 8 Detailed Description11              | 10.6 Glossary     |

| 8.1 Overview11                        | 11 Revision Histo |

| 8.2 Functional Block Diagram11        | 12 Mechanical, P  |

| 8.3 Feature Description11             | Information       |

| 8.4 Device Functional Modes           |                   |

|   | 8.5 Programming                                      | 23 |

|---|------------------------------------------------------|----|

|   | 8.6 Register Maps                                    | 24 |

| 9 | Application and Implementation                       |    |

|   | 9.1 Application Information                          |    |

|   | 9.2 Typical Application                              | 26 |

|   | 9.3 Power Supply Recommendations                     | 30 |

|   | 9.4 Layout                                           | 30 |

| 1 | 0 Device and Documentation Support                   |    |

|   | 10.1 Documentation Support                           |    |

|   | 10.2 Receiving Notification of Documentation Updates | 32 |

|   | 10.3 Support Resources                               | 32 |

|   | 10.4 Trademarks                                      | 32 |

|   | 10.5 Electrostatic Discharge Caution                 | 32 |

|   | 10.6 Glossary                                        | 32 |

| 1 | 1 Revision History                                   | 32 |

| 1 | 2 Mechanical, Packaging, and Orderable               |    |

|   | Information                                          | 33 |

|   |                                                      |    |

# **4 Device Comparison**

| PART   |           |             | DACKACE     | ACKACE MATERIAL | I <sup>2</sup> C Chip | Address | SOFTWARE   |

|--------|-----------|-------------|-------------|-----------------|-----------------------|---------|------------|

| NUMBER | Number    | Stage       | PACKAGE     | MATERIAL        | Bit 4                 | Bit 3   | COMPATIBLE |

|        |           |             |             | LP5813AYBHR     | 0                     | 0       |            |

|        |           |             | DODGA 40    | LP5813BYBHR     | 0                     | 1       |            |

|        |           |             | DSBGA-12    | LP5813CYBHR     | 1                     | 0       |            |

| LP5813 | 12        | Doost       |             | LP5813DYBHR     | 1                     | 1       |            |

| LP3013 | 12        | Boost       |             | LP5813ADRRR     | 0                     | 0       |            |

|        |           |             | WSON-12     | LP5813BDRRR     | 0                     | 1       |            |

|        |           |             | W50N-12     | LP5813CDRRR     | 1                     | 0       |            |

|        |           |             |             | LP5813DDRRR     | 1                     | 1       |            |

|        | LP5812 12 |             |             | LP5812AYBHR     | 0                     | 0       |            |

|        |           |             | DSBGA-9     | LP5812BYBHR     | 0                     | 1       |            |

|        |           | LP5812CYBHR | LP5812CYBHR | 1               | 0                     |         |            |

| LP5812 |           | Linear      |             | LP5812DYBHR     | 1                     | 1       |            |

| LF3012 | 12        |             | Linear      |                 | LP5812ADSDR           | 0       | 0          |

|        |           |             | WSON-8      | LP5812BDSDR     | 0                     | 1       |            |

|        |           |             |             | LP5812CDSDR     | 1                     | 0       |            |

|        |           |             |             | LP5812DDSDR     | 1                     | 1       | Yes        |

|        |           |             |             | LP5811AYBHR     | 0                     | 0       | — res      |

|        |           |             | DSBGA-12    | LP5811BYBHR     | 0                     | 1       |            |

|        |           |             | DSBGA-12    | LP5811CYBHR     | 1                     | 0       |            |

| LP5811 | 4         | Boost       |             | LP5811DYBHR     | 1                     | 1       |            |

| LF3011 | 4         | DOOSE       |             | LP5811ADRRR     | 0                     | 0       |            |

|        |           |             | WSON-12     | LP5811BDRRR     | 0                     | 1       |            |

|        |           |             | W30N-12     | LP5811CDRRR     | 1                     | 0       |            |

|        |           |             |             | LP5811DDRRR     | 1                     | 1       |            |

|        |           |             |             | LP5810AYBHR     | 0                     | 0       |            |

|        |           |             | DSBGA-9     | LP5810BYBHR     | 0                     | 1       |            |

|        |           |             | DSBGA-9     | LP5810CYBHR     | 1                     | 0       |            |

| LP5810 | LP5810 4  | Linear      |             | LP5810DYBHR     | 1                     | 1       |            |

| LF3010 | 4         | Lilleai     |             | LP5810ADSDR     | 0                     | 0       |            |

|        |           |             | WSON 9      | LP5810BDSDR     | 0                     | 1       |            |

|        |           |             | WSON-8      | LP5810CDSDR     | 1                     | 0       |            |

|        |           |             |             | LP5810DDSDR     | 1                     | 1       |            |

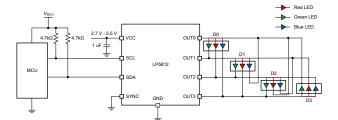

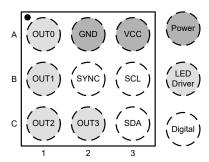

# **5 Pin Configuration and Functions**

Figure 5-1. LP5812 YBH Package 9-Pin DSBGA Top View

Figure 5-2. LP5812 DSD Package 8-Pin WSON Top View

|      |     |             | 1 114 |                                                                                                     | TYPE <sup>(1)</sup> |  | TVDE(1) | DESCRIPTION |

|------|-----|-------------|-------|-----------------------------------------------------------------------------------------------------|---------------------|--|---------|-------------|

| NAME | YBH | DSD         | IIFE, | DESCRIPTION                                                                                         |                     |  |         |             |

| OUT0 | A1  | 8           | 0     | Output 0 which contains current sink and scan FET. If not used, this pin must be floating           |                     |  |         |             |

| GND  | A2  | Thermal pad | G     | Ground. This pin must connect to the common ground plane.                                           |                     |  |         |             |

| VCC  | А3  | 1           | Р     | Power supply of the device.                                                                         |                     |  |         |             |

| OUT1 | B1  | 7           | 0     | Output 1 which contains current sink and scan FET. If not used, this pin must be floating           |                     |  |         |             |

| SYNC | B2  | 2           | I/O   | Clock synchronous among multiple devices. If not used, this pin can connect to ground t save power. |                     |  |         |             |

| SCL  | В3  | 3           | I     | I <sup>2</sup> C serial interface clock input.                                                      |                     |  |         |             |

I<sup>2</sup>C serial interface data input/output.

Output 2 which contains current sink and scan FET. If not used, this pin must be floating.

Output 3 which contains current sink and scan FET. If not used, this pin must be floating.

Table 5-1. Pin Functions

(1) G: Ground Pin; P: Power Pin; I: Input Pin; I/O: Input/Output Pin; O: Output Pin.

Submit Document Feedback

PIN

C1

C2

СЗ

6

5

4

0

0

I/O

Copyright © 2023 Texas Instruments Incorporated

to

OUT2

OUT3

SDA

## **6 Specifications**

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                            |                        | MIN  | MAX | UNIT |

|----------------------------|------------------------|------|-----|------|

|                            | VIN                    | -0.3 | 6   | V    |

|                            | SW spike at 10 ns      | -0.7 | 8   | V    |

| Voltage range at terminals | SW spike at 1 ns       | -0.7 | 9   | V    |

| at torring                 | OUT0, OUT1, OUT2, OUT3 | -0.3 | 6   | V    |

|                            | EN, SCL, SDA, SYNC     | -0.3 | 6   | V    |

| TJ                         | Junction temperature   | -40  | 150 | °C   |

| T <sub>stg</sub>           | Storage temperature    | -65  | 150 | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

## 6.2 ESD Ratings

|                                            |                                                                                 |                                                                                     | VALUE | UNIT |

|--------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001, all pins <sup>(1)</sup> | ±4000                                                                               | V     |      |

|                                            | Electrostatic discharge                                                         | Charged device model (CDM), per ANSI/ESDA/<br>JEDEC JS-002, all pins <sup>(2)</sup> | ±1000 | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                           |                                        | MIN | NOM | MAX | UNIT |

|---------------------------|----------------------------------------|-----|-----|-----|------|

| V <sub>IN</sub>           | Input voltage range                    | 0.5 |     | 5.5 | V    |

| C <sub>IN</sub>           | Effective input capacitance range      | 1   | 4.7 |     | μF   |

| OUT0, OUT1, OUT2,<br>OUT3 | Voltage on OUT0, OUT1, OUT2, OUT3 pins | 0   |     | 5.5 | V    |

| EN, SCL, SDA, SYNC        | Voltage on EN, SCL, SDA, SYNC pins     | 0   |     | 5.5 | V    |

| T <sub>A</sub>            | Ambient temperature                    | -40 |     | 85  | °C   |

| T <sub>J</sub>            | Operating junction temperature         | -40 |     | 125 | °C   |

## 6.4 Thermal Information

|                       |                                              | LP5         |            |      |

|-----------------------|----------------------------------------------|-------------|------------|------|

|                       | THERMAL METRIC(1)                            | YBH (DSBGA) | DRR (WSON) | UNIT |

|                       |                                              | 9 PINS      | 8 PINS     |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 113.1       | 50.8       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 0.6         | 51.1       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 33.9        | 22.9       | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.2         | 1.1        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 33.8        | 22.8       | °C/W |

Copyright © 2023 Texas Instruments Incorporated

|                               |                                              | LP5812/0    |            |      |  |

|-------------------------------|----------------------------------------------|-------------|------------|------|--|

| THERMAL METRIC <sup>(1)</sup> |                                              | YBH (DSBGA) | DRR (WSON) | UNIT |  |

|                               |                                              | 9 PINS      | 8 PINS     |      |  |

| R <sub>θJC(bot)</sub>         | Junction-to-case (bottom) thermal resistance | n/a         | 8.5        | °C/W |  |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 6.5 Electrical Characteristics

Unless specified otherwise, typical characteristics apply over the full ambient temperature range ( $-40^{\circ}\text{C} < \text{TA} < +85^{\circ}\text{C}$ ),  $V_{\text{IN}} = 3.6 \text{ V}$ ,  $V_{\text{CC}} = 5 \text{ V}$ ,  $C_{\text{IN}} = 1 \text{ }\mu\text{F}$ ,  $C_{\text{OUT}} = 1 \text{ }\mu\text{F}$ .

|                        | PARAMETER                                               | TEST CONDITIONS                                                                                                                                                                               | MIN | TYP  | MAX      | UNIT |

|------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|----------|------|

| Power Sup              | oly                                                     |                                                                                                                                                                                               |     |      | <u>'</u> |      |

| V <sub>IN</sub>        | Input voltage range                                     |                                                                                                                                                                                               | 0.5 |      | 5.5      | V    |

|                        | Hadana kan hada da     | V <sub>IN</sub> rising                                                                                                                                                                        |     | 1.7  | 1.8      | V    |

| $V_{IN\_UVLO}$         | Under-voltage lockout threshold                         | V <sub>IN</sub> falling                                                                                                                                                                       |     | 0.4  | 0.5      | V    |

| I <sub>SD</sub>        | Shutdown current into VIN and SW pin (LP5811/3)         | IC disabled (EN = Low), V <sub>IN</sub> = 3.6 V, T <sub>A</sub> = 25°C                                                                                                                        |     | 0.1  | 0.35     | μA   |

|                        | Standby current into VCC pin (LP5810/2)                 | CHIP_EN = 0 (bit), V <sub>CC</sub> = 3.6 V                                                                                                                                                    |     | 25   | 28       | μA   |

| I <sub>STB</sub>       | Standby current into VIN and SW pin (LP5811/3)          | CHIP_EN = 0 (bit), Boost enabled (EN = High), V <sub>IN</sub> = 3.6 V, VOUT set to 3 V, Pass-through mode                                                                                     |     | 26   | 29       | μA   |

|                        | Standby current into VOUT pin (LP5811/3)                | CHIP_EN = 0 (bit), Boost disabled (EN = Low), VIN no supply, VOUT force to 5 V                                                                                                                |     | 25   | 28       | μΑ   |

|                        | Normal operation current into VIN and SW pin (LP5811/3) | CHIP_EN = 1 (bit), Boost enabled (EN = High), $V_{IN}$ = 3.6 V, VOUT set to 3 V, Pass-through mode, $I_{OUT0}$ = $I_{OUT1}$ = $I_{OUT2}$ = $I_{OUT3}$ = 25.5 mA (MC = 0, DC = 255, PWM = 255) |     | 0.45 | 0.65     | mA   |

| I <sub>NOR</sub>       | Normal operation current into VOUT pin (LP5811/3)       | CHIP_EN = 1 (bit), Boost disabled (EN = LOW), VOUT force to 3.6 V, I <sub>OUT0</sub> = I <sub>OUT1</sub> = I <sub>OUT2</sub> = I <sub>OUT3</sub> = 25.5 mA (MC = 0, DC = 255, PWM = 255)      |     | 0.4  | 0.6      | mA   |

|                        | Normal operation current into VCC pin (LP5810/2)        | CHIP_EN = 1 (bit), VCC = 5V, I <sub>OUT0</sub><br>= I <sub>OUT1</sub> = I <sub>OUT2</sub> = I <sub>OUT3</sub> = 25.5 mA (MC<br>= 0, DC = 255, PWM = 255)                                      |     | 0.4  | 0.6      | mA   |

| Boost Outp             | ut(LP5811/3)                                            |                                                                                                                                                                                               |     |      | '        |      |

| V <sub>OUT</sub>       | Output voltage setting range                            |                                                                                                                                                                                               | 3   |      | 5.5      | V    |

| V <sub>OVP</sub>       | Output over-voltage protection threshold                | V <sub>OUT</sub> rising                                                                                                                                                                       | 5.5 | 5.7  | 5.9      | V    |

| V <sub>OVP_HYS</sub>   | Over-voltage protection hysteresis                      |                                                                                                                                                                                               |     | 0.2  |          | V    |

| t <sub>SS</sub>        | Soft startup time                                       | From active EN to VOUT regulation. $V_{IN}$ = 1.8 V, $C_{OUT}$ = 22 $\mu$ F, $I_{VOUT}$ = 0 mA                                                                                                |     | 450  |          | μs   |

| <b>Boost Pow</b>       | er Switch(LP5811/3)                                     |                                                                                                                                                                                               |     |      |          |      |

| Rook                   | High-side MOSFET on resistance                          | V <sub>VOUT</sub> = 5 V                                                                                                                                                                       |     | 140  |          | mΩ   |

| R <sub>DS(on)</sub>    | Low-side MOSFET on resistance                           | V <sub>VOUT</sub> = 5 V                                                                                                                                                                       |     | 60   |          | mΩ   |

| f                      | Switching frequency                                     | V <sub>IN</sub> = 3.6 V, V <sub>OUT</sub> set to 5.0 V, PWM mode                                                                                                                              |     | 1    |          | MHz  |

| t <sub>SW</sub>        | Switching frequency                                     | V <sub>IN</sub> = 1.0 V, V <sub>OUT</sub> set to 5.0 V, PFM mode                                                                                                                              |     | 0.5  |          | MHz  |

| I <sub>LIM_SW</sub>    | Valley current limit                                    | V <sub>IN</sub> = 3.6 V, V <sub>OUT</sub> set to 5.0 V                                                                                                                                        |     | 1.6  |          | Α    |

| I <sub>PRECHG</sub>    | Pre-charge current                                      | V <sub>IN</sub> = 3.6 V                                                                                                                                                                       |     | 350  |          | mA   |

| LED Driver             | Output                                                  |                                                                                                                                                                                               |     |      | •        |      |

| R <sub>DS(on)_SW</sub> | Scan line switch MOSFET on resistance                   | V <sub>VOUT</sub> = 3 V                                                                                                                                                                       |     | 1    | 1.4      | Ω    |

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Unless specified otherwise, typical characteristics apply over the full ambient temperature range ( $-40^{\circ}\text{C} < \text{TA} < +85^{\circ}\text{C}$ ),  $V_{\text{IN}} = 3.6 \text{ V}$ ,  $V_{\text{CC}} = 5 \text{ V}$ ,  $C_{\text{IN}} = 1 \text{ }\mu\text{F}$ ,  $C_{\text{OUT}} = 1 \text{ }\mu\text{F}$ .

|                        | $_{\text{C}}$ = 5 V, $_{\text{CIN}}$ = 1 $_{\text{HF}}$ , $_{\text{COUT}}$ = 1 $_{\text{HF}}$ .                       | TEST CONDITIONS                                                                                   | MIN        | TYP  | MAX  | UNIT |

|------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------|------|------|------|

| R <sub>DS(on)_SW</sub> | Scan line switch MOSFET on resistance                                                                                 | V <sub>VOUT</sub> = 5 V                                                                           |            | 0.7  | 1.1  | Ω    |

| I <sub>CS</sub>        | Constant current sink output range                                                                                    | V <sub>IN</sub> = 3.6 V, V <sub>OUT</sub> set to 5 V, MC = 0,<br>manual_pwm_x = FFh (100% ON)     | 0.1        |      | 25.5 | mA   |

| ics                    | Constant current sink output range                                                                                    | V <sub>IN</sub> = 3.6 V, V <sub>OUT</sub> set to 5 V, MC = 1,<br>manual_pwm_x = FFh (100% ON)     | 0.2        |      | 1.1  | mA   |

| I <sub>CS_LKG</sub>    | Constant current sink leakage current                                                                                 | V <sub>IN</sub> = 3.6 V, OUTx = 1 V, manual_pwm_x = 0 (0%)                                        |            | 0.1  | 1    | μΑ   |

| lena non               | Device to device current error,                                                                                       | All LEDs turn ON. Current set to 0.1 mA (max_current = 0, manual_dc_x = 01h, manual_pwm_x = FFh)  | -5         |      | 5    | %    |

| I <sub>ERR_D2D</sub>   | $I_{ERR\_D2D} = (I_{AVE} - I_{SET})/I_{SET} \times 100\%$                                                             | All LEDs turn ON. Current set to 0.2 mA (max_current = 1, manual_dc_x = 01h, manual_pwm_x = FFh)  | -3         |      | 3    | %    |

| I <sub>ERR_D2D</sub>   |                                                                                                                       | All LEDs turn ON. Current set to 1 mA (max_current = 0, manual_dc_x = 0Ah, manual_pwm_x = FFh)    | <b>-</b> 5 |      | 5    | %    |

|                        | Device to device current error,                                                                                       | All LEDs turn ON. Current set to 1 mA (max_current = 1, manual_dc_x = 05h, manual_pwm_x = FFh)    | -3         |      | 3    | %    |

|                        | I <sub>ERR_D2D</sub> = (I <sub>AVE</sub> -I <sub>SET</sub> )/I <sub>SET</sub> ×100%                                   | All LEDs turn ON. Current set to 25.5 mA (max_current = 0, manual_dc_x = FFh, manual_pwm_x = FFh) | <b>–</b> 5 |      | 5    | %    |

|                        |                                                                                                                       | All LEDs turn ON. Current set to 51 mA (max_current = 1, manual_dc_x = FFh, manual_pwm_x = FFh)   | -3         |      | 3    | %    |

|                        | Channel to Channel current error I <sub>ERR_C2C</sub> = (I <sub>OUTX</sub> -I <sub>AVE</sub> )/I <sub>AVE</sub> ×100% | All LEDs turn ON. Current set to 0.1 mA (max_current = 0, manual_dc_x = 01h, manual_pwm_x = FFh)  | <b>–</b> 5 |      | 5    | %    |

| I <sub>ERR_C2C</sub>   |                                                                                                                       | All LEDs turn ON. Current set to 0.2 mA (max_current = 1, manual_dc_x = 01h, manual_pwm_x = FFh)  | -3         |      | 3    | %    |

|                        |                                                                                                                       | All LEDs turn ON. Current set to 1 mA (max_current = 0, manual_dc_x = 0Ah, manual_pwm_x = FFh)    | <b>–</b> 5 |      | 5    | %    |

|                        | Channel to Channel current error                                                                                      | All LEDs turn ON. Current set to 1 mA (max_current = 1, manual_dc_x = 05h, manual_pwm_x = FFh)    | -3         |      | 3    | %    |

| I <sub>ERR_C2C</sub>   | $I_{\text{ERR\_C2C}} = (I_{\text{OUTX}} - I_{\text{AVE}}) / I_{\text{AVE}} \times 100\%$                              | All LEDs turn ON. Current set to 25.5 mA (max_current = 0, manual_dc_x = FFh, manual_pwm_x = FFh) | -5         |      | 5    | %    |

|                        |                                                                                                                       | All LEDs turn ON. Current set to 51 mA (max_current = 1, manual_dc_x = FFh, manual_pwm_x = FFh)   | -3         |      | 3    | %    |

| V                      | LED driver cutout became welters                                                                                      | All LEDs turn ON. Current set to 25.5 mA (max_current = 0, manual_dc_x = FFh)                     |            | 0.11 | 0.15 | V    |

| V <sub>HR</sub>        | LED driver output hearroom voltage                                                                                    | All LEDs turn ON. Current set to 51 mA (max_current = 1, manual_dc_x = FFh)                       |            | 0.21 | 0.28 | V    |

| f <sub>LED PWM</sub>   | LED PWM frequency                                                                                                     | pwm_fre = 0                                                                                       |            | 24   |      | kHz  |

| -FED_LAMM              | , ,                                                                                                                   | pwm_fre = 1                                                                                       |            | 12   |      | kHz  |

| f <sub>OSC</sub>       | Internal oscillator frequency                                                                                         | vsync_out_en = 1                                                                                  |            | 6    |      | MHz  |

| Logic Interl           | I                                                                                                                     | 1                                                                                                 |            |      | Т    |      |

| V <sub>EN_H</sub>      | EN logic high                                                                                                         | V <sub>IN</sub> > 1.8 V                                                                           | 1.2        |      |      | V    |

| V <sub>EN_L</sub>      | EN logic low                                                                                                          | V <sub>IN</sub> > 1.8 V                                                                           |            |      | 0.35 | V    |

Unless specified otherwise, typical characteristics apply over the full ambient temperature range ( $-40^{\circ}$ C < TA <  $+85^{\circ}$ C ),  $V_{IN} = 3.6$  V,  $V_{CC} = 5$  V,  $C_{IN} = 1$   $\mu$ F,  $C_{OLIT} = 1$   $\mu$ F.

|                       | PARAMETER                                           | TEST CONDITIONS                                             | MIN                     | TYP            | MAX            | UNIT |

|-----------------------|-----------------------------------------------------|-------------------------------------------------------------|-------------------------|----------------|----------------|------|

| V <sub>IH_LOGIC</sub> | High level input voltage of SDA, SCL, SYNC          |                                                             | 1.4                     |                |                | V    |

| V <sub>IL_LOGIC</sub> | Low level input voltage of SDA, SCL, SYNC           |                                                             |                         |                | 0.4            | V    |

| V <sub>OH_LOGIC</sub> | High level output voltage of SYNC                   |                                                             | V <sub>VOUT</sub> - 0.2 |                |                | V    |

| V <sub>OL_LOGIC</sub> | Low level output voltage of SDA, SYNC               |                                                             |                         |                | 0.4            | V    |

| Protection            |                                                     |                                                             |                         |                |                |      |

| T <sub>SD</sub>       | Thermal shutdown threshold for LED driver part      | T <sub>J</sub> rising                                       |                         | 150            |                | °C   |

| T <sub>SD</sub>       | Thermal shutdown threshold for Boost converter part | $T_J$ rising                                                |                         | 155            |                | °C   |

| T <sub>SD_HYS</sub>   | Thermal shutdown hysteresis                         | T <sub>J</sub> falling below T <sub>SD</sub>                |                         | 15             |                | °C   |

| V <sub>LOD_TH</sub>   | LED open detection threshold                        | Current set to 25.5 mA (max_current = 0, manual_dc_x = FFh) | 70                      | 90             | 110            | mV   |

| V <sub>LOD_TH</sub>   | LED open detection threshold                        | Current set to 51 mA (max_current = 1, manual_dc_x = FFh)   | 150                     | 180            | 220            | mV   |

|                       |                                                     | lsd_th = 00h                                                | 0.32 ×<br>VOUT          | 0.35 ×<br>VOUT | 0.38 ×<br>VOUT | V    |

| <b>.</b>              | LED short detection threshold                       | lsd_th = 01h                                                | 0.42 ×<br>VOUT          | 0.45 ×<br>VOUT | 0.48 ×<br>VOUT | V    |

| V <sub>LSD_TH</sub>   | LED SHOR detection theshold                         | lsd_th = 10h                                                | 0.52 ×<br>VOUT          | 0.55 ×<br>VOUT | 0.58 ×<br>VOUT | V    |

|                       |                                                     | Isd_th = 11h                                                | 0.62 ×<br>VOUT          | 0.65 ×<br>VOUT | 0.68 ×<br>VOUT | V    |

# **6.6 Timing Requirements**

Unless specified otherwise, typical characteristics apply over the full ambient temperature range ( $-40^{\circ}\text{C} < \text{TA} < +85^{\circ}\text{C}$ ),  $V_{\text{IN}} = 3.6 \text{ V}$ ,  $V_{\text{CC}} = 5 \text{ V}$ ,  $C_{\text{IN}} = 1 \text{ }\mu\text{F}$ ,  $C_{\text{OUT}} = 1 \text{ }\mu\text{F}$ .

|                     | I <sup>2</sup> C Timing Requirements                                                         | MIN | NOM MAX | UNIT |

|---------------------|----------------------------------------------------------------------------------------------|-----|---------|------|

| Standard            | -mode                                                                                        |     |         |      |

| f <sub>SCL</sub>    | SCL clock frequency                                                                          | 0   | 100     | kHz  |

| t <sub>HD_STA</sub> | Hold time (repeated) START condition. After this period, the first clock pulse is generated. | 4   |         | μs   |

| t <sub>LOW</sub>    | LOW period of the SCL clock                                                                  | 4.7 |         | μs   |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                                                                 | 4   |         | μs   |

| t <sub>SU_STA</sub> | Set-up time for a repeated START condition                                                   | 4.7 |         | μs   |

| t <sub>HD_DAT</sub> | Data hold time                                                                               | 0   |         | μs   |

| t <sub>SU_DAT</sub> | Data set-up time                                                                             | 250 |         | ns   |

| t <sub>r</sub>      | Rise time of both SDA and SCL signals                                                        |     | 1000    | ns   |

| t <sub>f</sub>      | Fall time of both SDA and SCL signals                                                        |     | 300     | ns   |

| t <sub>SU_STO</sub> | Set-up time for STOP condition                                                               | 4   |         | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition                                             | 4.7 |         | μs   |

| C <sub>b</sub>      | Capacitive load for each bus line                                                            |     | 400     | pF   |

| Fast-mod            | le                                                                                           |     |         |      |

| f <sub>SCL</sub>    | SCL clock frequency                                                                          | 0   | 400     | kHz  |

| t <sub>HD_STA</sub> | Hold time (repeated) START condition. After this period, the first clock pulse is generated. | 0.6 |         | μs   |

| t <sub>LOW</sub>    | LOW period of the SCL clock                                                                  | 1.3 |         | μs   |

Unless specified otherwise, typical characteristics apply over the full ambient temperature range ( $-40^{\circ}$ C < TA <  $+85^{\circ}$ C ),  $V_{IN}$  = 3.6 V,  $V_{CC}$  = 5 V,  $C_{IN}$  = 1  $\mu$ F,  $C_{OUT}$  = 1  $\mu$ F.

|                     | I <sup>2</sup> C Timing Requirements                                                         | MIN  | NOM MAX | UNIT |

|---------------------|----------------------------------------------------------------------------------------------|------|---------|------|

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                                                                 | 0.6  |         | μs   |

| t <sub>SU_STA</sub> | Set-up time for a repeated START condition                                                   | 0.6  |         | μs   |

| t <sub>HD_DAT</sub> | Data hold time                                                                               | 0    |         | μs   |

| t <sub>SU_DAT</sub> | Data set-up time                                                                             | 100  |         | ns   |

| t <sub>r</sub>      | Rise time of both SDA and SCL signals                                                        |      | 300     | ns   |

| t <sub>f</sub>      | Fall time of both SDA and SCL signals                                                        |      | 300     | ns   |

| t <sub>su_sто</sub> | Set-up time for STOP condition                                                               | 0.6  |         | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition                                             | 1.3  |         | μs   |

| C <sub>b</sub>      | Capacitive load for each bus line                                                            |      | 400     | pF   |

| Fast-mod            | le Plus                                                                                      |      |         |      |

| f <sub>SCL</sub>    | SCL clock frequency                                                                          | 0    | 1000    | kHz  |

| t <sub>HD_STA</sub> | Hold time (repeated) START condition. After this period, the first clock pulse is generated. | 0.26 |         | μs   |

| t <sub>LOW</sub>    | LOW period of the SCL clock                                                                  | 0.5  |         | μs   |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                                                                 | 0.26 |         | μs   |

| t <sub>SU_STA</sub> | Set-up time for a repeated START condition                                                   | 0.26 |         | μs   |

| t <sub>HD_DAT</sub> | Data hold time                                                                               | 0    |         | μs   |

| t <sub>SU_DAT</sub> | Data set-up time                                                                             | 50   |         | ns   |

| t <sub>r</sub>      | Rise time of both SDA and SCL signals                                                        |      | 120     | ns   |

| t <sub>f</sub>      | Fall time of both SDA and SCL signals                                                        |      | 120     | ns   |

| t <sub>su_sto</sub> | Set-up time for STOP condition                                                               | 0.26 |         | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition                                             | 0.5  |         | μs   |

| C <sub>b</sub>      | Capacitive load for each bus line                                                            |      | 550     | pF   |

| Misc. Tim           | ing Requirements                                                                             |      |         |      |

| f <sub>CLK_EX</sub> | VSYNC input clock frequency                                                                  |      | 6       | MHz  |

|                     |                                                                                              |      |         |      |

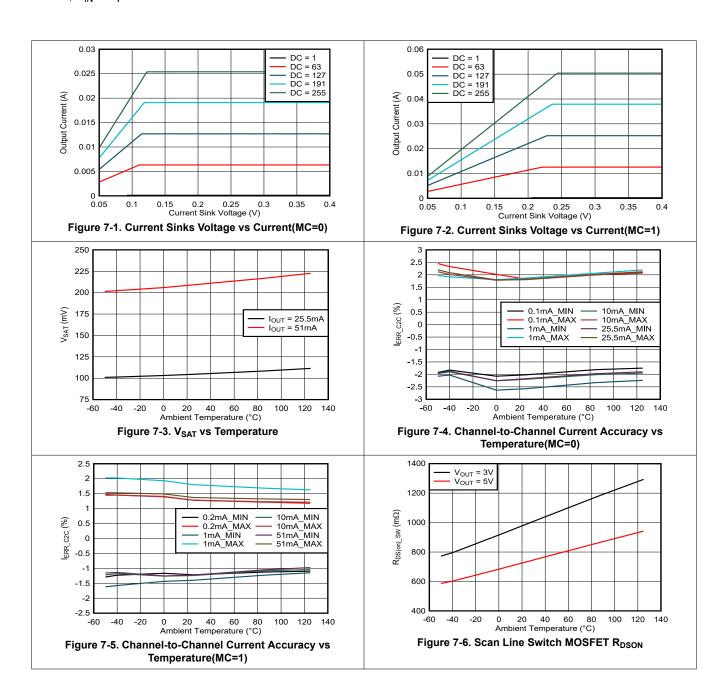

## 7 Typical Characteristics

Unless specified otherwise, typical characteristics apply over the full ambient temperature range ( $-40^{\circ}\text{C} < T_A < +85^{\circ}\text{C}$ ),  $V_{IN} = 3.6 \text{ V}$ ,  $C_{IN} = 1 \text{ }\mu\text{F}$

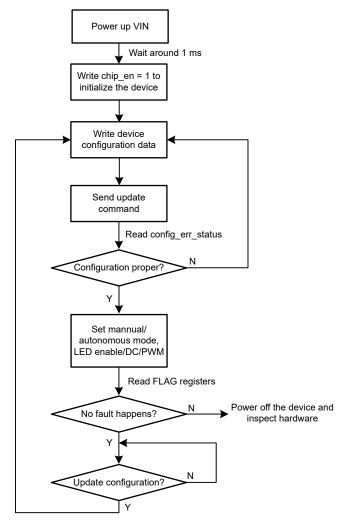

## **8 Detailed Description**

#### 8.1 Overview

The LP5812 is a 4 × 3 matrix RGB LED driver with autonomous animation engine control. Time-cross-multiplexing (TCM) scheme can support up to 4×3 matrix for 12 LEDs or 4 RGB LEDs, by ½ multiplexing ratio of the scan switches.

The LP5812 has ultra-low operation current at active mode, consuming about 0.4 mA when LED maximum current setting is 25.5 mA. If all LEDs are turned off, the device will enter standby state to reduce power consumption with data retained. When 'chip\_enable' bit setting is 0, initial state is entered with minimum power consumption to save power.

The LP5812 supports both analog dimming and PWM dimming. In analog dimming, the output current of each LED can be adjusted with 256 steps. In PWM dimming, the integrated 8-bit configurable PWM generator enables smooth brightness dimming control. Optional exponential PWM dimming can be activated for individual LED to achieve a human-eye-friendly visual performance.

The LP5812 integrates autonomous animation engine, with no need for brightness control commands from controller. Each LED has an individual animation engine which can be configured through the related registers. The device can generate a 6 MHz clock signal, which synchronizes the lighting effects among multiple devices.

The LP5812 has 4 different material versions with different I<sup>2</sup>C chip address. Up to 4 LP581x devices can be connected to the same I<sup>2</sup>C bus and controlled individually. The LP5812 materials and corresponding chip addresses are shown in Section 4.

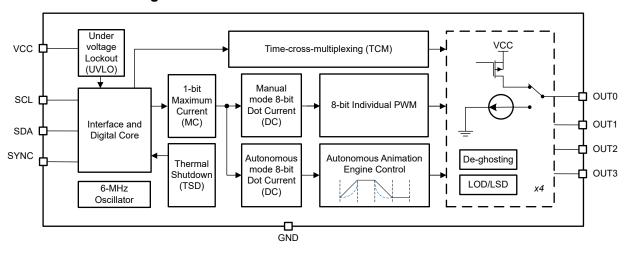

## 8.2 Functional Block Diagram

Figure 8-1. Functional Block Diagram

## 8.3 Feature Description

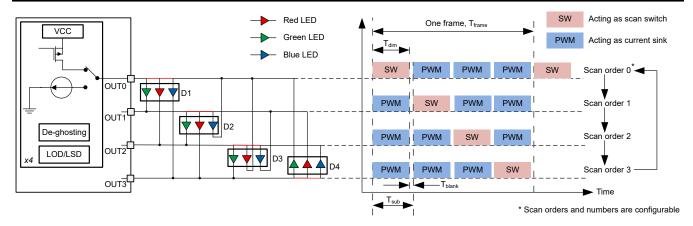

## 8.3.1 Time-cross-multiplexing (TCM) scheme

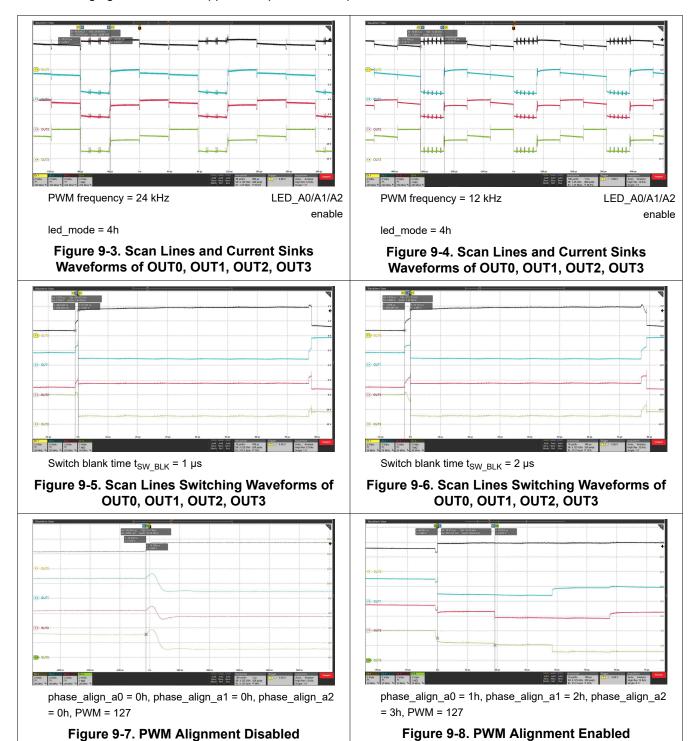

The LP5812 integrates 4 high-side PMOS scan switches and 4 constant current sinks. Each OUTx (x = 0, 1, 2, 3) has 1 PMOS scan switch and 1 constant current sink. The source of PMOS switches are connected to VCC. During normal operation at default setting, the switches turn on sequentially from OUT0 to OUT3. At the same time, only one OUT is selected working as switch, the other 3 OUTs act as constant current sink. Thus a  $4\times3$  matrix is formed with  $\frac{1}{4}$  multiplexing ratio. The scanning order of OUTs can be configured in 'Dev\_config\_2' register

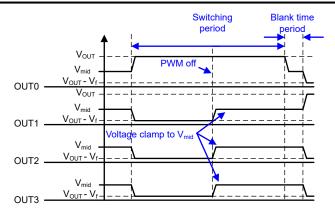

Figure 8-2. Time-cross-multiplexing (TCM) Scheme

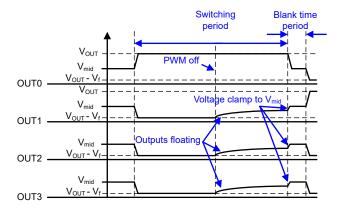

Figure 8-2 shows the simplified TCM scheme timing diagram of the four outputs. A complete display frame includes 4 sub-periods. Each sub-period contains dimming period and blank time period. In switching period, 1 output is selected as switch and the other 3 OUTs are selected as current sinks. Blank time is applied between two adjacent switching periods for ghosting elimination.

One sub-period cycle time T<sub>sub</sub> is calculated as Equation 1:

$$T_{sub} = T_{dim} + T_{blank} \tag{1}$$

- T<sub>dim</sub> is the scan switch on-time for one switching cycle, which equals to one PWM cycle 42 μs (PWM frequency set as 24 kHz) or 84 μs (PWM frequency set as 12 kHz).

- T<sub>blank</sub> is blank time is applied between two adjacent dimming periods, which is from 1 μs to 2 μs selected by 'Blank\_Time' bits in Dev\_Config11 Register.

One complete frame time T<sub>frame</sub> is calculated as Equation 2:

$$T_{frame} = T_{Sub} \times Scan$$

# (2)

Scan # is the total scan switches count.

The LP5812 can be configured to direct-drive mode, TCM-drive mode and mix-drive mode by the 'led\_mode' bits in 'Dev\_Config\_1' register. The mix-drive mode contains both direct drive mode and TCM-drive mode for different outputs. With this method, the LP5812 can provide the maximum flexibility for LED configurations of LED average current, LED count, and PCB layouts.

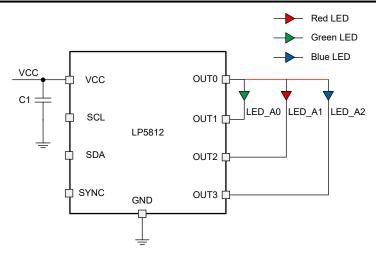

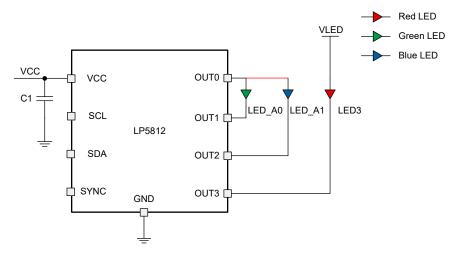

#### 8.3.1.1 Direct drive mode

The direct drive mode can drive up to 4 LEDs (or 1 RGBW / RGBA / RGBY LED) by the internal constant current sinks directly, when the 'led\_mode' bit is 0h. The typical application circuit is illustrated in Figure 8-3. Each current sink can support up to 51 mA maximum current. In the register map, LED\_x (x = 0, 1, 2, 3) are used as the name of each outputs for the related settings.

Figure 8-3. Direct Drive Mode (led mode = 0h)

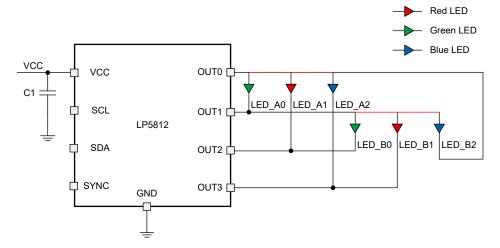

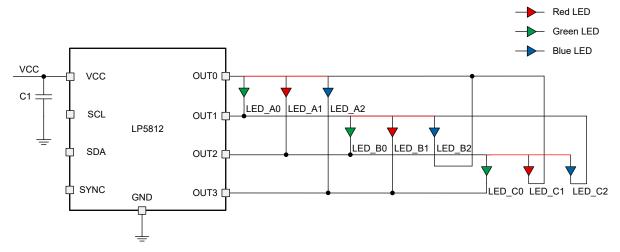

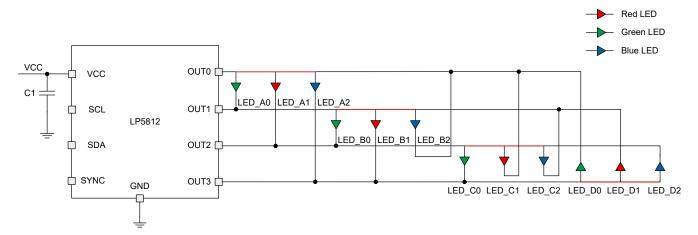

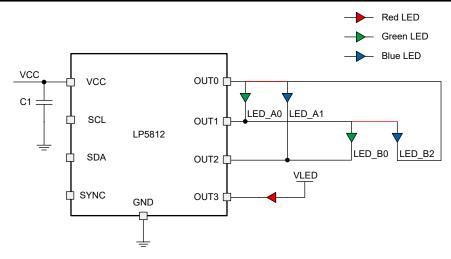

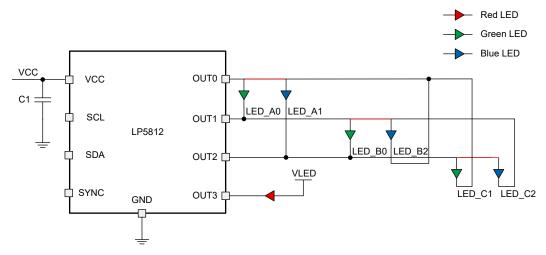

#### 8.3.1.2 TCM drive mode

The TCM drive mode is used to drive up to 12 LEDs (or 4 RGB LEDs) with TCM scheme, which is configured by setting led\_mode = 1h/2h/3h/4h for 1/2/3/4 scans. After setting the scan count, 'scan\_order\_x' (x = 1, 2, 3, 4) bits need to be written for the scan orders of each output. The default order is from OUT0 to OUT3 in 4 scans mode.

The TCM drive mode can drive 1 to 12 LEDs with 1 to 4 scans or  $\frac{1}{4}$  to 1 multiplexing ratio. The names LED\_xy (x = A, B, C, D; y = 0, 1, 2) are used in the register map for the corresponding LED, which is connected to OUTx (x = 0, 1, 2, 3). The detail naming rule is showed in Table 8-1.

Table 8-1. LED Names in Register Maps for TCM Drive Mode

| LED name in registers |          |        | LED Cathode |        |        |  |  |  |  |

|-----------------------|----------|--------|-------------|--------|--------|--|--|--|--|

|                       |          | OUT0   | OUT1        | OUT2   | OUT3   |  |  |  |  |

| LED Anode             | OUT0 (A) | -      | LED_A0      | LED_A1 | LED_A2 |  |  |  |  |

|                       | OUT1 (B) | LED_B2 | -           | LED_B0 | LED_B1 |  |  |  |  |

|                       | OUT2 (C) | LED_C1 | LED_C2      | -      | LED_C0 |  |  |  |  |

|                       | OUT3 (D) | LED_D0 | LED_D1      | LED_D2 | -      |  |  |  |  |

The typical application circuits are demonstrated as Figure 8-4 (1 scan), Figure 8-5 (2 scans), Figure 8-6 (3 scans) and Figure 8-7 (4 scans).

## Note

To avoid unexpected emitting, in RGB LEDs applications, Red LEDs are recommended to be placed in LED\_x1 (x = A, B, C, D) positions.

Figure 8-4. TCM Drive Mode, 1 Scan, (led\_mode = 1h, scan\_order\_0 = 0h)

Figure 8-5. TCM Drive Mode, 2 Scans (led\_mode = 2h, scan\_order\_0 = 0h, scan\_order\_1 = 1h)

Figure 8-6. TCM Drive Mode, 3 Scans (led\_mode = 3h, scan\_order\_0 = 0h, scan\_order\_1 = 1h, scan\_order\_2 = 2h)

Submit Document Feedback

Figure 8-7. TCM Drive Mode, 4 Scans (led\_mode = 4h scan\_order\_0 = 0h, scan\_order\_1 = 1h, scan\_order\_2 = 2h, scan\_order\_3 = 3h)

#### 8.3.1.3 Mix drive mode

The mix drive mode can drive LEDs separately by direct-drive and TCM-drive in the same time. The mix drive mode is configured by setting led\_mode = 5h/6h/7h for 1/2/3 scans. After setting the scan count, scan\_order\_x (x = 1, 2, 3, 4) needs to be written for the scan orders. Then the direct drive LEDs need to be configured by mix\_sel\_led in Dev\_Config\_1 register. To control the LEDs, LED\_x (x = 0, 1, 2, 3) in the register map is for the direct drive LEDs, while LED\_xy (x = A, B, C, D; y = 0, 1, 2) is for the TCM drive LEDs.

The typical application diagrams are illustrated as Figure 8-8 (1 scan), Figure 8-9 (2 scans) and Figure 8-10 (3 scans).

Figure 8-8. Mix drive, 1 scan (led\_mode = 5h, scan\_order\_0 = 0h, mix\_sel\_led = 8h)

Figure 8-9. Mix drive mode, 2 scans (led\_mode = 6h, scan\_order\_0 = 0h, scan\_order\_1 = 1h, mix\_sel\_led = 8h)

Figure 8-10. Mix drive mode, 3 scans (led\_mode = 7h, scan\_order\_0 = 0h, scan\_order\_1 = 1h, scan\_order\_2 = 2h, mix\_sel\_led = 8h)

#### 8.3.1.4 Ghosting elimination

The LP5812 integrates ghosting elimination circuits to avoid both upside and downside ghosting phenomenon. The ghosting elimination can be disabled by setting clamp\_dis = 1h, which is default as 0 and enabling the function.

Voltage on the outputs is clamped during PWM off time in the rest of switching period, or during blank time period, which is set in 'clamp\_sel' bit in Dev\_Config12 register. Figure 8-11 and Figure 8-12 show the effect of different clamp selection.

A middle voltage  $V_{mid}$  between  $V_{OUT}$  and  $V_{OUT}$  -  $V_f$  is used to clamp the OUTx (x = 0, 1, 2, 3), where  $V_f$  is the forward voltage of LED. This scheme can achieve both pre-discharge for scan switch FET and pre-charge for current sinks, which eliminate up-side and down-side ghosting issues in time-multiplexing topology. Since the clamp voltage for scan switch FET and current sinks is the same value, the reverse voltage on LED during deghosting is avoided. There are 4 options for  $V_{mid}$  which is selected in 'vmid\_sel' bits in Dev\_Config12 register, which can be used for different forward voltage range of different type LEDs.

Figure 8-11. Ghosting elimination waveform when clamp\_sel = 1

Figure 8-12. Ghosting elimination waveform when clamp\_sel = 0

## 8.3.2 Analog Dimming

The current gain of each LED can be controlled by 2 methods to achieve analog dimming in the LP5812.

- Global 1-bit Maximum Current (MC) control for all LEDs without external resistor

- Individual 8-bit Dot Current (DC) control for each LED

The maximum output current  $I_{OUT\_max}$  of each current sink can be programmed by the 1-bit max\_current. The default value of max\_current is 0h, which means the LED maximum current is set to 25.5 mA in default.

Table 8-2. Maximum Current (MC) bit setting

| 1 bit Maximun | l (mΔ)      |                           |  |

|---------------|-------------|---------------------------|--|

| Binary        | Decimal     | I <sub>OUT_MAX</sub> (mA) |  |

| 0 (default)   | 0 (default) | 25.5 (default)            |  |

| 1             | 1           | 51                        |  |

The LP5812 can individually adjust the peak current of each LED by using Dot Current (DC) function. The brightness deviation among the LED bins can be miminized, to achieve uniform display performance. The current is adjusted with 256 steps from 0 to 100% of I<sub>OUT\_MAX.</sub>, which is programmed in an 8-bit register whose default value is 80h.

Table 8-3. Dot Current (DC) bits setting

| 8-bits Dot Curre | Detic of I |                               |

|------------------|------------|-------------------------------|

| Binary           | Decimal    | Ratio of I <sub>OUT_MAX</sub> |

| 0000 0000        | 0          | 0%                            |

| 0000 0001        | 1          | 0.39%                         |

| 0000 0010        | 2          | 0.78%                         |

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

Table 8-3. Dot Current (DC) bits setting (continued)

| 8-bits Dot Curre    | Potio of I    |                               |

|---------------------|---------------|-------------------------------|

| Binary              | Decimal       | Ratio of I <sub>OUT_MAX</sub> |

|                     |               |                               |

| 1000 0000 (default) | 128 (default) | 50.2% (default)               |

|                     |               |                               |

| 1111 1101           | 253           | 99.2%                         |

| 1111 1110           | 254           | 99.6%                         |

| 1111 1111           | 255           | 100%                          |

By configuring the MC and DC, the peak current of each current sink can be calculated as Equation 3:

$$I_{OUT}(mA) = I_{OUT\_max} \times \frac{DC}{255}$$

(3)

The average current of each LED in TCM drive mode and mix drive mode is shown as Equation 4:

$$I_{AVE}\left(mA\right) = \frac{I_{OUT}}{N} \times \frac{DC}{255} \times D_{PWM} \tag{4}$$

- N is the total scan number setting.

- D<sub>PWM</sub> is the PWM duty.

#### 8.3.3 PWM Dimming

The LP5812 supports 8-bit PWM dimming with 24 kHz or 12 kHz frequency, which is configured by 'PWM\_Fre' bit in Dev\_config\_1 register. An internal 6 MHz oscillator is used to generate the PWM clock. SYNC pin can be configured as PWM clock input or output by configure 'vsync\_out\_en' bit in Dev\_Config\_11 register. If multiple LP5812 are used in the system with autonomous animation engine control, all devices can refer the same clock signal, which comes from one of LP5812 or external controller, to avoid animation mismatch in long time operation.

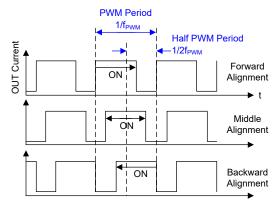

Each LED can be configured into 3 different PWM alignment phases: Forward, Middle, and Backward. The alignment phase of each LED is set by 'phase\_align' bits in Dev\_Config\_7 to Dev\_Config\_10 registers. By turning on the LEDs in different phase, the peak current load from boost or the system power supply is greatly decreased. The input current ripple and ceramic-capacitor audible ringing can also be reduced. Figure 8-13 shows the PWM alignment phases. In the forward alignment, the rising edge of PWM pulse is fixed at the beginning of PWM period. In the middle alignment, the middle point of PWM pulse is fixed at the middle of PWM period, while the pulse spreads to both directions. In the backward alignment, the falling edge of PWM pulse is fixed at the end of PWM period.

Figure 8-13. PWM Alignment Scheme

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

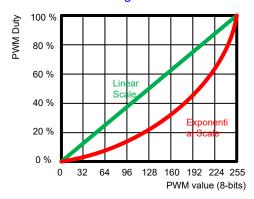

The LP5812 allow users to configure the dimming scale as exponential curve or linear curve, through the 'exp\_en' bits in Dev\_Config\_5 and Dev\_Config\_6 registers. A human-eye-friendly visual performance can be achieved by using the internal exponential scale. The linear scale has great linearity between PWM duty cycle and PWM setting value, which provides flexible approach for external controlled gamma correction algorithm. The 8-bit linear and exponential curves are shown as Figure 8-14.

Figure 8-14. Linear and Exponential PWM Dimming Curves

## 8.3.4 Autonomous Animation Engine Control

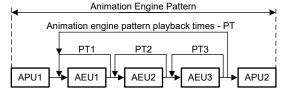

The LP5812 supports both manual mode and autonomous mode to control the DC and PWM of each LED. In manual mode, the LEDs are directly controlled by the related configuration registers and reflect the value immediately. In autonomous mode, the autonomous animation engine is applied for each LED, which can realize vivid lighting effects without external processor control. The animation engine pattern is composed by 3 animation engine units (AEU) and 2 animation pause units (APU) for complex and flexible control. One AEU is formed by 4 slopers, which is used for fading effect.

After setting up all animation engine pattern configurations, sending start\_cmd to the device can let the animation running autonomously, to free external controller real-time loading. The PWM value and unit status of each LED can be read from PWM\_value registers and pattern\_status registers. To make sure the precision of reading results, sending pause\_cmd to pause the animation firstly is recommended.

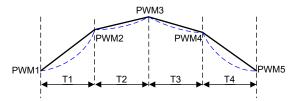

#### 8.3.4.1 Animation Engine Pattern

Each LED of the LP5812 has own animation engine, to achieve premium visual lighting effects. One whole animation engine pattern is defined as Figure 8-15. 3 animation engine units (AEU) and 2 animation pause units (APU) compose the animation engine pattern. AEU2 and AEU3 can be skipped by setting the playback times to 0. The LED current of each LEDs in the autonomous mode is set through the Autonomous DC registers.

Figure 8-15. Animation engine pattern

The whole animation pattern includes two APUs and three AEUs with several playback times:

- APUx (x = 1, 2): Animation pause unit, each unit includes one timing value T.

- AEUx (x = 1, 2, 3): Animation engine unit, including 5 PWM values PWM1 to PWM5 and 4 time values T1 to T4.

- PT: Playback times of AEU1+AEU2+AEU3, which has 2-bit value to set 0/1/2/Infinite times.

- PTx: Playback times of AEUx (x=1/2/3), which has 2-bit value to set 0/1/2/Infinite times.

Copyright © 2023 Texas Instruments Incorporated

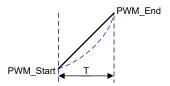

#### 8.3.4.2 Sloper

Sloper is the basic element to achieve autonomous fade-in and fade-out animations. It can achieve 256 steps fade-in or fade-out effects from 'PWM Start' to 'PWM End' within a target time period T as Figure 8-16. The 8-bit PWM steps, which is configurable in animation pattern PWM setting registers, help to achieve extremely smooth effects. Exponential dimming curve can also be supported in the sloper.

Figure 8-16. Sloper curve demonstration

The programable time T is selectable from 0 to around 8 s with 16 levels shown in Table 8-4.

Table 8-4. Programable time options

| Reg | gister value | 0h  | 1h     | 2h     | 3h     | 4h     | 5h     | 6h     | 7h     | 8h     | 9h     | Ah     | Bh     | Ch     | Dh     | Eh     | Fh     |

|-----|--------------|-----|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| Ti  | ime (Typ.)   | 0 s | 0.09 s | 0.18 s | 0.36 s | 0.54 s | 0.80 s | 1.07 s | 1.52 s | 2.06 s | 2.50 s | 3.04 s | 4.02 s | 5.01 s | 5.99 s | 7.06 s | 8.05 s |

#### 8.3.4.3 Animation Engine Unit (AEU)

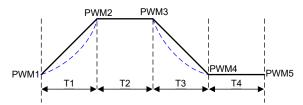

The AEU is the most important unit to achieve autonomous animation effects. One AEU is formed by 4 slopers. There are 5 PWM values and 4 time values can be configured in the AEU. Each PWMx (x = 1, 2,..., 5) can be arbitrarily programmed from 0 to 255, The Tx (x = 1, 2, 3, 4) is selectable from 0 to 8 s with 16 levels referring to Table 8-4. If two adjacent PWM values are equal, the brightness keeps unchange within the time setting. When a Tx is set to 0, this sloper is skipped. To avoid flicker happens due to PWM value suddenly changes, the begin and end PWM of this sloper need to be the same.

Typical breathing effect example is illustrated as Figure 8-17.

Figure 8-17. Animation engine unit - Example 1

Advanced breathing effect example is shown in Figure 8-18. 2 different fading speeds are set in the PWM rising and falling phases, to achieve a complex animation.

Figure 8-18. Animation engine unit - Example 2

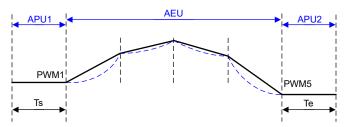

## 8.3.4.4 Animation Pause Unit (APU)

The APU is defined as the pausing time at the beginning and the end of the animation pattern. The APU contains 1 time value which is selectable from 0 to 8 s with 16 levels referring to Table 8-4. If the value is set as 0, the APU is skipped. The brightness of APU1 uses the PWM1 value of the AEU following the APU1, while the brightness of APU2 uses the PWM5 value of the AEU in front of APU2. One animation pattern example is shown

Product Folder Links: LP5812

in Figure 8-19. Only AEU2 is enabled in the pattern, so that the brightness of APU1 uses the PWM1 value of AEU2, and the brightness of APU2 uses PWM5 value of AEU2.

Figure 8-19. APU example

## 8.3.5 Protections and Diagnostics

### 8.3.5.1 LED Open Detections

The LP5812 integrates LED open detection (LOD) for the fault caused by any open LED. The threshold for LOD is 90 mV when max current is set as 25.5 mA, and 180 mV when max current is set as 51 mA. To have enough detection time, LOD can only be performed when the PWM setting of this LED is above 25. If the voltage on the cathode of this LED is lower than the LOD threshold in continuously 3 cycles, LED open of this LED is reported to the corresponding LOD status register.

The LOD flags can be cleared by writing 1h to 'lod\_clear' bit in Fault\_Clear register. If the LED open status is removed, the related 'lod status' bit is set to 0 automatically.

The 'lod\_action' bit in Dev\_config\_12 register can determine the action once open fault is detected. When the 'lod\_action' bit is set to 1h, the dot where LED open happens is turned off to avoid any unpredictable issue. When the 'lod\_action' bit is 0, no additional action is taken after LOD is detected. LED open fault detection and action is only executed in NORMAL state.

## 8.3.5.2 LED Short Detections

The LP5812 integrates LED short detection (LSD) for the fault caused by any short LED. The threshold of LSD is able to configure from  $(0.35 \times V_{OUT})$  V to  $(0.65 \times V_{OUT})$  V by configuring lsd\_threshold in Dev\_config\_12 register. To have enough detection time, LSD can only be performed when the PWM setting of this LED is above 25. If the voltage on the cathode of this LED is higher than the LSD threshold in continuously 3 cycles, LED short of this LED is reported to the corresponding LSD\_status register.

The LSD flags can be cleared by writing 1h to lsd\_clear in Fault\_CLR register. If the LED short status is removed, the related lsd status bit is set to 0 automatically.

The 'lsd\_action' bit in Dev\_config\_12 register can determine the reaction once open fault is detected. When the 'lsd\_action' bit is set to 1h, all LEDs are turned off which is called one fails all fail (OFAF) action, to prevent potential damage caused by the short issue. The device enters to STANDBY state after sending 'lsd\_clear' command. When the 'lsd\_action' bit is 0, no additional action is taken after LSD is detected. LSD detection is only executed in NORMAL state.

#### 8.3.5.3 Thermal Shutdown

The LED driver of LP5812 goes into thermal shutdown state once the junction temperature exceeds 150°C. All LEDs turn off to avoid damaging the device. When the junction temperature drops below the thermal shutdown recovery temperature 130°C, the LED driver starts operating again.

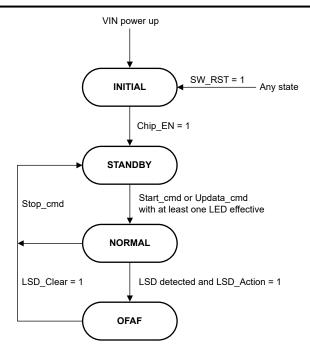

## 8.4 Device Functional Modes

The Figure 8-20 shows the main state machine of the LED driver.

Figure 8-20. LP5812 functional modes

- INITIAL: The device enters into INITIAL after VIN power up.

- STANDBY: The device enters into STANDBY state from INITIAL when Chip\_EN is set to 1. The device can

also enter into STANDBY from NORMAL when no LED is effective, or Stop\_cmd is received, or from OFAF

when LSD Clear = 1.

- NORMAL: The device enters NORMAL state from STANDBY when one or more LEDs are effective: for manual mode, at least one LED is enable (PWM and DC setting is not 0); for autonomous mode, at lease one LED is enable and Start\_cmd is received.

- OFAF: The device enters OFAF (one fail all fail) state when LED short is detected and LSD\_Action =1. In OFAF mode, all LEDs are turned off. Once LSD\_Clear is writen to 1, the device enters back to STANDBY state.

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

## 8.5 Programming

The LP5812 is compatible with I<sup>2</sup>C standard specification. The device supports standard mode (100-kHz maximum), fast mode (400-kHz maximum), and fast plus mode (1-MHz maximum). The device has 4 different chip address versions, which allows connecting up to four parallel devices in one I<sup>2</sup>C bus.

#### I<sup>2</sup>C Data Transactions

The data on SDA line must be stable during the HIGH period of the clock signal (SCL). In other words, state of the data line can only be changed when clock signal is LOW. START and STOP conditions classify the beginning and the end of the data transfer session. A START condition is defined as the SDA signal transitioning from HIGH to LOW while SCL line is HIGH. A STOP condition is defined as the SDA transitioning from LOW to HIGH while SCL is HIGH. The bus leader always generates START and STOP conditions. The bus is considered to be busy after a START condition and free after a STOP condition. During data transmission, the bus leader can generate repeated START conditions. First START and repeated START conditions are functionally equivalent.

Each byte of data has to be followed by an acknowledge bit. The acknowledge related clock pulse is generated by the leader. The leader releases the SDA line (HIGH) during the acknowledge clock pulse. The device pulls down the SDA line during the 9<sup>th</sup> clock pulse, signifying an acknowledge. The device generates an acknowledge after each byte has been received.

There is one exception to the acknowledge after every byte rule. When the leader is the receiver, the receiver must indicate to the transmitter an end of data by not acknowledging (negative acknowledge) the last byte clocked out of the follower. This negative acknowledge still includes the acknowledge clock pulse (generated by the leader), but the SDA line is not pulled down.

#### I<sup>2</sup>C Data Format

The address and data bits are transmitted MSB first with 8-bits length format in each cycle. Each transmission is started with Address Byte 1, which are divided into 5 bits of the chip address, 2 higher bits of the register address, and 1 read/write bit. The other 8 lower bits of register address are put in Address Byte 2. The device supports both independent mode and broadcast mode. The auto-increment feature allows writing / reading several consecutive registers within one transmission. If not consecutive, a new transmission must be started. The Bit 4 and Bit 3 are determined by the device, which can refer to Section 4.

Table 8-5. I<sup>2</sup>C Data Format

| Chip Address        |                     |                                   |                                                    |                                                                                                                                                                                                                      | Register                                                                                                                                                                                                                                                                         | R/W                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------|---------------------|-----------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 7               | Bit 6               | Bit 5                             | Bit 4                                              | Bit 3                                                                                                                                                                                                                | Bit 2                                                                                                                                                                                                                                                                            | Bit 1                                                                                                                                                                                                                                                                                                                                              | Bit 0                                                                                                                                                                                                                                                                                                                                                                  |

| 1                   | 0                   | 1                                 | Bit 4                                              | Bit 3                                                                                                                                                                                                                | 9 <sup>th</sup> bit                                                                                                                                                                                                                                                              | 8 <sup>th</sup> bit                                                                                                                                                                                                                                                                                                                                | R: 1 W: 0                                                                                                                                                                                                                                                                                                                                                              |

| 1                   | 1                   | 0                                 | 1                                                  | 1                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                        |

|                     |                     |                                   | Register                                           | Address                                                                                                                                                                                                              | ,                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                        |