Texas Instruments

MCT8329A SLLSFQ3 – JANUARY 2023

# MCT8329A High Speed Sensorless Trapezoidal Control Three-phase BLDC Gate Driver

# 1 Features

- Three-phase BLDC gate driver with integrated sensorless motor control algorithm

- Code-free high speed Trapezoidal Control

- Supports up to 3 kHz (electrical frequency)

- Very fast startup time (<50 ms)</li>

- Fast Deceleration (<150 ms)</li>

- Supports 120° or 150° modulation to improve acoustic performance

- Forward and reverse windmilling support

- Analog, PWM, freq. or I<sup>2</sup>C based control input

- Configurable motor startup and stop options

- Optional closed loop speed or power control, open loop voltage control

- 5-point configurable reference profile support

- Anti-voltage surge prevents overvoltage

- Variable monitoring through DACOUT

- 65-V Three phase half-bridge gate driver

- Drives 3 high-side and 3 low-side N-Channel MOSFETs, 4.5 to 60-V operating voltage

- Supports 100% PWM duty cycle

- Bootstrap based gate driver architecture

- 1-A/2-A Maximum peak source/sink current

- Integrated current sense amplifier

- Adjustable gain (5, 10, 20, 40 V/V)

- Low power sleep mode

- 5-

$$\mu$$

A (maximum) at V<sub>PVDD</sub> = 24-V, T<sub>A</sub> = 25°C

- Speed loop accuracy: < 3% with internal clock

- Supports up to 100-kHz PWM frequency

- Accurate LDO (AVDD) 3.3-V ±3%, 50-mA support with AVDD connected to VREG

- Independent driver shutdown path (DRVOFF)

- Spread spectrum for EMI mitigation

- Suite of Integrated protection features

- Supply undervoltage lockout (UVLO)

- Motor lock detection (3 different types)

- Overcurrent protection (OCP)

- Thermal shutdown (TSD)

- Fault condition indication pin (nFAULT)

- Optional fault diagnostics over I<sup>2</sup>C interface

# 2 Applications

- Brushless-DC (BLDC) Motor Modules

- Cordless Vacuum Cleaners

- HVAC Blowers and Ventilators

- Appliance Fans and Pumps

- Cordless Garden and Power Tools, Lawnmowers

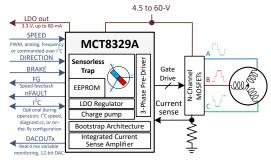

# **3 Description**

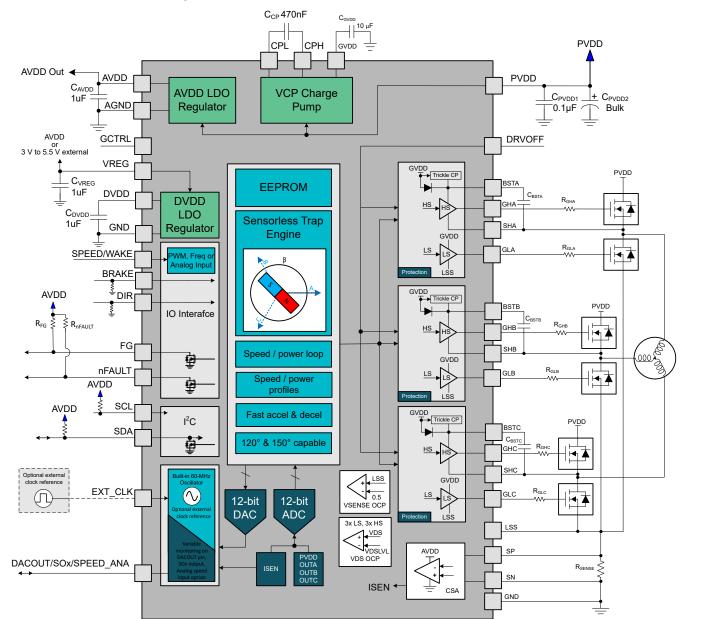

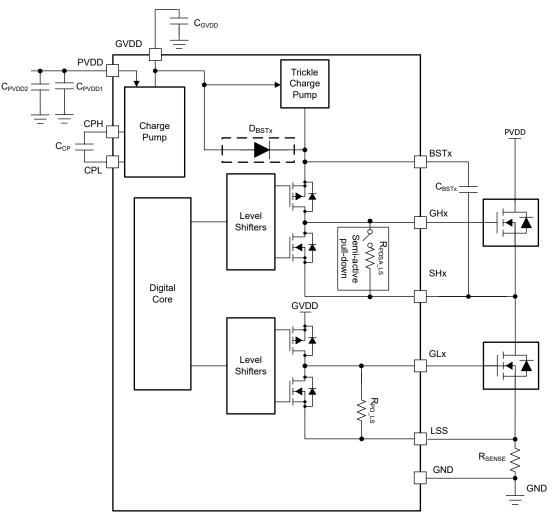

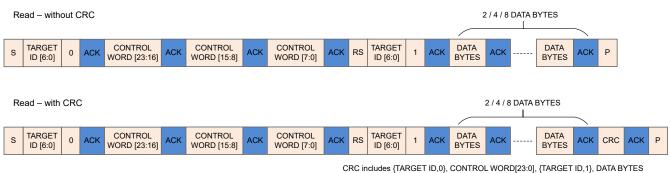

The MCT8329A provides a single-chip, code-free sensorless trapezoidal solution for applications requiring high speed operation or very fast startup time for three phase brushless-DC motors. The device provide three half-bridge gate drivers, each capable of driving high-side and low-side N-channel power MOSFETs. The device generates correct gate drive voltages using an internal charge pump and enhances the high-side MOSFETs using a bootstrap circuit. A trickle charge pump is included to support 100% duty cycle. The gate drive architecture supports peak gate drive currents up to 1-A source and 2-A sink. The MCT8329A can operate from a single power supply and supports a wide input supply range of 4.5 to 60 V.

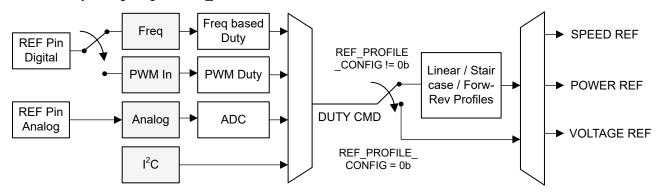

Sensorless trapezoidal control is highly configurable through register settings in a non-volatile EEPROM (MCT8329A1I) ranging from motor start-up behavior to closed loop operation, which allows the device to operate stand-alone once it has been configured. Motor current is sensed using an integrated current sensing amplifier supporting single external shunt resistor. The device receives a speed command through a PWM input or analog voltage or variable frequency square wave or I<sup>2</sup>C command. There are a large number of protection features integrated into the MCT8329A, intended to protect the device, motor, and system against fault events.

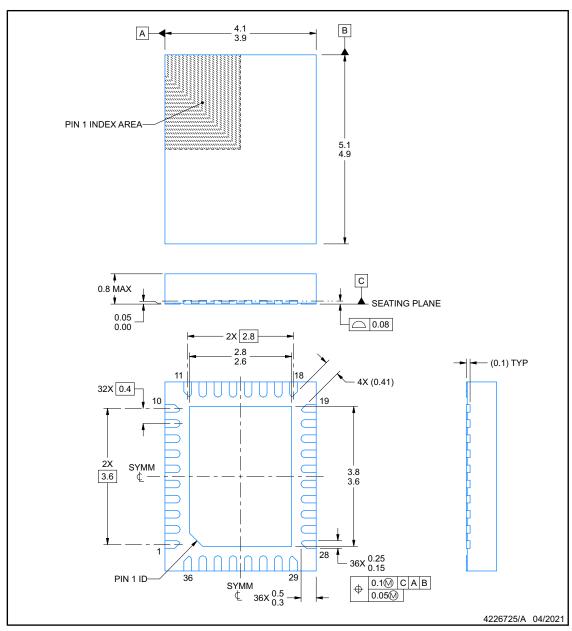

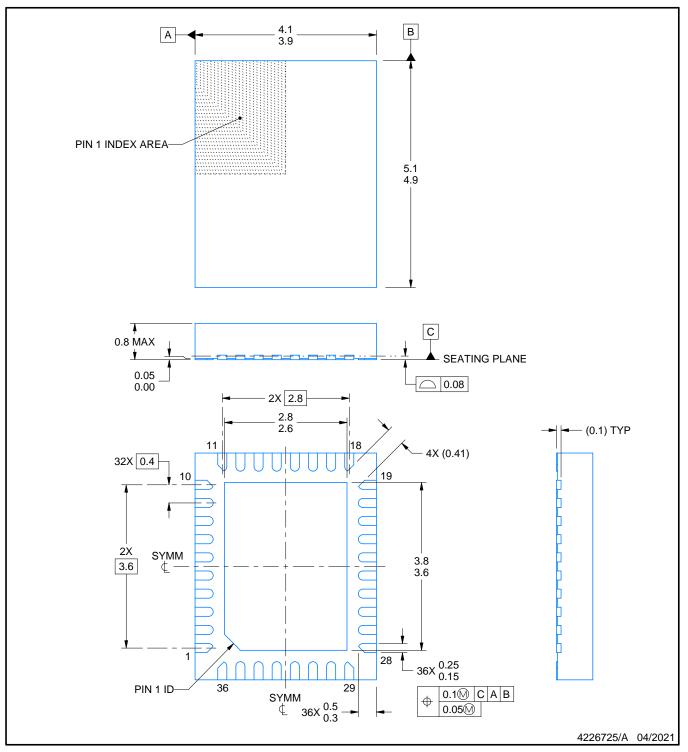

# Device Information<sup>(1)</sup>

| PART NUMBER    | PACKAGE   | BODY SIZE (NOM)   |

|----------------|-----------|-------------------|

| MCT8329A1IREER | VQFN (36) | 5.00 mm × 4.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

# **Table of Contents**

| 1 Features                                     | 1               |

|------------------------------------------------|-----------------|

| 2 Applications                                 |                 |

| 3 Description                                  | 1               |

| 4 Revision History                             | 2               |

| 5 Pin Configuration and Functions              |                 |

| 6 Specifications                               | 6               |

| 6.1 Absolute Maximum Ratings                   | 6               |

| 6.2 ESD Ratings Comm                           | 6               |

| 6.3 Recommended Operating Conditions           | <mark>8</mark>  |

| 6.4 Thermal Information 1pkg                   |                 |

| 6.5 Electrical Characteristics                 | 9               |

| 6.6 Characteristics of the SDA and SCL bus for |                 |

| Standard and Fast mode                         | 16              |

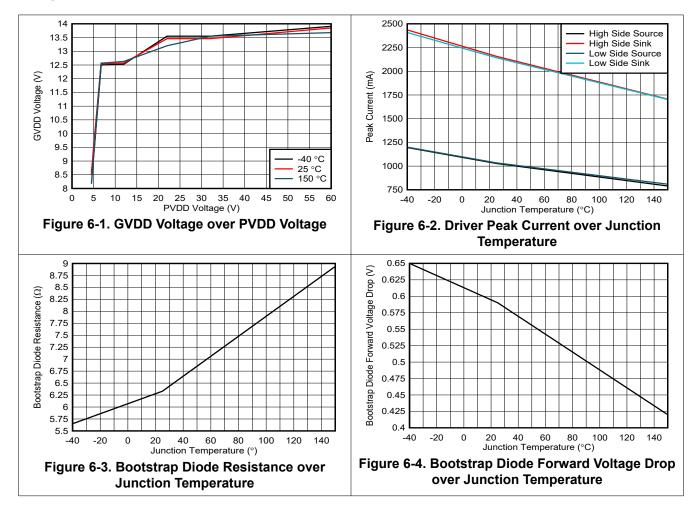

| 6.7 Typical Characteristics                    | 18              |

| 7 Detailed Description                         | 19              |

| 7.1 Overview                                   | 19              |

| 7.2 Functional Block Diagram                   | 20              |

| 7.3 Feature Description                        | <mark>21</mark> |

| 7.4 Device Functional Modes                    | <mark>67</mark> |

| 7.5 External Interface                         | <mark>68</mark> |

| 7.6 EEPROM access and I <sup>2</sup> C interface | 71  |

|--------------------------------------------------|-----|

| 7.7 EEPROM (Non-Volatile) Register Map           |     |

| 7.8 RAM (Volatile) Register Map                  |     |

| 8 Application and Implementation                 |     |

| 8.1 Application Information                      |     |

| 8.2 Typical Applications                         |     |

| 9 Power Supply Recommendations                   |     |

| 9.1 Bulk Capacitance                             |     |

| 10 Layout                                        |     |

| 10.1 Layout Guidelines                           |     |

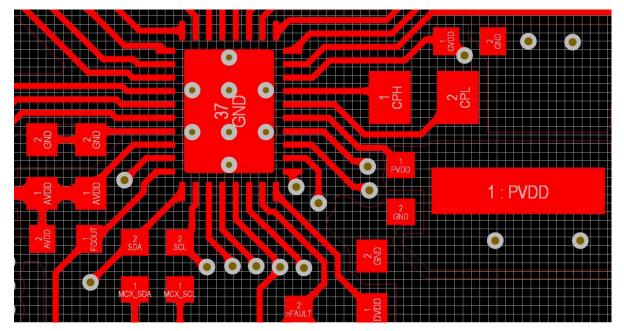

| 10.2 Layout Example                              |     |

| 10.3 Thermal Considerations                      |     |

| 11 Device and Documentation Support              |     |

| 11.1 Documentation Support                       |     |

| 11.2 Support Resources                           |     |

| 11.3 Trademarks                                  |     |

| 11.4 Electrostatic Discharge Caution             |     |

| 11.5 Glossary                                    |     |

| 12 Mechanical, Packaging, and Orderable          |     |

| Information                                      | 160 |

|                                                  |     |

# **4** Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| DATE         | REVISION | NOTES           |

|--------------|----------|-----------------|

| January 2023 | *        | Initial Release |

\_ ... .

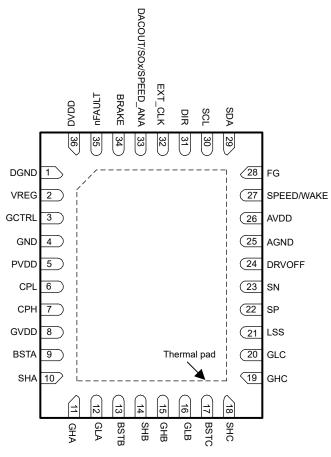

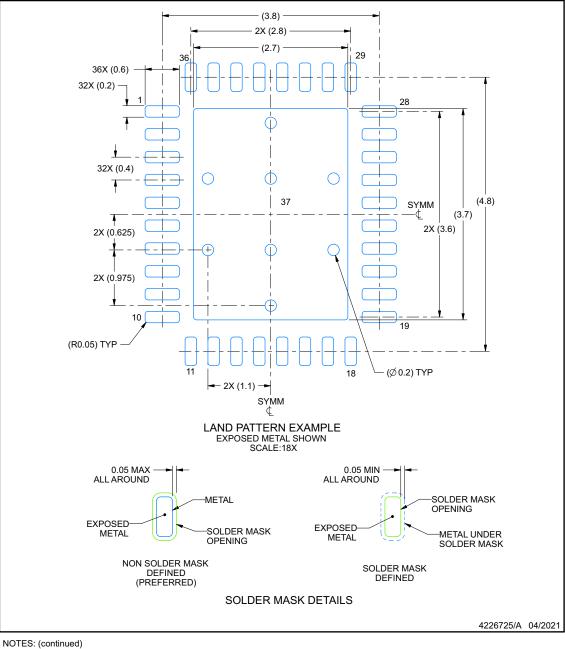

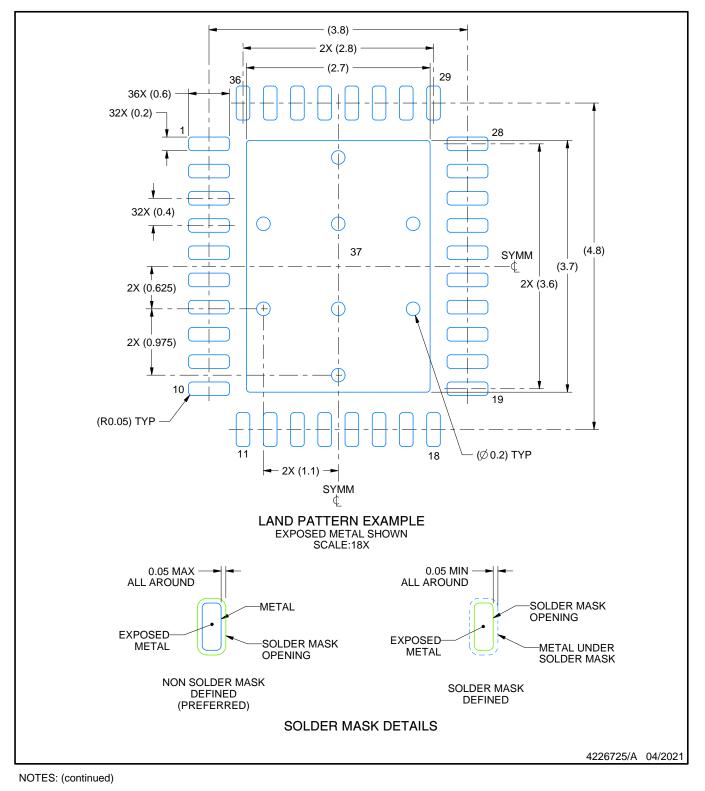

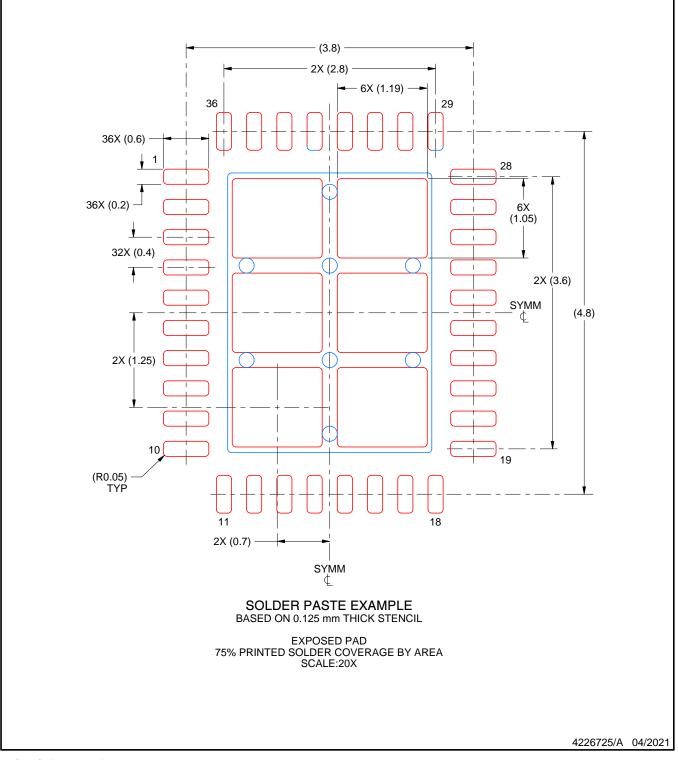

# **5** Pin Configuration and Functions

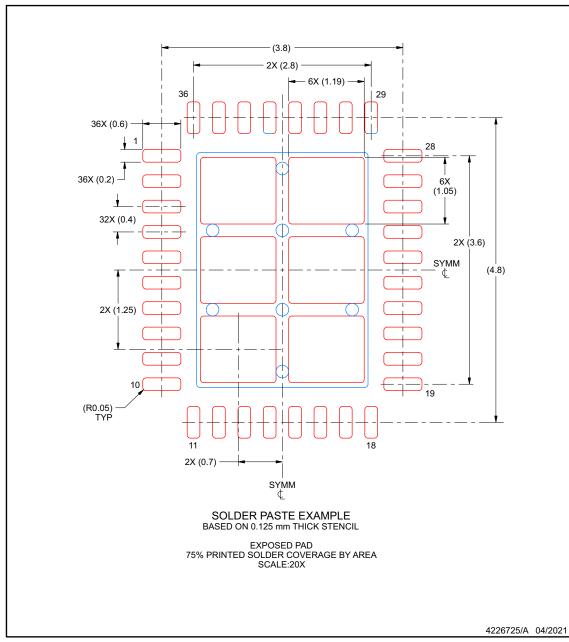

# Figure 5-1. MCT8329A1I 36-Pin VQFN With Exposed Thermal Pad Top View

### Table 5-1. Pin Functions

| PIN                              | 36-pin Package | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                  |

|----------------------------------|----------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                             | MCT8329A1I     |                     | DESCRIPTION                                                                                                                                                                                                                                                                                  |

| AGND                             | 25             | GND                 | Device analog ground                                                                                                                                                                                                                                                                         |

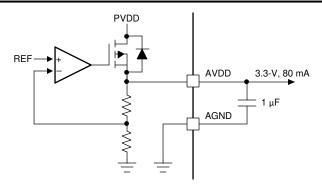

| AVDD                             | 26             | PWR                 | 3.3-V regulator output. Connect a X5R or X7R, 1- $\mu$ F, 6.3-V ceramic capacitor between the AVDD and AGND pins. This regulator can source up to 50 mA external (if AVDD shorted to VREG). TI recommends a capacitor voltage rating at least twice the normal operating voltage of the pin. |

| BRAKE                            | 34             | I                   | High $\rightarrow$ brake the motor<br>Low $\rightarrow$ normal operation<br>Connect to GND via 10-k $\Omega$ resistor, if not used                                                                                                                                                           |

| BSTA                             | 9              | 0                   | Bootstrap output pin. Connect a X5R or X7R, 1- $\mu$ F, 25-V ceramic capacitor between BSTA and SHA.                                                                                                                                                                                         |

| BSTB                             | 13             | 0                   | Bootstrap output pin. Connect a X5R or X7R, 1- $\mu$ F, 25-V ceramic capacitor between BSTB and SHB.                                                                                                                                                                                         |

| BSTC                             | 17             | 0                   | Bootstrap output pin. Connect a X5R or X7R, 1- $\mu$ F, 25-V ceramic capacitor between BSTC and SHC.                                                                                                                                                                                         |

| CPH                              | 7              | PWR                 | Charge pump switching node. Connect a X5R or X7R, PVDD-rated ceramic                                                                                                                                                                                                                         |

| CPL                              | 6              | PWR                 | capacitor between the CPH and CPL pins. TI recommends a capacitor voltage rating at least twice the normal operating voltage of the pin.                                                                                                                                                     |

| DACOUT/S<br>Ox/<br>SPEED_AN<br>A | 33             | I/O                 | Multipurpose pin. Configurable as DAC output, current sense amplifier output or analog reference (speed or power or voltage) input.                                                                                                                                                          |

Copyright © 2023 Texas Instruments Incorporated

# Table 5-1. Pin Functions (continued)

| PIN            | 36-pin Package |                     |                                                                                                                                                                                                                                                                                                   |

|----------------|----------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME           | MCT8329A1I     | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                       |

| DGND           | 1              | GND                 | Device digital ground                                                                                                                                                                                                                                                                             |

| DIR            | 31             | I                   | Direction of motor spinning;<br>When low, phase driving sequence is OUT A $\rightarrow$ OUT B $\rightarrow$ OUT C<br>When high, phase driving sequence is OUT A $\rightarrow$ OUT C $\rightarrow$ OUT B<br>Connect to GND via 10-k $\Omega$ resistor, if not used                                 |

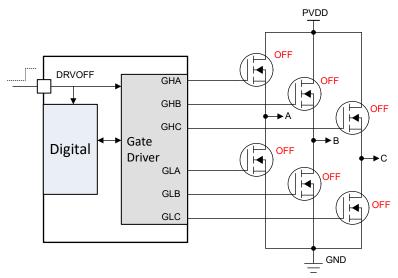

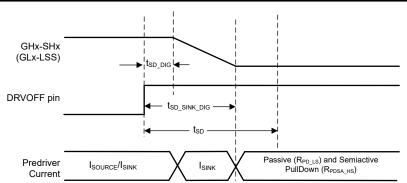

| DRVOFF         | 24             | I                   | Independent driver shutdown path. Pulling DRVOFF high turns off all external MOSFETs by putting the gate drivers into the pull-down state. This signal bypasses and overrides the digital and control core.                                                                                       |

| DVDD           | 36             | PWR                 | 1.5-V internal regulator output. Connect a X5R or X7R, 1- $\mu$ F, 6.3-V ceramic capacitor between the DVDD and DGND pins.                                                                                                                                                                        |

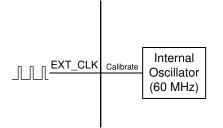

| EXT_CLK        | 32             | I                   | External clock reference input in external clock reference mode.                                                                                                                                                                                                                                  |

| FG             | 28             | 0                   | Motor speed indicator output. Open-drain output requires an external pull-up resistor to 1.8 to 5-V. External pull up resistor needs to be connected even if the pin functionality is not used.                                                                                                   |

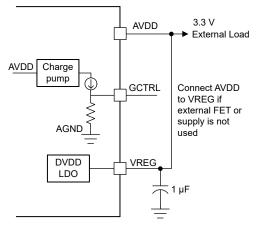

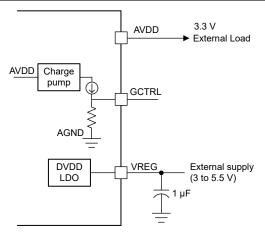

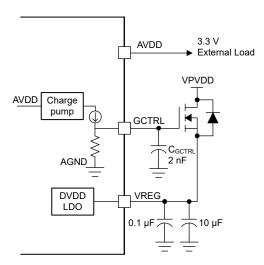

| GCTRL          | 3              | 0                   | Gate control for external MOSFET used as regulator to supply current to digital subsystem through VREG pin. This functionality helps to reduce power dissipation inside the device.                                                                                                               |

| GHA            | 11             | 0                   | High-side gate driver output. Connect to the gate of the high-side power MOSFET                                                                                                                                                                                                                   |

| GHB            | 15             | 0                   | High-side gate driver output. Connect to the gate of the high-side power MOSFET                                                                                                                                                                                                                   |

| GHC            | 19             | 0                   | High-side gate driver output. Connect to the gate of the high-side power MOSFET                                                                                                                                                                                                                   |

| GLA            | 12             | 0                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET                                                                                                                                                                                                                     |

| GLB            | 16             | 0                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET                                                                                                                                                                                                                     |

| GLC            | 20             | 0                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET                                                                                                                                                                                                                     |

| GND            | 4              | GND                 | Device power ground                                                                                                                                                                                                                                                                               |

| GVDD           | 8              | PWR                 | Gate driver power supply output. Connect a X5R or X7R, 30-V rated ceramic $\geq$ 10-<br>uF local capacitance between the GVDD and GND pins. TI recommends a capacitor<br>value of >10x C <sub>BSTx</sub> and voltage rating at least twice the normal operating voltage of<br>the pin.            |

| LSS            | 21             | PWR                 | Low side source pin, connect all sources of the external low-side MOSFETs here.<br>This pin is the sink path for the low-side gate driver, and serves as an input to<br>monitor the low-side MOSFET VDS voltage and VSEN_OCP voltage.                                                             |

| nFAULT         | 35             | 0                   | Fault indicator. This pin is pulled logic-low with fault condition. Open-drain output requires an external pull-up resistor to 1.8V to 5 V. External pull up resistor needs to be connected even if the pin functionality is not used.                                                            |

| PVDD           | 5              | PWR                 | Gate driver power supply input. Connect to the bridge power supply. Connect a X5R or X7R, 0.1- $\mu$ F, >2x PVDD-rated ceramic and >10- $\mu$ F local capacitance between the PVDD and GND pins. TI recommends a capacitor voltage rating at least twice the normal operating voltage of the pin. |

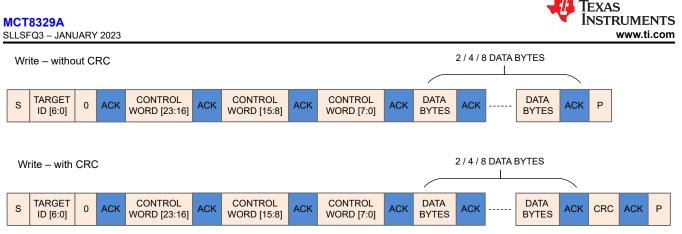

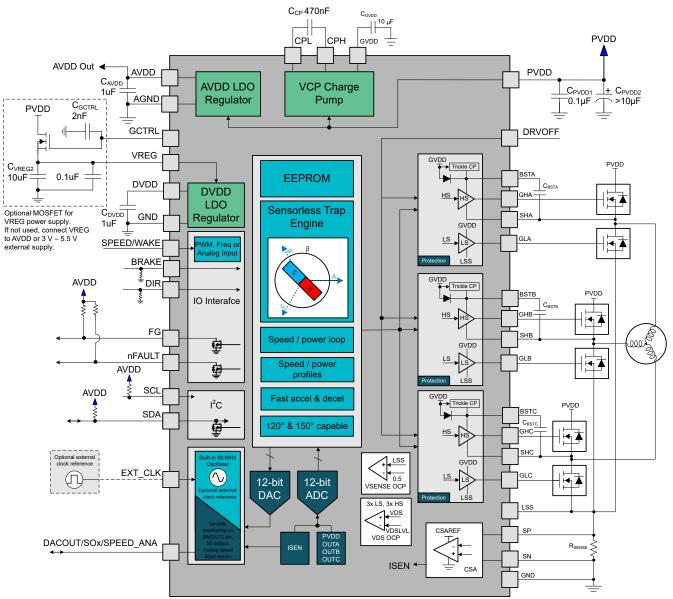

| SCL            | 30             | I                   | I <sup>2</sup> C clock input                                                                                                                                                                                                                                                                      |

| SDA            | 29             | I/O                 | I <sup>2</sup> C data line                                                                                                                                                                                                                                                                        |

| SHA            | 10             | I/O                 | High-side source pin. Connect to the high-side power MOSFET source. This pin is an input for the VDS monitor and the output for the high-side gate driver sink.                                                                                                                                   |

| SHB            | 14             | I/O                 | High-side source pin. Connect to the high-side power MOSFET source. This pin is an input for the VDS monitor and the output for the high-side gate driver sink.                                                                                                                                   |

| SHC            | 18             | I/O                 | High-side source pin. Connect to the high-side power MOSFET source. This pin is an input for the VDS monitor and the output for the high-side gate driver sink.                                                                                                                                   |

| SN             | 23             | I                   | Current sense amplifier input. Connect to the low-side of the current shunt resistor.                                                                                                                                                                                                             |

| SP             | 22             | I                   | Low-side current shunt amplifier input. Connect to the low-side power MOSFET source and high-side of the current shunt resistor.                                                                                                                                                                  |

| SPEED/<br>WAKE | 27             | I                   | Multifunction input.<br>Device sleep/wake input.<br>Device speed input; supports analog, PWM or frequency based reference (speed or<br>power or voltage) input.                                                                                                                                   |

|             |                | Table | 5-1. Pin Functions (continued)                                                                                                                                                       |

|-------------|----------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN         | 36-pin Package |       | DESCRIPTION                                                                                                                                                                          |

| NAME        | MCT8329A1I     |       | DESCRIPTION                                                                                                                                                                          |

| VREG        | 2              | PWR   | Voltage regulator input supply for internal DVDD LDO. Connect to AVDD or external 3-5.5 V. Connect a X5R or X7R, 1- $\mu$ F, 6.3-V ceramic capacitor between the VREG and DGND pins. |

| Thermal pad | -              | PWR   | Must be connected to ground                                                                                                                                                          |

(1) I = input, O = output, GND = ground pin, PWR = power, NC = no connect

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                                 |                                                                               | MIN                   | MAX                   | UNIT |

|-----------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------|-----------------------|------|

| Power supply pin voltage                                        | PVDD                                                                          | -0.3                  | 65                    | V    |

| Bootstrap pin voltage                                           | BSTx                                                                          | -0.3                  | 80                    | V    |

| Bootstrap pin voltage                                           | BSTx with respect to SHx                                                      | -0.3                  | 20                    | V    |

| Bootstrap pin voltage                                           | BSTx with respect to GHx                                                      | -0.3                  | 20                    | V    |

| Charge pump pin voltage                                         | CPL, CPH                                                                      | -0.3                  | V <sub>GVDD</sub>     | V    |

| Voltage difference between ground pins                          | GND, DGND, AGND                                                               | -0.3                  | 0.3                   | V    |

| Voltage regulator pin voltage (VREG)                            | VREG                                                                          | -0.3                  | 6                     | V    |

| Gate control pin voltage (GCTRL)                                | GCTRL                                                                         | -0.3                  | 7                     | V    |

| Gate driver regulator pin voltage                               | GVDD                                                                          | -0.3                  | 20                    | V    |

| Digital regulator pin voltage                                   | DVDD                                                                          | -0.3                  | 1.7                   | V    |

| Analog regulator pin voltage                                    | AVDD                                                                          | -0.3                  | 4                     | V    |

| Logic pin voltage                                               | BRAKE, DRVOFF, DIR,<br>EXT_CLK, SCL, SDA, SPEED/WAKE,<br>DACOUT/SOx/SPEED_ANA | -0.3                  | 6                     | V    |

| Open drain pin output voltage                                   | nFAULT, FG                                                                    | -0.3                  | 6                     | V    |

| High-side gate drive pin voltage                                | GHx                                                                           | -8                    | 80                    | V    |

| Transient 500-ns high-side gate drive pin voltage               | GHx                                                                           | -10                   | 80                    | V    |

| High-side gate drive pin voltage                                | GHx with respect to SHx                                                       | -0.3                  | 20                    | V    |

| High-side source pin voltage                                    | SHx                                                                           | -8                    | 70                    | V    |

| Transient 500-ns high-side source pin voltage                   | SHx                                                                           | -10                   | 72                    | V    |

| Low-side gate drive pin voltage                                 | GLx with respect to LSS                                                       | -0.3                  | 20                    | V    |

| Transient 500-ns low-side gate drive pin voltage <sup>(2)</sup> | GLx with respect to LSS                                                       | -1                    | 20                    | V    |

| Low-side gate drive pin voltage                                 | GLx with respect to GVDD                                                      |                       | 0.3                   | V    |

| Transient 500-ns low-side gate drive pin voltage                | GLx with respect to GVDD                                                      |                       | 1                     | V    |

| Low-side source sense pin voltage                               | LSS                                                                           | -1                    | 1                     | V    |

| Transient 500-ns low-side source sense pin voltage              | LSS                                                                           | -10                   | 8                     | V    |

| Gate drive current                                              | GHx, GLx                                                                      | Internally<br>Limited | Internally<br>Limited | А    |

| Shunt amplifier input pin voltage                               | SN, SP                                                                        | -1                    | 1                     | V    |

| Transient 500-ns shunt amplifier input pin voltage              | SN, SP                                                                        | -10                   | 8                     | V    |

| Ambient temperature, T <sub>A</sub>                             | ·                                                                             | -40                   | 125                   | °C   |

| Junction temperature, T <sub>J</sub>                            |                                                                               | -40                   | 150                   | °C   |

| Storage temperature, T <sub>stq</sub>                           |                                                                               | -65                   | 150                   | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime

(2) Supports upto 5A for 500 nS when GLx-LSS is negative

# 6.2 ESD Ratings Comm

|   |       |               |                                                                                | VALUE | UNIT |

|---|-------|---------------|--------------------------------------------------------------------------------|-------|------|

|   |       | Electrostatic | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 | V    |

| V | (ESD) | discharge     | Charged device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±750  | v    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating temperature range (unless otherwise noted)

|                                  |                                                                       |                                                      | MIN | NOM MA | X UNIT           |

|----------------------------------|-----------------------------------------------------------------------|------------------------------------------------------|-----|--------|------------------|

| V <sub>PVDD</sub>                | Power supply voltage                                                  | PVDD                                                 | 4.5 | e      | 0 V              |

| V <sub>PVDD_RAMP</sub>           | Power supply voltage ramp rate at power up                            | PVDD                                                 |     | 3      | 0 V/us           |

| V <sub>BST</sub>                 | Bootstrap pin voltage with respect to SHx                             | SPEED/WAKE = High, Outputs are<br>switching          | 4   | 2      | 0 V              |

| I <sub>AVDD</sub> <sup>(1)</sup> | Regulator external load current (AVDD connected to VREG)              | AVDD                                                 |     | 5      | 0 mA             |

| ITRICKLE                         | Trickle charge pump external load current                             | BSTx                                                 |     |        | 2 μΑ             |

| V <sub>VREG</sub>                | VREG pin voltage                                                      | VREG                                                 | 2.2 | 5      | 5 V              |

| V <sub>IN</sub>                  | Logic input voltage                                                   | BRAKE, DRVOFF, DIR, EXT_CLK,<br>SPEED/WAKE, SDA, SCL | 0   | 5      | 5 V              |

| f <sub>PWM</sub>                 | PWM frequency                                                         |                                                      | 0   | 10     | 0 kHz            |

| V <sub>OD</sub>                  | Open drain pullup voltage                                             | FG, nFAULT                                           |     | 5      | 5 V              |

| I <sub>OD</sub>                  | Open drain output current                                             | nFAULT                                               |     | -1     | 0 mA             |

| I <sub>GS</sub> <sup>(1)</sup>   | Total average gate-drive current (Low<br>Side and High Side Combined) | I <sub>GHx</sub> , I <sub>GLx</sub>                  |     | 3      | 0 mA             |

| V <sub>SHSL</sub>                | Slew Rate on SHx pins                                                 |                                                      |     |        | 4 V/ns           |

| C <sub>BOOT</sub>                | Capacitor between BSTx and SHx                                        |                                                      |     | 4.7    | <sup>2)</sup> µF |

| C <sub>GVDD</sub>                | Capacitor between GVDD and GND                                        |                                                      |     | 13     | 0 µF             |

| T <sub>A</sub>                   | Operating ambient temperature                                         |                                                      | -40 | 12     | 5 °C             |

| TJ                               | Operating junction temperature                                        |                                                      | -40 | 15     | 0 °C             |

(1) Power dissipation and thermal limits must be observed

(2) Current flowing through boot diode (DBOOT) needs to be limited for  $C_{BSTx} > 4.7 \mu F$ .

# 6.4 Thermal Information 1pkg

|                       |                                              | MCT8329A   |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | REE (VQFN) | UNIT |

|                       |                                              | 36         |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 37.7       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 23.3       | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 16         | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 3.8        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 16         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 5          | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 6.5 Electrical Characteristics

|--|

|                      | PARAMETER                                             | TEST CONDITIONS                                                                                                                                                                                                                                                          | MIN                          | TYP | MAX  | UNIT |

|----------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----|------|------|

| POWER SL             | JPPLIES (PVDD, GVDD, AVDD, DVDD, V                    | /REG, GCTRL)                                                                                                                                                                                                                                                             |                              |     |      |      |

|                      |                                                       | $V_{PVDD} = 24V, V_{SPEED/WAKE} = 0, T_A = 25$<br>°C, AVDD connected to VREG                                                                                                                                                                                             |                              | 3   | 5    | μA   |

| PVDDQ                | PVDD sleep mode current                               | $V_{\text{SPEED/WAKE}}$ = 0, $T_{\text{A}}$ = 125 °C, AVDD connected to VREG                                                                                                                                                                                             |                              | 3.5 | 6    | μA   |

| PVDDS                | PVDD standby mode current                             | $V_{PVDD} = 24 V, V_{SPEED/WAKE} < V_{EN_{SB}}, DRVOFF = LOW, T_A = 25$ °C, AVDD connected to VREG                                                                                                                                                                       |                              | 25  | 28   | mA   |

|                      |                                                       | V <sub>SPEED/WAKE</sub> < V <sub>EN_SB</sub> , DRVOFF =<br>LOW, AVDD connected to VREG                                                                                                                                                                                   |                              | 25  | 28   | mA   |

|                      |                                                       | $\label{eq:VPVDD} \begin{array}{l} V_{PVDD} = 24 \ V, \ V_{SPEED/WAKE} > V_{EX\_SL}, \\ PWM\_FREQ\_OUT = 10000b \ (25 \ kHz), \\ T_{J} = 25 \ ^\circC, \ No \ FETs \ and \ motor \\ connected, \ AVDD \ connected \ to \ VREG \end{array}$                               |                              | 28  | 30   | mA   |

|                      |                                                       | $\label{eq:VPVDD} \begin{array}{l} V_{PVDD} = 24 \ V, \ V_{SPEED/WAKE} > V_{EX\_SL}, \\ PWM\_FREQ\_OUT = 10000b \ (25 \ kHz), \\ No \ FETs \ and \ motor \ connected, \ AVDD \\ connected \ to \ VREG \end{array}$                                                       |                              | 28  | 30   | mA   |

| PVDD                 | PVDD active mode current                              | $\label{eq:VPVDD} \begin{array}{l} V_{PVDD} = 8 \ V, \ V_{SPEED/WAKE} > V_{EX} \ SL, \\ PWM_FREQ_OUT = 10000b \ (25 \ kHz), \\ T_J = 25 \ ^\circC, \ No \ FETs \ and \ motor \\ connected, \ AVDD \ not \ connected \ to \\ VREG, \ VREG = 3.3 V \ external \end{array}$ |                              | 8.5 | 14.1 | mA   |

|                      |                                                       | V <sub>PVDD</sub> = 24 V, V <sub>SPEED/WAKE</sub> > V <sub>EX_SL</sub> ,<br>PWM_FREQ_OUT = 10000b (25 kHz),<br>No FETs and motor connected, AVDD<br>not connected to VREG, VREG = 3.3V<br>external                                                                       |                              | 8.5 | 11.1 | mA   |

| VREG                 | VREG pin active mode current                          | V <sub>SPEED/WAKE</sub> > V <sub>EX_SL</sub> ,<br>PWM_FREQ_OUT = 10000b (25 kHz),<br>VREG connected to AVDD                                                                                                                                                              |                              |     | 25   | mA   |

| L <sub>BSx</sub>     | Bootstrap pin leakage current                         | $V_{BSTx} = V_{SHx} = 60V, V_{GVDD} = 0V, V_{SPEED/}$<br>WAKE = LOW                                                                                                                                                                                                      | 5                            | 10  | 16   | μA   |

| L <sub>BS_TRAN</sub> | Bootstrap pin active mode transient leakage current   | GLx = GHx = Switching at 20kHz, No<br>FETs connected                                                                                                                                                                                                                     | 60                           | 115 | 300  | μA   |

|                      |                                                       | V <sub>PVDD</sub> ≥ 40 V, I <sub>GS</sub> = 10 mA, T <sub>J</sub> = 25°C                                                                                                                                                                                                 | 11.8                         | 13  | 15   | V    |

|                      |                                                       | 22 V ≤V <sub>PVDD</sub> ≤ 40 V, I <sub>GS</sub> = 30 mA, T <sub>J</sub> =<br>25°C                                                                                                                                                                                        | 11.8                         | 13  | 15   | V    |

| / <sub>GVDD_RT</sub> | GVDD Gate driver regulator voltage (Room Temperature) | 8 V ≤V <sub>PVDD</sub> ≤ 22 V, I <sub>GS</sub> = 30 mA, T <sub>J</sub> =<br>25°C                                                                                                                                                                                         | 11.8                         | 13  | 15   | V    |

| _                    | (Room Temperature)                                    | 6.75 V ≤V <sub>PVDD</sub> ≤ 8 V, I <sub>GS</sub> = 10 mA, T <sub>J</sub> = 25°C                                                                                                                                                                                          | 11.8                         | 13  | 14.5 | V    |

|                      |                                                       | 4.5 V $\leq$ V <sub>PVDD</sub> $\leq$ 6.75 V, I <sub>GS</sub> = 10 mA, T <sub>J</sub> = 25°C                                                                                                                                                                             | 2*V <sub>PVDD</sub><br>- 1   |     | 13.5 | V    |

|                      |                                                       | $V_{PVDD} \ge 40 \text{ V}, \text{ I}_{GS} = 10 \text{ mA}$                                                                                                                                                                                                              | 11.5                         |     | 15.5 | V    |

|                      |                                                       | $22 \text{ V} \leq \text{V}_{\text{PVDD}} \leq 40 \text{ V}, \text{ I}_{\text{GS}} = 30 \text{ mA}$                                                                                                                                                                      | 11.5                         |     | 15.5 | V    |

| V <sub>GVDD</sub>    | GVDD Gate driver regulator voltage                    | 8 V ≤V <sub>PVDD</sub> ≤ 22 V; I <sub>GS</sub> = 30 mA                                                                                                                                                                                                                   | 11.5                         |     | 15.5 | V    |

| V GVDD               |                                                       | 6.75 V ≤V <sub>PVDD</sub> ≤ 8 V, I <sub>GS</sub> = 10 mA                                                                                                                                                                                                                 | 11.5                         |     | 14.5 | V    |

|                      |                                                       | 4.5 V ≤V <sub>PVDD</sub> ≤ 6.75 V, I <sub>GS</sub> = 10 mA                                                                                                                                                                                                               | 2*V <sub>PVDD</sub><br>- 1.4 |     | 13.5 | V    |

| 4.5 V ≤ V <sub>PVI</sub>      |                                                                                 | otherwise noted). Typical limits apply                                                               |               |      |               |      |

|-------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------|------|---------------|------|

|                               | PARAMETER                                                                       | TEST CONDITIONS                                                                                      | MIN           | TYP  | MAX           | UNIT |

|                               |                                                                                 | $V_{PVDD} \ge 6 \text{ V}, 0 \text{ mA} \le I_{AVDD} \le 30 \text{ mA}, T_{J} = 25^{\circ}\text{C}$  | 3.26          | 3.3  | 3.33          | V    |

| V <sub>AVDD_RT</sub>          | AVDD Analog regulator voltage (Room Temperature)                                | $V_{PVDD} \ge 6 \text{ V}, 30 \text{ mA} \le I_{AVDD} \le 80 \text{ mA}, T_{J} = 25^{\circ}\text{C}$ | 3.2           | 3.3  | 3.4           | V    |

|                               |                                                                                 | $V_{PVDD} \le 6 \text{ V}, 0 \text{ mA} \le I_{AVDD} \le 50 \text{ mA}, T_{J} = 25^{\circ}\text{C}$  | 3.13          | 3.3  | 3.46          | V    |

| V <sub>DVDD</sub>             | Digital regulator voltage                                                       | VREG = 3.3V                                                                                          | 1.4           | 1.55 | 1.65          | V    |

| \/                            |                                                                                 | $V_{PVDD} \ge 6 V, 0 mA \le I_{AVDD} \le 80 mA$                                                      | 3.2           | 3.3  | 3.4           | V    |

| V <sub>AVDD</sub>             | AVDD Analog regulator voltage                                                   | $V_{PVDD} \le 6 \text{ V}, 0 \text{ mA} \le I_{AVDD} \le 50 \text{ mA}$                              | 3.125         | 3.3  | 3.5           | V    |

| V <sub>GCTRL</sub>            | Gate control volatge                                                            | V <sub>PVDD</sub> > 4.5 V                                                                            | 4.9           | 5.7  | 6.5           | V    |

| GATE DRIVE                    | ERS (GHx, GLx, SHx, SLx)                                                        |                                                                                                      |               |      |               |      |

| V <sub>GSHx_LO</sub>          | High-side gate drive low level voltage                                          | I <sub>GHx</sub> = -100 mA; V <sub>GVDD</sub> = 12V; No FETs connected                               | 0.05          | 0.11 | 0.24          | V    |

| V <sub>GSHx_HI</sub>          | High-side gate drive high level voltage (V <sub>BSTx</sub> - V <sub>GHx</sub> ) | I <sub>GHx</sub> = 100 mA; V <sub>GVDD</sub> = 12V; No FETs connected                                | 0.28          | 0.44 | 0.82          | V    |

| V <sub>GSLx_LO</sub>          | Low-side gate drive low level voltage                                           | I <sub>GLx</sub> = -100 mA; V <sub>GVDD</sub> = 12V; No FETs connected                               | 0.05          | 0.11 | 0.27          | V    |

| V <sub>GSLx_HI</sub>          | Low-side gate drive high level voltage $(V_{GVDD} - V_{GLx})$                   | $I_{GLx}$ = 100 mA; $V_{GVDD}$ = 12V; No FETs connected                                              | 0.28          | 0.44 | 0.82          | V    |

| R <sub>DS(ON)_PU_</sub><br>HS | High-side pullup switch resistance                                              | I <sub>GHx</sub> = 100 mA; V <sub>GVDD</sub> = 12V                                                   | 2.7           | 4.5  | 8.4           | Ω    |

| R <sub>DS(ON)_PD_</sub><br>HS | High-side pulldown switch resistance                                            | I <sub>GHx</sub> = 100 mA; V <sub>GVDD</sub> = 12V                                                   | 0.5           | 1.1  | 2.4           | Ω    |

| R <sub>DS(ON)_PU_</sub><br>LS | Low-side pullup switch resistance                                               | I <sub>GLx</sub> = 100 mA; V <sub>GVDD</sub> = 12V                                                   | 2.7           | 4.5  | 8.3           | Ω    |

| R <sub>DS(ON)_PD_</sub><br>LS | Low-side pulldown switch resistance                                             | I <sub>GLx</sub> = 100 mA; V <sub>GVDD</sub> = 12V                                                   | 0.5           | 1.1  | 2.8           | Ω    |

| I <sub>DRIVEP_HS</sub>        | High-side peak source gate current                                              | V <sub>GSHx</sub> = 12V                                                                              | 550           | 1000 | 1575          | mA   |

| I <sub>DRIVEN_HS</sub>        | High-side peak sink gate current                                                | V <sub>GSHx</sub> = 0V                                                                               | 1150          | 2000 | 2675          | mA   |

| I <sub>DRIVEP_LS</sub>        | Low-side peak source gate current                                               | V <sub>GSLx</sub> = 12V                                                                              | 550           | 1000 | 1575          | mA   |

| I <sub>DRIVEN_LS</sub>        | Low-side peak sink gate current                                                 | V <sub>GSLx</sub> = 0V                                                                               | 1150          | 2000 | 2675          | mA   |

| R <sub>PD_LS</sub>            | Low-side passive pull down                                                      | GLx to LSS                                                                                           | 80            | 100  | 120           | kΩ   |

| R <sub>PDSA_HS</sub>          | High-side semiactive pull down                                                  | GHx to SHx, V <sub>GSHx</sub> = 2V                                                                   | 8             | 10   | 12.5          | kΩ   |

| BOOTSTRA                      | P DIODES                                                                        |                                                                                                      |               |      |               |      |

| VBOOTD                        | Bootstrap diode forward voltage                                                 | I <sub>BOOT</sub> = 100 μA                                                                           |               |      | 0.8           | V    |

| *BOOID                        | Doolstrap aload forward voltage                                                 | I <sub>BOOT</sub> = 100 mA                                                                           |               |      | 1.6           | V    |

| R <sub>BOOTD</sub>            | Bootstrap dynamic resistance $(\Delta V_{BOOTD} / \Delta I_{BOOT})$             | I <sub>BOOT</sub> = 100 mA and 50 mA                                                                 | 4.5           | 5.5  | 9             | Ω    |

| LOGIC-LEVI                    | EL INPUTS (BRAKE, DIR, EXT_CLK, SC                                              | L, SDA, SPEED/WAKE)                                                                                  |               |      |               |      |

| V <sub>IL</sub>               | Input logic low voltage                                                         | AVDD = 3 to 3.6 V                                                                                    |               |      | 0.25*AV<br>DD | V    |

| V <sub>IH</sub>               | Input logic high voltage                                                        | AVDD = 3 to 3.6 V                                                                                    | 0.65*AV<br>DD |      |               | V    |

| V <sub>HYS</sub>              | Input hysteresis                                                                |                                                                                                      | 50            | 500  | 800           | mV   |

| IIL                           | Input logic low current                                                         | AVDD = 3 to 3.6 V                                                                                    | -0.15         |      | 0.15          | μA   |

| I <sub>IH</sub>               | Input logic high current                                                        | AVDD = 3 to 3.6 V                                                                                    | -0.3          |      | 0.1           | μA   |

| R <sub>PD_SPEED</sub>         | Input pulldown resistance                                                       | SPEED/WAKE pin To GND                                                                                | 0.6           | 1    | 1.4           | MΩ   |

| LOGIC-LEV                     | EL INPUTS (DRVOFF)                                                              |                                                                                                      |               |      |               |      |

| V <sub>IL</sub>               | Input logic low voltage                                                         |                                                                                                      |               |      | 0.8           | V    |

| V <sub>IH</sub>               | Input logic high voltage                                                        |                                                                                                      | 2.2           |      |               | V    |

|                               | -                                                                               |                                                                                                      |               |      |               |      |

| $4.5 \text{ V} \le \text{V}_{\text{PVDD}} \le 60 \text{ V}, -40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 150^{\circ}\text{C}$ (unless otherwise noted | d). Typical limits apply for $T_A = 25^{\circ}C$ , $V_{PVDD} = 24 V$ |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

|                        | PARAMETER                 | TEST CONDITIONS         | MIN  | TYP | MAX  | UNIT |

|------------------------|---------------------------|-------------------------|------|-----|------|------|

| V <sub>HYS</sub>       | Input hysteresis          |                         | 200  | 400 | 650  | mV   |

| I <sub>IL</sub>        | Input logic low current   | Pin Voltage = 0 V;      | -1   | 0   | 1    | μA   |

| I <sub>IH</sub>        | Input logic high current  | Pin Voltage = 5 V;      | 7    | 20  | 35   | μA   |

| R <sub>PD_DRVOFF</sub> | Input pulldown resistance | DRVOFF To GND           | 100  | 200 | 300  | kΩ   |

| OPEN-DRAI              | N OUTPUTS (nFAULT, FG)    |                         |      |     |      |      |

| V <sub>OL</sub>        | Output logic low voltage  | I <sub>OD</sub> =-5 mA  |      |     | 0.4  | V    |

| I <sub>OZ</sub>        | Output logic high current | V <sub>OD</sub> = 3.3 V | 0    |     | 0.5  | μA   |

| SPEED INPU             | JT - ANALOG MODE          |                         |      |     |      |      |

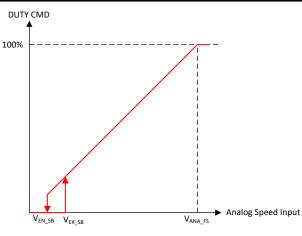

| V <sub>ANA_FS</sub>    | Analog full-speed voltage |                         | 2.95 | 3   | 3.05 | V    |

| V <sub>ANA_RES</sub>   | Analog voltage resolution |                         |      | 732 |      | μV   |

MCT8329A SLLSFQ3 – JANUARY 2023

|                               | PARAMETER                                               | TEST CONDITIONS                                                                                                                                                                                                                | MIN  | TYP  | MAX   | UNIT |

|-------------------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------|

| SPEED INP                     | JT - PWM MODE                                           | · · · · · ·                                                                                                                                                                                                                    |      |      | I     |      |

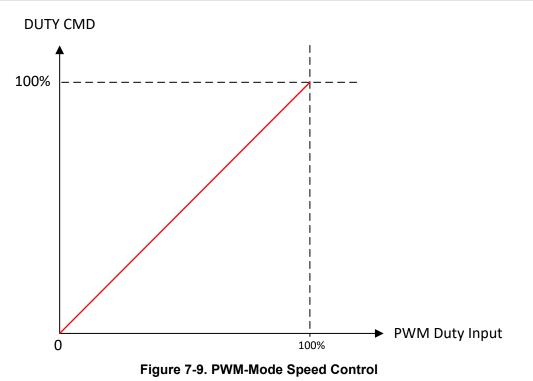

| f <sub>PWM</sub>              | PWM input frequency                                     |                                                                                                                                                                                                                                | 0.01 |      | 95    | kHz  |

|                               |                                                         | f <sub>PWM</sub> = 0.01 to 0.35 kHz                                                                                                                                                                                            | 11   | 12   | 13    | bits |

|                               |                                                         | f <sub>PWM</sub> = 0.35 to 2 kHz                                                                                                                                                                                               | 12   | 13   | 14    | bits |

|                               |                                                         | f <sub>PWM</sub> = 2 to 3.5 kHz                                                                                                                                                                                                | 11   | 11.5 | 12    | bits |

| Dee                           | DW/M input recelution                                   | f <sub>PWM</sub> = 3.5 to 7 kHz                                                                                                                                                                                                | 13   | 13.5 | 14    | bits |

| Res <sub>PWM</sub>            | PWM input resolution                                    | f <sub>PWM</sub> = 7 to 14 kHz                                                                                                                                                                                                 | 12   | 12.5 | 13    | bits |

|                               |                                                         | f <sub>PWM</sub> = 14 to 29.2 kHz                                                                                                                                                                                              | 11   | 11.5 | 12    | bits |

|                               |                                                         | f <sub>PWM</sub> = 29.3 to 60 kHz                                                                                                                                                                                              | 10   | 10.5 | 11    | bits |

|                               |                                                         | f <sub>PWM</sub> = 60 to 95 kHz                                                                                                                                                                                                | 8    | 9    | 10    | bits |

| SPEED INP                     | JT - FREQUENCY MODE                                     |                                                                                                                                                                                                                                |      |      |       |      |

| fpwm_freq                     | PWM input frequency range                               | Duty cycle = 50%                                                                                                                                                                                                               | 3    |      | 32767 | Hz   |

| SLEEP MOD                     | DE                                                      | · · · · ·                                                                                                                                                                                                                      |      |      |       |      |

| V <sub>EN_SL</sub>            | Analog voltage to enter sleep mode                      | SPD_CTRL_MODE = 00b (analog mode)                                                                                                                                                                                              |      |      | 40    | mV   |

| V <sub>EX_SL</sub>            | Analog voltage to exit sleep mode                       |                                                                                                                                                                                                                                | 2.6  |      |       | V    |

| t <sub>DET_ANA</sub>          | Time needed to detect wake up signal on SPEED/WAKE pin  | SPD_CTRL_MODE = 00b (analog<br>mode), V <sub>SPEED/WAKE</sub> > V <sub>EX_SL</sub>                                                                                                                                             | 0.5  | 1    | 1.5   | μs   |

| t <sub>WAKE</sub>             | Wakeup time from sleep mode                             | V <sub>SPEED/WAKE</sub> > V <sub>EX_SL</sub> to DVDD voltage<br>available, SPD_CTRL_MODE = 00b<br>(analog mode)                                                                                                                |      | 3    | 5     | ms   |

| <sup>t</sup> ex_sl_dr_a<br>Na | Time taken to drive motor after exiting from sleep mode | $\label{eq:spd_ctrl_MODE} \begin{split} & \text{SPD\_CTRL\_MODE} = 00b \text{ (analog} \\ & \text{mode)} \\ & \text{V}_{\text{SPEED/WAKE}} > \text{V}_{\text{EX\_SL}} \text{, ISD detection} \\ & \text{disabled} \end{split}$ |      |      | 30    | ms   |

| DET_PWM                       | Time needed to detect wake up signal on SPEED pin       | SPD_CTRL_MODE = 01b (PWM<br>mode) or 11b (Frequency mode),<br>V <sub>SPEED/WAKE</sub> > V <sub>IH</sub>                                                                                                                        | 0.5  | 1    | 1.5   | μs   |

| WAKE_PWM                      | Wakeup time from sleep mode                             | V <sub>SPEED/WAKE</sub> > V <sub>IH</sub> to DVDD<br>voltage available and release nFault,<br>SPD_CTRL_MODE = 01b (PWM mode)<br>or 11b (Frequency mode)                                                                        |      | 3    | 5     | ms   |

| EX_SL_DR_P                    | Time taken to drive motor after wakeup from sleep state | SPD_CTRL_MODE = 01b (PWM mode)<br>V <sub>SPEED/WAKE</sub> > V <sub>IH</sub> , ISD detection<br>disabled                                                                                                                        |      |      | 30    | ms   |

| DET_SL_ANA                    | Time needed to detect sleep command                     | SPD_CTRL_MODE = 00b (analog<br>mode)<br>V <sub>SPEED/WAKE</sub> < V <sub>EN_SL</sub> , SLEEP_TIME =<br>00b or 01b                                                                                                              | 0.5  | 1    | 2     | ms   |

|                         | PARAMETER                                                       | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | MIN   | TYP  | MAX   | UNIT |

|-------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| t <sub>det_sl_pwm</sub> |                                                                 | $\begin{array}{l} SPD\_CTRL\_MODE = 01b \ (PWM \ mode) \\ or \ 11b \ (Frequency \ mode), \ V_{SPEED/} \\ _{WAKE} < V_{IL} (PWM \ mode \ and \ Frequency \\ mode), \ SLEEP\_TIME = 00b \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.035 | 0.05 | 0.065 | ms   |

|                         |                                                                 | $\label{eq:spectral_mode} \begin{split} & \text{SPD\_CTRL\_MODE} = 01b \ (\text{PWM} \\ & \text{mode}), \ \text{or} \ 11b \ (\text{Frequency} \\ & \text{mode}), \ V_{\text{SPEEDWAKE}} < V_{\text{IL}} (\text{PWM} \ \text{mode} \\ & \text{and} \ \text{Frequency} \ \text{mode}), \ \text{SLEEP\_TIME} = \\ & 01b \end{split}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0.14  | 0.2  | 0.26  | ms   |

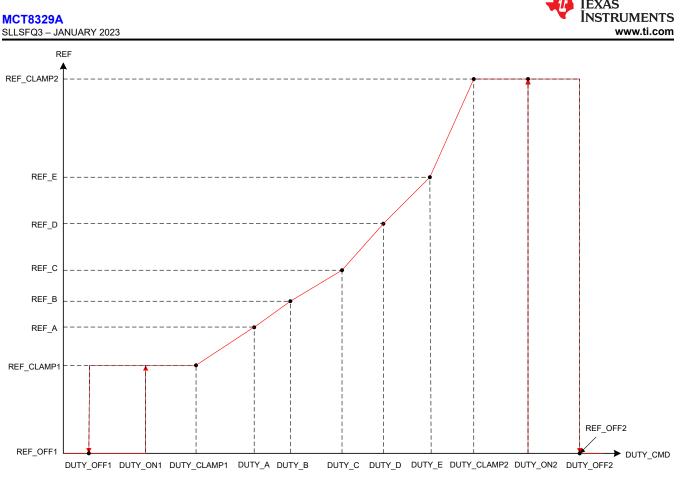

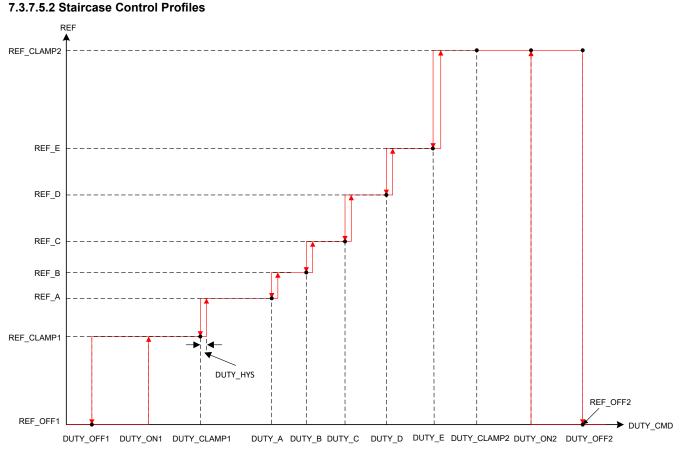

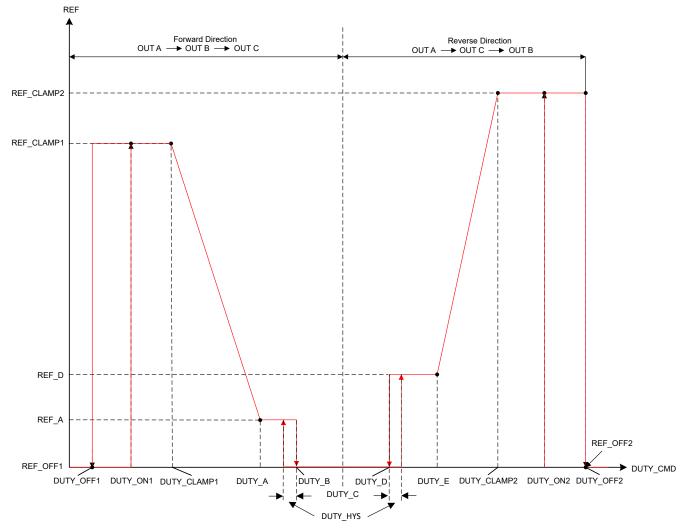

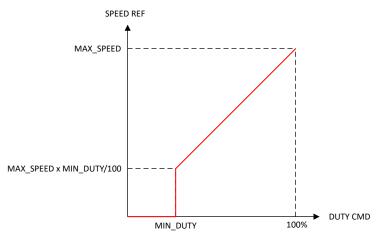

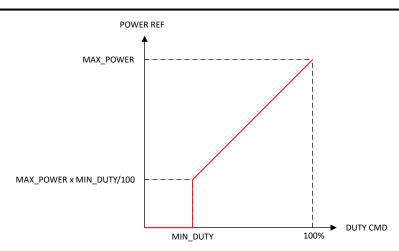

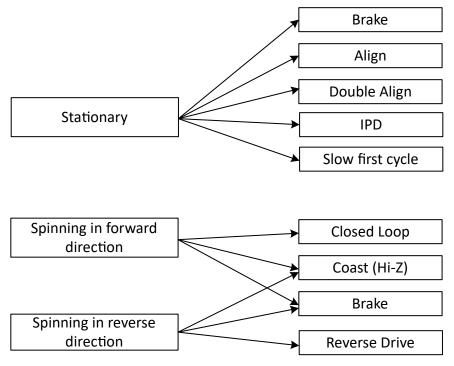

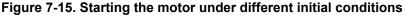

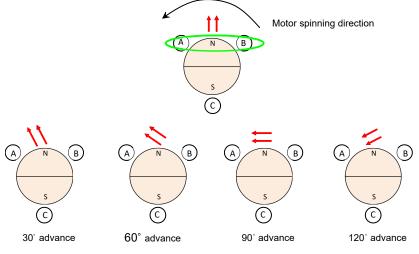

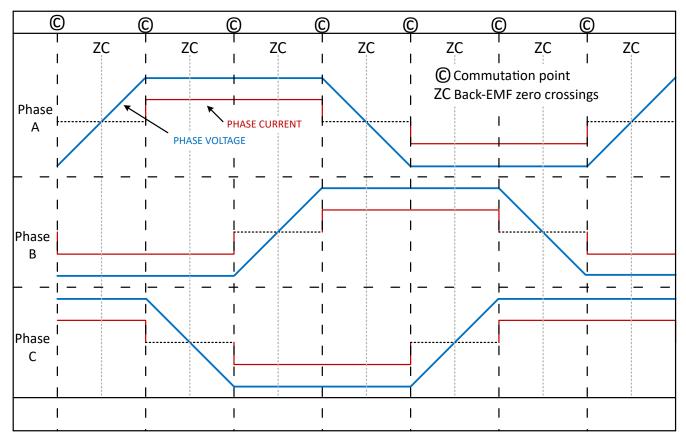

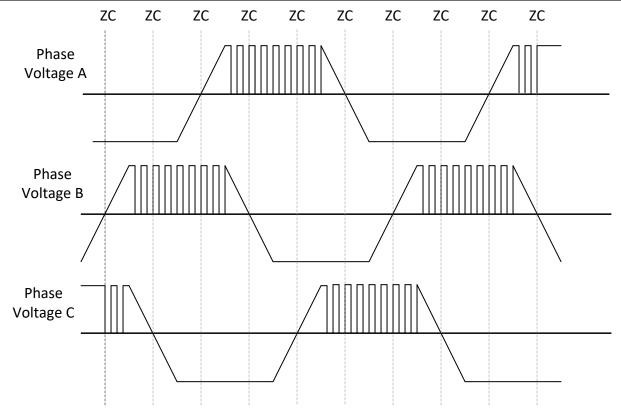

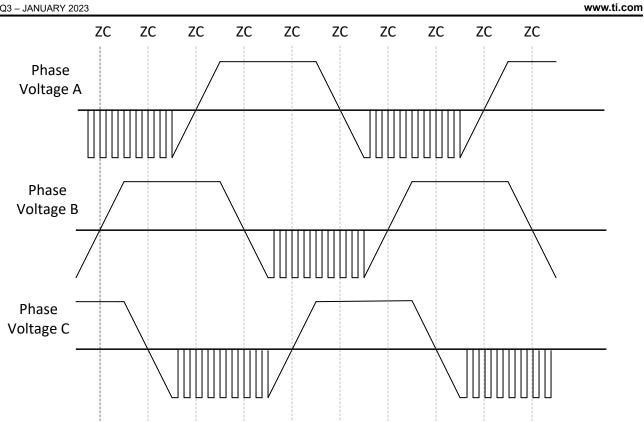

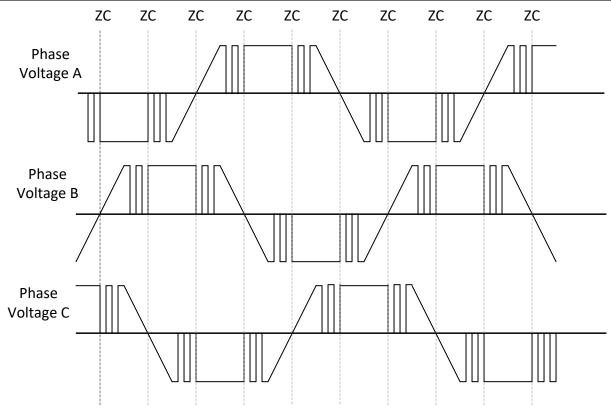

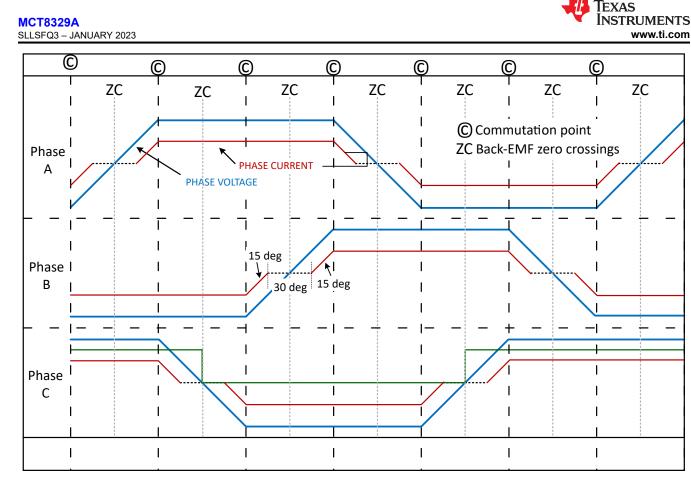

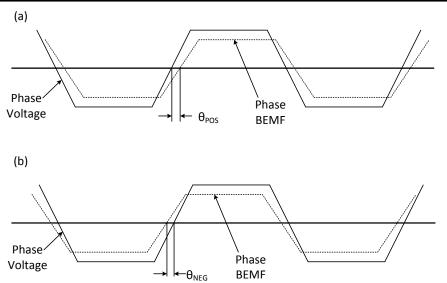

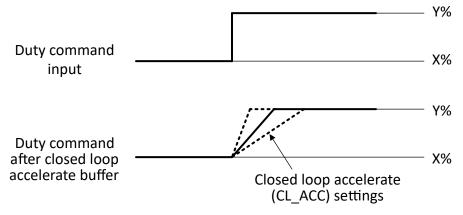

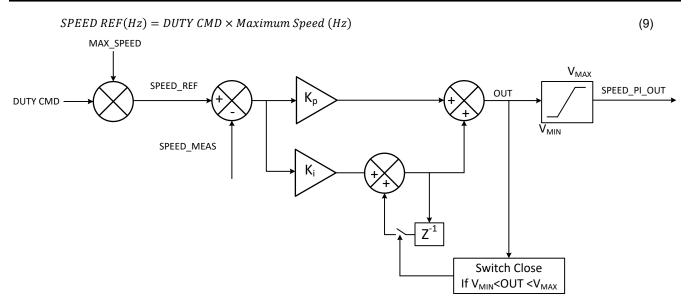

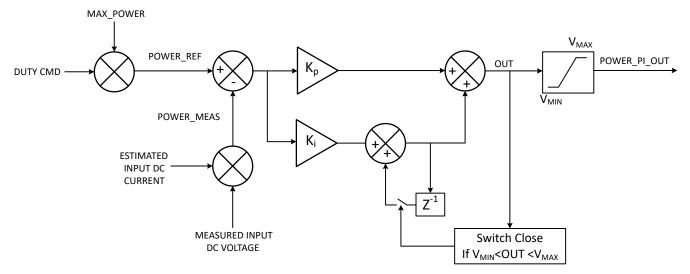

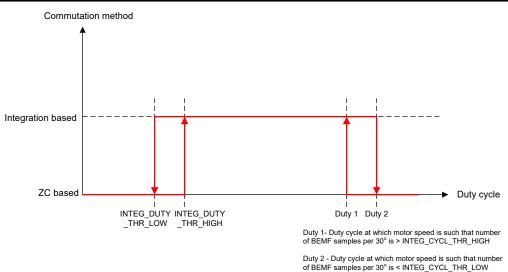

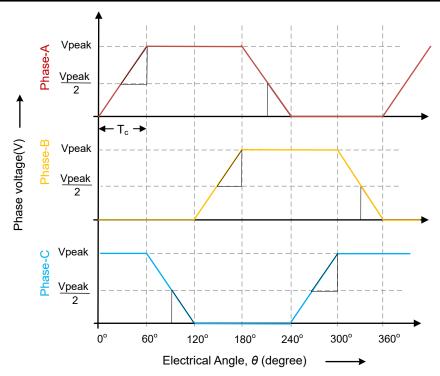

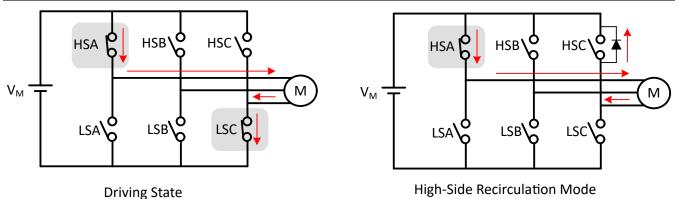

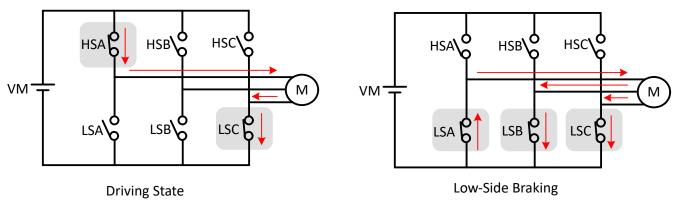

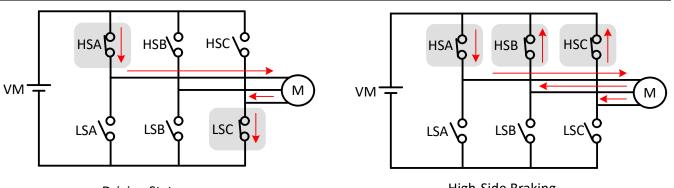

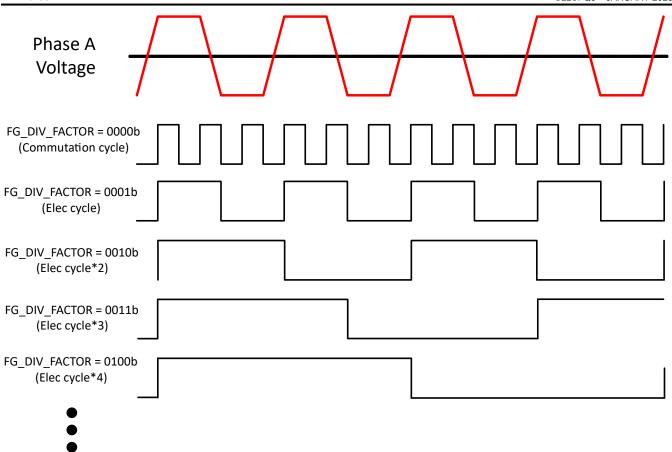

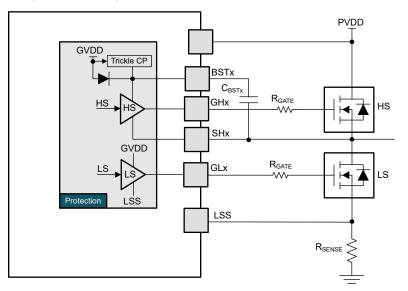

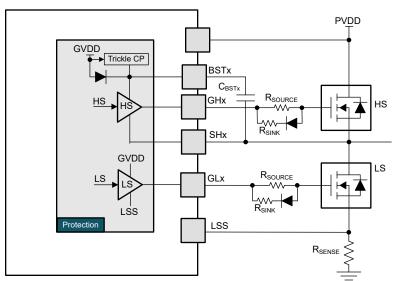

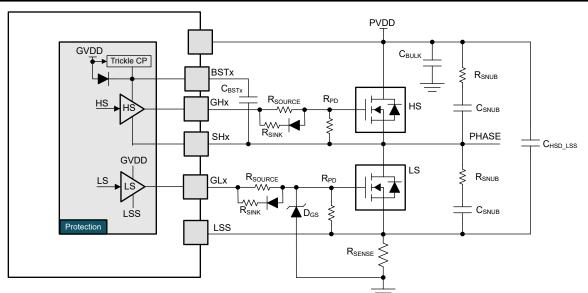

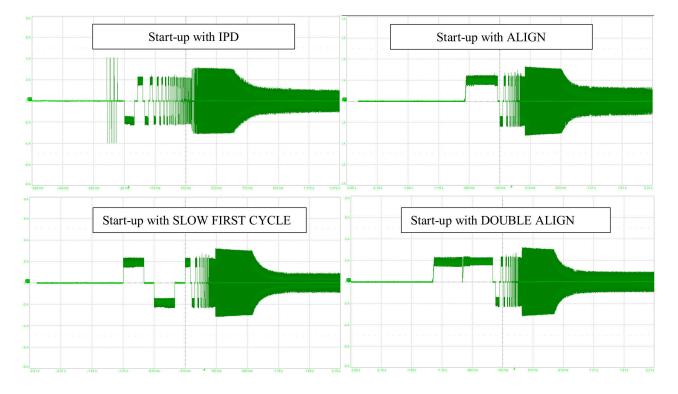

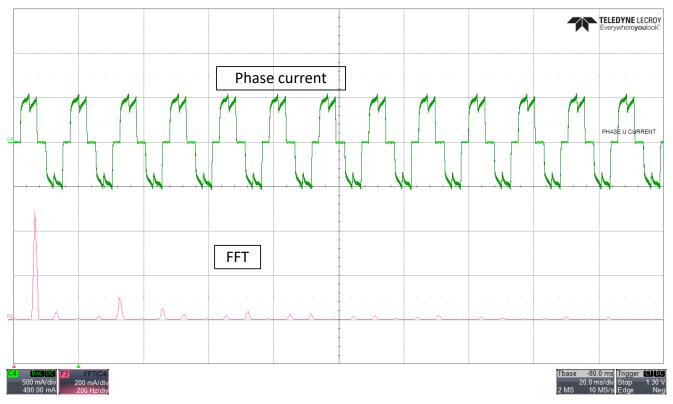

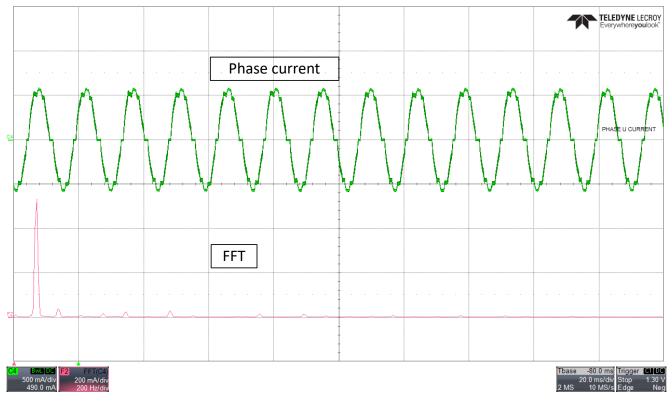

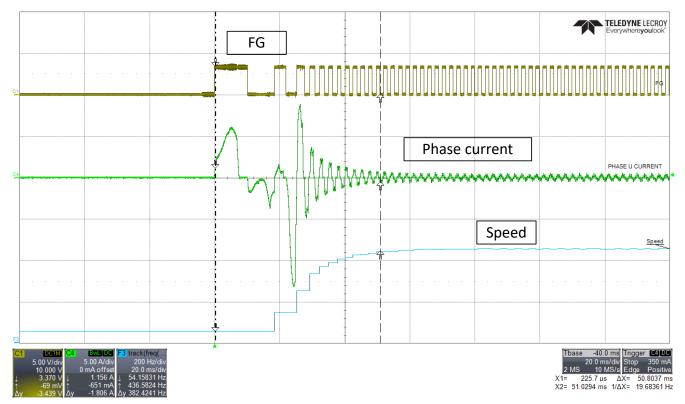

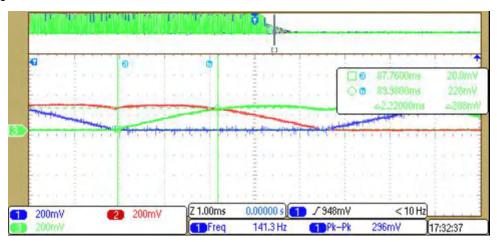

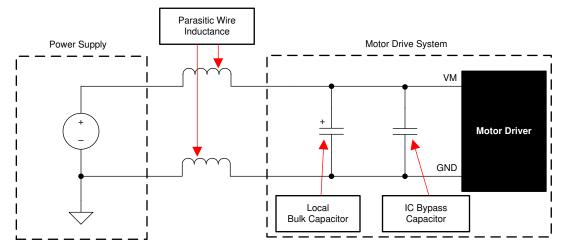

|                         | Time needed to detect sleep command                             | $eq:spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_spectral_$ | 14    | 20   | 26    | ms   |