# Dual Channel x1 PCle Redriver/Equalizer

Check for Samples: SN65LVPE501

### **FEATURES**

- Single Lane PCle Equalizer/Redriver

- Support for Both PCle Gen I (2.5Gbps) and Gen II (5.0 Gbps) Speed

- Selectable Equalization, De-emphasis and Output Swing Control

- Integrated Termination

- Hot-Plug Capable

- Receiver Detect

- Low Power:

- 330mW(TYP),  $V_{CC} = 3.3V$

- Auto Low Power Modes:

- 5mW (TYP) When no Connection Detected

- 70mW (TYP) When in Auto-Low Power Mode

- Excellent Jitter and Loss Compensation Capability:

- 30" of 6 mil Stripline on FR4

- Small Foot Print 24 Pin 4 x 4 QFN Package

- High Protection Against ESD Transient

HBM: 3,000 VCDM: 1,500 VMM: 200 V

#### **APPLICATIONS**

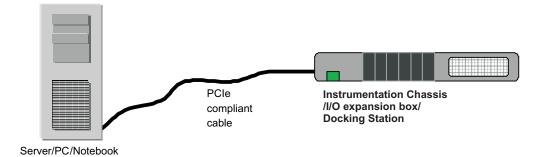

PC MB, Docking Stations, Backplane and Cabled Application

# **DESCRIPTION**

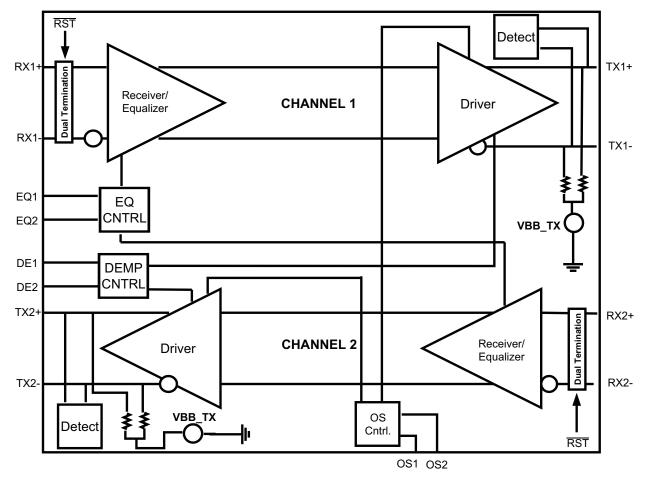

The SN65LVPE501 is a dual channel, single lane PCIe redriver and signal conditioner supporting data rates of up to 5.0Gbps. The device complies with PCIe spec revision 2.1.

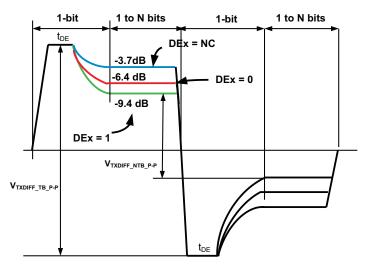

### Programmable EQ, De-Emphasis and Amplitude Swing

The SN65LVPE501 is designed to minimize the signal degradation effects such as crosstalk and inter-symbol interference (ISI) that limits the interconnect distance between two devices. The input stage of each channel offers selectable equalization settings that can be programmed to match loss in the channel. The differential outputs provide selectable de-emphasis to compensate for the anticipated distortion PCIe signal will experience. Level of de-emphasis will depend on the length of interconnect and its characteristics. Both equalization and de-emphasis levels are controlled by the setting of signal control pins EQ1, EQ2 and DE1, DE2.

To provide additional control of signal integrity in extended backplane applications LVPE501 provides independent output amplitude control for each channel. See Table 2 for setting details.

#### **Device PowerOn**

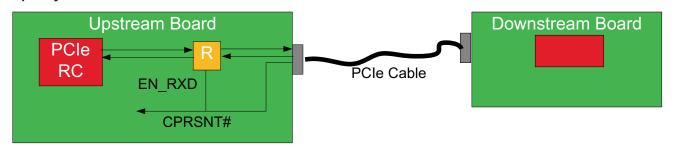

Device initiates internal power-on reset after  $V_{CC}$  has stabilized. External reset can also be applied at anytime by toggling RST pin. External reset is recommended after every device power-up. When RST is driven high, the device samples the state of EN\_RXD, if it is set H device enters Rx.Detect state where each channel will perform Rx.Detect function (as described in PCle spec). If EN\_RXD is set L, automatic RX detect function is disabled and both channels are enabled with their termination set to  $Z_{DC\_RX}$ .

#### **Receiver Detection**

While EN\_RXD pin is H and device is not in sleep mode ( $\overline{RST}$  is H), SN65LVPE501 performs RX.Detect on both channels indefinitely until remote termination is detected on both channels. Automatic Rx detection feature can be forced off by driving EN\_RXD low. In this state both channels input termination are set to  $Z_{DC_RX}$ .

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### **DESCRIPTION CONTINUED**

#### Sleep (Shut\_Down) Mode

This is low power state triggered by  $\overline{RST}$  = L. In sleep mode receiver termination resistor for each of the two channels is switched to  $Z_{RX-HIGH\_IMP}$  of >50 K $\Omega$  and transmitters are pulled to Hi-Z state. Device power is reduced to <1mW (TYP). To get device out of sleep mode  $\overline{RST}$  is toggled L-H.

### **Electrical Idle Support**

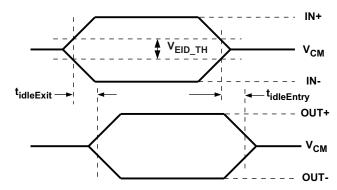

A link is in an electrical idle state when the TX $\pm$  voltage is held at a steady constant value like the common mode voltage. SN65LVPE501 detects an electrical idle state when RX $\pm$  input voltage of the associated channel falls below  $V_{EID\_TH}$  min. After detection of an electrical idle state in a given channel the device asserts electrical idle state in its corresponding TX. When RX $\pm$  voltage exceeds  $V_{EID\_TH}$  max, normal device operation is restored and output starts passing input signal. Electrical idle exit and entry time is specified at  $\leq$ 6ns.

Electrical idle support is independent for each channel.

#### **Power Save Features**

The device supports three power save modes as described below.

1. Sleep (Shut Down) Mode

This mode can be enabled from any state (Rx detect or active) by driving  $\overline{RST}$  L. In this state both channels have their termination set to  $Z_{RX-HIGH\ IMP+}$  and outputs are at Hi-Z. Device power is 1mW (MAX)

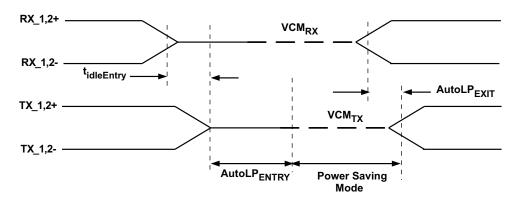

2. Auto Low Power Mode

This mode is enabled when PS pin is tied H and device is in active mode. In this mode anytime  $Vin_{diff\_pp}$  falls below selected  $V_{EID\_TH}$  for a *given channel* and stays below  $V_{EID\_TH}$  for >1µs (TYP), the associated CH will enter auto low power (ALP) mode where power/CH will be reduced to <1/3<sup>rd</sup> of normal operating power/CH or about 70mW under typical voltage of 3.3V when ALP conditions are met for both channels. A CH will exit ALP mode whenever  $Vin_{diff\_pp}$  exceeds max  $V_{EID\_TH}$  for that channel. Exit latency is 30ns max. To use this mode link latency will need to account for the ALP exit time for N\_FTS. ALP mode is handled by each channel independently based on its input differential signal level. This mode can be disabled by leaving PS as NC or tying PS to GND via  $4.7k\Omega$ .

3. Cable Disconnect Mode

This mode is activated when  $\overline{RST}$  is H,  $EN_RXD = H$ , and no termination is detected by either channel. Device is in the Rx.Detect state whereby it is continuously performing Rx.Detect on both channels. In this state total power consumed by device is typically <3% of normal active power. Or <10mW (MAX).

#### **Beacon Support**

With its broadband design, the SN65LVPE501 supports low frequency Beacon signal (as defined by PCIe 2.1 spec) used to indicate wake-up event to the system by a downstream device when in L2 power state. All requirements for a beacon signal as specified in PCI Express specification 2.1 must be met for device to pass beacon signals.

#### **Devic Power**

The SN65LVPE501 is designed to operate from a single 3.3V supply. Always practice proper supply sequencing procedure. Apply  $V_{CC}$  first before any input control pin signals are applied to the device. Power-down sequence is in reverse order.

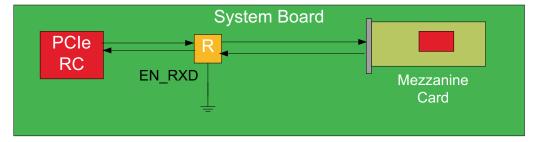

Figure 1. SN65LVPE501 Typical Applications

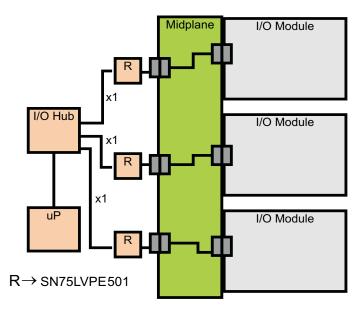

Figure 2. Data Flow Block Diagram

# **Split System**

# **Enclosed System**

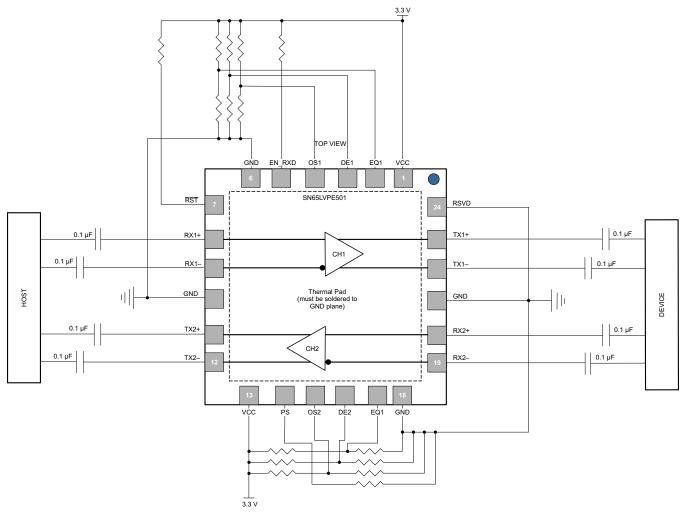

Figure 3. Typical Implementation

# **Table 1. Pin Description**

| P                    | IN                      |             |                                                                                                    |  |  |  |  |  |

|----------------------|-------------------------|-------------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NUMBER NAME I/O TYPE |                         |             | DESCRIPTION                                                                                        |  |  |  |  |  |

| HIGH SPEED           | DIFFERENTI              | AL I/O PINS |                                                                                                    |  |  |  |  |  |

| 8                    | RX1+                    | I, CML      |                                                                                                    |  |  |  |  |  |

| 9                    | RX1-                    | I, CML      | Non-inverting and inverting CML differential input for CH 1 and CH 2. These pins are tied to an    |  |  |  |  |  |

| 20                   | RX2+                    | I, CML      | internal voltage bias by dual termination resistor circuit.                                        |  |  |  |  |  |

| 19                   | RX2-                    | I, CML      |                                                                                                    |  |  |  |  |  |

| 23                   | TX1+                    | O, CML      |                                                                                                    |  |  |  |  |  |

| 22                   | TX1-                    | O, CML      | Non-inverting and inverting CML differential output for CH 1 and CH 2. These pins are              |  |  |  |  |  |

| 11                   | TX2+                    | O, CML      | internally tied to voltage bias by termination resistors.                                          |  |  |  |  |  |

| 12                   | TX2-                    |             |                                                                                                    |  |  |  |  |  |

| DEVICE CON           | TROL PIN <sup>(1)</sup> | <u> </u>    |                                                                                                    |  |  |  |  |  |

| 5                    | EN_RXD                  | I, LVCMOS   | Sets device operation modes per Table 2. Internally pulled to VCC                                  |  |  |  |  |  |

| 14                   | PS                      | I, LVCMOS   | Select auto-low power save mode per Table 2. Internally pulled to GND                              |  |  |  |  |  |

| 7                    | RST                     | I, LVCMOS   | Reset device, input active Low. Internally pulled to VCC                                           |  |  |  |  |  |

| 24                   | RSVD                    | I, LVCMOS   | Reserved for factory test. Must be connected to GND                                                |  |  |  |  |  |

| SIGNAL CON           | TROL PINS <sup>(2</sup> | 2)          |                                                                                                    |  |  |  |  |  |

| 3,16                 | DE1, DE2                | I, LVCMOS   | Selects de-emphasis settings for CH 1 and CH 2 per Table 2. Internally tied to V <sub>CC</sub> /2  |  |  |  |  |  |

| 2,17                 | EQ1, EQ2                | I, LVCMOS   | Selects equalization settings for CH 1 and CH 2 per Table 2. Internally tied to V <sub>CC</sub> /2 |  |  |  |  |  |

| 4, 15                | OS1, OS2                | I, LVCMOS   | Selects output amplitude for CH 1 and CH 2 per Table 2. Internally tied to V <sub>CC</sub> /2      |  |  |  |  |  |

| POWER PINS           | 3                       | •           |                                                                                                    |  |  |  |  |  |

| 1,13                 | VCC                     | Power       | Positive supply should be 3.3V ± 10%                                                               |  |  |  |  |  |

| 6,10,18,21           | GND                     | Power       | Supply ground                                                                                      |  |  |  |  |  |

When not used can be left as NC or connected to  $V_{CC}/GND$  via  $4.7k\Omega$  resistor. Internally biased to  $V_{CC}/2$  with >200k $\Omega$  pullup/pulldown. When 3-state pins are left as NC board leakage at the pin pad must be <1  $\mu$ A otherwise drive to  $V_{CC}/2$  to assert mid-level state.

**Table 2. Signal Control Pin Setting**

| 0                  | Sx                      | TRANSITION BIT AMPLITUDE (TYP mVpp)                                |                               |  |  |  |

|--------------------|-------------------------|--------------------------------------------------------------------|-------------------------------|--|--|--|

| N                  | IC                      | 1000                                                               |                               |  |  |  |

|                    | 0                       | 87                                                                 | 75                            |  |  |  |

|                    | 1                       | 11                                                                 | 00                            |  |  |  |

| DEx <sup>(1)</sup> | OSx <sup>(1)</sup> = NC | $OSx^{(1)} = 0$                                                    | OSx <sup>(1)</sup> = 1        |  |  |  |

| NC                 | −3.7 dB                 | -2.5 dB                                                            | -4.6 dB                       |  |  |  |

| 0                  | -6.4 dB                 | -5.5 dB                                                            | -6.6 dB                       |  |  |  |

| 1                  | -9.4 dB                 | -9.5 dB                                                            | -8.7 dB                       |  |  |  |

| EQ                 | x <sup>(1)</sup>        |                                                                    | ATION dB<br>I Speed)          |  |  |  |

| N                  | IC                      | (                                                                  | )                             |  |  |  |

| (                  | 0                       | 7                                                                  |                               |  |  |  |

|                    | 1                       | 15                                                                 |                               |  |  |  |

| EN_                | RXD                     | DEVICE FUNCTION                                                    |                               |  |  |  |

|                    | 0                       | Set input termination to Z <sub>DC_RX</sub> and disable Rx. Detect |                               |  |  |  |

|                    | 1                       | Perform Rx.Detect ( <b>default</b> , internally pulled to Vcc)     |                               |  |  |  |

| R                  | ST                      | DEVICE FUNCTION                                                    |                               |  |  |  |

| -                  | 0                       |                                                                    | scent state and<br>et to Hi-Z |  |  |  |

|                    | 1                       | Device not in shut_down mode (default, internally pulled to Vcc)   |                               |  |  |  |

| P                  | 'S                      | DEVICE F                                                           | UNCTION                       |  |  |  |

|                    | 0                       | Auto-low power mode disabled (default, internally pulled to GND    |                               |  |  |  |

|                    | 1                       | Auto-low power                                                     | r mode enabled                |  |  |  |

<sup>(1)</sup> Applies to Channel 1 and Channel 2 at 2.5 GHz.

- (1) This is a reference example and it is not intended to represent the best configuration; every designer should select the EQ and DE settings that better fits the system needs. All DEx, EQx and OSx pins default to NC.

- (2) The recommended value for all the resistors shown in the Figure is 4.9K  $\Omega$ .

- (3) For terminals OSx, DEx, and EQx, populate only pull-up or only pull-down according to the desired setting.

Figure 4. Reference Device Implementation

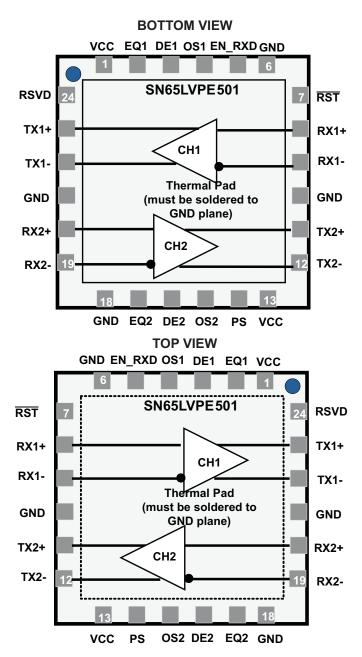

Figure 5. Flow-Through Pin-Out

### ORDERING INFORMATION(1)

| PART NUMBER     | PART MARKING | PCAKAGE                 |

|-----------------|--------------|-------------------------|

| SN65LVPE501RGER | LVPE501      | 24-pin RGE Reel (large) |

| SN65LVPE501RGET | LVPE501      | 24-pin RGE Reel (small) |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)(1)

|                              |                                                    | UNIT / VALUES                   |

|------------------------------|----------------------------------------------------|---------------------------------|

| Supply Voltage Range (2)     | V <sub>CC</sub>                                    | –0.5 V to 4 V                   |

| Voltage Range                | Differential I/O                                   | -0.5V to 4 V                    |

|                              | Control I/O                                        | -0.5 V to V <sub>CC</sub> + 0.5 |

|                              | (Human Body Model) QSS 009-105 (JESD22-A114B)      | ±3000 V                         |

| Electrostatic Discharge      | (Charged Device Model) QSS 009-147 (JESD22-C101-A) | ±1500 V                         |

|                              | (Machine Model) JESD22-A115-A                      | ±200 V                          |

| Continuous power dissipation | on                                                 | See Thermal Information Table   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### THERMAL INFORMATION

|                           |                                                  | SN65LVPE501 |       |

|---------------------------|--------------------------------------------------|-------------|-------|

|                           | THERMAL METRIC <sup>(1)</sup>                    | RGE         | UNITS |

|                           |                                                  | 24 PINS     |       |

| $\theta_{JA}$             | Junction-to-ambient thermal resistance (2)       | 46          |       |

| $\theta_{\text{JC(TOP)}}$ | Junction-to-case(top) thermal resistance (3)     | 42          |       |

| $\theta_{JB}$             | Junction-to-board thermal resistance (4)         | 13          | 2000  |

| Ψлт                       | Junction-to-top characterization parameter (5)   | 0.5         | °C/W  |

| ΨЈВ                       | Junction-to-board characterization parameter (6) | 9           |       |

| θ <sub>JC(BOTTOM)</sub>   | Junction-to-case(bottom) thermal resistance (7)  | 4           |       |

- (1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

- (2) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

- (3) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC-standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

- (4) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

- (5) The junction-to-top characterization parameter, ψ<sub>JT</sub>, estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining θ<sub>JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

- (6) The junction-to-board characterization parameter, ψ<sub>JB</sub>, estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining θ<sub>JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

- (7) The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

Copyright © 2010–2012, Texas Instruments Incorporated

Submit Documentation Feedback

<sup>(2)</sup> All voltage values, except differential voltages, are with respect to network ground terminal.

## **RECOMMENDED OPERATING CONDITIONS**

over operating free-air temperature range (unless otherwise noted)

|                       |                                | MIN | TYP | MAX | UNIT |

|-----------------------|--------------------------------|-----|-----|-----|------|

| V <sub>CC</sub>       | Supply Voltage                 | 3   | 3.3 | 3.6 | V    |

| C <sub>COUPLING</sub> | AC Coupling Capacitor          | 75  |     | 200 | nF   |

|                       | Operating free-air temperature | -40 |     | 85  | °C   |

## **ELECTRICAL CHARACTERISTICS**

over operating free-air temperature range (unless otherwise noted)

| •                         | g free-air temperature range (  PARAMETER |                                                               | T CONDITIONS                            | MIN    | TYP | MAX      | UNIT  |

|---------------------------|-------------------------------------------|---------------------------------------------------------------|-----------------------------------------|--------|-----|----------|-------|

| DEVICE BARA               |                                           |                                                               |                                         | IVIIIV | IIF | IVIAA    | UNII  |

| DEVICE PARAI              | METERS (under recommended opera           |                                                               | •                                       |        |     | ı        |       |

| I <sub>CC</sub>           |                                           | RST, DEx, EQx, OSx = NC, E<br>$V_{ID} = 1000 \text{mV}_{p-p}$ |                                         | 101    | 120 |          |       |

| ICC <sub>idle</sub>       | Supply Current                            | urrent PS=1; When auto-low power conditions are met           |                                         |        |     |          |       |

| ICC <sub>shut-down</sub>  |                                           | RST = GND                                                     |                                         |        | 0.2 | 1        |       |

| ICC <sub>RX.Detect</sub>  |                                           | $\overline{RST}$ , EN_RXD = NC                                |                                         |        | 2   |          | l     |

|                           | Maximum Data Rate                         |                                                               |                                         |        |     | 5        | Gbps  |

| AutoLP <sub>ENTRY</sub>   | Auto Low Power Entry Time                 | Electrical Idle at Input, Refer t                             | o Figure 9                              | 1.0    | 1.3 |          | μs    |

| AutoLP <sub>EXIT</sub>    | Auto Low Power Exit Time                  | After first signal activity, Refer                            | to Figure 9                             |        | 15  | 30       | ns    |

| t <sub>PU</sub>           | Power Up Time                             | Rx Detect Start Event, Vcc = RST, EN_RXD = H                  | Stable                                  |        | 15  | 30       | μs    |

| t <sub>DIS</sub>          | Sleep (shut-down) Mode Entry<br>Time      | RST H→L; EN_RXD=X                                             |                                         |        |     | 1        | μs    |

| T <sub>ENB</sub>          | Sleep (shut-down) Mode Exit Time          | RST L→H; EN_RXD=H, Start                                      | of Ex detect event                      |        |     | 10       | μs    |

| CONTROL LO                | GIC (under recommended operating of       | conditions, unless otherwise                                  | noted)                                  |        |     |          |       |

| V <sub>IH</sub>           | High level Input Voltage                  |                                                               |                                         | 1.4    |     | $V_{CC}$ | V     |

| V <sub>IL</sub>           | Low Level Input Voltage                   |                                                               |                                         | -0.3   |     | 0.5      | ٧     |

| V <sub>HYS</sub>          | Input Hysteresis                          |                                                               |                                         | 150    |     | mV       |       |

|                           | High Level Innut Current                  | OSx, EQx, DEx = V <sub>CC</sub>                               |                                         |        | 30  |          |       |

| I <sub>IH</sub>           | High Level Input Current                  | $EN_RXD$ , $\overline{RST} = V_{CC}$                          |                                         |        | 1   | μA       |       |

|                           |                                           | OSx, EQx, DEx = GND                                           |                                         |        |     |          |       |

| $I_{\rm IL}$              | Low Level Input Current                   | PS = GND                                                      | -1                                      |        |     | μΑ       |       |

|                           |                                           | $EN_RXD$ , $\overline{RST} = GND$                             | -20                                     |        |     |          |       |

| RECEIVER AC               | /DC (under recommended operating          | conditions, unless otherwise                                  | noted)                                  |        |     |          |       |

| Vin <sub>diff pp</sub>    | RX1, RX2 Input Voltage Swing              | AC coupled differential signal                                |                                         | 100    |     | 1200     | mVp-p |

| V <sub>CM_RX</sub>        | RX1, RX2 Common Mode Voltage              |                                                               |                                         | 0      |     | 3.6      | ٧     |

| Vin <sub>COM_P</sub>      | RX1, RX2 AC Peak common mode voltage      |                                                               |                                         |        |     | 150      | mVP   |

| Z <sub>DC_RX</sub>        | DC single ended impedance                 |                                                               |                                         | 40     | 50  | 60       | Ω     |

| Z <sub>diff_RX</sub>      | DC Differential Input impedance           |                                                               |                                         | 80     | 100 | 120      | Ω     |

| Z <sub>RX_High_IMP+</sub> | DC Input High Impedance                   | Device in sleep mode Rx term respect to GND over 200mV r      | nination not powered; Measured with max | 50     | 74  |          | kΩ    |

| V <sub>EID_TH</sub>       | Electrical Idle Detect Threshold          | Measured at receiver pin (see                                 | Figure 7)                               | 65     | 84  | 175      | mVpp  |

|                           |                                           | 50 MHz – 1.25 GHz                                             |                                         | 10     |     |          | dB    |

| RL <sub>RX-DIFF</sub>     | Differential Return Loss                  | 4.05.011 0.5.011                                              | Operating temperature 0°C to 85°C       | 8      |     |          | i     |

|                           |                                           | 1.25 GHz – 2.5 GHz                                            | Operating temperature –40°C to 85°C     | 7      |     |          | dB    |

| RL <sub>RX-CM</sub>       | Common Mode Return Loss                   | 50 MHz – 2.5 GHz                                              | +                                       | 10     |     |          | dB    |

Submit Documentation Feedback

Copyright © 2010–2012, Texas Instruments Incorporated

# **ELECTRICAL CHARACTERISTICS (continued)**

|                                              | free-air temperature range ( PARAMETER                     |                                                                     | ST CONDITIONS                                 | MINI | TVD  | MAY  | UNIT  |

|----------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------|------|------|------|-------|

| TD 4 NO                                      |                                                            |                                                                     |                                               | MIN  | TYP  | MAX  | UNII  |

| TRANSMITTER A                                | AC/DC (under recommended opera                             | 1                                                                   | •                                             |      |      |      |       |

|                                              |                                                            | $R_L = 100\Omega \pm 1\%$ , DEx, OS = 1                             | 800                                           | 1000 | 1200 |      |       |

| $V_{TXDIFF\_PP}$                             |                                                            | $R_L = 100\Omega \pm 1\%$ , DEx = NC, 0                             |                                               |      | 875  |      | mV    |

|                                              |                                                            | $R_L = 100\Omega \pm 1\%$ , DEx = NC, 0                             | OSx = VCC Transition Bit                      |      | 1100 |      |       |

|                                              | Differential peak-to-peak Output Voltage                   | $R_L$ =100 $\Omega$ ±1%, DEx=NC, O<br>Non-Transition Bit            | Sx = 0,1,NC                                   |      | 655  |      |       |

| V <sub>TXDIFF_NTB_PP</sub>                   |                                                            | $R_L$ =100 $\Omega$ ±1%, DEx=0,OSx<br>Non-Transition Bit            | = 0,1,NC                                      |      | 495  |      | mV    |

|                                              |                                                            | R <sub>L</sub> =100Ω ±1%, DEx=1, OS><br>NC Non-Transition Bit       | ζ = 0,1,                                      |      | 350  |      |       |

|                                              |                                                            | DEx, OSx = NC, See                                                  | Operating temperature 0°C to 85°C             | -3.0 | -3.7 | -4.0 |       |

|                                              | De-Emphasis Level                                          | Figure 11;<br>(for OS1,2 = 1 and 0 see<br>Table 2)                  | Operating temperature –40°C to 85°C           | -3.0 | -3.7 | -4.2 | dB    |

|                                              |                                                            | DEx = 0, OSx = NC                                                   |                                               |      | -6.4 |      |       |

|                                              |                                                            | DEx = 1, OSx = NC                                                   |                                               |      | -9.4 |      | dB    |

| T <sub>DE</sub>                              | De-Emphasis Width                                          | At 5Gbps                                                            |                                               |      | 0.8  |      | UI    |

| Z <sub>diff_TX</sub>                         | DC Differential Impedance                                  | Defined during signaling                                            |                                               | 80   | 100  | 120  | Ω     |

| -diii_1X                                     | 20 2o.oapodaeo                                             | 20mod damig digitamig                                               | Operating temperature 0°C to 85°C             | 10   |      | 0    |       |

| $RL_{diff\_TX}$                              |                                                            | f = 50 MHz - 1.25 GHz.                                              | Operating temperature –40°C to 85°C           | 9.5  |      |      |       |

|                                              | Differential Return Loss                                   |                                                                     | Operating temperature 0°C to 85°C             | 6    |      |      | dB    |

|                                              |                                                            | f = 1.25 GHz - 2.5 GHz,                                             |                                               |      |      |      |       |

| DI                                           | 0 M I D I                                                  | Operating temperature –40°C to 85°C                                 |                                               | 5.5  |      |      |       |

| RL <sub>CM_TX</sub>                          | Common Mode Return Loss                                    | f = 50 MHz – 2.5 GHz                                                |                                               | 10   | 00   | 00   | dB    |

| I <sub>TX_SC</sub>                           | TX short circuit current                                   | TX± shorted to GND                                                  |                                               |      | 60   | 90   | mA    |

| V <sub>TX_CM_DC</sub>                        | Transmitter DC common-mode voltage                         | Allowed DC CM voltage at T                                          | 2.1                                           | 2.65 | 3.1  | V    |       |

| V <sub>TX_CM_AC2</sub>                       | TX AC common mode voltage at GEN II speed                  | - Max(V <sub>d+</sub> + V <sub>d-</sub> )/2 - Min(V <sub>d+</sub> - | ⊾ V. √2                                       |      | 26   | 100  | mVpp  |

| V <sub>TX_CM_AC1</sub>                       | TX AC common mode voltage at GEN I speed                   | 1012A(Vd+ + Vd-)/2 - 10111(Vd+ +                                    | • v <sub>d</sub> _//∠                         |      | 2    | 20   | mV    |

| V <sub>TX_CM_DeltaL0-L0s</sub>               | Absolute Delta DC CM voltage during active and idle states | VTX_CM_DC [L0] - VTX_CM_DC [L                                       | <sub>.0s]</sub>  , PS=L                       | 0    |      | 100  | mV    |

| V <sub>TX_CM-DC-Line-</sub><br>Delta         | Absolute Delta of DC CM voltage between D+ and D-          | V <sub>TX_CM_DC-D+ [L0]</sub> - V <sub>TX_CM_DC</sub>               | C-D- [L0]                                     | 0    |      | 25   | mV    |

| $V_{TX\_idle\_diff-AC-p}$                    | Electrical idle differential peak output voltage           | $ V_{TX-Idle-D+} - V_{TX-Idle-D-} $ HP fil                          | tered to remove any DC component              | 0    | 1    | 10   | mVpp  |

| $V_{TX\_idle\_diff\text{-DC}}$               | DC Electrical idle differential output voltage             | V <sub>TX_idle-D+</sub> - V <sub>TX_idle-D-</sub>   LP fil          | tered to remove any AC component              |      | 3.5  |      | mV    |

| V <sub>detect</sub>                          | Voltage change to allow receiver detect                    | Positive voltage to sense rec                                       | ceiver                                        |      |      | 600  | mV    |

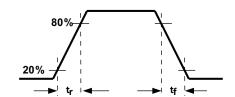

| $t_R, t_F$                                   | Output Rise/Fall time                                      | DEx = NC, OS = NC (CH 0 a at the output; VID > 1000mV               | and CH 1) 20%-80% of differential voltage (pp | 30   | 53   |      | ps    |

| t <sub>RF_MM</sub>                           | Output Rise/Fall time mismatch                             | DEx = NC, OS = NC (CH 0 a at the output                             |                                               | 1    | 20   | ps   |       |

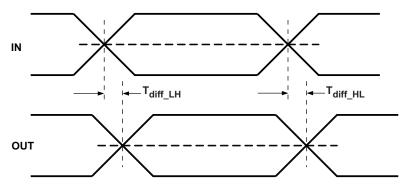

| T <sub>diff_LH</sub> , T <sub>diff_HL</sub>  | Differential Propagation Delay                             | DEx = NC (CH 0 and CH 1). input and output. See Figure              |                                               | 280  | 330  | ps   |       |

| t <sub>idleEntry</sub> t <sub>idleExit</sub> | Idle entry and exit times                                  | See Figure 7                                                        |                                               |      | 4    | 6    | ns    |

| -                                            | ON at GEN II Speed (under recomn                           | nenced operating conditions                                         | )                                             |      |      |      |       |

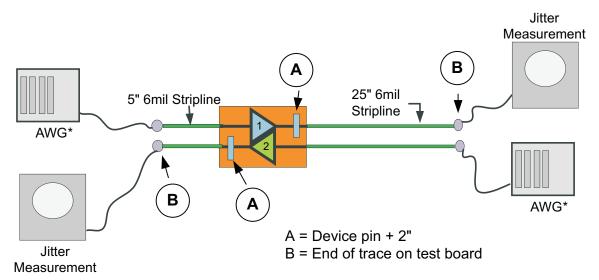

|                                              | ,,                                                         | At point A in Figure 10 <sup>(2)</sup>                              |                                               |      | 30   | 50   |       |

| T <sub>TX-TJ</sub> <sup>(1)</sup>            | Total Jitter                                               | At point B in Figure 10 <sup>(2)</sup>                              |                                               |      | 25   | 80   | ps pp |

|                                              |                                                            | At point A in Figure 10 <sup>(2)</sup>                              |                                               |      | 16   | 30   |       |

|                                              |                                                            |                                                                     |                                               |      |      |      |       |

<sup>(1)</sup> Includes RJ at 10<sup>-12</sup>

<sup>(2)</sup> Refer to Figure 10 with ± K28.5 pattern at 5Gbps, -3.5dB DE from source AWG.

Figure 6. Propagation Delay

Figure 7. Idle Mode Exit and Entry Delay

Figure 8. Output Rise and Fall Times

Figure 9. Auto Low Power Mode Timing (when enabled)

Submit Documentation Feedback

Figure 10. Jitter Measurement Setup

Figure 11. Output De-Emphasis Levels OSx = NC

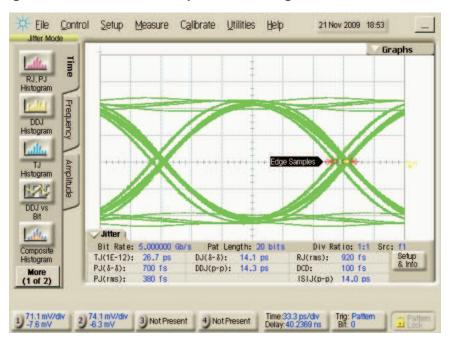

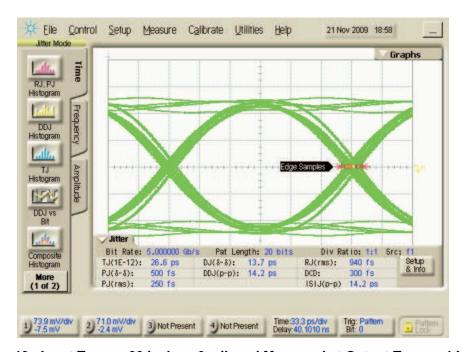

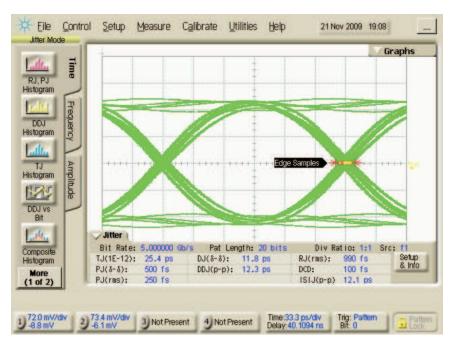

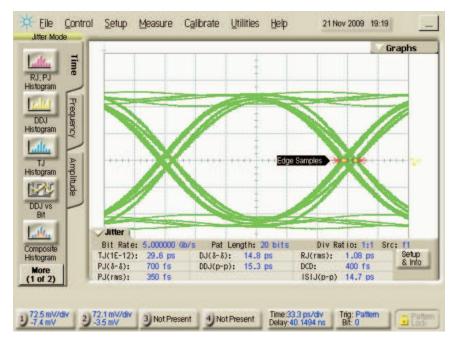

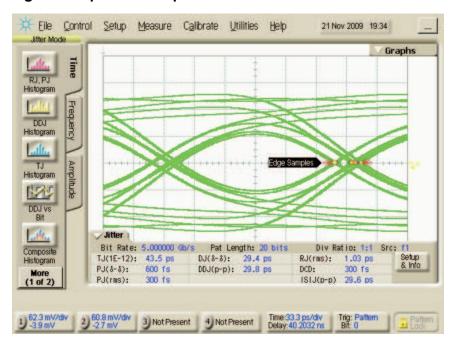

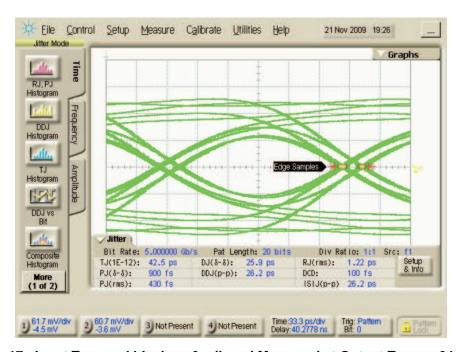

# Typical Eye Diagram and Performance Curves at Output

Input Signal Characteristics: Data Rate = 5 Gbps,  $V_{ID}$  = 1000 mVpp, DE = -3.5 dB, Pattern = K28.5 Device Operating Conditions: VCC = 3.3 V, Temp = 25°C

Device EQ settings (EQ/DE/OS) adjusted for best eye performance

## **Output Trace Length Held Constant and Input Trace Length Varied**

Figure 12. Input Trace = 4 Inches, 6 mil, and Measured at Output Trace = 4 Inches

Figure 13. Input Trace = 20 Inches, 6 mil, and Measured at Output Trace = 4 Inches

Figure 14. Input Trace = 32 Inches, 6 mil, and Measured at Output Trace = 4 Inches

Figure 15. Input Trace = 44 Inches, 6 mil, and Measured at Output Trace = 4 Inches

# Variable Trace Lengths at Input and Output

Figure 16. Input Trace = 28 Inches, 6 mil, and Measured at Output Trace = 24 Inches

Figure 17. Input Trace = 44 Inches, 6 mil, and Measured at Output Trace = 24 Inches

# **REVISION HISTORY**

| Ch | hanges from Original (May 2010) to Revision A | Page |

|----|-----------------------------------------------|------|

| •  | Added Figure 4                                | 7    |

www.ti.com 11-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins  | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/         | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|-----------------|-----------------------|------|---------------|---------------------|--------------|--------------|

|                       | (1)    | (2)           |                 |                       | (3)  | Ball material | Peak reflow         |              | (6)          |

|                       |        |               |                 |                       |      | (4)           | (5)                 |              |              |

| SN65LVPE501RGER       | Active | Production    | VQFN (RGE)   24 | 3000   LARGE T&R      | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | LVPE501      |

| SN65LVPE501RGER.B     | Active | Production    | VQFN (RGE)   24 | 3000   LARGE T&R      | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | LVPE501      |

| SN65LVPE501RGET       | Active | Production    | VQFN (RGE)   24 | 250   SMALL T&R       | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | LVPE501      |

| SN65LVPE501RGET.B     | Active | Production    | VQFN (RGE)   24 | 250   SMALL T&R       | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | LVPE501      |

| SN65LVPE501RGETG4     | Active | Production    | VQFN (RGE)   24 | 250   SMALL T&R       | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | LVPE501      |

| SN65LVPE501RGETG4.B   | Active | Production    | VQFN (RGE)   24 | 250   SMALL T&R       | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | LVPE501      |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 11-Nov-2025

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 24-Jul-2025

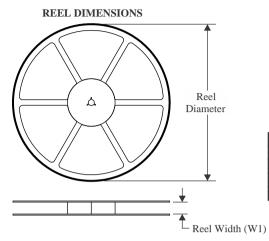

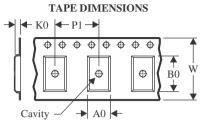

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

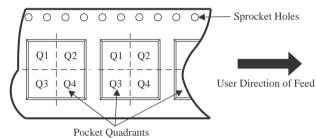

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device            | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| SN65LVPE501RGER   | VQFN            | RGE                | 24 | 3000 | 330.0                    | 12.4                     | 4.25       | 4.25       | 1.15       | 8.0        | 12.0      | Q2               |

| SN65LVPE501RGET   | VQFN            | RGE                | 24 | 250  | 180.0                    | 12.4                     | 4.25       | 4.25       | 1.15       | 8.0        | 12.0      | Q2               |

| SN65LVPE501RGETG4 | VQFN            | RGE                | 24 | 250  | 180.0                    | 12.4                     | 4.25       | 4.25       | 1.15       | 8.0        | 12.0      | Q2               |

www.ti.com 24-Jul-2025

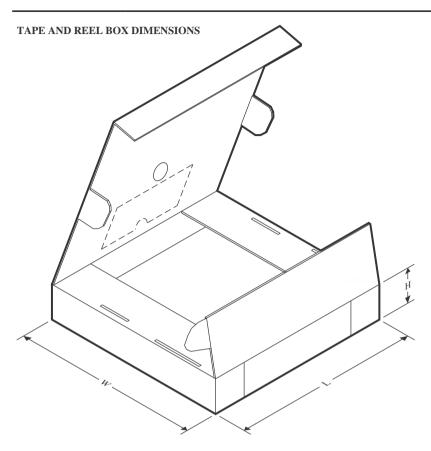

## \*All dimensions are nominal

| Device            | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| SN65LVPE501RGER   | VQFN         | RGE             | 24   | 3000 | 353.0       | 353.0      | 32.0        |

| SN65LVPE501RGET   | VQFN         | RGE             | 24   | 250  | 213.0       | 191.0      | 35.0        |

| SN65LVPE501RGETG4 | VQFN         | RGE             | 24   | 250  | 213.0       | 191.0      | 35.0        |

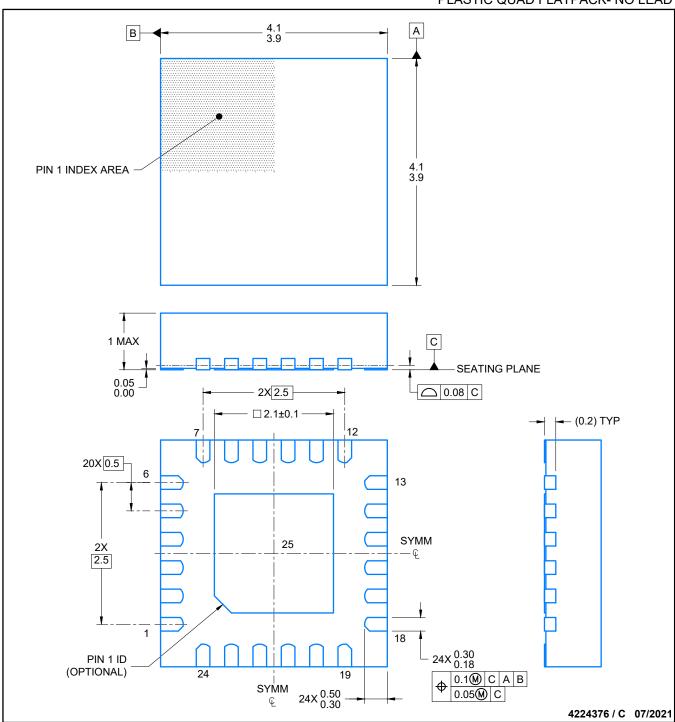

PLASTIC QUAD FLATPACK - NO LEAD

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

4204104/H

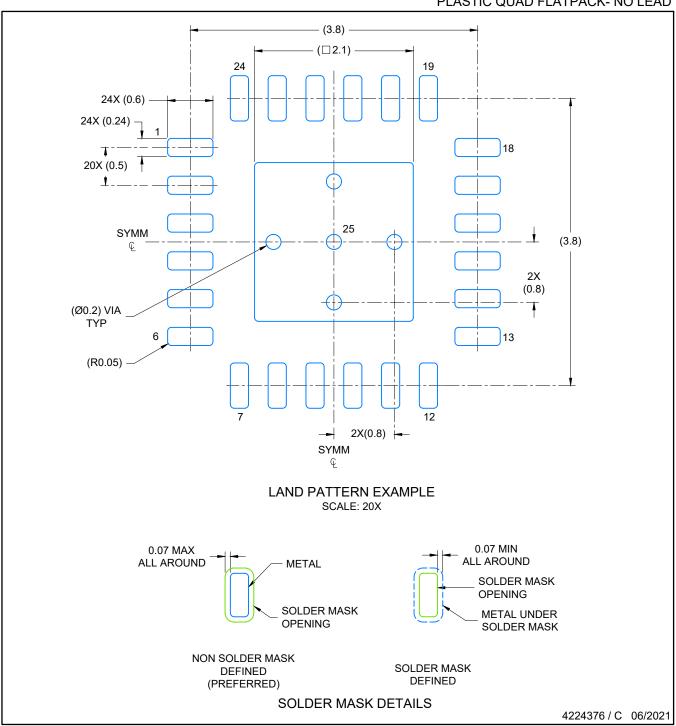

PLASTIC QUAD FLATPACK- NO LEAD

### NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

PLASTIC QUAD FLATPACK- NO LEAD

NOTES: (continued)

- This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- Solder mask tolerances between and around signal pads can vary based on board fabrication site.

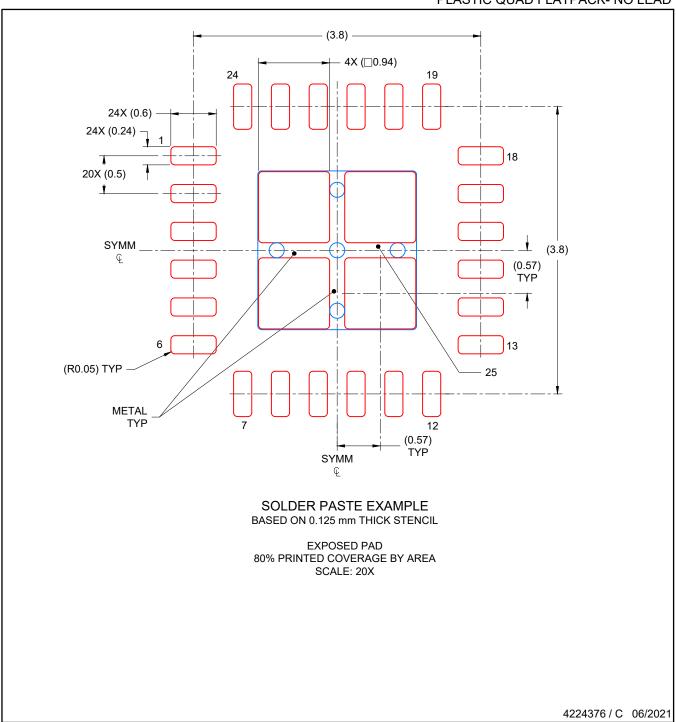

PLASTIC QUAD FLATPACK- NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations..

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025