SLAS097E – SEPTEMBER 1994 – REVISED MAY 1997

Voltage-Controlled Oscillator (VCO) Section:

Complete Oscillator Using Only One External Bias Resistor (R<sub>BIAS</sub>)

- Lock Frequency: 22 MHz to 50 MHz ( $V_{DD} = 5 V \pm 5\%$ ,  $T_A = -20^{\circ}$ C to 75°C, ×1 Output) 11 MHz to 25 MHz ( $V_{DD} = 5 V \pm 5\%$ ,  $T_A = -20^{\circ}$ C to 75°C, ×1/2 Output)

- Output Frequency . . . ×1 and ×1/2 Selectable

- Phase-Frequency Detector (PFD) Section Includes a High-Speed Edge-Triggered Detector With Internal Charge Pump

- Independent VCO, PFD Power-Down Mode

- Thin Small-Outline Package (14 terminal)

- CMOS Technology

- Typical Applications:

- Frequency Synthesis

- Modulation/Demodulation

- Fractional Frequency Division

- Application Report Available<sup>†</sup>

- CMOS Input Logic Level

#### description

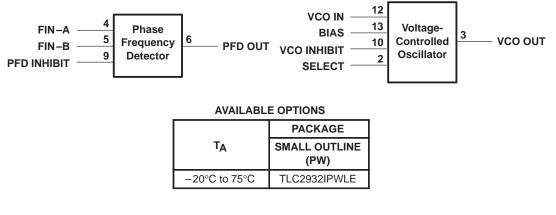

The TLC2932 is designed for phase-locked-loop (PLL) systems and is composed of a voltage-controlled oscillator (VCO) and an edge-triggered-type phase frequency detector (PFD). The oscillation frequency range of the VCO is set by an external bias resistor ( $R_{BIAS}$ ). The VCO has a 1/2 frequency divider at the output stage. The high-speed PFD with internal charge pump detects the phase difference between the reference frequency input and signal frequency input from the external counter. Both the VCO and the PFD have inhibit functions, which can be used as a power-down mode. The TLC2932 is suitable for use as a high-performance PLL due to the high speed and stable oscillation capability of the device.

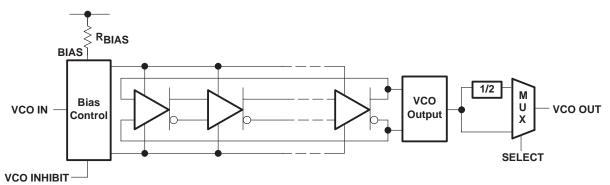

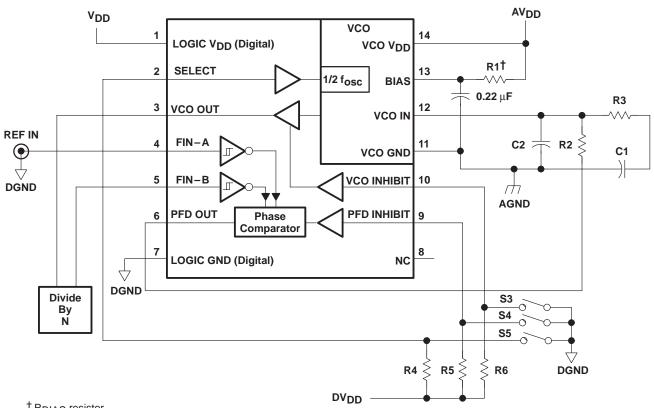

### functional block diagram

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

<sup>†</sup>TLC2932 Phase-Locked-Loop Building Block With Analog Voltage-Controlled Oscillator and Phase Frequency Detector (SLAA011).

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1997, Texas Instruments Incorporated

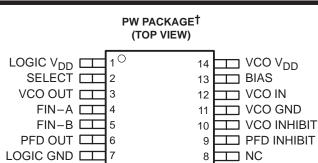

<sup>†</sup> Available in tape and reel only and ordered as the TLC2932IPWLE.

NC – No internal connection

SLAS097E - SEPTEMBER 1994 - REVISED MAY 1997

| TERMINA               | 4L  |     |                                                                                                                                                            |

|-----------------------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                  | NO. | 1/0 | DESCRIPTION                                                                                                                                                |

| FIN-A                 | 4   | 1   | Input reference frequency f(REF IN) is applied to FIN-A.                                                                                                   |

| FIN-B                 | 5   | I   | Input for VCO external counter output frequency f <sub>(FIN-B)</sub> . FIN-B is nominally provided from the external counter.                              |

| LOGIC GND             | 7   |     | GND for the internal logic.                                                                                                                                |

| LOGIC V <sub>DD</sub> | 1   |     | Power supply for the internal logic. This power supply should be separate from VCO $V_{DD}$ to reduce cross-coupling between supplies.                     |

| NC                    | 8   |     | No internal connection.                                                                                                                                    |

| PFD INHIBIT           | 9   | I   | PFD inhibit control. When PFD INHIBIT is high, PFD output is in the high-impedance state, see Table 3.                                                     |

| PFD OUT               | 6   | 0   | PFD output. When the PFD INHIBIT is high, PFD output is in the high-impedance state.                                                                       |

| BIAS                  | 13  | 1   | Bias supply. An external resistor ( $R_{BIAS}$ ) between VCO $V_{DD}$ and BIAS supplies bias for adjusting the oscillation frequency range.                |

| SELECT                | 2   | 1   | VCO output frequency select. When SELECT is high, the VCO output frequency is $\times 1/2$ and when low, the output frequency is $\times 1$ , see Table 1. |

| VCO IN                | 12  | 1   | VCO control voltage input. Nominally the external loop filter output connects to VCO IN to control VCO oscillation frequency.                              |

| VCO INHIBIT           | 10  | 1   | VCO inhibit control. When VCO INHIBIT is high, VCO OUT is low (see Table 2).                                                                               |

| VCO GND               | 11  |     | GND for VCO.                                                                                                                                               |

| VCO OUT               | 3   | 0   | VCO output. When the VCO INHIBIT is high, VCO output is low.                                                                                               |

| VCO V <sub>DD</sub>   | 14  |     | Power supply for VCO. This power supply should be separated from LOGIC $V_{\text{DD}}$ to reduce cross-coupling between supplies.                          |

# **Terminal Functions**

### detailed description

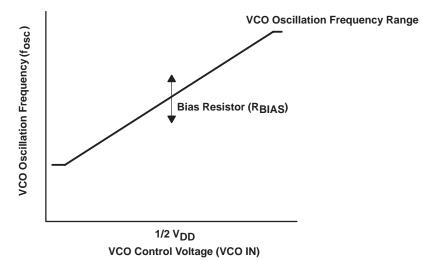

### VCO oscillation frequency

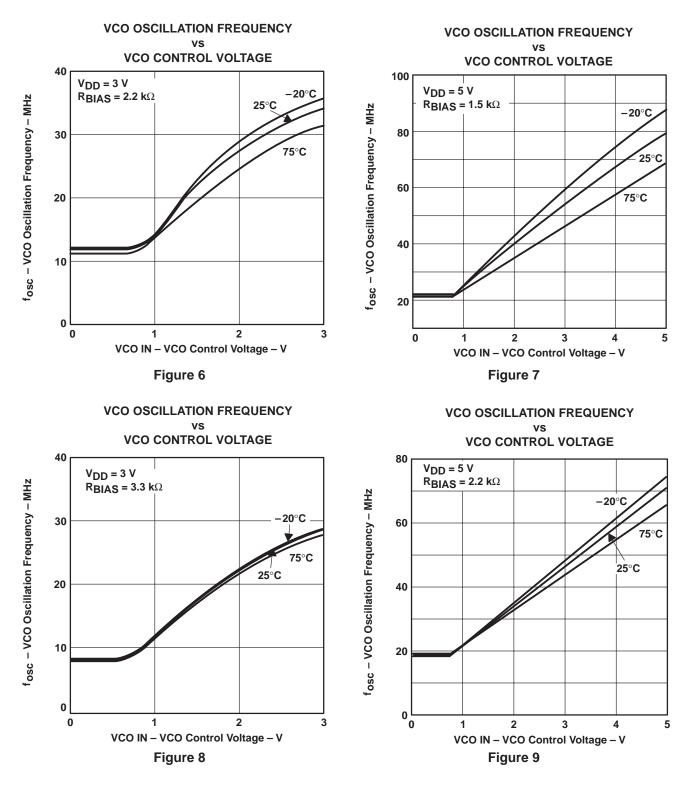

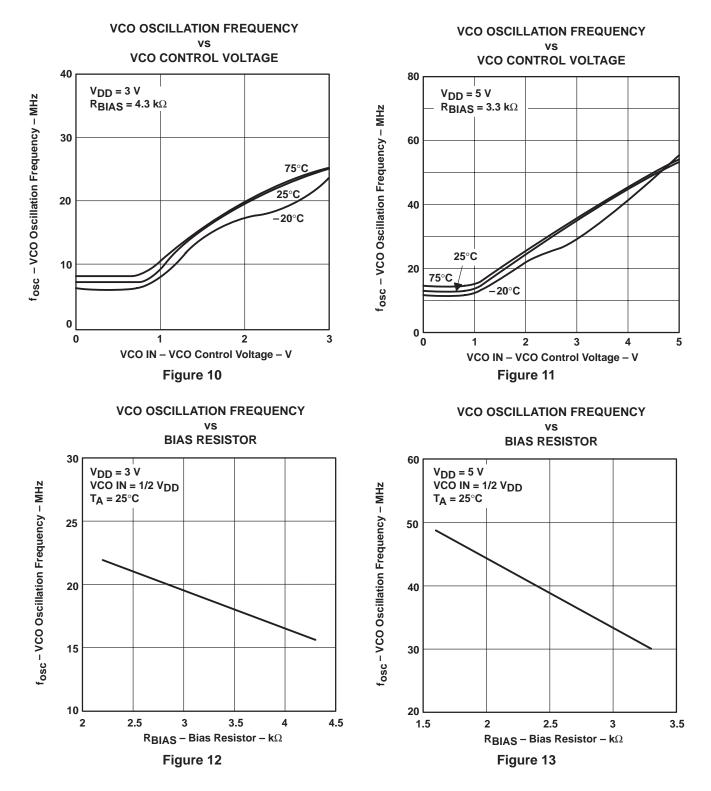

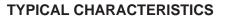

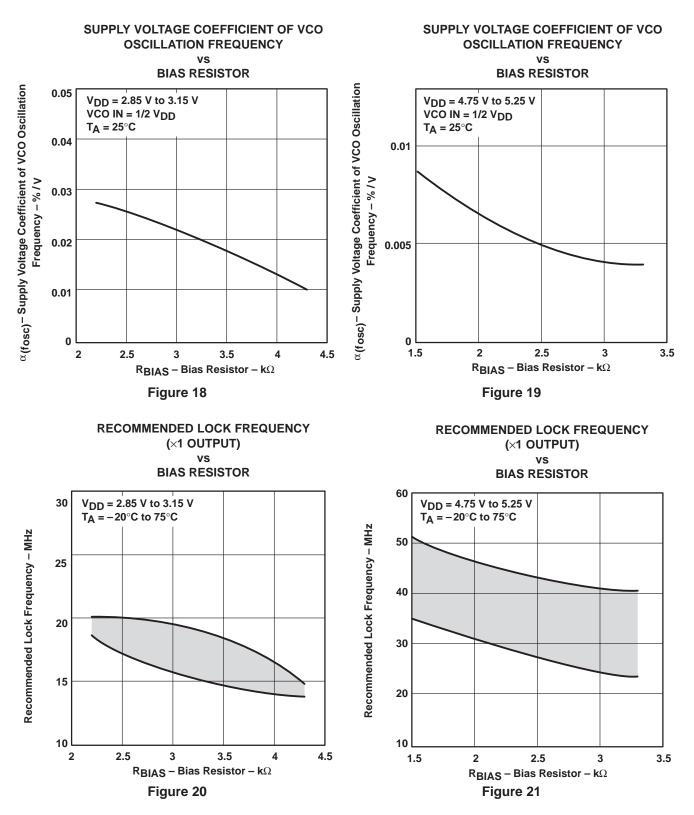

The VCO oscillation frequency is determined by an external resistor (R<sub>BIAS</sub>) connected between the VCO V<sub>DD</sub> and the BIAS terminals. The oscillation frequency and range depends on this resistor value. The bias resistor value for the minimum temperature coefficient is nominally 3.3 k $\Omega$  with 3-V at the VCO V<sub>DD</sub> terminal and nominally 2.2 k $\Omega$  with 5-V at the VCO V<sub>DD</sub> terminal. For the lock frequency range refer to the recommended operating conditions. Figure 1 shows the typical frequency variation and VCO control voltage.

### VCO output frequency 1/2 divider

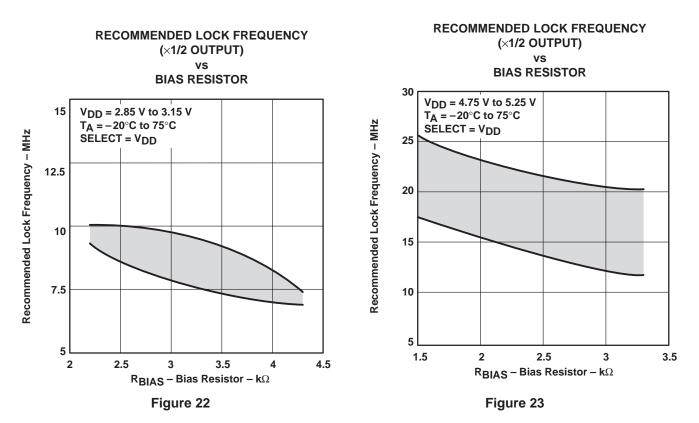

The TLC2932 SELECT terminal sets the  $f_{OSC}$  or 1/2  $f_{OSC}$  VCO output frequency as shown in Table 1. The 1/2  $f_{OSC}$  output should be used for minimum VCO output jitter.

### Table 1. VCO Output 1/2 Divider Function

| SELECT | VCO OUTPUT           |

|--------|----------------------|

| Low    | fosc                 |

| High   | 1/2 f <sub>OSC</sub> |

#### **VCO** inhibit function

The VCO has an externally controlled inhibit function which inhibits the VCO output. A high level on the VCO INHIBIT terminal stops the VCO oscillation and powers down the VCO. The output maintains a low level during the power-down mode, refer to Table 2.

| VCO INHIBIT | VCO OSCILLATOR | VCO OUTPUT IDD(VCO |            |

|-------------|----------------|--------------------|------------|

| Low         | Active         | Active             | Normal     |

| High        | Stopped        | Low level          | Power Down |

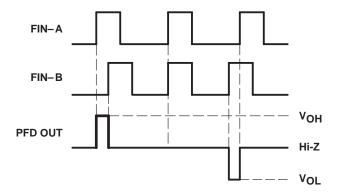

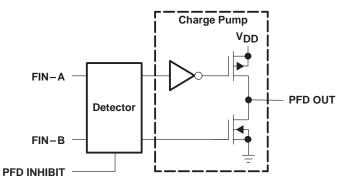

#### **PFD** operation

The PFD is a high-speed, edge-triggered detector with an internal charge pump. The PFD detects the phase difference between two frequency inputs supplied to FIN–A and FIN–B as shown in Figure 2. Nominally the reference is supplied to FIN–A, and the frequency from the external counter output is fed to FIN–B.

Figure 2. PFD Function Timing Chart

#### **PFD** output control

A high level on the PFD INHIBIT terminal places the PFD output in the high-impedance state and the PFD stops phase detection as shown in Table 3. A high level on the PFD INHIBIT terminal also can be used as the power-down mode for the PFD.

| PFD INHIBIT | DETECTION | PFD OUTPUT | IDD(PFD)   |

|-------------|-----------|------------|------------|

| Low         | Active    | Active     | Normal     |

| High        | Stopped   | Hi-Z       | Power Down |

#### Table 3. VCO Output Control Function

SLAS097E - SEPTEMBER 1994 - REVISED MAY 1997

### schematics

### VCO block schematic

#### **PFD block schematic**

### absolute maximum ratings<sup>†</sup>

| Supply voltage (each supply), V <sub>DD</sub> (see Note 1)                         |                |

|------------------------------------------------------------------------------------|----------------|

| Input voltage range (each input), VI (see Note 1)                                  |                |

| Input current (each input), I <sub>I</sub>                                         | ±20 mA         |

| Output current (each output), IO                                                   | ±20 mA         |

| Continuous total power dissipation, at (or below) $T_A = 25^{\circ}C$ (see Note 2) |                |

| Operating free-air temperature range, T <sub>A</sub>                               | –20°C to 75°C  |

| Storage temperature range, T <sub>stg</sub>                                        | –65°C to 150°C |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds                       |                |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. All voltage values are with respect to network GND.

2. For operation above 25°C free-air temperature, derate linearly at the rate of 5.6 mW/°C.

SLAS097E - SEPTEMBER 1994 - REVISED MAY 1997

### recommended operating conditions

| PAR                                                | AMETER                | MIN  | NOM | MAX             | UNIT   |

|----------------------------------------------------|-----------------------|------|-----|-----------------|--------|

| Supply voltage // (apply supply app Note 2)        | $V_{DD} = 3 V$        | 2.85 | 3   | 3.15            | V      |

| Supply voltage, $V_{DD}$ (each supply, see Note 3) | $V_{DD} = 5 V$        | 4.75 | 5   | 5.25            | v      |

| Input voltage, VI (inputs except VCO IN)           |                       | 0    |     | V <sub>DD</sub> | V      |

| Output current, IO (each output)                   |                       | 0    |     | ±2              | mA     |

| VCO control voltage at VCO IN                      |                       | 0.9  |     | V <sub>DD</sub> | V      |

| Look from on a (14 output)                         | $V_{DD} = 3 V$        | 14   |     | 21              | MHz    |

| Lock frequency (×1 output)                         | $V_{DD} = 5 V$        | 22   |     | 50              |        |

| Look frequency (x1/2 output)                       | $V_{DD} = 3 V$        | 7    |     | 10.5            | MHz    |

| Lock frequency (×1/2 output)                       | $V_{DD} = 5 V$        | 11   |     | 25              | IVITIZ |

| Pige register Paulo                                | V <sub>DD</sub> = 3 V | 2.2  | 3.3 | 4.3             | kΩ     |

| Bias resistor, RBIAS                               | $V_{DD} = 5 V$        | 1.5  | 2.2 | 3.3             | K12    |

NOTE 3: It is recommended that the logic supply terminal (LOGIC V<sub>DD</sub>) and the VCO supply terminal (VCO V<sub>DD</sub>) should be at the same voltage and separated from each other.

# electrical characteristics over recommended operating free-air temperature range, $V_{DD}$ = 3 V (unless otherwise noted)

#### VCO section

| PARAMETER                                      | TEST CONDITIONS                                                                                                                                                                                         | MIN                                                                                                                                                                                                                                                                                                                      | TYP                                                                                                                                                                                                                                                                                                                          | MAX                                                                                                                                                                                                                                                                                                                                                                   | UNIT                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High-level output voltage                      | $I_{OH} = -2 \text{ mA}$                                                                                                                                                                                | 2.4                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                       | V                                                                                                                                                                                                                                                                                                                                               |

| Low-level output voltage                       | $I_{OL} = 2 \text{ mA}$                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                              | 0.3                                                                                                                                                                                                                                                                                                                                                                   | V                                                                                                                                                                                                                                                                                                                                               |

| Input threshold voltage at SELECT, VCO INHIBIT |                                                                                                                                                                                                         | 0.9                                                                                                                                                                                                                                                                                                                      | 1.5                                                                                                                                                                                                                                                                                                                          | 2.1                                                                                                                                                                                                                                                                                                                                                                   | V                                                                                                                                                                                                                                                                                                                                               |

| Input current at SELECT, VCO INHIBIT           | $V_{I} = V_{DD}$ or GND                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                              | ±1                                                                                                                                                                                                                                                                                                                                                                    | μΑ                                                                                                                                                                                                                                                                                                                                              |

| Input impedance                                | VCO IN = $1/2 V_{DD}$                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                          | 10                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                       | MΩ                                                                                                                                                                                                                                                                                                                                              |

| VCO supply current (inhibit)                   | See Note 4                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                          | 0.01                                                                                                                                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                     | μΑ                                                                                                                                                                                                                                                                                                                                              |

| VCO supply current                             | See Note 5                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                          | 5                                                                                                                                                                                                                                                                                                                            | 15                                                                                                                                                                                                                                                                                                                                                                    | mA                                                                                                                                                                                                                                                                                                                                              |

|                                                | High-level output voltage     Low-level output voltage     Input threshold voltage at SELECT, VCO INHIBIT     Input current at SELECT, VCO INHIBIT     Input impedance     VCO supply current (inhibit) | High-level output voltage $I_{OH} = -2 \text{ mA}$ Low-level output voltage $I_{OL} = 2 \text{ mA}$ Input threshold voltage at SELECT, VCO INHIBITInput current at SELECT, VCO INHIBITInput current at SELECT, VCO INHIBIT $V_I = V_{DD}$ or GNDInput impedanceVCO IN = 1/2 V_{DD}VCO supply current (inhibit)See Note 4 | High-level output voltage $I_{OH} = -2 \text{ mA}$ 2.4Low-level output voltage $I_{OL} = 2 \text{ mA}$ 1Input threshold voltage at SELECT, VCO INHIBIT0.90.9Input current at SELECT, VCO INHIBIT $V_I = V_{DD}$ or GND1Input impedanceVCO IN = 1/2 V_{DD}VCO supply current (inhibit)VCO supply current (inhibit)See Note 41 | High-level output voltage $I_{OH} = -2 \text{ mA}$ $2.4$ Low-level output voltage $I_{OL} = 2 \text{ mA}$ $I_{OL} = 2 \text{ mA}$ Input threshold voltage at SELECT, VCO INHIBIT $0.9$ $1.5$ Input current at SELECT, VCO INHIBIT $V_I = V_{DD}$ or GND $V_{OI} = 1/2 V_{DD}$ Input impedanceVCO IN = $1/2 V_{DD}$ $10$ VCO supply current (inhibit)See Note 4 $0.01$ | High-level output voltage $I_{OH} = -2 \text{ mA}$ $2.4$ Low-level output voltage $I_{OL} = 2 \text{ mA}$ $2.4$ Input threshold voltage at SELECT, VCO INHIBIT $0.9$ $1.5$ $2.1$ Input current at SELECT, VCO INHIBIT $V_I = V_{DD}$ or GND $\pm 1$ Input impedanceVCO IN = $1/2 V_{DD}$ $10$ VCO supply current (inhibit)See Note 4 $0.01$ $1$ |

NOTES: 4. Current into VCO  $V_{DD}$ , when VCO INHIBIT =  $V_{DD}$ , PFD is inhibited.

5. Current into VCO  $V_{DD}$ , when VCO IN = 1/2  $V_{DD}$ ,  $R_{BIAS}$  = 3.3 k $\Omega$ , VCO INHIBIT = GND, and PFD is inhibited.

#### **PFD** section

|                    | PARAMETER                                | TEST CONDITIONS                              | MIN | TYP  | MAX | UNIT |

|--------------------|------------------------------------------|----------------------------------------------|-----|------|-----|------|

| VOH                | High-level output voltage                | $I_{OH} = -2 \text{ mA}$                     | 2.7 |      |     | V    |

| VOL                | Low-level output voltage                 | I <sub>OL</sub> = 2 mA                       |     |      | 0.2 | V    |

| IOZ                | High-impedance-state output current      | PFD INHIBIT = high,<br>$V_I = V_{DD}$ or GND |     |      | ±1  | μΑ   |

| VIH                | High-level input voltage at FIN–A, FIN–B |                                              | 2.7 |      |     | V    |

| VIL                | Low-level input voltage at FIN–A, FIN–B  |                                              |     |      | 0.5 | V    |

| VIT                | Input threshold voltage at PFD INHIBIT   |                                              | 0.9 | 1.5  | 2.1 | V    |

| Ci                 | Input capacitance at FIN–A, FIN–B        |                                              |     | 5    |     | pF   |

| Zi                 | Input impedance at FIN–A, FIN–B          |                                              |     | 10   |     | MΩ   |

| I <sub>DD(Z)</sub> | High-impedance-state PFD supply current  | See Note 6                                   |     | 0.01 | 1   | μA   |

| IDD(PFD)           | PFD supply current                       | See Note 7                                   |     | 0.1  | 1.5 | mA   |

NOTES: 6. Current into LOGIC  $V_{DD}$ , when FIN–A, FIN–B = GND, PFD INHIBIT =  $V_{DD}$ , no load, and VCO OUT is inhibited.

Current into LOGIC V<sub>DD</sub>, when FIN–A, FIN–B = 1 MHz (V<sub>I(PP)</sub> = 3 V, rectangular wave), NC = GND, no load, and VCO OUT is inhibited.

SLAS097E - SEPTEMBER 1994 - REVISED MAY 1997

# operating characteristics over recommended operating free-air temperature range, $V_{DD} = 3 V$ (unless otherwise noted)

### VCO section

|                     | PARAMETER                                           | TEST CONDITION                                                                                               | ONS                       | MIN | TYP  | MAX | UNIT |

|---------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------|-----|------|-----|------|

| fosc                | Operating oscillation frequency                     | $R_{BIAS} = 3.3 \text{ k}\Omega, \text{ VCO IN}$                                                             | $I = 1/2 V_{DD}$          | 15  | 19   | 23  | MHz  |

| ts(fosc)            | Time to stable oscillation (see Note 8)             | Measured from VCO INH                                                                                        | IBIT↓                     |     |      | 10  | μs   |

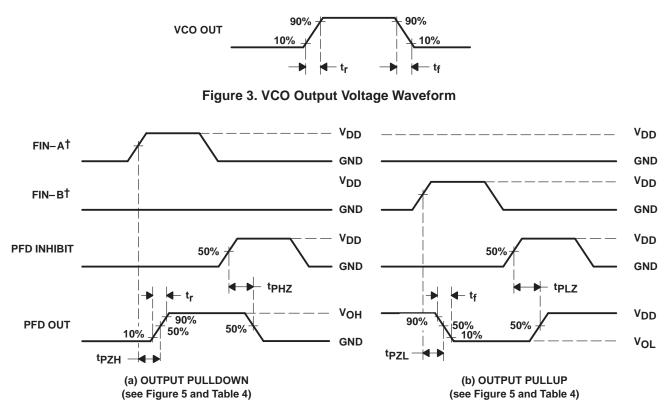

| +                   | Rise time                                           | C <sub>L</sub> = 15 pF, See Fig                                                                              | gure 3                    |     | 7    | 14  | 20   |

| t <sub>r</sub>      | Rise une                                            | C <sub>L</sub> = 50 pF, See Fig                                                                              | gure 3                    |     | 14   |     | ns   |

| 4.                  | Fall time                                           | C <sub>L</sub> = 15 pF, See Fig                                                                              | gure 3                    |     | 6    | 12  |      |

| tf                  | Fair ume                                            | C <sub>L</sub> = 50 pF, See Fig                                                                              | gure 3                    |     | 10   |     | ns   |

|                     | Duty cycle at VCO OUT                               | $R_{BIAS} = 3.3 \text{ k}\Omega, \text{ VCO IN}$                                                             | $I = 1/2 V_{DD},$         | 45% | 50%  | 55% |      |

| α <sub>(fosc)</sub> | Temperature coefficient of oscillation frequency    | $R_{BIAS} = 3.3 \text{ k}\Omega$ , VCO IN<br>T <sub>A</sub> = -20°C to 75°C                                  | l = 1/2 V <sub>DD</sub> , |     | 0.04 |     | %/°C |

| kSVS(fosc)          | Supply voltage coefficient of oscillation frequency | R <sub>BIAS</sub> = $3.3 \text{ k}\Omega$ , VCO IN<br>V <sub>DD</sub> = $2.85 \text{ V}$ to $3.15 \text{ V}$ | l = 1.5 V,                |     | 0.02 |     | %/mV |

|                     | Jitter absolute (see Note 9)                        | R <sub>BIAS</sub> = 3.3 kΩ                                                                                   |                           |     | 100  |     | ps   |

NOTES: 8. The time period to the stable VCO oscillation frequency after the VCO INHIBIT terminal is changed to a low level.

The low-pass-filter (LPF) circuit is shown in Figure 28 with calculated values listed in Table 7. Jitter performance is highly dependent on circuit layout and external device characteristics. The jitter specification was made with a carefully designed PCB with no device socket.

#### **PFD** section

| PARAMETER        |                                         | TEST CONDITIONS                      | MIN | TYP | MAX | UNIT |

|------------------|-----------------------------------------|--------------------------------------|-----|-----|-----|------|

| fmax             | Maximum operating frequency             |                                      | 20  |     |     | MHz  |

| <sup>t</sup> PLZ | PFD output disable time from low level  |                                      |     | 21  | 50  |      |

| <sup>t</sup> PHZ | PFD output disable time from high level | See Figures 4 and 5 and Table 4      |     | 23  | 50  | ns   |

| <sup>t</sup> PZL | PFD output enable time to low level     | See Figures 4 and 5 and Table 4      |     | 11  | 30  | 20   |

| <sup>t</sup> PZH | PFD output enable time to high level    |                                      |     | 10  | 30  | ns   |

| t <sub>r</sub>   | Rise time                               |                                      |     | 2.3 | 10  | ns   |

| t <sub>f</sub>   | Fall time                               | $C_L = 15 \text{ pF}$ , See Figure 4 |     | 2.1 | 10  | ns   |

SLAS097E - SEPTEMBER 1994 - REVISED MAY 1997

## electrical characteristics over recommended operating free-air temperature range, V<sub>DD</sub> = 5 V (unless otherwise noted)

### VCO section

|            | PARAMETER                                      | TEST CONDITIONS          | MIN | TYP  | MAX | UNIT |

|------------|------------------------------------------------|--------------------------|-----|------|-----|------|

| VOH        | High-level output voltage                      | $I_{OH} = -2 \text{ mA}$ | 4   |      |     | V    |

| VOL        | Low-level output voltage                       | $I_{OL} = 2 \text{ mA}$  |     |      | 0.5 | V    |

| VIT        | Input threshold voltage at SELECT, VCO INHIBIT |                          | 1.5 | 2.5  | 3.5 | V    |

| lj         | Input current at SELECT, VCO INHIBIT           | $V_I = V_{DD}$ or GND    |     |      | ±1  | μA   |

| Zi(VCO IN) | Input impedance                                | VCO IN = $1/2 V_{DD}$    |     | 10   |     | MΩ   |

| IDD(INH)   | VCO supply current (inhibit)                   | See Note 4               |     | 0.01 | 1   | μA   |

| IDD(VCO)   | VCO supply current                             | See Note 5               |     | 15   | 35  | mA   |

NOTES: 4. Current into VCO V<sub>DD</sub>, when VCO INHIBIT =  $V_{DD}$ , and PFD is inhibited.

5. Current into VCO V<sub>DD</sub>, when VCO IN = 1/2 V<sub>DD</sub>, R<sub>BIAS</sub> = 3.3 k $\Omega$ , VCO INHIBIT = GND, and PFD is inhibited.

#### **PFD** section

|          | PARAMETER                                | TEST CONDITIONS                              | MIN | TYP  | MAX | UNIT |

|----------|------------------------------------------|----------------------------------------------|-----|------|-----|------|

| VOH      | High-level output voltage                | I <sub>OH</sub> = 2 mA                       | 4.5 |      |     | V    |

| VOL      | Low-level output voltage                 | $I_{OL} = 2 \text{ mA}$                      |     |      | 0.2 | V    |

| IOZ      | High-impedance-state output current      | PFD INHIBIT = high,<br>$V_I = V_{DD}$ or GND |     |      | ±1  | μΑ   |

| VIH      | High-level input voltage at FIN–A, FIN–B |                                              | 4.5 |      |     | V    |

| VIL      | Low-level input voltage at FIN–A, FIN–B  |                                              |     |      | 1   | V    |

| VIT      | Input threshold voltage at PFD INHIBIT   |                                              | 1.5 | 2.5  | 3.5 | V    |

| Ci       | Input capacitance at FIN–A, FIN–B        |                                              |     | 5    |     | pF   |

| Zi       | Input impedance at FIN–A, FIN–B          |                                              |     | 10   |     | MΩ   |

| IDD(Z)   | High-impedance-state PFD supply current  | See Note 6                                   |     | 0.01 | 1   | μA   |

| IDD(PFD) | PFD supply current                       | See Note 7                                   |     | 0.15 | 3   | mA   |

NOTES: 6. Current into LOGIC V<sub>DD</sub>, when FIN–A, FIN–B = GND, PFD INHIBIT = V<sub>DD</sub>, no load, and VCO OUT is inhibited.

7. Current into LOGIC V<sub>DD</sub>, when FIN–A, FIN–B = 1 MHz (V<sub>I(PP)</sub> = 5 V, rectangular wave), PFD INHIBIT = GND, no load, and VCO OUT is inhibited.

SLAS097E - SEPTEMBER 1994 - REVISED MAY 1997

# operating characteristics over recommended operating free-air temperature range, $V_{DD} = 5 V$ (unless otherwise noted)

### VCO section

|                      | PARAMETER                                           | TEST CONDITI                                                                                                                    | IONS              | MIN | TYP    | MAX | UNIT |  |

|----------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------|-----|--------|-----|------|--|

| fosc                 | Operating oscillation frequency                     | $R_{BIAS} = 2.2 \text{ k}\Omega, \text{ VCO II}$                                                                                | $N = 1/2 V_{DD}$  | 30  | 41     | 52  | MHz  |  |

| <sup>t</sup> s(fosc) | Time to stable oscillation (see Note 8)             | Measured from VCO INH                                                                                                           | HIBIT↓            |     |        | 10  | μs   |  |

| +                    | Rise time                                           | C <sub>L</sub> = 15 pF, See Fi                                                                                                  | igure 3           |     | 5.5 10 |     | ns   |  |

| t <sub>r</sub>       | Rise time                                           | C <sub>L</sub> = 50 pF, See Fi                                                                                                  | igure 3           |     | 8      |     | 115  |  |

| t <sub>f</sub>       | Fall time                                           | C <sub>L</sub> = 15 pF, See Fi                                                                                                  | igure 3           |     | 5      | 10  | 20   |  |

|                      | Fairune                                             | C <sub>L</sub> = 50 pF, See Fi                                                                                                  | igure 3           |     | 6      |     | ns   |  |

|                      | Duty cycle at VCO OUT                               | $R_{BIAS} = 2.2 \text{ k}\Omega, \text{ VCO II}$                                                                                | $N = 1/2 V_{DD},$ | 45% | 50%    | 55% |      |  |

| α <sub>(fosc)</sub>  | Temperature coefficient of oscillation frequency    | $R_{BIAS} = 2.2 \text{ k}\Omega$ , VCO II<br>T <sub>A</sub> = -20°C to 75°C                                                     | $N = 1/2 V_{DD},$ |     | 0.06   |     | %/°C |  |

| kSVS(fosc)           | Supply voltage coefficient of oscillation frequency | $\begin{array}{l} R_{BIAS} = 2.2 \ \text{k}\Omega, \ \text{VCO II} \\ V_{DD} = 4.75 \ \text{V to } 5.25 \ \text{V} \end{array}$ | N = 2.5 V,        |     | 0.006  |     | %/mV |  |

|                      | Jitter absolute (see Note 9)                        | $R_{BIAS} = 2.2 \text{ k}\Omega$                                                                                                |                   |     | 100    |     | ps   |  |

NOTES: 8: The time period to the stable VCO oscillation frequency after the VCO INHIBIT terminal is changed to a low level.

9. The LPF circuit is shown in Figure 28 with calculated values listed in Table 7. Jitter performance is highly dependent on circuit layout and external device characteristics. The jitter specification was made with a carefully designed PCB with no device socket.

#### **PFD** section

|                  | PARAMETER                               | TEST CONDITIONS                      | MIN | TYP | MAX | UNIT |

|------------------|-----------------------------------------|--------------------------------------|-----|-----|-----|------|

| fmax             | Maximum operating frequency             |                                      | 40  |     |     | MHz  |

| <sup>t</sup> PLZ | PFD output disable time from low level  |                                      |     | 21  | 40  | ns   |

| <sup>t</sup> PHZ | PFD output disable time from high level | See Figures 4 and 5 and Table 4      |     | 20  | 40  |      |

| t <sub>PZL</sub> | PFD output enable time to low level     | See Figures 4 and 5 and Table 4      |     | 7.3 | 20  |      |

| <sup>t</sup> PZH | PFD output enable time to high level    |                                      |     | 6.5 | 20  | ns   |

| t <sub>r</sub>   | Rise time                               | C <sub>1</sub> = 15 pF, See Figure 4 |     | 2.3 | 10  | ns   |

| t <sub>f</sub>   | Fall time                               | C <sub>L</sub> = 15 pF, See Figure 4 |     | 1.7 | 10  | ns   |

SLAS097E - SEPTEMBER 1994 - REVISED MAY 1997

### PARAMETER MEASUREMENT INFORMATION

<sup>†</sup> FIN–A and FIN–B are for reference phase only, not for timing.

### Figure 4. PFD Output Voltage Waveform

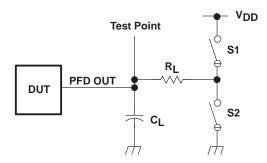

| PARAMETER        | RL   | CL    | s <sub>1</sub> | S <sub>2</sub> |  |

|------------------|------|-------|----------------|----------------|--|

| <sup>t</sup> PZH |      |       |                |                |  |

| <sup>t</sup> PHZ | 1 kΩ | 15 pF | Open           | Close          |  |

| tr               |      |       |                |                |  |

| tPZL             |      |       |                |                |  |

| <sup>t</sup> PLZ |      |       | Close          | Open           |  |

| t <sub>f</sub>   |      |       |                |                |  |

### Table 4. PFD Output Test Conditions

Figure 5. PFD Output Test Conditions

SLAS097E - SEPTEMBER 1994 - REVISED MAY 1997

## **TYPICAL CHARACTERISTICS**

SLAS097E - SEPTEMBER 1994 - REVISED MAY 1997

# **TYPICAL CHARACTERISTICS**

SLAS097E - SEPTEMBER 1994 - REVISED MAY 1997

SLAS097E - SEPTEMBER 1994 - REVISED MAY 1997

**TYPICAL CHARACTERISTICS**

SLAS097E - SEPTEMBER 1994 - REVISED MAY 1997

### **APPLICATION INFORMATION**

SLAS097E – SEPTEMBER 1994 – REVISED MAY 1997

## **APPLICATION INFORMATION**

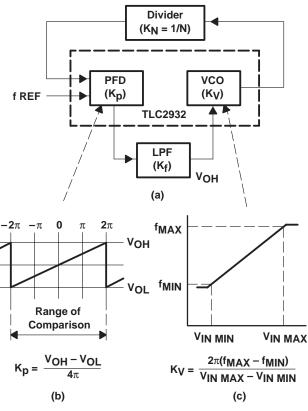

### gain of VCO and PFD

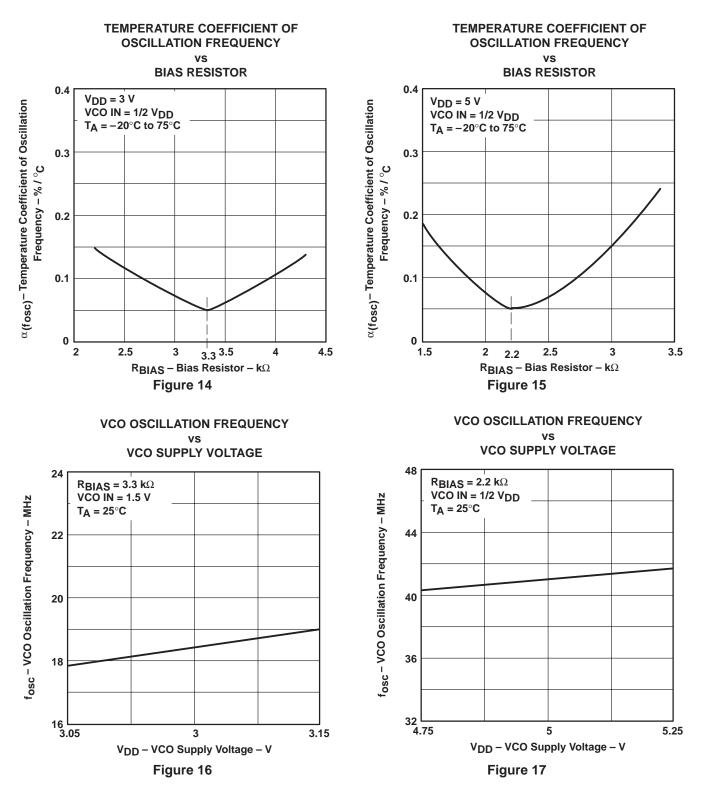

Figure 24 is a block diagram of the PLL. The countdown N value depends on the input frequency and the desired VCO output frequency according to the system application requirements. The K<sub>p</sub> and K<sub>V</sub> values are obtained from the operating characteristics of the device as shown in Figure 24. K<sub>p</sub> is defined from the phase detector V<sub>OL</sub> and V<sub>OH</sub> specifications and the equation shown in Figure 24(b). K<sub>V</sub> is defined from Figures 8, 9, 10, and 11 as shown in Figure 24(c).

The parameters for the block diagram with the units are as follows:

### external counter

When a large N counter is required by the application, there is a possibility that the PLL response becomes slow due to the counter response delay time. In the case of a high frequency application, the counter delay time should be accounted for in the overall PLL design.

The external bias resistor sets the VCO center frequency with 1/2 V<sub>DD</sub> applied to the VCO IN terminal. However, for optimum temperature performance, a resistor value of 3.3 k $\Omega$  with a 3-V supply and a resistor value of 2.5 k $\Omega$  for a 5-V supply is recommended. For the most accurate results, a metal-film resistor is the better choice but a carbon-compositiion resistor can be used with excellent results also. A 0.22  $\mu$ F capacitor should be connected from the BIAS terminal to ground as close to the device terminals as possible.

### hold-in range

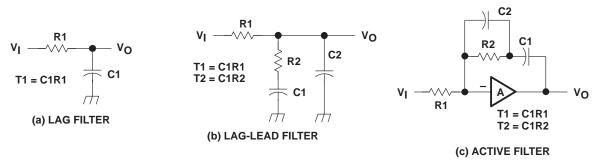

From the technical literature, the maximum hold-in range for an input frequency step for the three types of filter configurations shown in Figure 25 is as follows:

$$\Delta \omega_{\textrm{H}} \simeq 0.8 \, \left(\textrm{K}_{\textrm{p}}\right) \, \left(\textrm{K}_{\textrm{V}}\right) \, \left(\textrm{K}_{\textrm{f}} \, \left(\infty\right)\right)$$

Where

$K_f(\infty)$  = the filter transfer function value at  $\omega = \infty$

Figure 24. Example of a PLL Block Diagram

SLAS097E - SEPTEMBER 1994 - REVISED MAY 1997

# **APPLICATION INFORMATION**

### low-pass-filter (LPF) configurations

Many excellent references are available that include detailed design information about LPFs and should be consulted for additional information. Lag-lead filters or active filters are often used. Examples of LPFs are shown in Figure 25. When the active filter of Figure 25(c) is used, the reference should be applied to FIN-B because of the amplifier inversion. Also, in practical filter implementations, C2 is used as additional filtering at the VCO input. The value of C2 should be equal to or less than one tenth the value of C1.

Figure 25. LPF Examples for PLL

### the passive filter

The transfer function for the lag-lead filter shown in Figure 25(b) is;

$$\frac{V_{O}}{V_{IN}} = \frac{1 + s \cdot T_{2}}{1 + s \cdot (T_{1} + T_{2})}$$

Where

T1 = R1  $\cdot$  C1 and T2 = R2  $\cdot$  C1

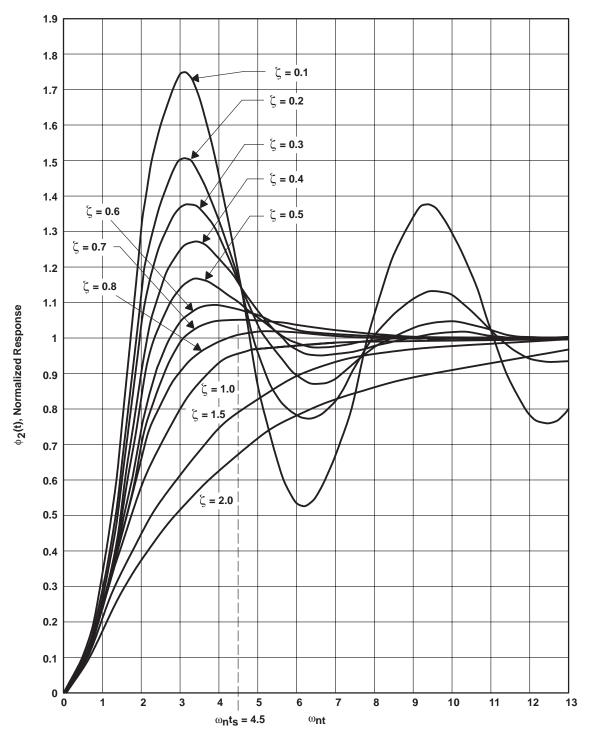

Using this filter makes the closed loop PLL system a second-order type 1 system. The response curves of this system to a unit step are shown in Figure 26.

### the active filter

When using the active integrator shown in Figure 25(c), the phase detector inputs must be reversed since the integrator adds an additional inversion. Therefore, the input reference frequency should be applied to the FIN-B terminal and the output of the VCO divider should be applied to the input reference terminal, FIN-A.

The transfer function for the active filter shown in Figure 25(c) is:

$$F(s) = \frac{1 + s \cdot R2 \cdot C1}{s \cdot R1 \cdot C1}$$

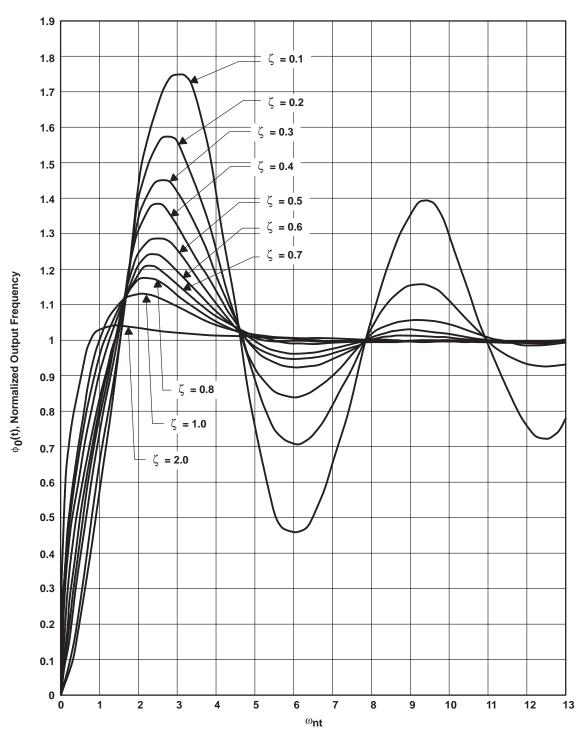

Using this filter makes the closed loop PLL system a second-order type 2 system. The response curves of this system to a unit step are shown in Figure 27.

### basic design example

The following design example presupposes that the input reference frequency and the required frequency of the VCO are within the respective ranges of the device.

# **APPLICATION INFORMATION**

### basic design example (continued)

Assume the loop has to have a 100  $\mu$ s settling time (t<sub>s</sub>) with a countdown N = 8. Using the Type 1, second order response curves of Figure 26, a value of 4.5 radians is selected for  $\omega_n t_s$  with a damping factor of 0.7. This selection gives a good combination for settling time, accuracy, and loop gain margin. The initial parameters are summarized in Table 5. The loop constants, K<sub>V</sub> and K<sub>p</sub>, are calculated from the data sheet specifications and Table 6 shows these values.

The natural loop frequency is calculated as follows:

Since

$$\omega_n t_s = 4.5$$

Then

$$\omega_n = \frac{4.5}{100 \ \mu s} = 45 \ k\text{-radians/sec}$$

| PARAMETER                            | SYMBOL           | VALUE | UNITS |

|--------------------------------------|------------------|-------|-------|

| Division factor                      | N                | 8     |       |

| Lockup time                          | t                | 100   | μs    |

| Radian value to selected lockup time | ω <sub>n</sub> t | 4.5   | rad   |

| Damping factor                       | ζ                | 0.7   |       |

**Table 6. Device Specifications**

#### **Table 5. Design Parameters**

| PARAMETER | SYMBOL         | VALUE    | UNITS    |

|-----------|----------------|----------|----------|

| VCO gain  |                | 76.6     | Mrad/V/s |

| fMAX      |                | 70       | MHz      |

| fMIN      | KV             | 20       | MHz      |

| VIN MAX   |                | 5        | V        |

|           |                | 0.9      | V        |

| PFD gain  | К <sub>р</sub> | 0.342357 | V/rad    |

### Table 7. Calculated Values

| PARAMETER                                                     | SYMBOL         | VALUE          | UNITS    |

|---------------------------------------------------------------|----------------|----------------|----------|

| Natural angular frequency                                     | ω <sub>n</sub> | 45000          | rad/sec  |

| $K = (K_V \bullet K_p)/N$                                     |                | 3.277          | Mrad/sec |

| Lag-lead filter<br>Calculated value<br>Nearest standard value | R1             | 15870<br>16000 | Ω        |

| Calculated value<br>Nearest standard value                    | R2             | 308<br>300     | Ω        |

| Selected value                                                | C1             | 0.1            | μF       |

SLAS097E - SEPTEMBER 1994 - REVISED MAY 1997

## **APPLICATION INFORMATION**

Using the low-pass filter in Figure 25(b) and divider ratio N, the transfer function for phase and frequency are shown in equations 1 and 2. Note that the transfer function for phase differs from the transfer function for frequency by only the divider value N. The difference arises from the fact that the feedback for phase is unity while the feedback for frequency is 1/N.

Hence, transfer function of Figure 24 (a) for phase is

$$\frac{\Phi 2(s)}{\Phi 1(s)} = \frac{K_p \cdot K_V}{N \cdot (T1 + T2)} \left[ \frac{1 + s \cdot T2}{s^2 + s \left[ 1 + \frac{K_p \cdot K_V \cdot T2}{N \cdot (T1 + T2)} \right] + \frac{K_p \cdot K_V}{N \cdot (T1 + T2)}} \right]$$

(1)

and the transfer function for frequency is

$$\frac{F_{OUT(s)}}{F_{REF(s)}} = \frac{K_{p} \cdot K_{V}}{(T1 + T2)} \left[ \frac{1 + s \cdot T2}{s^{2} + s \cdot \left[1 + \frac{K_{p} \cdot K_{V} \cdot T2}{N \cdot (T1 + T2)}\right] + \frac{K_{p} \cdot K_{V}}{N \cdot (T1 + T2)}} \right]$$

(2)

The standard two-pole denominator is  $D = s^2 + 2\zeta \omega_n s + \omega_n^2$  and comparing the coefficients of the denominator of equation 1 and 2 with the standard two-pole denominator gives the following results.

$$\omega_{n} = \sqrt{\frac{K_{p} \cdot K_{V}}{N \cdot (T1 + T2)}}$$

Solving for T1 + T2

$$T1 + T2 = \frac{K_p \cdot K_V}{N \cdot \omega_n^2}$$

(3)

and by using this value for T1 + T2 in equation 3 the damping factor is

$$\zeta = \frac{\omega_n}{2} \cdot \left( \mathsf{T2} + \frac{\mathsf{N}}{\mathsf{K}_p \cdot \mathsf{K}_V} \right)$$

solving for T2

$$T2 = \frac{2 \zeta}{\omega} - \frac{N}{K_{p} \cdot K_{V}}$$

then by substituting for T2 in equation 3

$$T1 = \frac{\kappa_{V} \cdot \kappa_{p}}{N \cdot \omega_{n}^{2}} - \frac{2\zeta}{\omega_{n}} + \frac{N}{\kappa_{p} \cdot \kappa_{V}}$$

### **APPLICATION INFORMATION**

From the circuit constants and the initial design parameters then

$$R2 = \left[\frac{2\zeta}{\omega_{n}} - \frac{N}{K_{p} \cdot K_{V}}\right] \frac{1}{C1}$$

$$R1 = \left[\frac{K_{p} \cdot K_{V}}{\omega_{n}^{2} \cdot N} - \frac{2\zeta}{\omega_{n}} + \frac{N}{K_{p} \cdot K_{V}}\right] \frac{1}{C1}$$

The capacitor, C1, is usually chosen between 1  $\mu$ F and 0.1  $\mu$ F to allow for reasonable resistor values and physical capacitor size. In this example, C1 is chosen to be 0.1  $\mu$ F and the corresponding R1 and R2 calculated values are listed in Table 7.

SLAS097E - SEPTEMBER 1994 - REVISED MAY 1997

### **APPLICATION INFORMATION**

SLAS097E - SEPTEMBER 1994 - REVISED MAY 1997

APPLICATION INFORMATION

Figure 27. Type 2 Second-Order Step Response

SLAS097E - SEPTEMBER 1994 - REVISED MAY 1997

### APPLICATION INFORMATION

<sup>†</sup>R<sub>BIAS</sub> resistor

Figure 28. Evaluation and Operation Schematic

### PCB layout considerations

The TLC2932 contains a high frequency analog oscillator; therefore, very careful breadboarding and printed-circuit-board (PCB) layout is required for evaluation.

The following design recommendations benefit the TLC2932 user:

- External analog and digital circuitry should be physically separated and shielded as much as possible to reduce system noise.

- RF breadboarding or RF PCB techniques should be used throughout the evaluation and production process.

- Wide ground leads or a ground plane should be used on the PCB layouts to minimize parasitic inductance and resistance. The ground plane is the better choice for noise reduction.

- LOGIC V<sub>DD</sub> and VCO V<sub>DD</sub> should be separate PCB traces and connected to the best filtered supply point available in the system to minimize supply cross-coupling.

- VCO V<sub>DD</sub> to GND and LOGIC V<sub>DD</sub> to GND should be decoupled with a 0.1-µF capacitor placed as close as possible to the appropriate device terminals.

- The no-connection (NC) terminal on the package should be connected to GND.

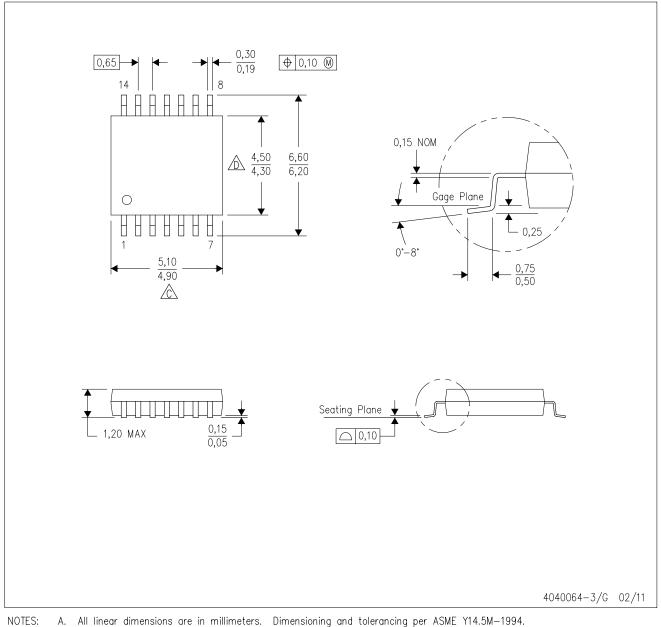

# PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|-------------------------------|----------------------|--------------|-------------------------|---------|

| TLC2932IPW       | OBSOLETE      | TSSOP        | PW                 | 11   |                | TBD             | (6)<br>Call TI                | Call TI              |              | Y2932                   |         |

|                  |               |              |                    | 14   |                |                 |                               |                      |              |                         |         |

| TLC2932IPWR      | OBSOLETE      | TSSOP        | PW                 | 14   |                | TBD             | Call TI                       | Call TI              |              | Y2932                   |         |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

PW (R-PDSO-G14)

PLASTIC SMALL OUTLINE

A. An integration of the information o

Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0,15 each side.

Body width does not include interlead flash. Interlead flash shall not exceed 0,25 each side.

E. Falls within JEDEC MO-153

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated