TPS1HB16-Q1 SLVSE17B - MAY 2019 - REVISED FEBRUARY 2023

# TPS1HB16-Q1 40-V, 16-mΩ Single-Channel Automotive Smart High-Side Switch

### 1 Features

- AEC-Q100 qualified for automotive applications

- Temperature grade 1: –40°C to 125°C

- Device HBM ESD classification level 2

- Device CDM ESD classification level C4B

- Withstands 40-V load dump

- · Functional Safety-Capable

- Documentation available to aid functional safety system design

- Single-channel smart high-side switch with 16-m $\Omega$  $R_{ON} (T_J = 25^{\circ}C)$

- Improve system level reliability through adjustable current limiting

- Current limit set-point from 4.4 A to 49 A

- Robust integrated output protection:

- Integrated thermal protection

- Protection against short to ground and battery

- Protection against reverse battery events including automatic switch on of FET with reverse voltage

- Automatic shut off on loss of battery and ground

- Integrated output clamp to demagnetize inductive loads

- Configurable fault handling

- Analog sense output can be configured to accurately measure:

- Load current

- Device temperature

- Provides fault indication through SNS pin

- Detection of open load and short-to-battery

# 2 Applications

- Automotive display module

- **ADAS** modules

- Seat comfort module

- Transmission control unit

- **HVAC** control module

- Body control modules

- Incandescent and LED lighting

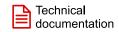

## 3 Description

The TPS1HB16-Q1 device is a smart high-side switch intended for use in 12-V automotive systems. The device integrates robust protection and diagnostic features to ensure output port protection even during harmful events like short circuits in automotive systems. The device protects against faults through a reliable current limit, which, depending on device variant, is adjustable from 4.4 A to 49 A. The high current limit range allows for usage in loads that require large transient currents, while the low current limit range provides improved protection for loads that do not require high peak current. The device is capable of reliably driving a wide range of load profiles.

The TPS1HB16-Q1 also provides a high accuracy analog current sense that allows for improved load diagnostics. By reporting load current and device temperature to a system MCU, the device enables predictive maintenance and load diagnostics that improves the system lifetime.

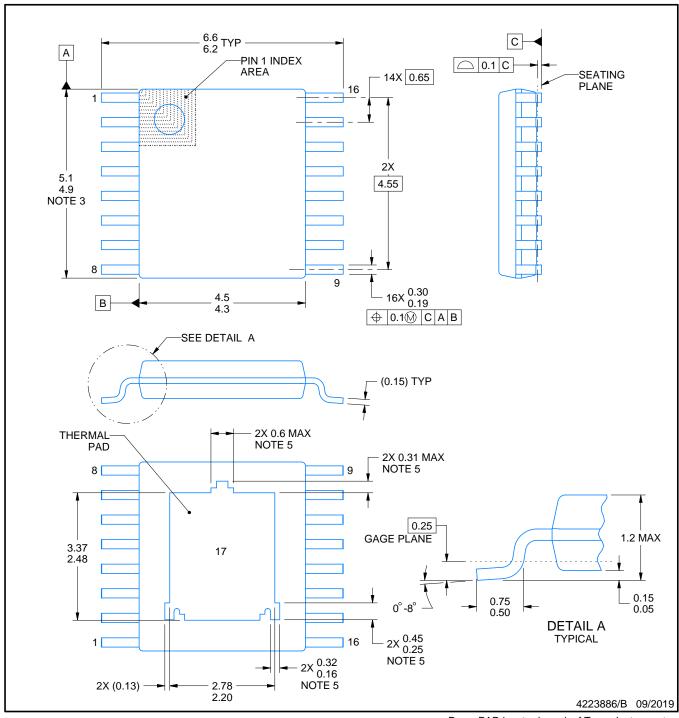

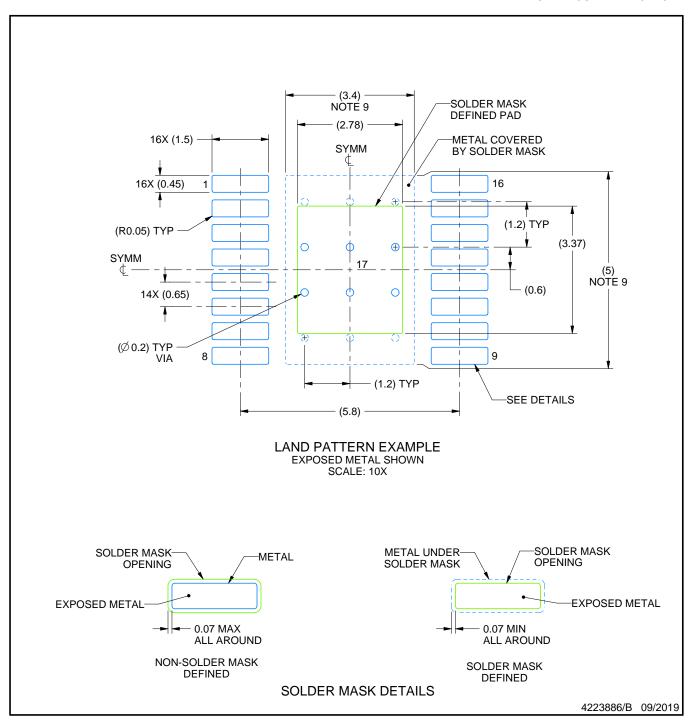

The TPS1HB16-Q1 is available in a HTSSOP package which allows for reduced PCB footprint.

#### **Package Information**

| PART NUMBER (1) | PACKAGE     | BODY SIZE (NOM)   |

|-----------------|-------------|-------------------|

| TPS1HB16-Q1     | HTSSOP (16) | 5.00 mm × 4.40 mm |

For all available packages, see the orderable addendum at the end of the data sheet.

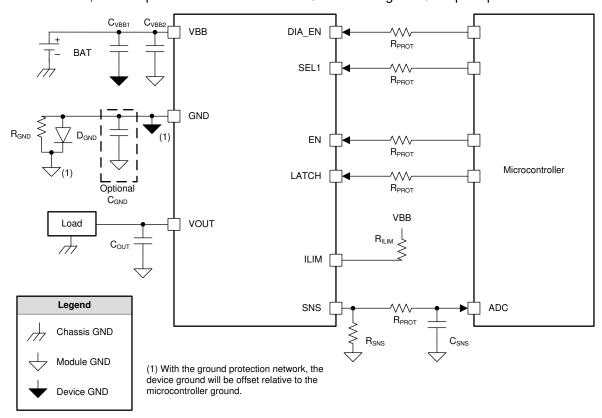

Simplified Schematic

# **Table of Contents**

| 1 Features1                                  | 9.2 Functional Block Diagram19                          |

|----------------------------------------------|---------------------------------------------------------|

| 2 Applications1                              | 9.3 Feature Description19                               |

| 3 Description1                               | 9.4 Device Functional Modes30                           |

| 4 Revision History2                          | 10 Application and Implementation32                     |

| 5 Device Comparison Table3                   | 10.1 Application Information32                          |

| 6 Pin Configuration and Functions4           | 10.2 Typical Application35                              |

| 6.1 Recommended Connections for Unused Pins5 | 10.3 Typical Application41                              |

| 7 Specifications6                            | 10.4 Power Supply Recommendations44                     |

| 7.1 Absolute Maximum Ratings6                | 10.5 Layout44                                           |

| 7.2 ESD Ratings6                             | 11 Device and Documentation Support46                   |

| 7.3 Recommended Operating Conditions6        | 11.1 Documentation Support46                            |

| 7.4 Thermal Information7                     | 11.2 Receiving Notification of Documentation Updates 46 |

| 7.5 Electrical Characteristics7              | 11.3 Support Resources46                                |

| 7.6 SNS Timing Characteristics9              | 11.4 Trademarks46                                       |

| 7.7 Switching Characteristics10              | 11.5 Electrostatic Discharge Caution46                  |

| 7.8 Typical Characteristics11                | 11.6 Glossary46                                         |

| 8 Parameter Measurement Information16        | 12 Mechanical, Packaging, and Orderable                 |

| 9 Detailed Description18                     | Information46                                           |

| 9.1 Overview                                 |                                                         |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| С | hanges from Revision A (April 2020) to Revision B (February 2023)                                                                                                  | Page |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|   | Updated the numbering format for tables, figures and cross-references throughout the document  Addition of V <sub>SC</sub> parameter to the Specifications section |      |

| С | hanges from Revision * (May 2019) to Revision A (April 2020)                                                                                                       | Page |

| • | Changed status from Advance Information to Production Data                                                                                                         | 1    |

| • | Added device variant F to the data sheet                                                                                                                           | 3    |

# **5 Device Comparison Table**

# Table 5-1. Device Options

| DEVICE<br>VERSION | PART NUMBER           | T NUMBER CURRENT LIMIT CURRENT LIMIT R |               | OVERCURRENT BEHAVIOR       |

|-------------------|-----------------------|----------------------------------------|---------------|----------------------------|

| Α                 | TPS1HB16 <b>A</b> -Q1 | Resistor Programmable                  | 4.4 A to 22 A | Disable switch immediately |

| В                 | TPS1HB16 <b>B</b> -Q1 | Resistor Programmable                  | 9.8 A to 49 A | Disable switch immediately |

| F                 | TPS1HB16 <b>F</b> -Q1 | Internally set                         | 60 A          | Disable switch immediately |

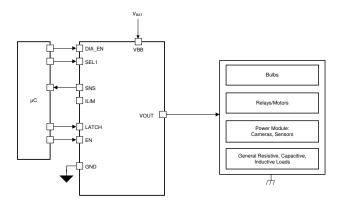

# **6 Pin Configuration and Functions**

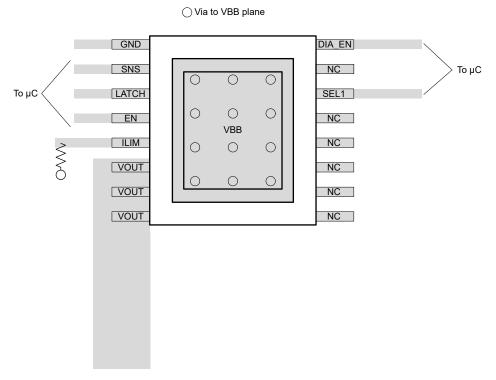

Figure 6-1. PWP Package 16-Pin HTSSOP Top View

**Table 6-1. Pin Functions**

| P      | IN             |              |     |                                                                                                                |  |  |  |

|--------|----------------|--------------|-----|----------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME   | VERSION<br>A/B | VERSION<br>F | I/O | DESCRIPTION                                                                                                    |  |  |  |

| GND    | 1              | 1            | _   | Device ground                                                                                                  |  |  |  |

| SNS    | 2              | 2            | 0   | Sense output                                                                                                   |  |  |  |

| LATCH  | 3              | 3            | I   | Sets fault handling behavior (latched or auto-retry)                                                           |  |  |  |

| EN     | 4              | 4            | I   | Control input, active high                                                                                     |  |  |  |

| ILIM   | 5              | -            | 0   | Connect resistor to set current-limit threshold                                                                |  |  |  |

| FLT    | -              | 5            | 0   | Open drain output with pulldown to signal fault.                                                               |  |  |  |

| VOUT   | 6 - 8          | 6 - 8        | 0   | Channel output                                                                                                 |  |  |  |

| NC     | 9 - 13, 15     | 9 - 13, 15   | I   | No Connect, leave floating                                                                                     |  |  |  |

| SEL1   | 14             | 14           | I   | Diagnostics select. No functionality on device version F; connect to IC GND through R <sub>PROT</sub> resistor |  |  |  |

| DIA_EN | 16             | 16           | I   | Diagnostic enable, active high                                                                                 |  |  |  |

| VBB    | Exposed pad    | Exposed pad  | I   | Power supply input                                                                                             |  |  |  |

Product Folder Links: TPS1HB16-Q1

# **6.1 Recommended Connections for Unused Pins**

The TPS1HB16-Q1 is designed to provide an enhanced set of diagnostic and protection features. However, if the system design only allows for a limited number of I/O connections, some pins can be considered as optional.

**Table 6-2. Connections For Optional Pins**

|                          | Table of El Collinous Coll Optional Time           |                                                                                                                                                                                                                                               |  |  |  |  |  |

|--------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| PIN NAME                 | CONNECTION IF NOT USED                             | IMPACT IF NOT USED                                                                                                                                                                                                                            |  |  |  |  |  |

| SNS                      | Ground through 1-kΩ resistor                       | Analog sense is not available.                                                                                                                                                                                                                |  |  |  |  |  |

| LATCH                    | Float or ground through R <sub>PROT</sub> resistor | With LATCH unused, the device auto-retries after a fault. If latched behavior is desired, but the system describes limited I/O, it is possible to use one microcontroller output to control the latch function of several high-side channels. |  |  |  |  |  |

| ILIM (Version A/B) Float |                                                    | If the ILIM pin is left floating, the device is set to the default internal current-limit threshold.                                                                                                                                          |  |  |  |  |  |

| FAULT (Version F)        | Float                                              | Open drain FAULT signal is not able to be used                                                                                                                                                                                                |  |  |  |  |  |

| SEL1                     | Ground through RPROT                               | SEL1 selects the TJ sensing feature. With SEL1 unused, only current sensing and open load detection are available. If unused, must be grounded through a resistor to engage FET turn-on during reverse battery.                               |  |  |  |  |  |

| DIA_EN                   | Float or ground through R <sub>PROT</sub> resistor | With DIA_EN unused, the analog sense, open-load, and short-to-battery diagnostics are not available.                                                                                                                                          |  |  |  |  |  |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                           | ,                                                                       | MIN | MAX               | UNIT |

|-----------------------------------------------------------|-------------------------------------------------------------------------|-----|-------------------|------|

| Maximum continuous supply voltage, V <sub>BB</sub>        |                                                                         |     | 36                | V    |

| Load dump voltage, V <sub>LD</sub>                        | ISO16750-2:2010(E)                                                      |     | 40                | V    |

| Reverse battery voltage, V <sub>Rev</sub> , t ≤ 3 minutes |                                                                         | -18 |                   | V    |

| Enable pin voltage, V <sub>EN</sub>                       |                                                                         | -1  | 7                 | V    |

| LATCH pin voltage, V <sub>LATCH</sub>                     |                                                                         | -1  | 7                 | V    |

| Diagnostic Enable pin voltage, V <sub>DIA_EN</sub>        |                                                                         | -1  | 7                 | V    |

| Sense pin voltage, V <sub>SNS</sub>                       |                                                                         | -1  | 18                | V    |

| Select pin voltage, V <sub>SEL1</sub>                     |                                                                         | -1  | 7                 | V    |

| Reverse ground current, I <sub>GND</sub>                  | V <sub>BB</sub> < 0 V                                                   |     | -50               | mA   |

| Energy dissipation during turnoff, E <sub>TOFF</sub>      | Single pulse, L <sub>OUT</sub> = 5 mH, T <sub>J,start</sub> = 125°C     |     | 34 <sup>(2)</sup> | mJ   |

| Energy dissipation during turnoff, E <sub>TOFF</sub>      | Repetitive pulse, L <sub>OUT</sub> = 5 mH, T <sub>J,start</sub> = 125°C |     | 14 <sup>(2)</sup> | mJ   |

| Maximum junction temperature, T <sub>J</sub>              |                                                                         |     | 150               | °C   |

| Storage temperature, T <sub>stg</sub>                     |                                                                         | -65 | 150               | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|                    |               |                                                         |                              | VALUE | UNIT |

|--------------------|---------------|---------------------------------------------------------|------------------------------|-------|------|

|                    | Electrostatic | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> | All pins except VBB and VOUT | ±2000 |      |

| V <sub>(ESD)</sub> | discharge     |                                                         | VBB and VOUT                 | ±4000 | V    |

|                    |               | Charged-device model (CDM), per AEC Q100-011            | All pins                     | ±750  |      |

<sup>(1)</sup> AEC-Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specifications.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted) (1)

|                     |                                               | MIN | MAX | UNIT |

|---------------------|-----------------------------------------------|-----|-----|------|

| $V_{BB}$            | Nominal supply voltage (1)                    | 6   | 18  | V    |

| $V_{BB}$            | Extended lower supply voltage                 | 3   | 6   | V    |

| V <sub>BB</sub>     | Extended higher supply voltage <sup>(2)</sup> | 18  | 28  | V    |

| V <sub>EN</sub>     | Enable voltage                                | -1  | 5.5 | V    |

| V <sub>LATCH</sub>  | LATCH voltage                                 | -1  | 5.5 | V    |

| V <sub>DIA_EN</sub> | Diagnostic Enable voltage                     | -1  | 5.5 | V    |

| V <sub>SEL1</sub>   | Select voltage                                | -1  | 5.5 | V    |

| V <sub>SNS</sub>    | Sense voltage                                 | -1  | 7   | V    |

<sup>(1)</sup> All operating voltage conditions are measured with respect to device GND

Product Folder Links: TPS1HB16-Q1

<sup>(2)</sup> For further details, see the section regarding switch-off of an inductive load.

<sup>(2)</sup> All parameters specified are still valid, short circuit protection valide to value specified by V<sub>SC</sub> parameter

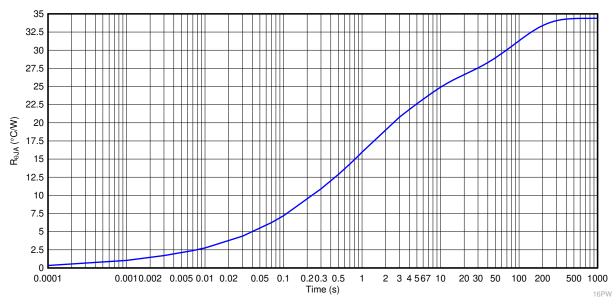

# 7.4 Thermal Information

|                       |                                              | TPS1HB16-Q1  |      |

|-----------------------|----------------------------------------------|--------------|------|

|                       | THERMAL METRIC (1) (2)                       | PWP (HTSSOP) | UNIT |

|                       |                                              | 16 PINS      |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 34.3         | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 31.2         | °C/W |

| R <sub>0JB</sub>      | Junction-to-board thermal resistance         | 10.8         | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 2.4          | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 10.8         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.6          | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 7.5 Electrical Characteristics

$V_{BB}$  = 6 V to 18 V,  $T_{J}$  = -40°C to 150°C (unless otherwise noted)

|                            | PARAMETER                                    | TEST CONDITIONS                                                                                                              | MIN | TYP  | MAX | UNIT |

|----------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| INPUT VOL                  | TAGE AND CURRENT                             |                                                                                                                              |     |      | •   |      |

| V <sub>DSCLAMP</sub>       | V <sub>DS</sub> clamp voltage                |                                                                                                                              | 40  |      | 46  | V    |

| V <sub>BBCLAMP</sub>       | V <sub>BB</sub> clamp voltage                |                                                                                                                              | 58  |      | 76  | V    |

| V <sub>UVLOF</sub>         | V <sub>BB</sub> undervoltage lockout falling | Measured with respect to the GND pin of the device                                                                           | 2.0 |      | 3   | V    |

| V <sub>UVLOR</sub>         | V <sub>BB</sub> undervoltage lockout rising  | Measured with respect to the GND pin of the device                                                                           | 2.2 |      | 3   | V    |

| l <sub>SB</sub> d          | Standby current (total                       | V <sub>BB</sub> = 13.5 V, T <sub>J</sub> = 25°C<br>V <sub>EN</sub> = V <sub>DIA_EN</sub> = 0 V, V <sub>OUT</sub> = 0 V       |     |      | 0.1 | μΑ   |

|                            | device leakage including MOSFET channel)     | V <sub>BB</sub> = 13.5 V, T <sub>J</sub> = 85°C,<br>V <sub>EN</sub> = V <sub>DIA_EN</sub> = 0 V, V <sub>OUT</sub> = 0 V      |     |      | 0.5 | μΑ   |

| IL <sub>NOM</sub>          | Continuous load current                      | T <sub>AMB</sub> = 70°C                                                                                                      |     | 7    |     | Α    |

|                            | Output leakage current                       | V <sub>BB</sub> = 13.5 V, T <sub>J</sub> = 25°C<br>V <sub>EN</sub> = V <sub>DIA_EN</sub> = 0 V, V <sub>OUT</sub> = 0 V       |     | 0.01 | 0.1 | μΑ   |

| I <sub>OUT</sub> (standby) |                                              | V <sub>BB</sub> = 13.5 V, T <sub>J</sub> = 125°C<br>V <sub>EN</sub> = V <sub>DIA_EN</sub> = 0 V, V <sub>OUT</sub> = 0 V      |     |      | 1.5 | μΑ   |

| I <sub>DIA</sub>           | Current consumption in diagnostic mode       | V <sub>BB</sub> = 13.5 V, I <sub>SNS</sub> = 0 mA<br>V <sub>EN</sub> = 0 V, V <sub>DIA_EN</sub> = 5 V, V <sub>OUT</sub> = 0V |     | 3    | 6   | mA   |

| IQ                         | Quiescent current                            | V <sub>BB</sub> = 13.5 V<br>V <sub>EN</sub> = V <sub>DIA_EN</sub> = 5 V, I <sub>OUT</sub> = 0 A                              |     | 3    | 6   | mA   |

| t <sub>STBY</sub>          | Standby mode delay time                      | V <sub>EN</sub> = V <sub>DIA_EN</sub> = 0 V to standby                                                                       | 12  | 17   | 22  | ms   |

| RON CHAR                   | ACTERISTICS                                  |                                                                                                                              |     |      |     |      |

|                            | On-resistance                                | $T_J = 25^{\circ}C, 6 \text{ V} \le V_{BB} \le 28 \text{ V}$                                                                 |     | 16   |     | mΩ   |

| R <sub>ON</sub>            | (Includes MOSFET and                         | T <sub>J</sub> = 150°C, 6 V ≤ V <sub>BB</sub> ≤ 28 V                                                                         |     |      | 32  | mΩ   |

|                            | package)                                     | $T_J = 25^{\circ}C, 3 \text{ V} \le V_{BB} \le 6 \text{ V}$                                                                  |     |      | 30  | mΩ   |

| D                          | On-resistance during                         | $T_J = 25^{\circ}C$ , -18 V $\leq V_{BB} \leq$ -8 V                                                                          |     | 16   |     | mΩ   |

| R <sub>ON(REV)</sub>       | reverse polarity                             | $T_J = 105^{\circ}C, -18 \text{ V} \le V_{BB} \le -8 \text{ V}$                                                              |     |      | 39  | mΩ   |

| CURRENT                    | SENSE CHARACTERISTIC                         | cs                                                                                                                           |     |      |     |      |

| K <sub>SNS</sub>           | Current sense ratio                          | I <sub>OUT</sub> = 1 A                                                                                                       |     | 3000 |     |      |

<sup>(2)</sup> The thermal parameters are based on a 4-layer PCB according to the JESD51-5 and JESD51-7 standards.

$V_{BB} = 6 \text{ V}$  to 18 V,  $T_{J} = -40^{\circ}\text{C}$  to 150°C (unless otherwise noted)

|                        | PARAMETER                                         | TEST CO                                                                                             | ONDITIONS                                                                 | MIN      | TYP     | MAX      | UNIT   |

|------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------|---------|----------|--------|

|                        |                                                   |                                                                                                     | I - 0 A                                                                   |          | 2.6     |          | mA     |

|                        |                                                   |                                                                                                     | I <sub>OUT</sub> = 8 A                                                    | -5       |         | 5        | %      |

|                        |                                                   |                                                                                                     | I - 2 A                                                                   |          | 1.000   |          | mA     |

|                        |                                                   |                                                                                                     | I <sub>OUT</sub> = 3 A                                                    | -5       |         | 5        | %      |

|                        |                                                   |                                                                                                     |                                                                           |          | 0.333   |          | mA     |

|                        |                                                   |                                                                                                     | I <sub>OUT</sub> = 1 A                                                    | -5       |         | 5        | %      |

|                        | Current sense current                             | $V_{EN} = V_{DIA EN} = 5 V$                                                                         |                                                                           |          | 0.101   |          | mA     |

| I <sub>SNSI</sub>      | and accuracy                                      | V <sub>SEL1</sub> = 0 V                                                                             | I <sub>OUT</sub> = 300 mA                                                 | -6       | -       | 6        | %      |

|                        |                                                   |                                                                                                     |                                                                           |          | 0.03438 |          | mA     |

|                        |                                                   |                                                                                                     | I <sub>OUT</sub> = 100 mA                                                 | -11      |         | 11       | %      |

|                        |                                                   |                                                                                                     |                                                                           |          | 0.0174  |          | mA     |

|                        |                                                   |                                                                                                     | I <sub>OUT</sub> = 50 mA                                                  | -18      |         | 18       | %      |

|                        |                                                   |                                                                                                     |                                                                           |          | 0.00737 |          | mA     |

|                        |                                                   |                                                                                                     | I <sub>OUT</sub> = 20 mA                                                  | -38      |         | 38       | %      |

| TJ SENSE               | E CHARACTERISTICS                                 | I                                                                                                   |                                                                           | <u> </u> |         | - 1      |        |

|                        |                                                   |                                                                                                     | T <sub>J</sub> = -40°C                                                    | 0.01     | 0.12    | 0.38     | mA     |

| I <sub>SNST</sub>      |                                                   | V <sub>DIA_EN</sub> = 5 V, V <sub>SEL1</sub> = 5 V                                                  | T <sub>J</sub> = 25°C                                                     | 0.72     | 0.85    | 0.98     | mA     |

|                        | Temperature sense                                 |                                                                                                     | T <sub>J</sub> = 85°C                                                     | 1.25     | 1.52    | 1.79     | mA     |

|                        | current                                           |                                                                                                     | T <sub>J</sub> = 125°C                                                    | 1.61     | 1.96    | 2.31     | mA     |

|                        |                                                   |                                                                                                     | T <sub>J</sub> = 150°C                                                    | 1.80     | 2.25    | 2.70     | mA     |

| dl <sub>SNST</sub> /dT | Coefficient                                       |                                                                                                     | 11 100 0                                                                  | 1.00     | 0.0112  | 2.70     | mA/°C  |

|                        | RACTERISTICS                                      |                                                                                                     |                                                                           |          | 0.0112  |          | 111/0  |

|                        | I <sub>SNS</sub> fault high-level                 | V <sub>DIA EN</sub> = 5 V, V <sub>SEL1</sub> = 0                                                    |                                                                           | 4        | 4.5     | 5.3      | mA     |

| I <sub>SNSFH</sub>     | I <sub>SNS</sub> leakage                          | $V_{DIA\_EN} = 0 V$                                                                                 | v                                                                         |          | 4.5     | 1        | μA     |

| I <sub>SNSleak</sub>   | T LIMIT CHARACTERISTIC                            | _                                                                                                   |                                                                           |          |         | <u>'</u> | μΑ     |

| CORREN                 | I LIWIT CHARACTERISTIC                            |                                                                                                     |                                                                           |          |         | 18       | V      |

| \/                     | Short Circuit Maximum                             | Version B                                                                                           | Version A                                                                 |          | -       | 18       | V      |

| $V_{SC}$               | Supply Voltage                                    |                                                                                                     |                                                                           |          |         |          |        |

|                        |                                                   | Version F                                                                                           | D OND                                                                     |          |         | 18       | V      |

|                        |                                                   | Device Version A, T <sub>J</sub> = -40°C to 150°C                                                   | R <sub>ILIM</sub> = GND, open, or out of range                            |          | 28.6    |          | Α      |

|                        |                                                   |                                                                                                     | $R_{ILIM} = 5 k\Omega$                                                    | 18.16    | 22      | 28       | Α      |

|                        |                                                   |                                                                                                     | $R_{ILIM} = 25 \text{ k}\Omega$                                           | 2.62     | 4.4     | 5.7      | Α      |

| I <sub>CL</sub>        | Current limit threshold                           | Device Version B, T,I =                                                                             | R <sub>ILIM</sub> = GND, open, or out of range                            |          | 70      |          | Α      |

|                        |                                                   | -40°C to 150°C                                                                                      | $R_{ILIM} = 5 k\Omega$                                                    | 40.44    | 49      | 62.4     | Α      |

|                        |                                                   |                                                                                                     | $R_{ILIM} = 25 \text{ k}\Omega$                                           | 8        | 9.8     | 11.76    | Α      |

|                        |                                                   | Davies Versien F                                                                                    | T <sub>J</sub> = 25°C                                                     | 53       | 60      | 72       | Α      |

|                        |                                                   | Device Version F                                                                                    | T <sub>J</sub> = 150°C                                                    | 42       | 47      | 56       | Α      |

|                        | Command Lineid Dadia                              | Version A                                                                                           |                                                                           |          | 110     |          | A * kΩ |

| K <sub>CL</sub>        | Current Limit Ratio                               | Version B                                                                                           |                                                                           |          | 245     |          | A * kΩ |

| FAULT CH               | HARACTERISTICS                                    | 1                                                                                                   |                                                                           |          |         | 1        |        |

| V <sub>OL</sub>        | Open-load (OL) detection voltage                  | V <sub>EN</sub> = 0 V, V <sub>DIA_EN</sub> = 5 V,                                                   | V <sub>EN</sub> = 0 V, V <sub>DIA_EN</sub> = 5 V, V <sub>SEL1</sub> = 0 V |          | 3       | 4        | V      |

| t <sub>OL1</sub>       | OL and STB indication-<br>time from EN falling    | $V_{EN}$ = 5 V to 0 V, $V_{DIA\_EN}$<br>$I_{OUT}$ = 0 mA, $V_{OUT}$ = 4 V                           | = 5 V, V <sub>SEL1</sub> = 0 V                                            | 300      | 500     | 700      | μs     |

| t <sub>OL2</sub>       | OL and STB indication-<br>time from DIA_EN rising | V <sub>EN</sub> = 0 V, V <sub>DIA_EN</sub> = 0 V<br>I <sub>OUT</sub> = 0 mA, V <sub>OUT</sub> = 4 V | to 5 V, V <sub>SEL1</sub> = 0 V                                           | 2        | 20      | 50       | μs     |

$V_{BB}$  = 6 V to 18 V,  $T_{J}$  = -40°C to 150°C (unless otherwise noted)

|                              | PARAMETER                                       | TEST CONDITIONS                                                                                                                     | MIN | TYP | MAX | UNIT |

|------------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>OL3</sub>             | OL and STB indication-<br>time from VOUT rising | V <sub>EN</sub> = 0 V, V <sub>DIA_EN</sub> = 5 V, V <sub>SEL1</sub> = 0 V<br>I <sub>OUT</sub> = 0 mA, V <sub>OUT</sub> = 0 V to 4 V | 2   | 20  | 50  | μs   |

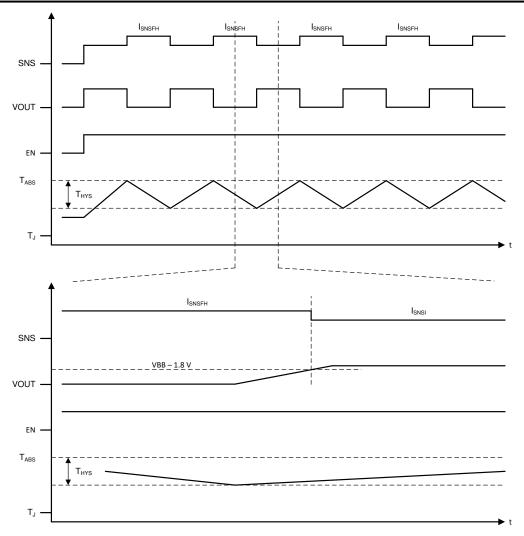

| T <sub>ABS</sub>             | Thermal shutdown                                |                                                                                                                                     | 150 |     |     | °C   |

| T <sub>HYS</sub>             | Thermal shutdown hysteresis                     |                                                                                                                                     | 20  | 25  | 30  | °C   |

| t <sub>FAULT</sub>           | Fault shutdown indication-time                  | V <sub>DIA_EN</sub> = 5 V<br>Time between switch shutdown and I <sub>SNS</sub> settling at<br>I <sub>SNSFH</sub>                    |     |     | 50  | μs   |

| t <sub>RETRY</sub>           | Retry time                                      | Time from fault shutdown until switch re-enable (thermal shutdown or current limit).                                                | 1   | 2   | 3   | ms   |

| EN PIN CH                    | ARACTERISTICS                                   |                                                                                                                                     |     |     | '   |      |

| V <sub>IL, EN</sub>          | Input voltage low-level                         | No GND network diode                                                                                                                |     |     | 0.8 | V    |

| V <sub>IH, EN</sub>          | Input voltage high-level                        | No GND network diode                                                                                                                | 2.0 |     |     | V    |

| V <sub>IHYS, EN</sub>        | Input voltage hysteresis                        |                                                                                                                                     |     | 350 |     | mV   |

| R <sub>EN</sub>              | Internal pulldown resistor                      |                                                                                                                                     | 0.5 | 1   | 2   | ΜΩ   |

| I <sub>IL, EN</sub>          | Input current low-level                         | V <sub>EN</sub> = 0.8 V                                                                                                             |     | 0.8 |     | μΑ   |

| I <sub>IH, EN</sub>          | Input current high-level                        | V <sub>EN</sub> = 5 V                                                                                                               |     | 5.0 |     | μΑ   |

| DIA_EN PI                    | N CHARACTERISTICS                               |                                                                                                                                     |     |     |     |      |

| V <sub>IL, DIA_EN</sub>      | Input voltage low-level                         | No GND network diode                                                                                                                |     |     | 8.0 | V    |

| V <sub>IH, DIA_EN</sub>      | Input voltage high-level                        | No GND network diode                                                                                                                | 2.0 |     |     | V    |

| V <sub>IHYS,</sub><br>DIA_EN | Input voltage hysteresis                        |                                                                                                                                     |     | 350 |     | mV   |

| R <sub>DIA_EN</sub>          | Internal pulldown resistor                      |                                                                                                                                     | 0.5 | 1   | 2   | ΜΩ   |

| I <sub>IL, DIA_EN</sub>      | Input current low-level                         | V <sub>DIA_EN</sub> = 0.8 V                                                                                                         |     | 0.8 |     | μΑ   |

| I <sub>IH, DIA_EN</sub>      | Input current high-level                        | V <sub>DIA_EN</sub> = 5 V                                                                                                           |     | 5.0 |     | μΑ   |

| SEL1 PIN (                   | CHARACTERISTICS                                 |                                                                                                                                     |     |     | '   |      |

| V <sub>IL, SEL1</sub>        | Input voltage low-level                         | No GND network diode                                                                                                                |     |     | 0.8 | V    |

| V <sub>IH, SEL1</sub>        | Input voltage high-level                        | No GND network diode                                                                                                                | 2.0 |     |     | V    |

| V <sub>IHYS, SEL1</sub>      | Input voltage hysteresis                        |                                                                                                                                     |     | 350 |     | mV   |

| R <sub>SEL1</sub>            | Internal pulldown resistor                      |                                                                                                                                     | 0.5 | 1   | 2   | ΜΩ   |

| I <sub>IL, SEL1</sub>        | Input current low-level                         | V <sub>SEL1</sub> = 0.8 V                                                                                                           |     | 0.8 |     | μA   |

| I <sub>IH, SEL1</sub>        | Input current high-level                        | V <sub>SEL1</sub> = 5 V                                                                                                             |     | 5.0 |     | μA   |

| LATCH PIN                    | CHARACTERISTICS                                 |                                                                                                                                     |     |     | '   |      |

| V <sub>IL, LATCH</sub>       | Input voltage low-level                         | No GND network diode                                                                                                                |     |     | 8.0 | V    |

| V <sub>IH, LATCH</sub>       | Input voltage high-level                        | No GND network diode                                                                                                                | 2.0 | ,   |     | V    |

| V <sub>IHYS,</sub><br>LATCH  | Input voltage hysteresis                        |                                                                                                                                     |     | 350 |     | mV   |

| R <sub>LATCH</sub>           | Internal pulldown resistor                      |                                                                                                                                     | 0.5 | 1   | 2   | ΜΩ   |

| I <sub>IL, LATCH</sub>       | Input current low-level                         | V <sub>LATCH</sub> = 0.8 V                                                                                                          |     | 0.8 |     | μA   |

| I <sub>IH, LATCH</sub>       | Input current high-level                        | V <sub>LATCH</sub> = 5 V                                                                                                            |     | 5   |     | μA   |

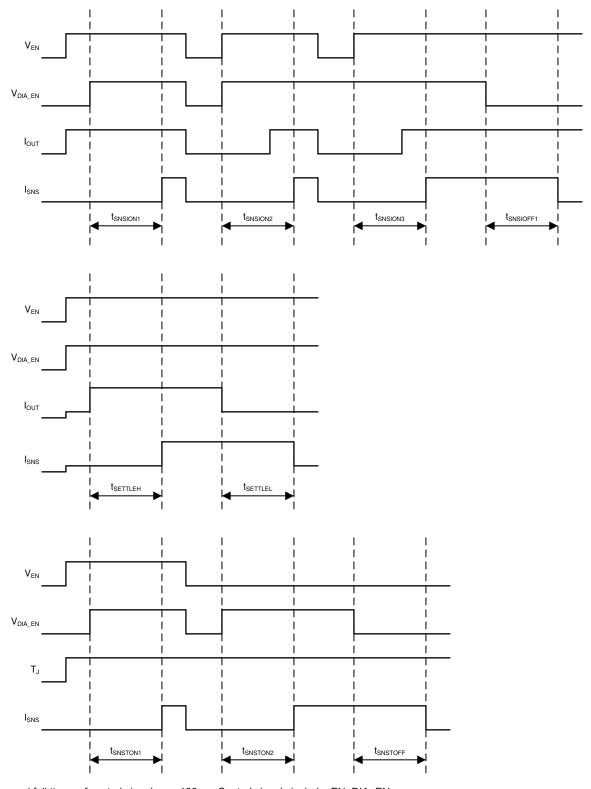

# 7.6 SNS Timing Characteristics

$V_{BB} = 6 \text{ V to } 18 \text{ V}, T_{J} = -40 ^{\circ}\text{C to } +150 ^{\circ}\text{C} \text{ (unless otherwise noted)}$

|                      | PARAMETER                                | TEST CONDITIONS                                                                          | MIN | TYP | MAX | UNIT |

|----------------------|------------------------------------------|------------------------------------------------------------------------------------------|-----|-----|-----|------|

| SNS TIMIN            | G - CURRENT SENSE                        |                                                                                          |     | ,   |     |      |

| t <sub>SNSION1</sub> | Settling time from rising edge of DIA_EN | $V_{EN}$ = 5 V, $V_{DIA\_EN}$ = 0 V to 5 V $R_{SNS}$ = 1 k $\Omega$ , $R_L$ ≤ 4 $\Omega$ |     |     | 40  | μs   |

# 7.6 SNS Timing Characteristics (continued)

$V_{BB}$  = 6 V to 18 V,  $T_{J}$  = -40°C to +150°C (unless otherwise noted)

|                       | PARAMETER                                             | TEST CONDITIONS                                                                                                                                                                                | MIN | TYP | MAX | UNIT |

|-----------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>SNSION2</sub>  | Settling time from rising edge of EN and DIA_EN       | $V_{EN} = V_{DIA\_EN} = 0 \text{ V to 5 V}$<br>$R_{SNS} = 1 \text{ k}\overline{\Omega}, R_L \le 4 \Omega$                                                                                      |     |     | 200 | μs   |

| t <sub>SNSION3</sub>  | Settling time from rising edge of EN                  | $V_{EN}$ = 0 V to 5 V, $V_{DIA\_EN}$ = 5 V $R_{SNS}$ = 1 k $\Omega$ , $R_L$ $\leq$ 4 $\Omega$                                                                                                  |     |     | 165 | μs   |

| t <sub>SNSIOFF1</sub> | Settling time from falling edge of DIA_EN             | $V_{EN}$ = 5 V, $V_{DIA\_EN}$ = 5 V to 0 V<br>$R_{SNS}$ = 1 k $\Omega$ , $R_L$ ≤ 4 $\Omega$                                                                                                    |     |     | 20  | μs   |

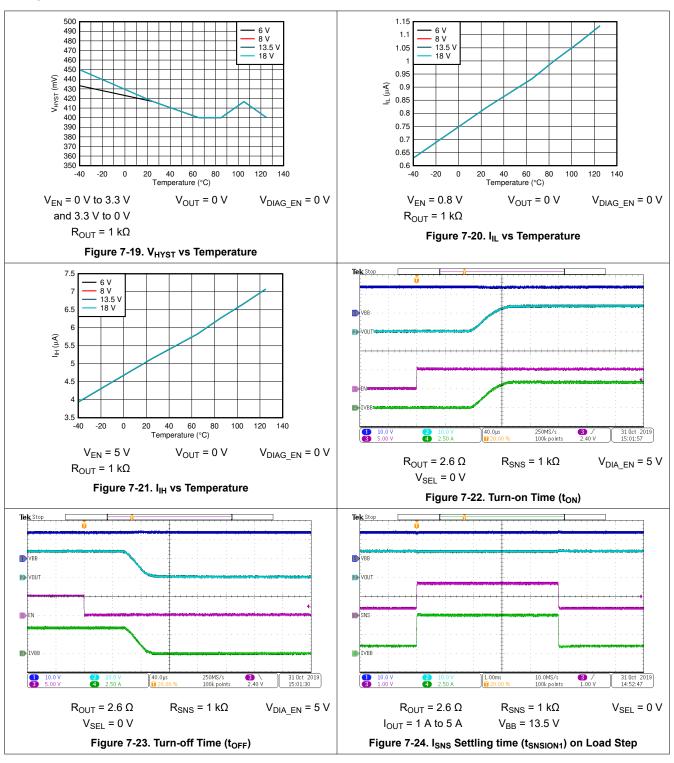

| t <sub>SETTLEH</sub>  | Settling time from rising edge of load step           | $V_{EN} = 5 \text{ V}, V_{DIA\_EN} = 5 \text{ V}$<br>$R_{SNS} = 1 \text{ k}\Omega, I_{OUT} = 1 \text{ A to 5 A}$                                                                               |     |     | 20  | μs   |

| t <sub>SETTLEL</sub>  | Settling time from falling edge of load step          | $V_{EN}$ = 5 V, $V_{DIA\_EN}$ = 5 V<br>R <sub>SNS</sub> = 1 k $\Omega$ , I <sub>OUT</sub> = 5 A to 1 A                                                                                         |     |     | 20  | μs   |

| SNS TIMII             | NG - TEMPERATURE SENSE                                |                                                                                                                                                                                                |     |     |     |      |

| t <sub>SNSTON1</sub>  | Settling time from rising edge of DIA_EN              | $V_{EN}$ = 5 V, $V_{DIA\_EN}$ = 0 V to 5 V $R_{SNS}$ = 1 k $\Omega$                                                                                                                            |     |     | 40  | μs   |

| t <sub>SNSTON2</sub>  | Settling time from rising edge of DIA_EN              | $V_{EN} = 0 \text{ V}, V_{DIA\_EN} = 0 \text{ V to 5 V}$<br>$R_{SNS} = 1 \text{ k}\Omega$                                                                                                      |     |     | 70  | μs   |

| t <sub>SNSTOFF</sub>  | Settling time from falling edge of DIA_EN             | $V_{EN} = X$ , $V_{DIA\_EN} = 5$ V to 0 V $R_{SNS} = 1$ k $\Omega$                                                                                                                             |     |     | 20  | μs   |

| SNS TIMII             | NG - MULTIPLEXER                                      |                                                                                                                                                                                                |     |     |     |      |

| <b>t.</b>             | Settling time from temperature sense to current sense | $\begin{aligned} &V_{EN} = 5 \text{ V, } V_{DIA\_EN} = 5 \text{ V} \\ &V_{SEL1} = 5 \text{ V to } \overline{0} \text{ V} \\ &R_{SNS} = 1 \text{ k}\Omega, \ R_L \leq 4 \ \Omega \end{aligned}$ |     |     | 60  | μs   |

| t <sub>MUX</sub>      | Settling time from current sense to temperature sense | $V_{EN} = 5 \text{ V}, V_{DIA\_EN} = 5 \text{ V}$ $V_{SEL1} = 0 \text{ V to } 5 \text{ V}$ $R_{SNS} = 1 \text{ k}\Omega, R_L \le 4 \Omega$                                                     |     |     | 60  | μs   |

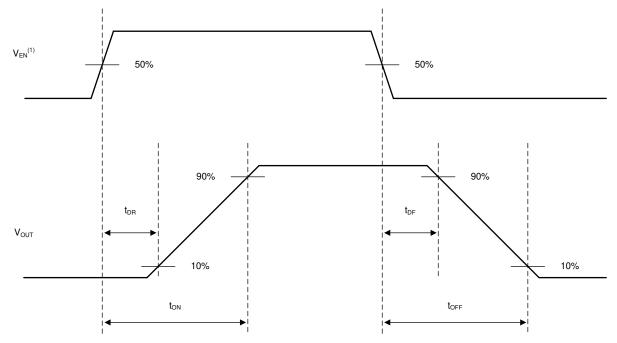

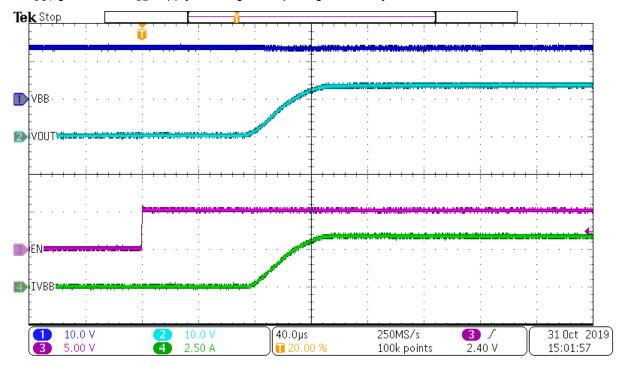

# 7.7 Switching Characteristics

$V_{BB} = 13.5 \text{ V}, T_{J} = -40^{\circ}\text{C} \text{ to } +150^{\circ}\text{C} \text{ (unless otherwise noted)}$

|                                    | PARAMETER                              | TEST CONDITIONS                                                                 | MIN | TYP | MAX | UNIT |

|------------------------------------|----------------------------------------|---------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>DR</sub>                    | Turnon delay time (from Active)        | $V_{BB}$ = 13.5 V, $R_L \le 4 \Omega$ , 50% EN rising to 10% $V_{OUT}$ rising   | 20  | 60  | 100 | μs   |

| t <sub>DF</sub>                    | Turnoff delay time                     | $V_{BB}$ = 13.5 V, $R_L \le 4 \Omega$ , 50% EN falling to 90% $V_{OUT}$ Falling | 20  | 60  | 100 | μs   |

| SR <sub>R</sub>                    | VOUT rising slew rate                  | $V_{BB}$ = 13.5 V, 20% to 80% of $V_{OUT}$ , $R_L \le 4 \Omega$                 | 0.1 | 0.4 | 0.7 | V/µs |

| SR <sub>F</sub>                    | VOUT falling slew rate                 | $V_{BB}$ = 13.5 V, 80% to 20% of $V_{OUT}$ , $R_L \le 4 \Omega$                 | 0.1 | 0.4 | 0.7 | V/µs |

| t <sub>ON</sub>                    | Turnon time (active)                   | $V_{BB}$ = 13.5 V, $R_L \le 4 \Omega$ , 50% EN rising to 80% $V_{OUT}$ rising   | 39  | 94  | 235 | μs   |

| t <sub>OFF</sub>                   | Turnoff time                           | $V_{BB}$ = 13.5 V, $R_L \le 4 \Omega$                                           | 39  | 94  | 235 | μs   |

| $\Delta_{PWM}$                     | PWM accuracy - average load current    | 200-μs enable pulse, $V_S$ = 13.5 V, $R_L$ = 4 $\Omega$                         | -25 | 0   | 25  | %    |

| t <sub>ON</sub> - t <sub>OFF</sub> | Turnon and turnoff matching            | 200-us enable pulse                                                             | -85 | 0   | 85  | μs   |

| E <sub>ON</sub>                    | Switching energy losses during turnon  | $V_{BB} = 13.5 \text{ V}, R_{L} \le 4 \Omega$                                   |     | 0.7 |     | mJ   |

| E <sub>OFF</sub>                   | Switching energy losses during turnoff | $V_{BB} = 13.5 \text{ V}, R_{L} \le 4 \Omega$                                   |     | 0.7 |     | mJ   |

Product Folder Links: TPS1HB16-Q1

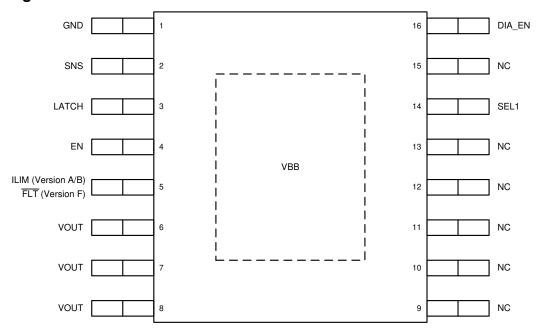

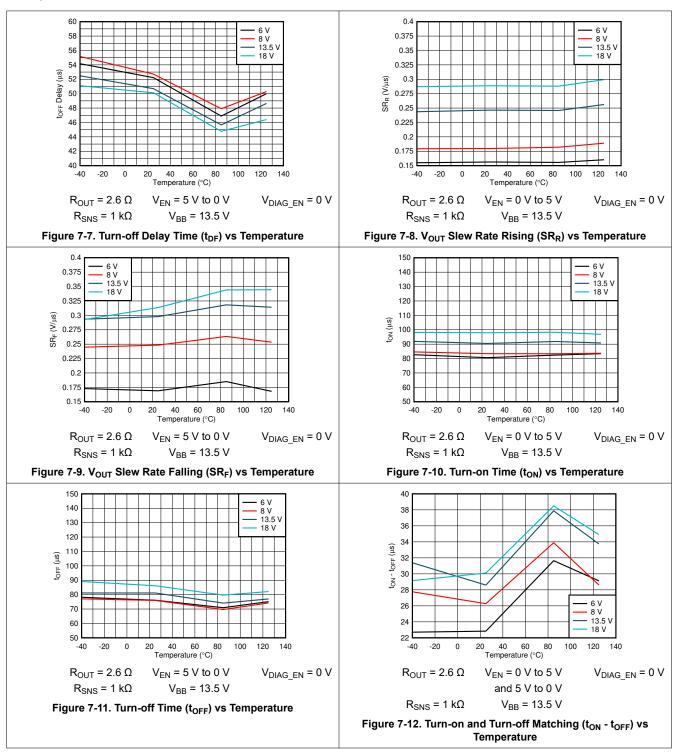

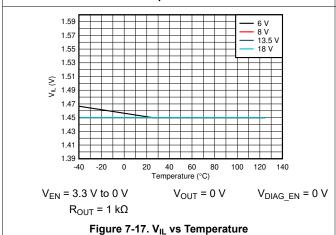

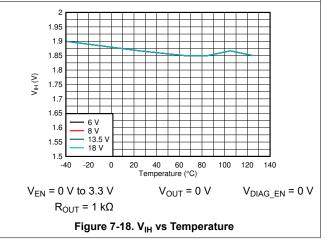

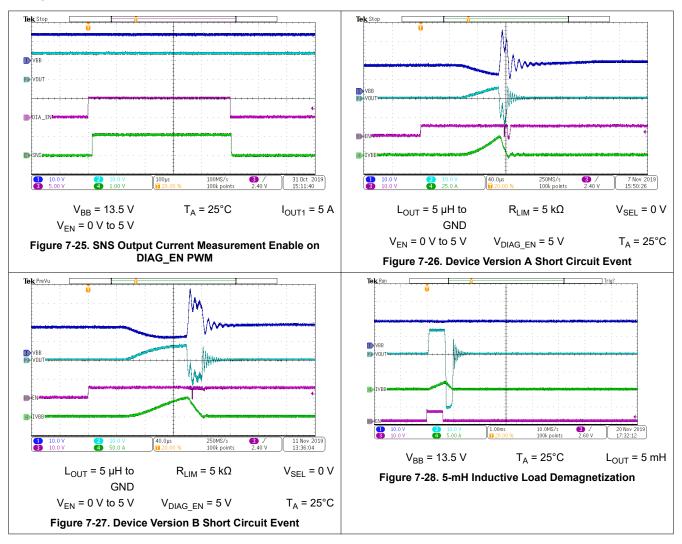

## 7.8 Typical Characteristics

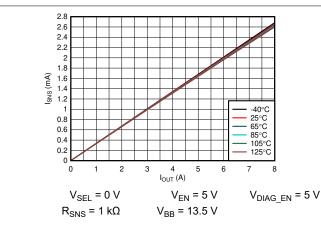

Figure 7-13. Current Sense Output Current (I<sub>SNSI</sub> ) vs Load Current (I<sub>OUT</sub>) Across Temperature

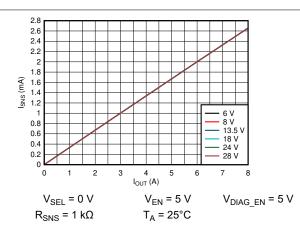

Figure 7-14. Current Sense Output Current (I<sub>SNSI</sub>) vs Load Current (I<sub>OUT</sub>) Across V<sub>BB</sub>

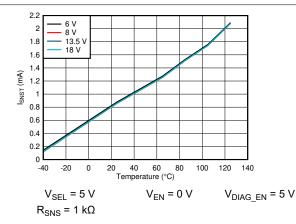

Figure 7-15. Temperature Sense Output Current (I<sub>SNST</sub>) vs Temperature

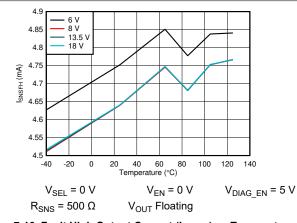

Figure 7-16. Fault High Output Current (I<sub>SNSFH</sub>) vs Temperature

# **8 Parameter Measurement Information**

Figure 8-1. Parameter Definitions

Rise and fall time of V<sub>EN</sub> is 100 ns.

Figure 8-2. Switching Characteristics Definitions

Rise and fall times of control signals are 100 ns. Control signals include: EN, DIA\_EN.

**Figure 8-3. SNS Timing Characteristics Definitions**

# 9 Detailed Description

# 9.1 Overview

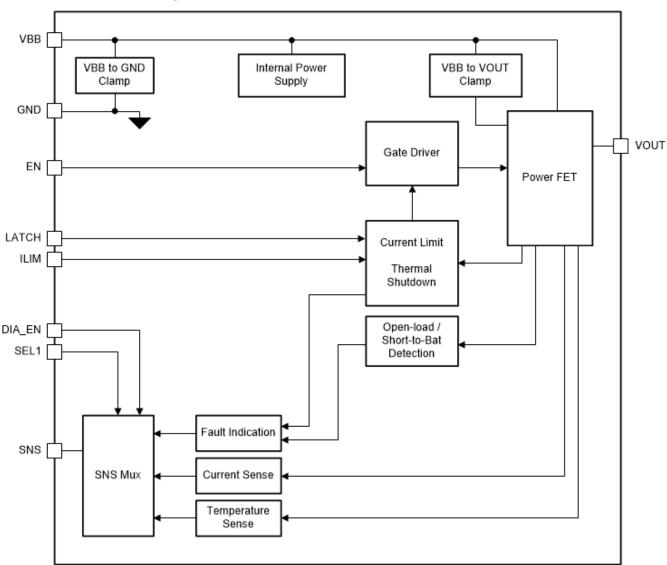

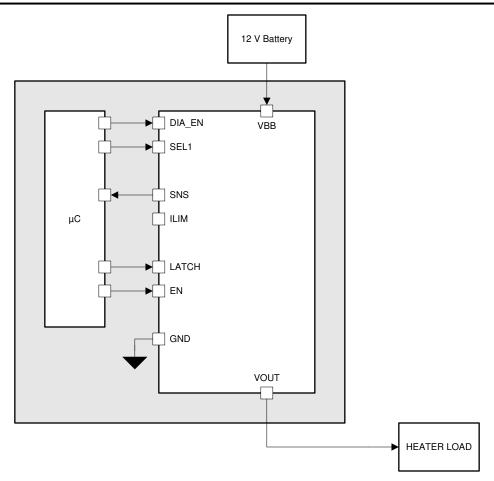

The TPS1HB16-Q1 device is a single-channel smart high-side switch intended for use with 12-V automotive batteries. Many protection and diagnostic features are integrated in the device.

Diagnostics features include the analog SNS output that is capable of providing a signal that is proportional to load current or device temperature. The high-accuracy load current sense allows for diagnostics of complex loads.

This device includes protection through thermal shutdown, current limiting, transient withstand, and reverse battery operation. For more details on the protection features, refer to the *Section 9.3* and *Section 10.1* sections of the document.

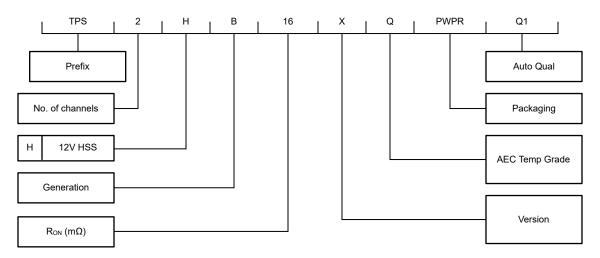

The TPS1HB16-Q1 is one device in a family of TI high side switches. For each device, the part number indicates elements of the device behavior. Figure 9-1 gives an example of the device nomenclature.

Figure 9-1. Naming Convention

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

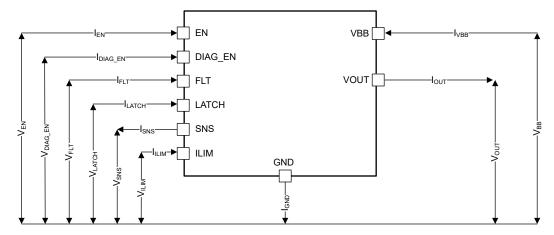

# 9.2 Functional Block Diagram

# 9.3 Feature Description

### 9.3.1 Protection Mechanisms

The TPS1HB16-Q1 is designed to operate in the automotive environment. The protection mechanisms allow the device to be robust against many system-level events such as load dump, reverse battery, short-to-ground, and more.

There are two protection features which, if triggered, will cause the switch to automatically disable:

- Thermal Shutdown

- Current Limit

When any of these protections are triggered, the device will enter the FAULT state. In the FAULT state, the fault indication will be available on the SNS pin (see the *Diagnostic Mechanisms* section of the data sheet for more details).

The switch is no longer held off and the fault indication is reset when all of the below conditions are met:

- LATCH pin is low

- t<sub>RETRY</sub> has expired

- All faults are cleared (thermal shutdown, current limit)

#### 9.3.1.1 Thermal Shutdown

The TPS1HB16-Q1 includes a temperature sensor on the power FET and also within the controller portion of the device. There are two cases that the device will consider to be a thermal shutdown fault:

- $T_{J,FET} > T_{ABS}$

- $(T_{J,FET} T_{J,controller}) > T_{REL}$

After the fault is detected, the switch will turn off. If  $T_{J,FET}$  passes  $T_{ABS}$ , the fault is cleared when the switch temperature decreases by the hysteresis value,  $T_{HYS}$ . If instead the  $T_{REL}$  threshold is exceeded, the fault is cleared after  $T_{RETRY}$  passes.

### 9.3.1.2 Current Limit

When  $I_{OUT}$  reaches the current limit threshold,  $I_{CL}$ , the channel will switch off immediately. The  $I_{CL}$  value will vary with slew rate and a fast current increase that occurs during a powered-on short circuit can temporarily go above the specified  $I_{CL}$  value. When the switch is in the FAULT state, it will output an output current  $I_{SNSFH}$  on the SNS pin .

During a short-circuit event, the device will hit the  $I_{CL}$  value that is listed in the Electrical Characteristics table (for the given device version and  $R_{ILIM}$ ) and then turn the output off to protect the device. The device will register a short-circuit event when the output current exceeds  $I_{CL}$ , however, the measured maximum current can exceed the  $I_{CL}$  value due to the TPS1HB16-Q1 deglitch filter and turn-off time. This deglitch time is defined at 3  $\mu$ s, so use the test setup described in the *AEC-Q100-012 Short Circuit Reliability* section, and take 3  $\mu$ s before the peak value as the  $I_{CL}$ . The device is assured to protect itself during a short-circuit event over the nominal supple voltage range (as defined in the Electrical Characteristics table) at 125°C.

#### 9.3.1.2.1 Current Limit Foldback

Version B of the TPS1HB16-Q1 implements a current limit foldback feature that is designed to protect the device in the case of a long-term fault condition. If the device undergoes fault shutdown events (either of thermal shutdown or current limit) seven consecutive times, the current limit will be reduced to half of the original value. The device will revert back to the original current limit threshold if either of the following occurs:

- · The device goes to standby mode.

- · The switch turns on and turns off without any fault occurring.

Version A does not implement the current limit foldback due to the lower current limit causing less harm during repetitive long-term faults.

#### 9.3.1.2.2 Programmable Current Limit

All versions of the TPS1HB16-Q1 include an adjustable current limit. Some applications (for example, incandescent bulbs) will require a high current limit while other applications can benefit from a lower current limit threshold. In general, wherever possible a lower current limit is recommended due to allowing system advantages through:

- Reduced size and cost in current carrying components such as PCB traces and module connectors

- Less disturbance at the power supply (V<sub>BB</sub> pin) during a short-circuit event

- Improved protection of the downstream load

To set the current limit threshold, connect a resistor from  $I_{LIM}$  to  $V_{BB}$ . The current limit threshold is determined by Equation 1 ( $R_{ILIM}$  in  $k\Omega$ ):

$$I_{CL} = K_{CL} / R_{ILIM}$$

(1)

The  $R_{ILIM}$  range is between 5 k $\Omega$  and 25 k $\Omega$ . An  $R_{ILIM}$  resistor is required, however in the fault case where the pin is floating, grounded, or outside of this range the current limit will default to an internal level that is defined in the *Specifications* section of this document. If  $R_{ILIM}$  is out of this range, the device cannot assure complete short-circuit protection.

#### Note

Capacitance on the  $I_{LIM}$  pin can cause  $I_{LIM}$  to go out of range during short-circuit events. For accurate current limiting, place  $R_{ILIM}$  near to the device with short traces to ensure < 5-pF capacitance to GND on the  $I_{LIM}$  pin.

#### 9.3.1.2.3 Undervoltage Lockout (UVLO)

The device monitors the supply voltage  $V_{BB}$  to prevent unpredicted behaviors in the event that the supply voltage is too low. When the supply voltage falls down to  $V_{UVLOF}$ , the output stage is shut down automatically. When the supply rises up to  $V_{UVLOR}$ , the device turns back on.

During an initial ramp of  $V_{BB}$  from 0 V at a ramp rate slower than 1 V/ms,  $V_{EN}$  pin will have to be held low until  $V_{BB}$  is above UVLO threshold (with respect to board ground) and the supply voltage to the device has reliably reached above the UVLO condition. For best operation, ensure that  $V_{BB}$  has risen above UVLO before setting the  $V_{EN}$  pin to high.

## 9.3.1.2.4 V<sub>BB</sub> During Short-to-Ground

When  $V_{OUT}$  is shorted to ground, the module power supply ( $V_{BB}$ ) can have a transient decrease. This decrease is caused by the sudden increase in current flowing through the wiring harness cables. To achieve ideal system behavior, TI recommends that the module maintain  $V_{BB} > 3$  V (above the maximum  $V_{UVLOF}$ ) during  $V_{OUT}$  short-to-ground. This maintenance is typically accomplished by placing bulk capacitance on the power supply node.

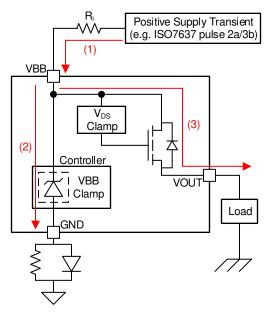

# 9.3.1.3 Voltage Transients

The TPS1HB16-Q1 device contains two types of voltage clamps which protect the FET against system-level voltage transients. The two different clamps are shown in Figure 9-2.

The clamp from  $V_{BB}$  to GND is primarily used to protect the controller from positive transients on the supply line (for example, ISO7637-2). The clamp from  $V_{BB}$  to  $V_{OUT}$  is primarily used to limit the voltage across the FET when switching off an inductive load. If the voltage potential from  $V_{BB}$  to GND exceeds the  $V_{BB}$  clamp level, the clamp will allow current to flow through the device from  $V_{BB}$  to GND (path 2). If the voltage potential from  $V_{BB}$  to  $V_{OUT}$  exceeds the clamping voltage, the power FET will allow current to flow from  $V_{BB}$  to  $V_{OUT}$  (path 3). Additional capacitance from  $V_{BB}$  to GND can increase the reliability of the system during ISO 7637 pulse 2-A testing.

Figure 9-2. Current Path During Supply Voltage Transient

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

#### 9.3.1.3.1 Load Dump

The TPS1HB16-Q1 device is tested according to ISO 16750-2:2010(E) suppressed load dump pulse. The device supports up to 40-V load dump transient and will maintain normal operation during the load dump pulse. If the switch is enabled, it will stay enabled and if the switch is disabled, it will stay disabled.

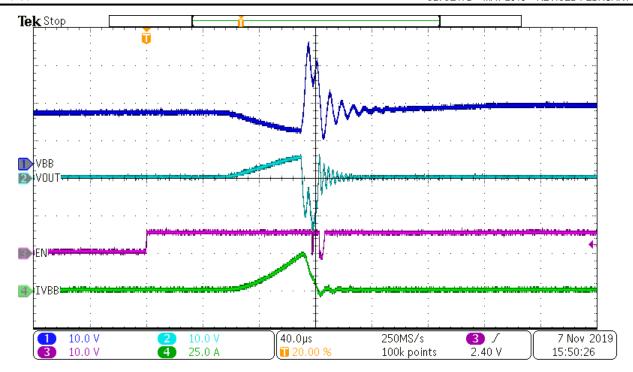

#### 9.3.1.3.2 Driving Inductive Loads

When switching off an inductive load, the inductor can impose a negative voltage on the output of the switch. The TPS1HB16-Q1 includes a voltage clamp to limit voltage across the FET. The maximum acceptable load inductance is a function of the device robustness.

### Figure 9-3. TPS1HB16-Q1 Inductive Discharge (5 mH)

For more information on driving inductive loads, refer to TI's *How To Drive Inductive, Capacitive, and Lighting Loads With Smart High Side Switches* application report.

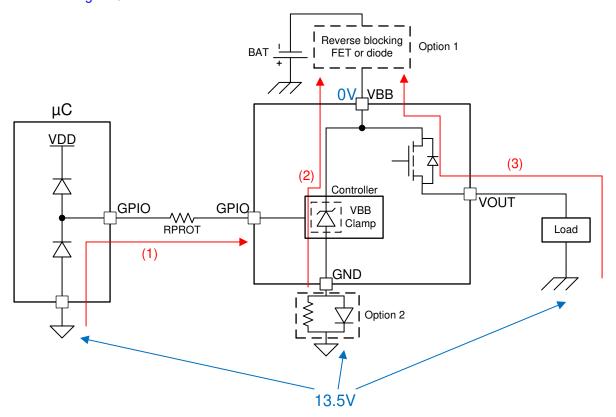

### 9.3.1.4 Reverse Battery

In the reverse battery condition, the switch will automatically be enabled regardless of the state of EN to prevent excess power dissipation inside the MOSFET body diode. In many applications (for example, resistive loads), the full load current can be present during reverse battery. In order to activate the automatic switch on feature, SEL must have a path to ground from either from the MCU or it needs to be tied to ground through R<sub>PROT</sub> if unused.

There are two options for blocking reverse current in the system. The first option is to place a blocking device (FET or diode) in series with the battery supply, blocking all current paths. The second option is to place a blocking diode in series with the GND node of the high-side switch. This method will protect the controller portion of the switch (path 2), but it will not prevent current from flowing through the load (path 3). The diode used for the second option can be shared amongst multiple high-side switches.

Path 1 shown in Figure 9-4 is blocked inside of the device.

Figure 9-4. Current Path During Reverse Battery

For more information on reverse battery protection, refer to TI's *Reverse Battery Protection for High Side Switches* application note.

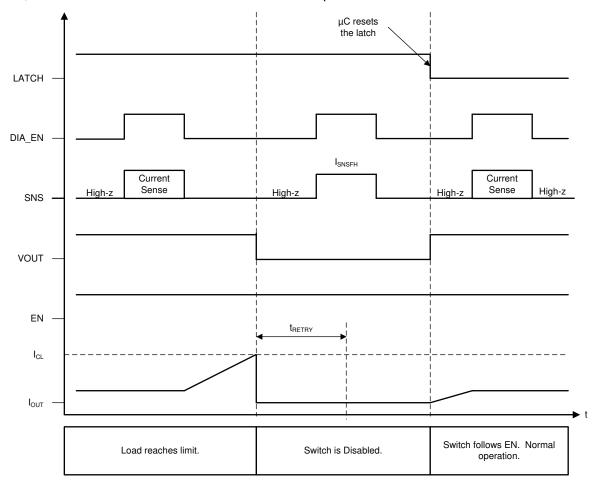

### 9.3.1.5 Fault Event - Timing Diagrams

#### **Note**

All timing diagrams assume that the SEL1 pin is low.

The LATCH, DIA\_EN, and EN pins are controlled by the user. The timing diagrams represent a possible use-case.

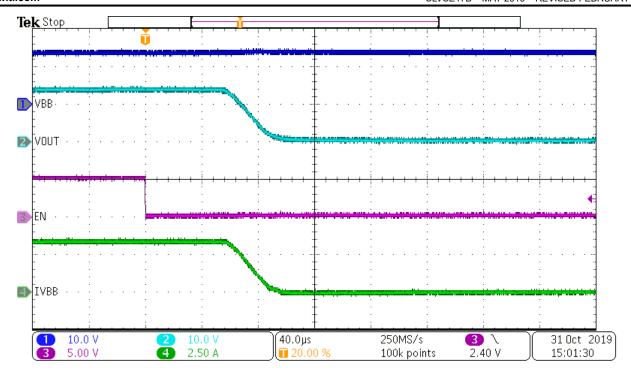

Figure 9-5 shows the immediate current limit switch off behavior. The diagram also illustrates the retry behavior. As shown, the switch will remain latched off until the LATCH pin is low.

Figure 9-5. Current Limit - Version A and B - Latched Behavior

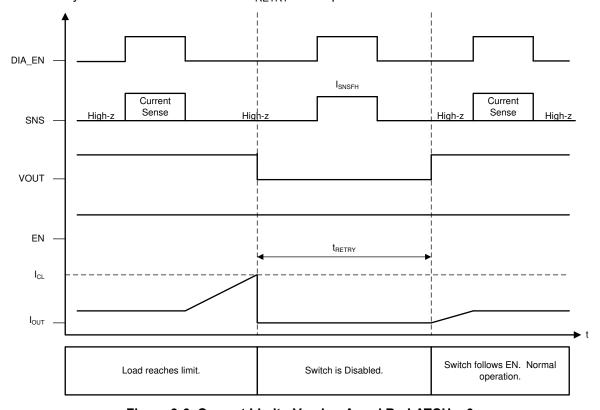

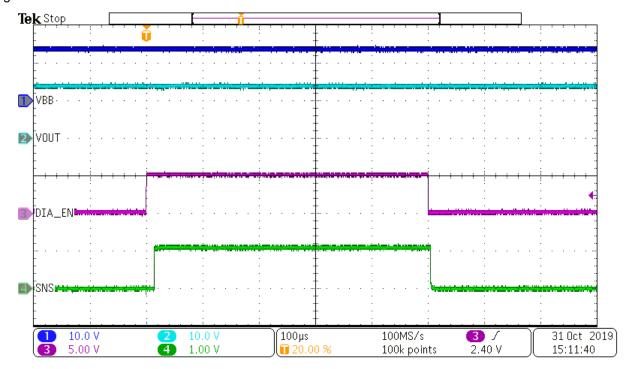

Figure 9-6 shows the immediate current limit switch off behavior. In this example, LATCH is tied to GND; hence, the switch will retry after the fault is cleared and t<sub>RETRY</sub> has expired.

Figure 9-6. Current Limit - Version A and B - LATCH = 0

When the switch retries after a shutdown event, the SNS fault indication will remain until  $V_{OUT}$  has risen to  $V_{BB}$  – 1.8 V. After  $V_{OUT}$  has risen, the SNS fault indication is reset and current sensing is available. If there is a short-to-ground and  $V_{OUT}$  is not able to rise, the SNS fault indication will remain indefinitely. Figure 9-7 illustrates auto-retry behavior and provides a zoomed-in view of the fault indication during retry.

#### Note

Figure 9-7 assumes that t<sub>RETRY</sub> has expired by the time that T<sub>J</sub> reaches the hysteresis threshold.

LATCH = 0 V and DIA EN = 5 V

Figure 9-7. Fault Indication During Retry

## 9.3.2 Diagnostic Mechanisms

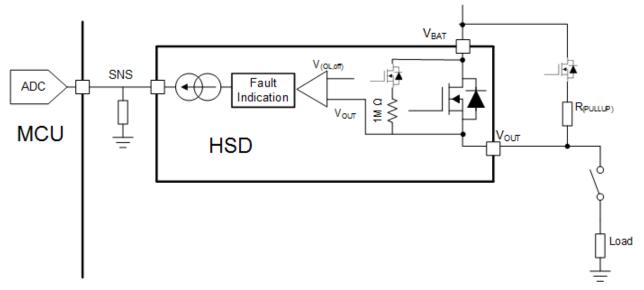

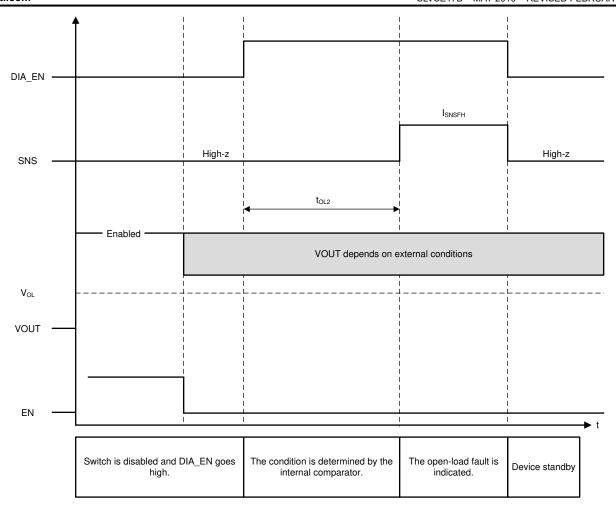

# 9.3.2.1 VOUT Short-to-Battery and Open-Load

The TPS1HB16-Q1 is capable of detecting short-to-battery and open-load events regardless of whether the switch is turned on or off, however the two conditions use different methods.

#### 9.3.2.1.1 Detection With Switch Enabled

When the switch is enabled, the VOUT short-to-battery and open-load conditions can be detected by the current sense feature. In both cases, the load current will be measured through the SNS pin as below the expected value.

### 9.3.2.1.2 Detection With Switch Disabled

While the switch is disabled, if DIA\_EN is high, an internal comparator will detect the condition of  $V_{OUT}$ . If the load is disconnected (open load condition) or there is a short to battery the  $V_{OUT}$  voltage will be higher than the open load threshold ( $V_{OL,off}$ ) and a fault is indicated on the SNS pin. An internal pull-up of 1 M $\Omega$  is in series with an internal MOSFET switch, so no external component is required if a completely open load must be detected. However, if there is significant leakage or other current draw even when the load is disconnected, a lower value pull-up resistor and switch can be added externally to set the  $V_{OUT}$  voltage above the  $V_{OL,off}$  during open load conditions.

This figure assumes that the device ground and the load ground are at the same potential. In a real system, there can be a ground shift voltage of 1 V to 2 V.

Figure 9-8. Short to Battery and Open Load Detection

The detection circuitry is only enabled when DIA\_EN = HIGH and EN = LOW. If  $V_{OUT} > V_{OL}$ , the SNS pin will go to the fault level, but if  $V_{OUT} < V_{OL}$  there will be no fault indication. The fault indication will only occur if the SEL1 pin is low.

While the switch is disabled and DIA\_EN is high, the fault indication mechanisms will continuously represent the present status. For example, if  $V_{OUT}$  decreases from greater than  $V_{OL}$  to less than  $V_{OL}$ , the fault indication is reset. Additionally, the fault indication is reset upon the falling edge of DIA\_EN or the rising edge of EN.

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

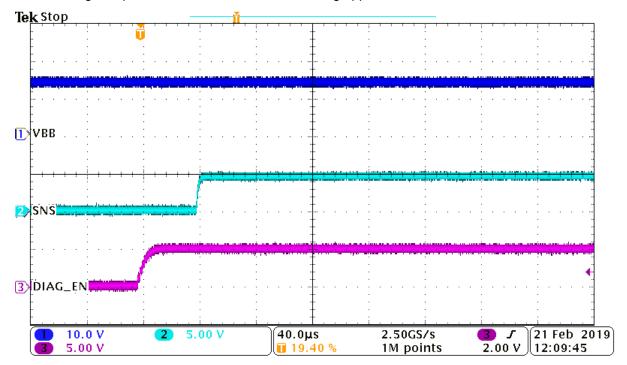

Figure 9-9. Open Load

#### 9.3.2.2 SNS Output

The SNS output can be used to sense the load current if the SEL1 pin is low and there is no fault or device temperature if the SEL1 pin is high and there is no fault. The sense circuit will provide a current that is proportional to the selected parameter. This current will be sourced into an external resistor to create a voltage that is proportional to the selected parameter. This voltage can be measured by an ADC or comparator. In addition, the SNS pin can be used to measure the FET temperature.

To ensure accurate sensing measurement, the sensing resistor must be connected to the same ground potential as the  $\mu$ C ADC.

**Table 9-1. Analog Sense Transfer Function**

| PARAMETER          | TRANSFER FUNCTION                                                                 |

|--------------------|-----------------------------------------------------------------------------------|

| Load current       | I <sub>SNSI</sub> = I <sub>OUT</sub> / K <sub>SNS</sub> = I <sub>OUT</sub> / 3000 |

| Device temperature | $I_{SNST} = (T_J - 25^{\circ}C) \times dI_{SNST} / dT + 0.85$                     |

The SNS output will also be used to indicate system faults.  $I_{SNS}$  will go to the predefined level,  $I_{SNSFH}$ , when there is a fault.  $I_{SNSFH}$ ,  $dI_{SNST}/dT$ , and  $K_{SNS}$  are defined in the *Specifications* section.

## 9.3.2.2.1 R<sub>SNS</sub> Value

The following factors must be considered when selecting the R<sub>SNS</sub> value:

- Current sense ratio (K<sub>SNS</sub>)

- Largest and smallest diagnosable load current required for application operation

- · Full-scale voltage of the ADC

- · Resolution of the ADC

For an example of selecting  $R_{ISNS}$  value, reference  $R_{ILIM}$  Calculation in the applications section of this data sheet.

### 9.3.2.2.1.1 High Accuracy Load Current Sense

In many automotive modules, it is required that the high-side switch provide diagnostic information about the downstream load. With more complex loads, high accuracy sensing is required. A few examples follow:

- **LED lighting**: In many architectures, the body control module (BCM) must be compatible with both incandescent bulbs and also LED modules. The bulb can be relatively simple to diagnose. However, the LED module will consume less current and also can include multiple LED strings in parallel. The same BCM is used in both cases, so the high-side switch can accurately diagnose both load types.

- **Solenoid protection**: Often solenoids are precisely controlled by low-side switches. However, in a fault event, the low-side switch cannot disconnect the solenoid from the power supply. A high-side switch can be used to continuously monitor several solenoids. If the system current becomes higher than expected, the high-side switch can disable the module.

### 9.3.2.2.1.2 SNS Output Filter

To achieve the most accurate current sense value, TI recommends to filter the SNS output. There are two methods of filtering:

- Low-Pass RC filter between the SNS pin and the ADC input. This filter is illustrated in Figure 10-1 with typical

values for the resistor and capacitor. The designer must select a C<sub>SNS</sub> capacitor value based on system

requirements. A larger value will provide improved filtering but a smaller value will allow for faster transient

response.

- The ADC and microcontroller can also be used for filtering. TI recommends that the ADC collects several

measurements of the SNS output. The median value of this data set must be considered as the most

accurate result. By performing this median calculation, the microcontroller can filter out any noise or outlier

data.

### 9.3.2.3 Fault Indication and SNS Mux

The following faults will be communicated through the SNS output:

- · Switch shutdown, due to:

- Thermal Shutdown

Submit Document Feedback

- Current limit

- Open-Load and V<sub>OUT</sub> shorted-to-battery

Open-load and Short-to-battery are not indicated while the switch is enabled, although these conditions can still be detected through the sense current. Hence, if there is a fault indication while the channel is enabled, then it must be either due to an overcurrent or overtemperature event.

The SNS pin will only indicate the fault if the SEL1 pins is low. When the SEL1 pin is high and the device is set to measure temperature, the pin will be measuring the channel FET temperature.

Product Folder Links: TPS1HB16-Q1

| 4/3   | TEXAS       |

|-------|-------------|

| •     | Instruments |

| www.t | i.com       |

| Table 9-2. Device Version A/B SN | NS | Mus | • |

|----------------------------------|----|-----|---|

|----------------------------------|----|-----|---|

|        | OUTPUTS                                 |   |                    |

|--------|-----------------------------------------|---|--------------------|

| DIA_EN | DIA_EN SEL1 FAULT DETECT <sup>(1)</sup> |   | SNS                |

| 0      | X                                       | X | High-z             |

| 1      | 0                                       | 0 | Output current     |

| 1      | 1                                       | 0 | Device temperature |

| 1      | 0                                       | 1 | I <sub>SNSFH</sub> |

| 1      | 1                                       | 1 | Device temperature |

- (1) Fault Detect encompasses multiple conditions:

- Switch shutdown and waiting for retry

- Open Load and Short To Battery

For device version F, the SEL1 pin has no functionality so the device cannot output a temperature sense current. In this case, SEL1 must be connected to ground through an R<sub>PROT</sub> resistor and the SNS behavior will follow the table below.

Table 9-3. Device Version F SNS Mux

| INPUTS |      |                 | OUTPUTS            |            |  |

|--------|------|-----------------|--------------------|------------|--|

| DIA_EN | SEL1 | FAULT DETECT(1) | SNS                | FLT (2)    |  |

| 0      | X    | X               | High-z             | High-z     |  |

| 1      | X    | 0               | Output current     | High-z     |  |

| 1      | X    | 1               | I <sub>SNSFH</sub> | Open-drain |  |

- (1) Fault Detect encompasses multiple conditions:

- Switch shutdown and waiting for retry

- Open Load / Short To Battery

- Version F Only

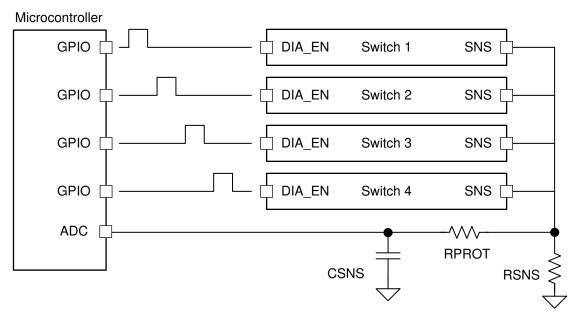

### 9.3.2.4 Resistor Sharing

Multiple high-side devices can use the same SNS resistor as shown in Figure 9-10. This action reduces the total number of passive components in the system and the number of ADC terminals that are required of the microcontroller.

Figure 9-10. Sharing R<sub>SNS</sub> Among Multiple Devices

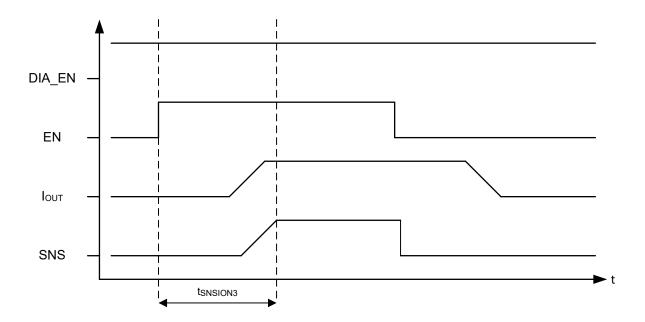

## 9.3.2.5 High-Frequency, Low Duty-Cycle Current Sensing

Some applications will operate with a high-frequency, low duty-cycle PWM or require fast settling of the SNS output. For example, a 250-Hz, 5% duty cycle PWM will have an on-time of only 200  $\mu$ s that must be accommodated. The micro-controller ADC can sample the SNS signal after the defined settling time  $t_{SNSION3}$ .

Figure 9-11. Current Sensing in Low-Duty Cycle Applications

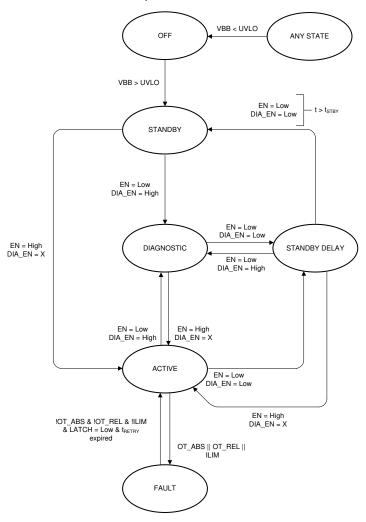

### 9.4 Device Functional Modes

During typical operation, the TPS1HB16-Q1 can operate in a number of states that are described below and shown as a state diagram in Figure 9-12.

#### 9.4.1 Off

Off state occurs when the device is not powered.

### 9.4.2 Standby

Standby state is a low-power mode used to reduce power consumption to the lowest level. Diagnostic capabilities are not available in Standby mode.

### 9.4.3 Diagnostic

Diagnostic state can be used to perform diagnostics while the switch is disabled.

#### 9.4.4 Standby Delay

The Standby Delay state is entered when EN and DIA\_EN are low. After t<sub>STBY</sub>, if the EN and DIA\_EN pins are still low, the device will go to Standby State.

### 9.4.5 Active

In Active state, the switch is enabled. The diagnostic functions can be turned on or off during Active state.

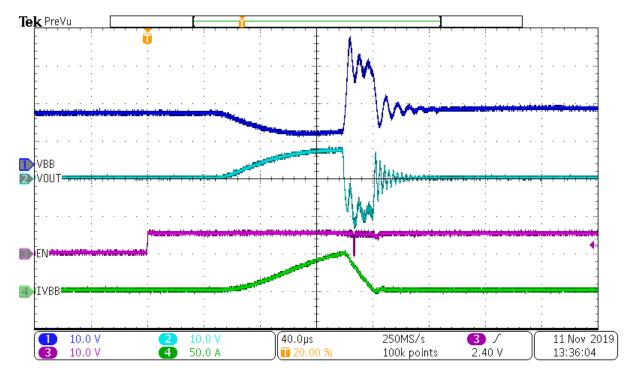

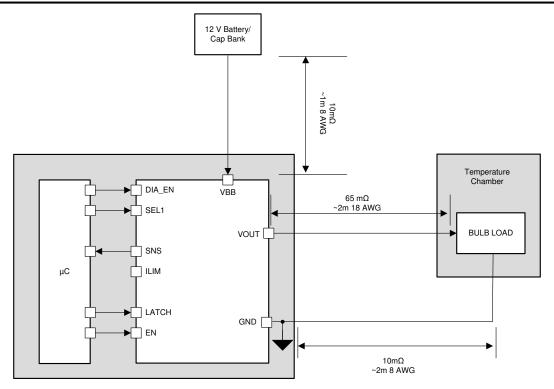

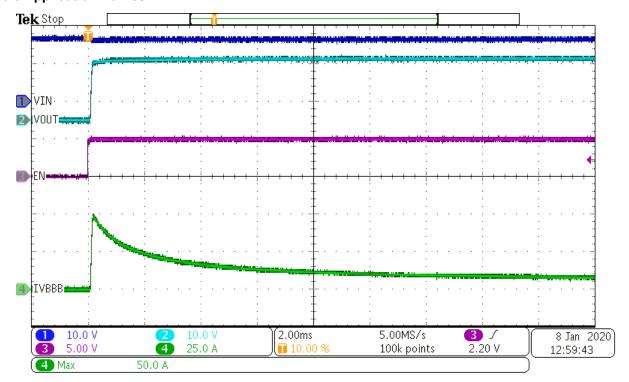

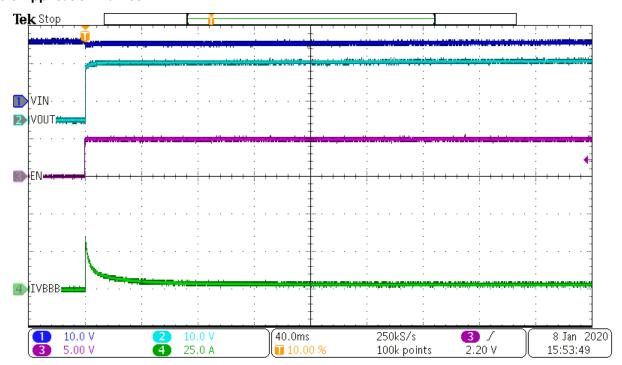

### 9.4.6 Fault