# TPS1HC100-Q1 100mΩ, 2.5A Single-Channel Automotive Smart High-Side Switch

## 1 Features

- Single-channel smart high-side power switch for 12V automotive systems with full diagnostics

- Open-drain status output

- Current sense analog output

- Wide operating voltage 3V to 28V

- Low standby current, < 0.5µA at 85°C

- Operating junction temperature, -40°C to 150°C

- 1.8V, 3.3V, and 5V logic compatible

- Fault sense voltage scaling for ADC protection

- Programmable current limit accuracy ±18% at 1.9A

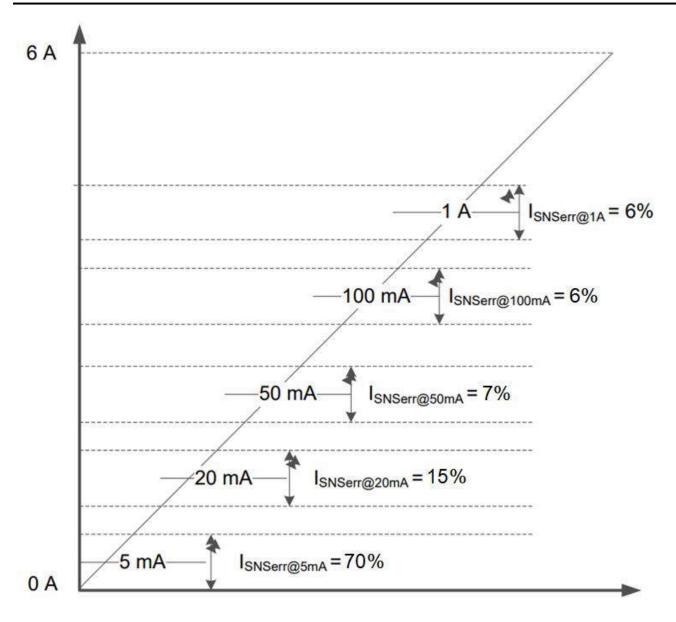

- High-accuracy current sense, ±6% at 1A

- Protection

- Overload and short-circuit protection

- Inductive load negative voltage clamp

- Undervoltage lockout (UVLO) protection

- Thermal shutdown and swing with self recovery

- Loss of GND, loss of supply protection

- Reverse battery protection with external components

- Diagnostic

- On- and off-state output open-load and shortto-battery detection

- Overload and short-to-ground detection

- Thermal shutdown and swing detection

- Qualifications

- AEC-Q100 automotive qualified for grade 1 temperature

- Functional Safety-Capable

- Documentation available to aid functional safety system design

- Tested according to AECQ100-12 Grade A, 1 million times short-to-GND test

- Electrical transient disturbance immunity certification of ISO7637-2 and ISO16750-2

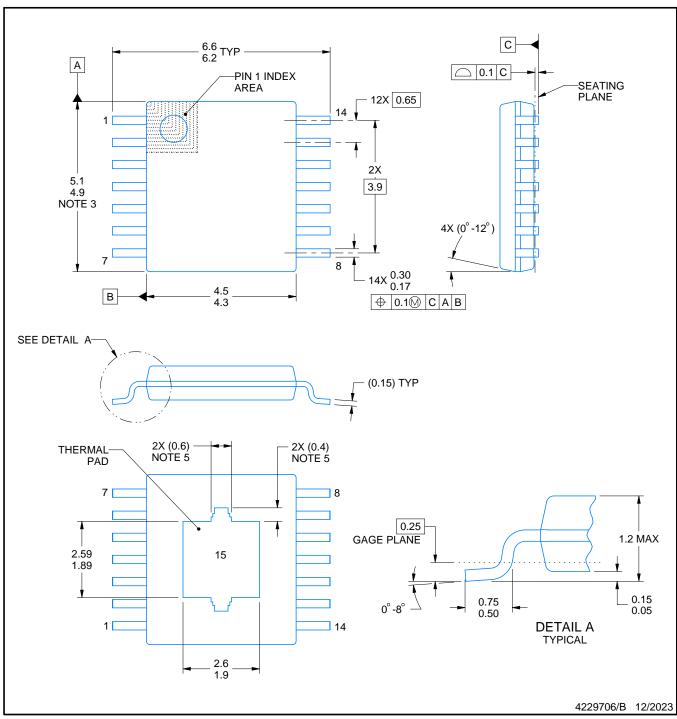

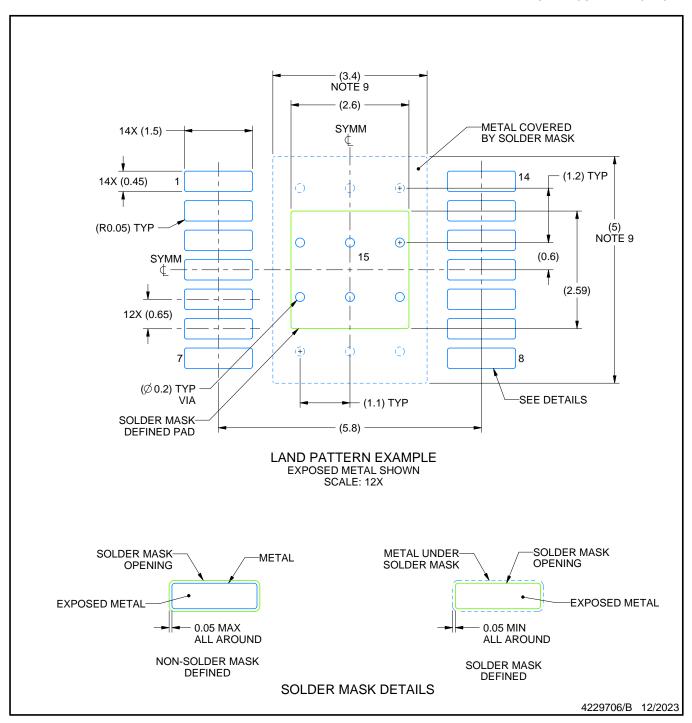

- 14-pin thermally-enhanced PWP package

# 2 Applications

- Automotive display module

- **ADAS** modules

- Seat comfort module

- **HVAC** control module

- Body control module

# 3 Description

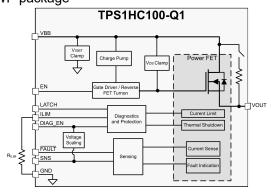

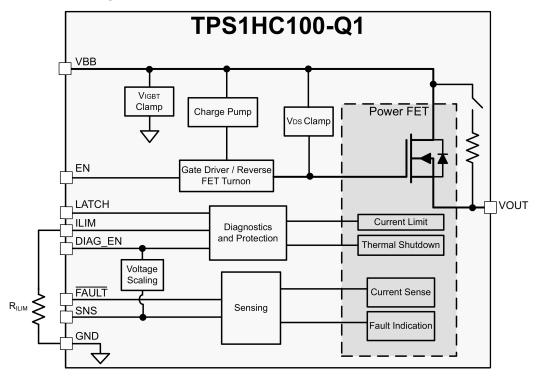

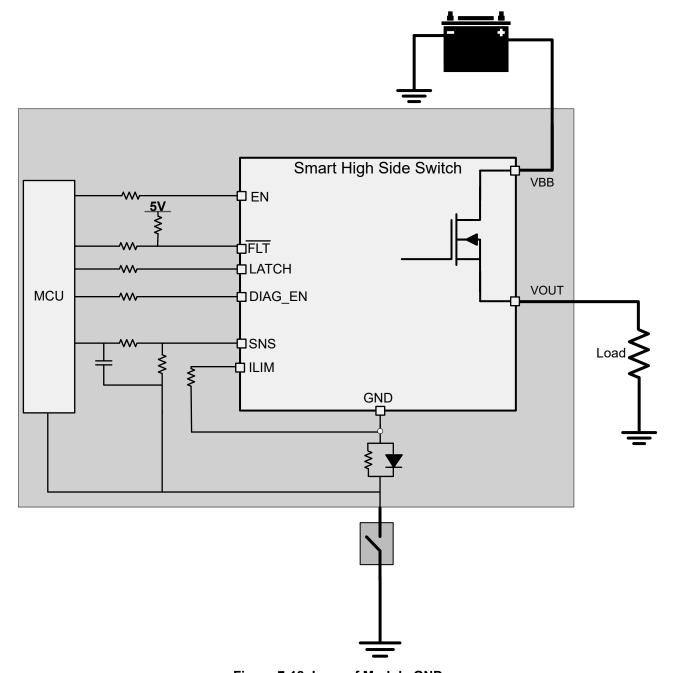

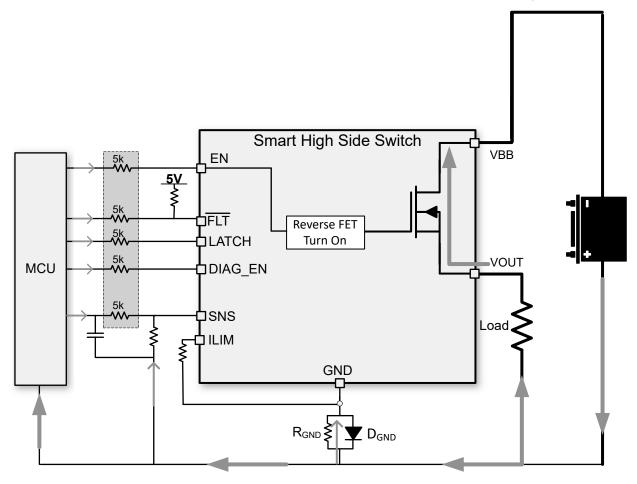

The TPS1HC100-Q1 device is a fully protected highside power switch, with integrated NMOS power FET and charge pump, targeted for the intelligent control of various loads. Accurate current sense and programmable current limit features differentiate it from the market.

Low logic high threshold,  $V_{IH}$ , of 1.5V on the input pins allow use of MCUs GPIO signals to 1.8V. High-accuracy current sensing provides a better realtime monitoring effect and more accurate diagnostics without further calibration. The external high-accuracy current limit allows setting the current limit value by application. The device highly improves the reliability of the system by effectively clamping the inrush current under start-up or short-circuit conditions. The TPS1HC100-Q1 device can be used as a high-side power switch for a wide variety of resistive, inductive, and capacitive loads, including low-wattage bulbs, LEDs, relays, solenoids, and heaters.

#### **Package Information**

| PART NUMBER  | PACKAGE <sup>(1)</sup> | PACKAGE SIZE(2) |  |

|--------------|------------------------|-----------------|--|

| TPS1HC100-Q1 | PWP (HTSSOP, 14)       | 5mm × 6.4mm     |  |

- For all available packages, see the orderable addendum at the end of the data sheet.

- The package size (length × width) is a nominal value and includes pins, where applicable.

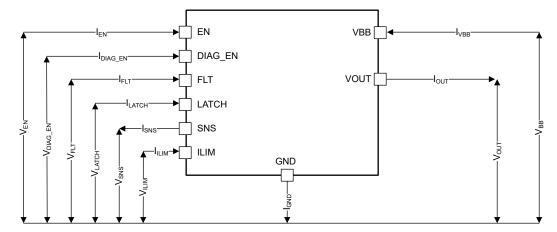

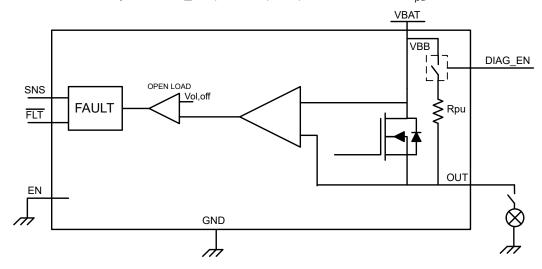

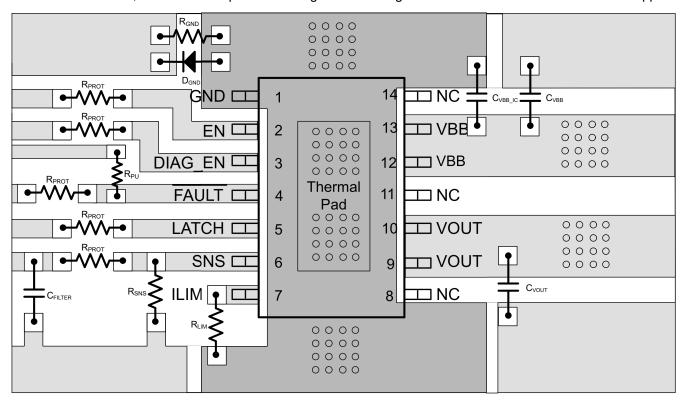

**Functional Block Diagram**

# **Table of Contents**

| 1 Features                                   | 7.3 Feature Description  |

|----------------------------------------------|--------------------------|

| 2 Applications1                              | 7.4 Device Functional N  |

| 3 Description1                               | 8 Application and Imple  |

| 4 Pin Configuration and Functions3           | 8.1 Application Informa  |

| 4.1 Recommended Connections for Unused Pins4 | 8.2 Typical Application. |

| 5 Specifications5                            | 8.3 Power Supply Reco    |

| 5.1 Absolute Maximum Ratings5                | 8.4 Layout               |

| 5.2 ESD Ratings5                             | 9 Device and Document    |

| 5.3 Recommended Operating Conditions5        | 9.1 Documentation Sup    |

| 5.4 Thermal Information6                     | 9.2 Receiving Notificati |

| 5.5 Electrical Characteristics6              | 9.3 Support Resources    |

| 5.6 SNS Timing Characteristics9              | 9.4 Trademarks           |

| 5.7 Switching Characteristics9               | 9.5 Electrostatic Discha |

| 5.8 Typical Characteristics11                | 9.6 Glossary             |

| 6 Parameter Measurement Information16        | 10 Revision History      |

| 7 Detailed Description18                     | 11 Mechanical, Packagii  |

| 7.1 Overview                                 | Information              |

| 7.2 Functional Block Diagram19               |                          |

|    | 7.3 Feature Description                             | 18   |

|----|-----------------------------------------------------|------|

|    | 7.4 Device Functional Modes                         | 37   |

| 8  | Application and Implementation                      | 39   |

|    | 8.1 Application Information                         | . 39 |

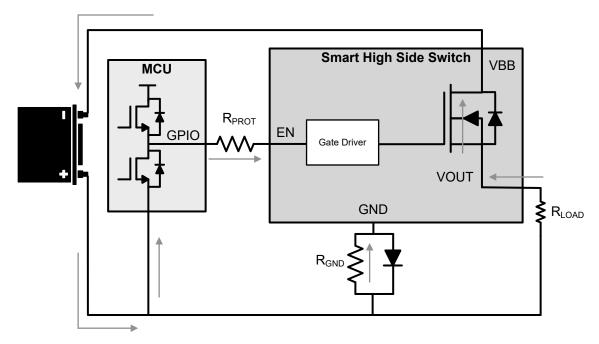

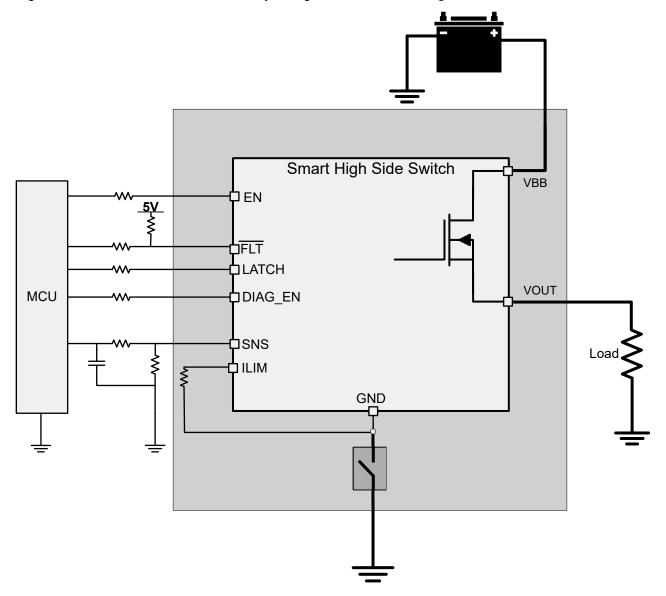

|    | 8.2 Typical Application                             | . 39 |

|    | 8.3 Power Supply Recommendations                    | 44   |

|    | 8.4 Layout                                          | 45   |

| 9  | Device and Documentation Support                    |      |

|    | 9.1 Documentation Support                           | . 47 |

|    | 9.2 Receiving Notification of Documentation Updates | 47   |

|    | 9.3 Support Resources                               | . 47 |

|    | 9.4 Trademarks                                      | 47   |

|    | 9.5 Electrostatic Discharge Caution                 | 47   |

|    | 9.6 Glossary                                        | 47   |

| 1( | 0 Revision History                                  |      |

|    | 1 Mechanical, Packaging, and Orderable              |      |

|    | Information                                         | . 47 |

|    |                                                     |      |

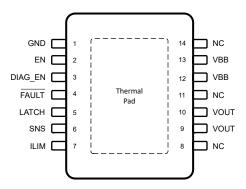

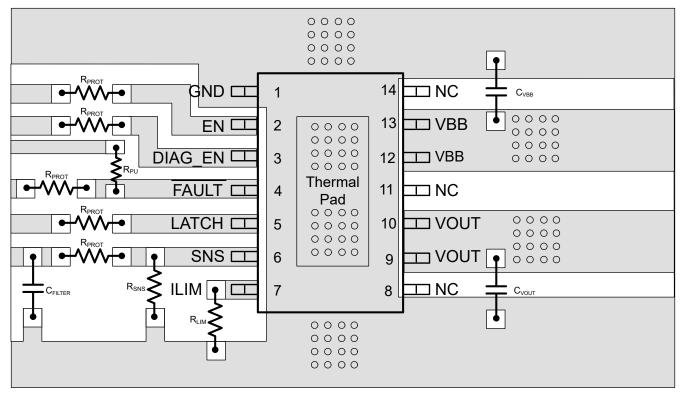

# **4 Pin Configuration and Functions**

Figure 4-1. PWP Package 14-Pin HTSSOP Top View

### **Table 4-1. Pin Functions**

over operating free-air temperature range (unless otherwise noted)

| PI          |         |       | ,                                                                                                  |  |  |

|-------------|---------|-------|----------------------------------------------------------------------------------------------------|--|--|

| NO.         | NAME    | TYPE  | DESCRIPTION                                                                                        |  |  |

| 1           | GND     | Power | Ground of device. Connect to resistor-diode ground network to have reverse battery protection.     |  |  |

| 2           | EN      | I     | Input control for channel activation                                                               |  |  |

| 3           | DIAG_EN | I     | Enable-disable pin for diagnostics, internal pulldown                                              |  |  |

| 4           | FAULT   | 0     | Open drain global fault output. Referred to FAULT, FLT, or fault pin.                              |  |  |

| 5           | LATCH   | I     | Thermal shutdown behavior, latch off or auto retry, internal pull down                             |  |  |

| 6           | SNS     | 0     | Output corresponding sense value based on sense ratio                                              |  |  |

| 7           | ILIM    | 0     | Adjustable current limit. Short to ground or leave floating if external current limit is not used. |  |  |

| 8, 11, 14   | NC      | N/A   | No internal connection                                                                             |  |  |

| 9, 10       | VOUT    | Power | Output of high side switch, connected to load                                                      |  |  |

| 12, 13      | VBB     | Power | Power supply                                                                                       |  |  |

| Thermal Pad | Pad     | _     | Thermal Pad, internally shorted to ground                                                          |  |  |

# **4.1 Recommended Connections for Unused Pins**

The TPS1HC100-Q1 is designed to provide an enhanced set of diagnostic and protection features. However, if the system design only allows for a limited number of I/O connections, some pins can be considered as optional.

**Table 4-2. Connections For Optional Pins**

|          | 10010 1 21 001111                                  |                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|----------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| PIN NAME | CONNECTION IF NOT USED                             | IMPACT IF NOT USED                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| SNS      | Ground through 1-kΩ resistor                       | Analog sense is not available.                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| LATCH    | i inci                                             | With LATCH unused, the device auto-retries after a fault. If latched behavior is desired, but the system describes limited I/O, it is possible to use one microcontroller output to control the latch function of several high-side channels. |  |  |  |  |  |  |  |

| ILIM     | Float                                              | If the ILIM pin is left floating, the device is set to the default internal current-limit threshold.                                                                                                                                          |  |  |  |  |  |  |  |

| DIA_EN   | Float or ground through R <sub>PROT</sub> resistor | With DIA_EN unused, the analog sense, open-load, and short-to-battery diagnostics are not available.                                                                                                                                          |  |  |  |  |  |  |  |

| FAULT    | Float                                              | Open drain FAULT signal is not able to be used                                                                                                                                                                                                |  |  |  |  |  |  |  |

# 5 Specifications

# 5.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)(1)

|                                                    |                            | MIN  | MAX | UNIT |

|----------------------------------------------------|----------------------------|------|-----|------|

| Maximum continuous supply voltage, V <sub>BB</sub> |                            |      | 28  | V    |

| Load dump voltage, V <sub>LD</sub>                 | ISO16750-2:2010(E)         |      | 36  | V    |

| Reverse Polarity Voltage                           | Maximum duration 3 minutes | -18  |     | V    |

| Enable pin current, I <sub>EN</sub>                |                            | -1   | 20  | mA   |

| Enable pin voltage, V <sub>EN</sub>                |                            | -1   | 7   | V    |

| Diagnostic Enable pin current, I <sub>DIA_EN</sub> |                            | -1   | 20  | mA   |

| Diagnostic Enable pin voltage, V <sub>DIA_EN</sub> |                            | -1   | 7   | V    |

| Sense pin current, I <sub>SNS</sub>                |                            | -100 | 10  | mA   |

| Sense pin voltage, V <sub>SNS</sub>                |                            | -1   | 5.5 | V    |

| Latch pin current, I <sub>LATCH</sub>              |                            | -1   | 10  | mA   |

| Latch pin voltage, V <sub>LATCH</sub>              |                            | -1   | 7   | V    |

| FLT pin current, I <sub>FLT</sub>                  |                            | -30  | 10  | mA   |

| FLT pin voltage, V <sub>FLT</sub>                  |                            | -0.3 | 7   | V    |

| Reverse ground current, I <sub>GND</sub>           | V <sub>BB</sub> < 0 V      |      | -50 | mA   |

| Storage temperature, T <sub>stq</sub>              | ,                          | -65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

# 5.2 ESD Ratings

|                    |                                        |                                                                                     |                             | VALUE | UNIT |

|--------------------|----------------------------------------|-------------------------------------------------------------------------------------|-----------------------------|-------|------|

|                    |                                        | Human-body model (HBM), per AEC<br>Q100-002 Classification Level H2 <sup>(2)</sup>  | All pins except VS and VOUT | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge <sup>(1)</sup> | Human-body model (HBM), per AEC<br>Q100-002 Classification Level H3A <sup>(2)</sup> | VS and VOUT                 | ±4000 | V    |

|                    |                                        | Charged-device model (CDM), per AEC Q100-011 Classification Level C5                | All pins                    | ±750  |      |

- (1) All ESD strikes are with reference from the pin mentioned to GND

- (2) AEC-Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specifications.

## **5.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted) (1)

|                      |                                         | MIN | MAX | UNIT |

|----------------------|-----------------------------------------|-----|-----|------|

| V <sub>VBB_NOM</sub> | Nominal supply voltage (1)              | 3.5 | 18  | V    |

| V <sub>VBB_EXT</sub> | Extended supply voltage <sup>(2)</sup>  | 2.6 | 28  | V    |

| V <sub>VBB_SC</sub>  | Short circuit supply voltage capability |     | 28  | V    |

| V <sub>EN</sub>      | Enable voltage                          | -1  | 5.5 | V    |

| V <sub>DIA_EN</sub>  | Diagnostic Enable voltage               | -1  | 5.5 | V    |

| V <sub>LATCH</sub>   | Latch voltage                           | -1  | 5.5 | V    |

| V <sub>SNS</sub>     | Sense voltage                           | -1  | 7   | V    |

| T <sub>A</sub>       | Operating free-air temperature          | -40 | 125 | °C   |

- (1) All operating voltage conditions are measured with respect to device GND

- (2) Device will function within extended operating range, however some timing parametric values might not apply. See the respective sections for what voltages are used. Additionally more explanation can be found in Power Supply Recommendations

Copyright © 2025 Texas Instruments Incorporated

### **5.4 Thermal Information**

|                       |                                              | TPS1HC100-Q1 |      |

|-----------------------|----------------------------------------------|--------------|------|

|                       | THERMAL METRIC <sup>(1)</sup> (2)            | PWP (HTSSOP) | UNIT |

|                       |                                              | 14 PINS      |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 46.4         | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 36.6         | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 21.9         | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 1.9          | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 21.8         | °C/W |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 6.8          | °C/W |

- (1) For more information about traditional and new thermal metrics, see the SPRA953 application report.

- (2) The thermal parameters are based on a 4-layer PCB according to the JESD51-5 and JESD51-7 standards.

# 5.5 Electrical Characteristics

$V_{BB}$  = 6 V to 28 V,  $T_{A}$  = -40°C to 125°C (unless otherwise noted); Typical application is 13.5V, 10 $\Omega$ , RILIM=Open (unless otherwise specified)

| PARAMETER            |                                                 | TEST CONDITIONS                                                                                                              |                                                   | MIN | TYP  | MAX | UNIT |

|----------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----|------|-----|------|

| INPUT VOL            | TAGE AND CURRENT                                |                                                                                                                              |                                                   |     |      |     |      |

| V                    | VDC alama valtaga                               |                                                                                                                              | T <sub>J</sub> =25°C                              | 35  |      | 43  | V    |

| $V_{Clamp}$          | VDS clamp voltage                               |                                                                                                                              | T <sub>J</sub> = -40°C to 150°C                   | 33  | -    | 45  | V    |

| V <sub>UVLOR</sub>   | V <sub>BB</sub> undervoltage lockout rising     | Manager d with respect to                                                                                                    | the CND pin of the device                         | 3.0 | 3.5  | 4.0 | V    |

| V <sub>UVLOF</sub>   | V <sub>BB</sub> undervoltage lockout falling    | measured with respect to                                                                                                     | easured with respect to the GND pin of the device |     | 2.6  | 3.0 | V    |

| 1                    | Standby current (total device leakage including | $V_{BB} \le 28 \text{ V}, V_{EN} = 0.000 \text{ V}$                                                                          | T <sub>J</sub> = 25°C                             |     |      | 0.3 | μA   |

| I <sub>SB</sub>      | MOSFET channel)                                 | $V_{DIA\_EN} = 0 V, V_{OUT} = 0$                                                                                             | T <sub>J</sub> = 85°C                             |     |      | 0.5 | μΑ   |

| I <sub>NOM</sub>     | Continuous load current, per channel            | Channel enabled, T <sub>AMB</sub> =                                                                                          | 85°C                                              |     | 2    |     | Α    |

|                      | Output leakage current                          | $V_{BB} \le 28 \text{ V}, T_J = 25^{\circ}\text{C}$<br>$V_{EN} = V_{DIA\_EN} = 0 \text{ V}, V_{OUT} = 0 \text{ V}$           |                                                   |     | 0.01 | 0.1 | μA   |

| IOUT(standby)        | Output leakage current                          | $V_{BB} \le 28 \text{ V}, T_J = 85^{\circ}\text{C}$<br>$V_{EN} = V_{DIA\_EN} = 0 \text{ V}, V_{OUT} = 0 \text{ V}$           |                                                   |     |      | 0.3 | μΑ   |

| I <sub>DIA</sub>     | Current consumption in diagnostic mode          | $V_{BB} \le 28 \text{ V}, I_{SNS} = 0 \text{ mA}$<br>$V_{EN} = 0 \text{ V}, V_{DIA\_EN} = 5 \text{ V}, V_{OUT} = 0 \text{V}$ |                                                   |     | 1.3  | 1.5 | mA   |

| IQ                   | Quiescent current channel enabled               | $V_{BB} \le 28 \text{ V}$<br>$V_{EN} = V_{DIA\_EN} = 5 \text{ V}, I_{OUT}$                                                   | <sub>x</sub> = 0 A                                |     | 1.6  | 2.5 | mA   |

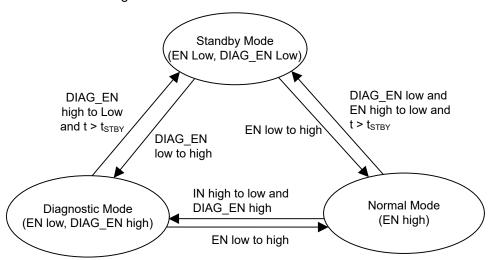

| t <sub>STBY</sub>    | Standby mode delay time                         | V <sub>ENx</sub> = V <sub>DIA_EN</sub> = 0 V to s                                                                            | tandby                                            |     | 20   |     | ms   |

| RON CHAR             | ACTERISTICS                                     |                                                                                                                              |                                                   |     |      |     |      |

|                      | On-resistance                                   | 6 V ≤ V <sub>BB</sub> ≤ 28                                                                                                   | T <sub>J</sub> = 25°C                             |     | 88   |     | mΩ   |

| В                    | (Includes MOSFET                                | V, I <sub>OUT</sub> = 1 A                                                                                                    | T <sub>J</sub> = 150°C                            |     |      | 176 | mΩ   |

| R <sub>ON</sub>      | channel and metallization                       | 3V ≤ V <sub>BB</sub> ≤                                                                                                       | T <sub>J</sub> = 25°C                             |     |      | 190 | mΩ   |

|                      | on die)                                         | 6V, I <sub>OUT</sub> =1A                                                                                                     | T <sub>J</sub> = 150°C                            |     |      | 250 | mΩ   |

|                      | On-resistance during                            | 40.1/4.1/4.4.0.1/                                                                                                            | T <sub>J</sub> = 25°C                             |     | 94   |     | mΩ   |

| $R_{ON(REV)}$        | reverse polarity                                | -18 V ≤ V <sub>BB</sub> ≤ -6 V                                                                                               | T <sub>J</sub> = 150°C                            |     |      | 188 | mΩ   |

| CURRENT              | SENSE CHARACTERISTIC                            | CS                                                                                                                           | 1                                                 |     |      | -   |      |

| K <sub>SNS</sub>     | Current sense ratio                             | I <sub>OUT</sub> = 1 A                                                                                                       |                                                   |     | 1040 |     |      |

| I <sub>SAT_SNS</sub> | Saturated sense current level                   | Maximum amount of load                                                                                                       | current that can be sensed                        |     | 6    |     | Α    |

# **5.5 Electrical Characteristics (continued)**

$V_{BB}$  = 6 V to 28 V,  $T_A$  = -40°C to 125°C (unless otherwise noted); Typical application is 13.5V, 10 $\Omega$ , RILIM=Open (unless

|                       | PARAMETER                                                                            | TEST CO                                              | NDITIONS                                  | MIN                   | TYP    | MAX                   | UNIT |

|-----------------------|--------------------------------------------------------------------------------------|------------------------------------------------------|-------------------------------------------|-----------------------|--------|-----------------------|------|

|                       |                                                                                      | V <sub>EN</sub> = V <sub>DIA_EN</sub> = 5 V, VBB     | I <sub>OUT</sub> = 4 A                    |                       | 3.87   |                       | mA   |

|                       |                                                                                      | ≥ 6 V                                                | 1001                                      | -6                    |        | 6                     | %    |

|                       |                                                                                      |                                                      | I <sub>OUT</sub> = 2 A                    |                       | 1.93   |                       | mA   |

|                       |                                                                                      |                                                      | 1001 - 2 A                                | -6                    |        | 6                     | %    |

|                       |                                                                                      |                                                      | I <sub>OUT</sub> = 1 A                    |                       | 0.96   |                       | mA   |

|                       |                                                                                      |                                                      | 1001 - 17                                 | -6                    |        | 6                     | %    |

|                       |                                                                                      |                                                      | I <sub>OUT</sub> = 500 mA                 |                       | 0.48   |                       | mA   |

|                       |                                                                                      |                                                      | 1001 - 200 HIA                            | -6                    |        | 6                     | %    |

|                       |                                                                                      |                                                      | I <sub>OUT</sub> = 200 mA                 |                       | 0.192  |                       | mA   |

| laviai                | Current sense current                                                                |                                                      | 1001 - 200 MA                             | -6                    |        | 6                     | %    |

| SNSI                  | and accuracy                                                                         | $V_{EN} = V_{DIA\_EN} = 5 V$                         | I <sub>OUT</sub> = 100 mA                 |                       | 0.096  |                       | mA   |

|                       |                                                                                      | VBB ≥ 5 V                                            | 100T - 100 IIIA                           | -6                    |        | 6                     | %    |

|                       |                                                                                      |                                                      | I <sub>OUT</sub> = 50 mA                  |                       | 0.048  |                       | mA   |

|                       |                                                                                      |                                                      | 1001 - 20 1117                            | -7                    |        | 7                     | %    |

|                       |                                                                                      |                                                      | I <sub>OUT</sub> = 20 mA                  |                       | 0.0192 |                       | mA   |

|                       |                                                                                      |                                                      | 100T - 20 IIIA                            | -15                   |        | 15                    | %    |

|                       |                                                                                      |                                                      | I <sub>OUT</sub> = 10 mA                  |                       | 0.0096 |                       | mA   |

|                       |                                                                                      |                                                      |                                           | -40                   |        | 40                    | %    |

|                       |                                                                                      |                                                      | I <sub>OUT</sub> = 5 mA                   |                       | 0.0048 |                       | mA   |

|                       |                                                                                      |                                                      |                                           | -70                   |        | 70                    | %    |

| SNS CHAF              | RACTERISTICS                                                                         |                                                      |                                           |                       |        |                       |      |

| $V_{SNSFH}$           | V <sub>SNS</sub> fault high-level                                                    | V <sub>DIA_EN</sub> = 5 V                            |                                           | 4.75                  | 5      | 5.5                   | V    |

| ▼ SNSFH               | V SNS rault riigir-lever                                                             | V <sub>DIA_EN</sub> = 3.3 V                          |                                           | 3.3                   | 3.5    | 3.75                  | V    |

| V <sub>SNSFH</sub>    | V <sub>SNS</sub> fault high-level                                                    | V <sub>DIA_EN</sub> = V <sub>IH</sub>                |                                           | 2.8                   | 3.15   | 3.5                   | V    |

| I <sub>SNSFH</sub>    | I <sub>SNS</sub> fault high-level                                                    | V <sub>DIA_EN</sub> > V <sub>IH,DIAG_EN</sub>        |                                           |                       | 6.6    |                       | mA   |

| lava i                | I <sub>SNS</sub> leakage                                                             | V <sub>DIA_EN</sub> = 5 V, IL = 0 mA                 | T <sub>A</sub> = 25°C                     |                       |        | 1.8                   | μΑ   |

| SNSleak               | ISNS Icakage                                                                         | VDIA_EN = 5 V, IE = 0 IIIA                           | T <sub>A</sub> = 125°C                    |                       |        | 2.2                   | μΑ   |

| V <sub>BB_ISNS</sub>  | V <sub>BB</sub> headroom needed<br>for full current sense and<br>fault functionality | V <sub>DIAG_EN</sub> = 3.3V                          |                                           | 5.3                   |        |                       | V    |

| V <sub>BB_ISNS</sub>  | V <sub>BB</sub> headroom needed<br>for full current sense and<br>fault functionality | V <sub>DIAG_EN</sub> = 5V                            |                                           | 6.5                   |        |                       | V    |

| CURRENT               | LIMIT CHARACTERISTICS                                                                | 3                                                    |                                           |                       |        | '                     |      |

| I <sub>CL_LINPK</sub> | Linear Mode peak                                                                     | T <sub>J</sub> = -40°C to 150°C dI/dt<br>< 0.01 A/ms | I <sub>ILIM</sub> = 0.7A to 7A            | 0.9 × I <sub>CL</sub> |        | 1.4 × I <sub>CL</sub> | Α    |

| I <sub>CL_ENPS</sub>  | Peak current enabling into permanent short                                           | T <sub>J</sub> = -40°C to 150°C                      | R <sub>ILIM</sub> = 7.15K to 71.5K        |                       |        | 2 × I <sub>CL</sub>   | Α    |

|                       | OVCR Peak current                                                                    |                                                      | $R_{ILIM} > 35k\Omega$                    |                       |        | 6.5                   | Α    |

| lovcr                 | threshold when short is applied while switch                                         | T <sub>J</sub> = -40°C to 150°C                      | $15kΩ ≤ R_{ILIM} ≤ 35kΩ$                  |                       |        | 9.5                   | Α    |

|                       | enabled write switch                                                                 |                                                      | R <sub>ILIM</sub> < 15kΩ                  |                       |        | 16                    | Α    |

|                       |                                                                                      |                                                      | R <sub>ILIM</sub> = GND                   | 5                     | 7      | 9                     | Α    |

| I <sub>CL</sub>       | I <sub>CL</sub> Current Limit<br>Threshold                                           | T <sub>J</sub> = -40°C to 150°C                      | R <sub>ILIM</sub> = open, or out of range |                       | 3      |                       | Α    |

# **5.5 Electrical Characteristics (continued)**

$V_{BB}$  = 6 V to 28 V,  $T_{A}$  = -40°C to 125°C (unless otherwise noted); Typical application is 13.5V, 10 $\Omega$ , RILIM=Open (unless otherwise specified)

|                              | PARAMETER                                          | TEST CONDITIONS                                                                                     |                                                                                        | MIN   | TYP  | MAX   | UNIT   |

|------------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------|------|-------|--------|

|                              |                                                    |                                                                                                     | R <sub>ILIM</sub> = 7.15 kΩ                                                            | 36.34 | 44.3 | 55.41 | A * kΩ |

| K <sub>CL</sub>              | Current Limit Ratio                                | $T_J = -40^{\circ}\text{C} \text{ to } 150^{\circ}\text{C}$                                         | R <sub>ILIM</sub> = 25 kΩ                                                              | 45    | 48.5 | 57.25 | A * kΩ |

|                              |                                                    |                                                                                                     | R <sub>ILIM</sub> = 71.5 kΩ                                                            | 36.75 | 49   | 61.26 | A * kΩ |

| FAULT CH                     | ARACTERISTICS                                      |                                                                                                     |                                                                                        |       |      |       |        |

| R <sub>VOL</sub>             | Open-load (OL) detection internal pull-up resistor | V <sub>EN</sub> = 0 V, V <sub>DIA_EN</sub> = 5 \                                                    | /                                                                                      |       | 150  |       | kΩ     |

| t <sub>OL</sub>              | Open-load (OL) detection deglitch time             | V <sub>EN</sub> = 0 V, V <sub>DIA_EN</sub> = 5 \<br>duration longer than t <sub>OL</sub>            | /, When V <sub>BB</sub> – V <sub>OUT</sub> < V <sub>OL</sub> ,<br>. Openload detected. |       | 350  | 1000  | μs     |

| V <sub>OL</sub>              | Open-load (OL) detection voltage                   | V <sub>EN</sub> = 0 V, V <sub>DIA_EN</sub> = 5 \                                                    | /                                                                                      |       | 2    | 2.5   | V      |

| V <sub>FLT</sub>             | FLT low output voltage                             | I <sub>FLT</sub> = 2.5 mA                                                                           |                                                                                        |       |      | 0.5   | V      |

| t <sub>OL1</sub>             | OL and STB indication-<br>time from EN falling     | $V_{EN}$ = 5 V to 0 V, $V_{DIA\_E}$<br>$I_{OUT}$ = 0 mA, $V_{OUT}$ = $V_{B}$                        |                                                                                        |       | 350  | 1000  | μs     |

| t <sub>OL2</sub>             | OL and STB indication-<br>time from DIA_EN rising  | $V_{EN} = 0 \text{ V}, V_{DIA\_EN} = 0 \text{ V}$<br>$I_{OUT} = 0 \text{ mA}, V_{OUT} = V_{BI}$     |                                                                                        |       |      | 1000  | μs     |

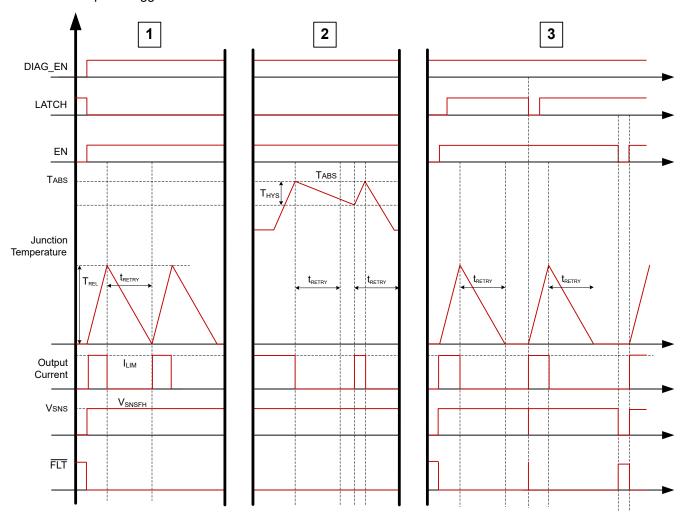

| T <sub>ABS</sub>             | Thermal shutdown                                   |                                                                                                     |                                                                                        |       | 165  |       | °C     |

| T <sub>REL</sub>             | Relative thermal shutdown                          |                                                                                                     |                                                                                        |       | 60   |       | °C     |

| T <sub>HYS</sub>             | Thermal shutdown hysteresis                        |                                                                                                     |                                                                                        |       | 25   |       | °C     |

| t <sub>FAULT_FLT</sub>       | Fault indication-time                              | V <sub>DIA_EN</sub> = 5 V<br>Time between fault and                                                 | FLT asserting                                                                          |       |      | 60    | μs     |

| t <sub>FAULT_SNS</sub>       | Fault indication-time                              | V <sub>DIA_EN</sub> = 5 V<br>Fime between fault and I <sub>SNS</sub> settling at V <sub>SNSFH</sub> |                                                                                        |       |      | 60    | μs     |

| t <sub>RETRY</sub>           | Retry time                                         | Time from fault shutdow (thermal shutdown).                                                         | n until switch re-enable                                                               | 1     | 2    | 3     | ms     |

| EN PIN CH                    | IARACTERISTICS                                     |                                                                                                     |                                                                                        |       |      |       |        |

| V <sub>IL, EN</sub>          | Input voltage low-level                            | No GND Network                                                                                      |                                                                                        |       |      | 0.8   | V      |

| V <sub>IH, EN</sub>          | Input voltage high-level                           | No GND Network                                                                                      |                                                                                        | 1.5   |      |       | V      |

| V <sub>IHYS, EN</sub>        | Input voltage hysteresis                           |                                                                                                     |                                                                                        |       | 280  |       | mV     |

| R <sub>EN</sub>              | Internal pulldown resistor                         |                                                                                                     |                                                                                        | 200   | 350  | 500   | kΩ     |

| I <sub>IL, EN</sub>          | Input current low-level                            | V <sub>EN</sub> = 0.8 V                                                                             |                                                                                        |       | 2.2  |       | μA     |

| I <sub>IH, EN</sub>          | Input current high-level                           | V <sub>EN</sub> = 5 V                                                                               |                                                                                        |       | 14   |       | μΑ     |

| DIA_EN PI                    | N CHARACTERISTICS                                  |                                                                                                     | ,                                                                                      |       |      |       |        |

| V <sub>IL, DIA_EN</sub>      | Input voltage low-level                            | No GND Network                                                                                      |                                                                                        |       |      | 0.8   | V      |

| V <sub>IH, DIA_EN</sub>      | Input voltage high-level                           | No GND Network                                                                                      |                                                                                        | 1.5   |      |       | V      |

| V <sub>IHYS,</sub><br>DIA_EN | Input voltage hysteresis                           |                                                                                                     |                                                                                        |       | 280  |       | mV     |

| R <sub>DIA_EN</sub>          | Internal pulldown resistor                         |                                                                                                     |                                                                                        | 100   | 250  | 450   | kΩ     |

| I <sub>IL, DIA_EN</sub>      | Input current low-level                            | V <sub>DIA_EN</sub> = 0.8 V                                                                         |                                                                                        |       | 3.2  |       | μA     |

| I <sub>IH, DIA_EN</sub>      | Input current high-level                           | V <sub>DIA_EN</sub> = 5 V                                                                           |                                                                                        |       | 20   |       | μA     |

|                              | N Characteristics                                  |                                                                                                     |                                                                                        |       |      |       |        |

| V <sub>IL, LATCH</sub>       | Input voltage low-level                            | No GND Network                                                                                      |                                                                                        |       |      | 0.8   | V      |

| V <sub>IH, LATCH</sub>       | Input voltage high-level                           | No GND Network                                                                                      |                                                                                        | 1.5   |      |       | V      |

|                              | +                                                  |                                                                                                     |                                                                                        |       |      |       |        |

| V <sub>IHYS,</sub><br>LATCH  | Input voltage hysteresis                           |                                                                                                     |                                                                                        |       | 280  |       | mV     |

# **5.5 Electrical Characteristics (continued)**

$V_{BB}$  = 6 V to 28 V,  $T_{A}$  = -40°C to 125°C (unless otherwise noted); Typical application is 13.5V, 10 $\Omega$ , RILIM=Open (unless otherwise specified)

|                        | PARAMETER                | TEST CONDITIONS             | MIN | TYP M | AX | UNIT |

|------------------------|--------------------------|-----------------------------|-----|-------|----|------|

| I <sub>IL, LATCH</sub> | Input current low-level  | V <sub>DIA_EN</sub> = 0.8 V |     | 2.2   |    | μA   |

| I <sub>IH, LATCH</sub> | Input current high-level | V <sub>DIA_EN</sub> = 5 V   |     | 5     |    | μA   |

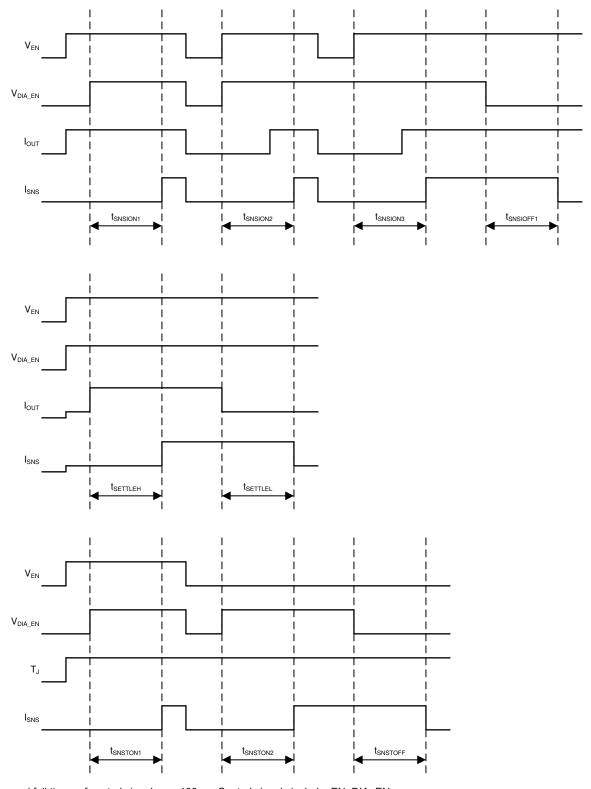

# **5.6 SNS Timing Characteristics**

$V_{BB} = 6 \text{ V}$  to 18 V,  $T_{J} = -40^{\circ}\text{C}$  to +150°C (unless otherwise noted)

|                            | PARAMETER                                                                                                              | TEST CONDITIONS                                                                                                                    | MIN | TYP | MAX | UNIT |  |

|----------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|--|

| SNS TIMING - CURRENT SENSE |                                                                                                                        |                                                                                                                                    |     |     |     |      |  |

| t <sub>SNSION1</sub>       | Settling time from rising edge of DIA_EN 50% of V <sub>DIA_EN</sub> to 90% of settled ISNS                             | $V_{ENx}$ = 5 V, $V_{DIA\_EN}$ = 0 V to 5 V<br>$R_{SNS}$ = 1 k $\Omega$ , $I_L$ = 1A                                               |     |     | 30  | μs   |  |

| t <sub>SNSION1</sub>       | Settling time from rising edge of DIA_EN 50% of V <sub>DIA_EN</sub> to 90% of settled ISNS                             | $V_{EN}$ = 5 V, $V_{DIA\_EN}$ = 0 V to 5 V<br>$R_{SNS}$ = 1 k $\Omega$ , $I_L$ = 30 mA                                             |     |     | 30  | μs   |  |

| t <sub>SNSION2</sub>       | Settling time from rising edge of EN and DIA_EN 50% of V <sub>DIA_EN</sub> V <sub>EN</sub> to 90% of settled ISNS      | $V_{EN} = V_{DIA\_EN} = 0 \text{ V to 5 V}$<br>VBB = 13.5V R <sub>SNS</sub> = 1 k $\Omega$ , R <sub>LOAD</sub> = 10 $\Omega$       |     |     | 150 | μs   |  |

| t <sub>SNSION3</sub>       | Settling time from rising edge of EN with DIA_EN HI; 50% of V <sub>DIA_EN</sub> V <sub>EN</sub> to 90% of settled ISNS | $V_{EN}$ = 0 V to 5 V, $V_{DIA\_EN}$ = 5 V VBB = 13.5V $R_{SNS}$ = 1 k $\Omega$ , $R_{LOAD}$ = 10 $\Omega$                         |     |     | 150 | μs   |  |

| t <sub>SNSIOFF</sub>       | Settling time from falling edge of DIA_EN                                                                              | $V_{EN} = 5 \text{ V}, V_{DIA\_EN} = 5 \text{ V to } 0 \text{ V VBB}$<br>= 13.5V<br>$R_{SNS} = 1 \text{ k}\Omega, R_L = 10 \Omega$ |     |     | 20  | μs   |  |

| t <sub>SETTLEH</sub>       | Settling time from rising edge of load step                                                                            | $V_{EN} = 5 \text{ V}, V_{DIA\_EN} = 5 \text{ V}$<br>$R_{SNS} = 1 \text{ k}\Omega, I_{OUT} = 0.5 \text{ A to } 3 \text{ A}$        |     |     | 20  | μs   |  |

| t <sub>SETTLEL</sub>       | Settling time from falling edge of load step                                                                           | $V_{EN} = 5 \text{ V}, V_{DIA\_EN} = 5 \text{ V}$<br>$R_{SNS} = 1 \text{ k}\Omega, I_{OUT} = 3 \text{ A to } 0.5 \text{ A}$        |     |     | 20  | μs   |  |

# **5.7 Switching Characteristics**

$V_{BB}$  = 13.5 V,  $T_{J}$  = -40°C to +150°C (unless otherwise noted)

|                                    | PARAMETER                                | TEST CONDITIONS                                                   | MIN | TYP  | MAX | UNIT |

|------------------------------------|------------------------------------------|-------------------------------------------------------------------|-----|------|-----|------|

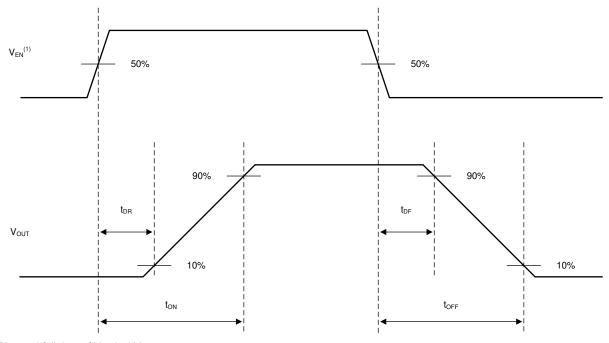

| t <sub>DR</sub>                    | Channel Turnon delay time (from Standby) | $V_{BB}$ = 13.5 V, $R_{L}$ = 10 $\Omega$ 50% of EN to 10% of VOUT | 10  | 40   | 55  | μs   |

| t <sub>DR</sub>                    | Channel Turnon delay time (from Active)  | $V_{BB}$ = 13.5 V, $R_{L}$ = 10 $\Omega$ 50% of EN to 10% of VOUT | 10  | 30   | 45  | μs   |

| t <sub>DF</sub>                    | Channel Turnoff delay time               | $V_{BB}$ = 13.5 V, $R_{L}$ = 10 $\Omega$ 50% of EN to 90% of VOUT | 10  | 30   | 45  | μs   |

| SR <sub>R</sub>                    | VOUT rising slew rate                    | $V_{BB}$ = 13.5 V, 20% to 80% of $V_{OUT}$ , $R_L$ = 10 $\Omega$  | 0.1 | 0.25 | 0.5 | V/µs |

| SR <sub>F</sub>                    | VOUT falling slew rate                   | $V_{BB}$ = 13.5 V, 80% to 20% of $V_{OUT}$ , $R_L$ = 10 $\Omega$  | 0.1 | 0.25 | 0.5 | V/µs |

| f <sub>max</sub>                   | Maximum PWM frequency <sup>(1)</sup>     |                                                                   | -   | 0.4  | 2   | kHz  |

| t <sub>ON</sub>                    | Channel Turnon time                      | $V_{BB}$ = 13.5 V, $R_{L}$ = 10 $\Omega$ 50% of EN to 80% of VOUT | 30  | 70   | 145 | μs   |

| t <sub>OFF</sub>                   | Channel Turnoff time                     | $V_{BB}$ = 13.5 V, $R_{L}$ = 10 $\Omega$ 50% of EN to 20% of VOUT | 39  | 70   | 145 | μs   |

|                                    |                                          | 1ms enable pulse $V_{BB}$ = 13.5 V, $R_{L}$ = 10 $\Omega$         | -30 |      | 30  | μs   |

| t <sub>ON</sub> - t <sub>OFF</sub> | Turnon and off matching                  | 200-μs enable pulse, $V_{BB}$ = 13.5 V, $R_L$ = 10 $\Omega$ ,     | -30 |      | 30  | μs   |

# **5.7 Switching Characteristics (continued)**

$V_{BB}$  = 13.5 V,  $T_{J}$  = -40°C to +150°C (unless otherwise noted)

| PARAMETER        |                                        | TEST CONDITIONS                                                                     | MIN | TYP | MAX | UNIT |

|------------------|----------------------------------------|-------------------------------------------------------------------------------------|-----|-----|-----|------|

|                  | PWM accuracy - average load            | 200-μs enable pulse (1ms period), $V_{BB}$ = 13.5 V, $R_{L}$ = 10 $\Omega$          | -25 |     | 25  | %    |

| $\Delta_{PWM}$   | current                                | $\leq$ 500Hz, 50% Duty cycle V <sub>BB</sub> = 13.5 V, R <sub>L</sub> = 10 $\Omega$ | -10 |     | 10  | %    |

| E <sub>ON</sub>  | Switching energy losses during turnon  | V <sub>BB</sub> = 13.5 V, R <sub>L</sub> = 10 Ω                                     |     | 0.5 |     | mJ   |

| E <sub>OFF</sub> | Switching energy losses during turnoff | V <sub>BB</sub> = 13.5 V, R <sub>L</sub> = 10 Ω                                     |     | 0.5 |     | mJ   |

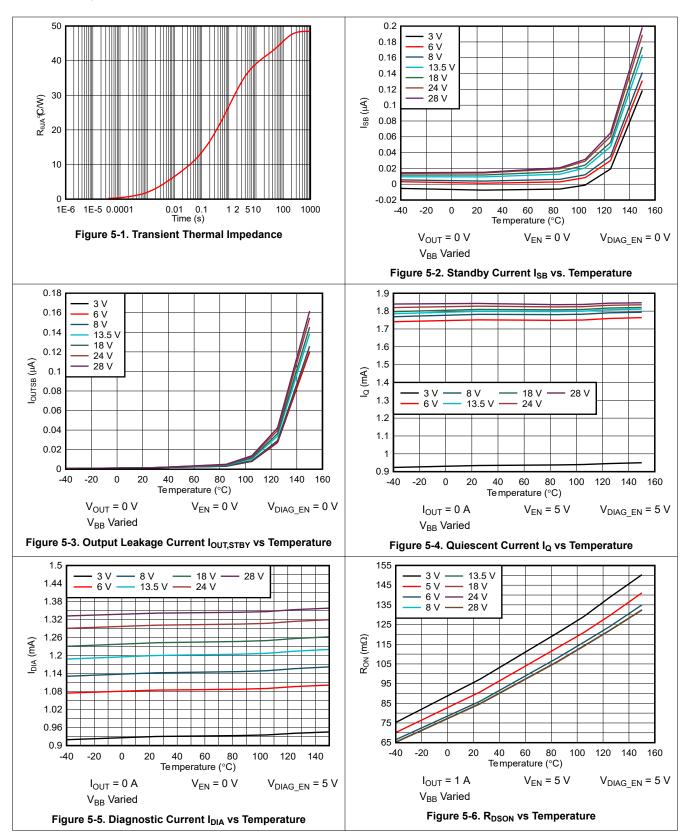

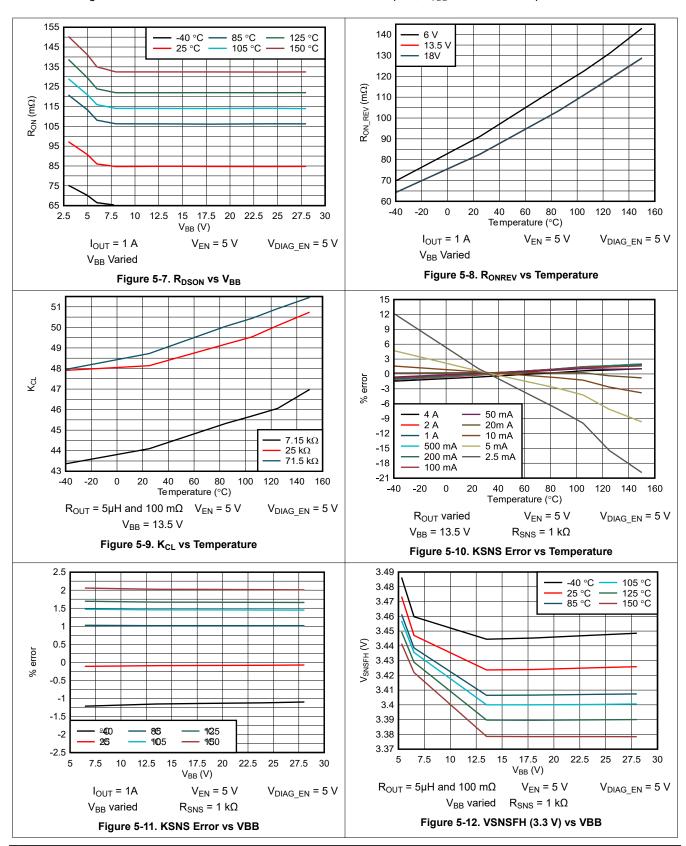

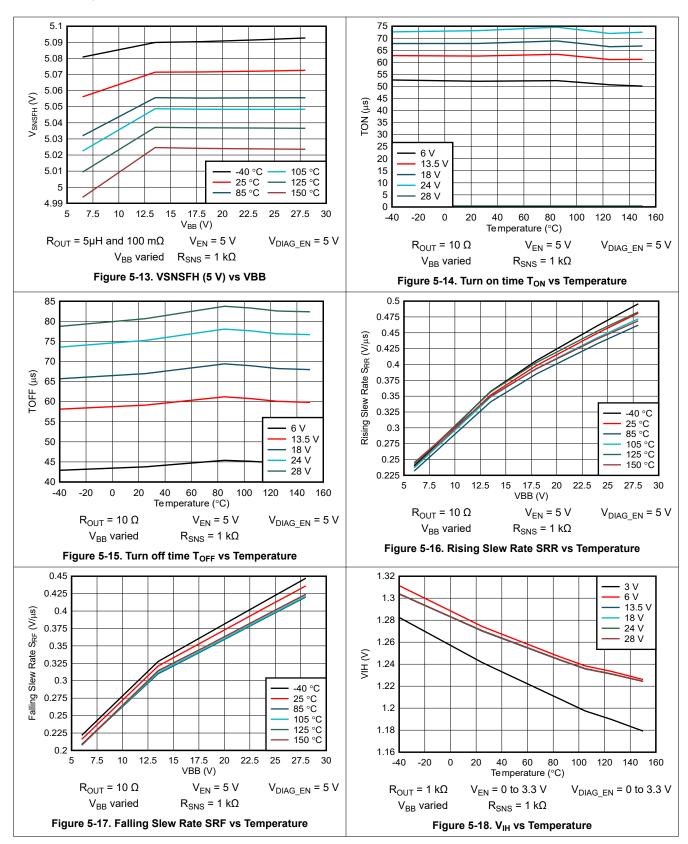

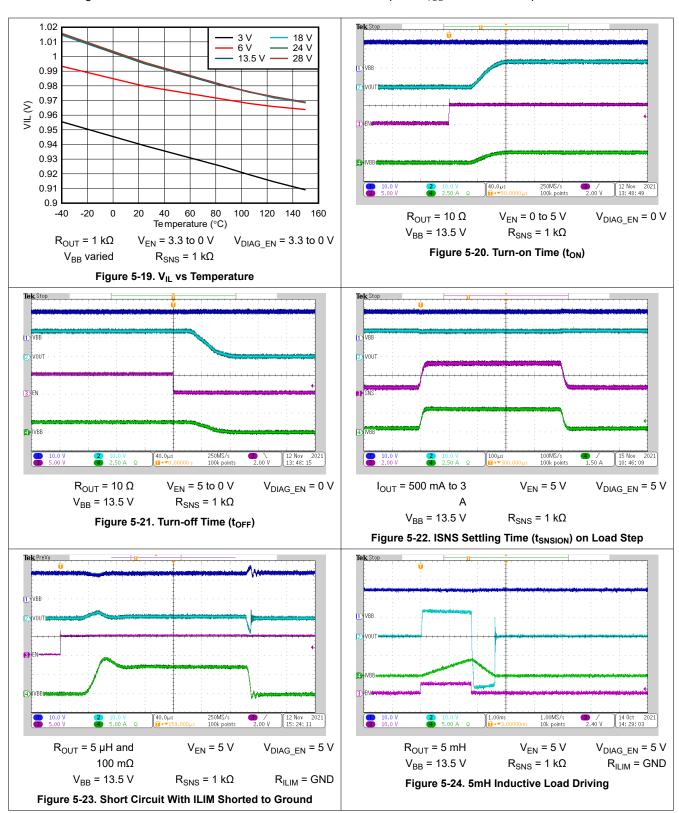

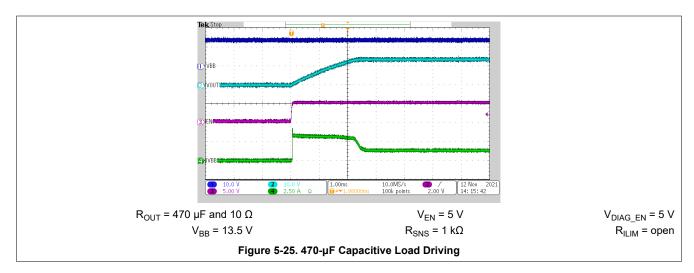

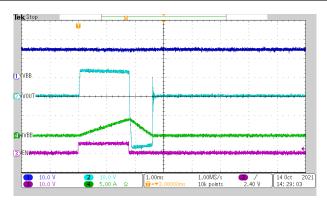

## 5.8 Typical Characteristics

All the following data are based on the mean value of the three lots samples, V<sub>VBB</sub> = 13.5 V if not specified.

All the following data are based on the mean value of the three lots samples, V<sub>VBB</sub> = 13.5 V if not specified.

All the following data are based on the mean value of the three lots samples, V<sub>VBB</sub> = 13.5 V if not specified.

All the following data are based on the mean value of the three lots samples, V<sub>VBB</sub> = 13.5 V if not specified.

Submit Document Feedback

Copyright © 2025 Texas Instruments Incorporated

All the following data are based on the mean value of the three lots samples,  $V_{VBB}$  = 13.5 V if not specified.

# **6 Parameter Measurement Information**

Figure 6-1. Parameter Definitions

Rise and fall time of  $\ensuremath{V_{EN}}$  is 100 ns.

Figure 6-2. Switching Characteristics Definitions

Submit Document Feedback

Copyright © 2025 Texas Instruments Incorporated

Rise and fall times of control signals are 100 ns. Control signals include: EN, DIA\_EN.

**Figure 6-3. SNS Timing Characteristics Definitions**

# 7 Detailed Description

### 7.1 Overview

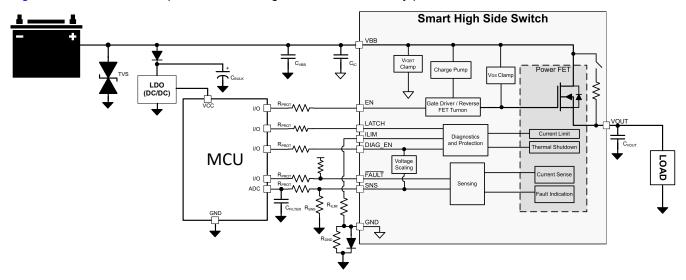

The TPS1HC100-Q1 is a single-channel, fully-protected, high-side power switch with an integrated NMOS power FET and charge pump. Full diagnostics and high-accuracy current-sense features enable intelligent control of the load. Low logic high threshold,  $V_{IH}$ , of 1.5 V on the input pins allow use of MCU GPIO signals of 1.8 V. A programmable current-limit function greatly improves the reliability of the whole system. The device diagnostic reporting has two pins to support both digital status and analog current-sense output, both of which can be set to the high-impedance state when diagnostics are disabled, for multiplexing the MCU analog or digital interface among devices.

The digital status report is implemented with an open-drain structure on the fault pin. When a fault condition occurs, the pin is pulled down to GND. An external pullup is required to match the microcontroller supply level. High-accuracy current sensing allows a better real-time monitoring effect and more-accurate diagnostics without further calibration. A current mirror is used to source 1 /  $K_{SNS}$  of the load current, which is reflected as voltage on the SNS pin.  $K_{SNS}$  is a constant value across the temperature and supply voltage. The current-sensing function operates normally within a wide linear region from 0 to 4 V. The SNS pin can also report a fault by forcing a voltage of  $V_{SNSFH}$  that scales with the diagnostic enable voltage so that the maximum voltage seen by the system's ADC is within an acceptable value. This action removes the need for an external zener diode or resistor divider on the SNS pin.

The external high-accuracy current limit allows setting the current limit value by application. The current limit highly improves the reliability of the system by clamping the inrush current effectively under start-up or short-circuit conditions. Also, the current limit can save system costs by reducing PCB trace, connector size, and the preceding power-stage capacity. An internal current limit is also implemented in this device. The lower value of the external or internal current-limit value is applied.

An active drain to source voltage clamp is built in to address switching off the energy of inductive loads, such as relays, solenoids, pumps, motors, and so forth. During the inductive switching-off cycle, both the energy of the power supply ( $E_{BAT}$ ) and the load ( $E_{LOAD}$ ) are dissipated on the high-side power switch itself. With the benefits of process technology and excellent IC layout, the TPS1HC100-Q1 device can achieve excellent power dissipation capacity, which can help save the external free-wheeling circuitry in most cases. For more details, see *Inductive-Load Switching-Off Clamp*.

Short-circuit reliability is critical for smart high-side power-switch devices. The standard of AEC-Q100-012 is to determine the reliability of the devices when operating in a continuous short-circuit condition. Different grade levels are specified according to the pass cycles. This device is qualified with the highest level, Grade A, 1 million times short-to-GND certification.

The TPS1HC100-Q1 device can be used as a high-side power switch for a wide variety of resistive, inductive, and capacitive loads, including the low-wattage bulbs, LEDs, relays, solenoids, and heaters.

Copyright © 2025 Texas Instruments Incorporated

Product Folder Links: TPS1HC100-Q1

### 7.2 Functional Block Diagram

# 7.3 Feature Description

### 7.3.1 Accurate Current Sense

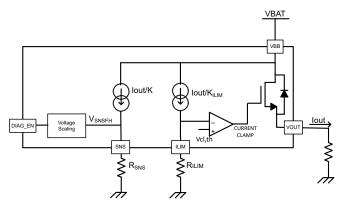

The high-accuracy current-sense function is internally implemented, which allows a better real-time monitoring effect and more-accurate diagnostics without further calibration. A current mirror is used to source 1 /  $K_{SNS}$  of the load current, flowing out to the external resistor between the SNS pin and GND, and reflected as voltage on the SNS pin.

$K_{SNS}$  is the ratio of the output current and the sense current. The accuracy values of  $K_{SNS}$  quoted in the electrical characteristics do take into consideration temperature and supply voltage. Each device was internally calibrated while in production, so post-calibration by users is not required in most cases.

Figure 7-1. Current-Sense Accuracy

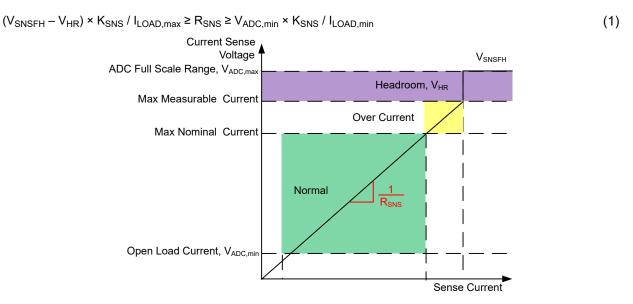

The maximum voltage out on the SNS pin is clamped to  $V_{SNSFH}$ , which is the fault voltage level. To make sure that this voltage is not higher than the system can tolerate, TI has correlated the voltage coming in on the DIAG\_EN pin with the maximum voltage out on the SNS pin. If DIAG\_EN is between  $V_{IH}$  and 3.3 V, the maximum output on the SNS pin is approximately 3.3 V. However, if the voltage at DIAG\_EN is above 3.3 V, then the fault SNS voltage,  $V_{SNSFH}$ , tracks that voltage up to 5 V. Tracking is done because the GPIO voltage output that is powering the diagnostics through DIAG\_EN is close to the maximum acceptable ADC voltage within the same microcontroller. Therefore, the sense resistor value,  $R_{SNS}$ , can be chosen to maximize the range of currents needed to be measured by the system. The  $R_{SNS}$  value must be chosen based on application need. The maximum usable  $R_{SNS}$  value is bounded by the ADC minimum acceptable voltage,  $V_{ADC,min}$ , for the smallest load current needed to be measured by the system,  $I_{LOAD,min}$ . The minimum acceptable  $R_{SNS}$  value has to ensure the  $R_{SNS}$  voltage is below the  $R_{SNS}$  value so that the system can determine faults. This difference between the maximum readable current through the SNS pin,  $R_{SNS}$ , and the  $R_{SNS}$  and the  $R_{SNS}$  value has difference between the maximum readable current and a fault condition. Therefore, the minimum  $R_{SNS}$  value has

to be the  $V_{SNSFH}$  minus the  $V_{HR}$  times the sense current ratio,  $K_{SNS}$  divided by the maximum load current the system must measure,  $I_{LOAD,max}$ . This boundary equation can be seen in Equation 1.

Figure 7-2. Voltage Indication on the Current-Sense Pin

The maximum current the system wants to read,  $I_{LOAD,max}$ , must be below the current limit threshold because after the current limit threshold is tripped the  $V_{SNS}$  value goes to  $V_{SNSFH}$ . Additionally, currents being measured must be below 6 A to ensure that the current sense output is not saturated.

Figure 7-3. Current-Sense and Current-Limit Block Diagram

Because this scheme adapts based on the voltage coming in from the MCU, there is no need to have a Zener diode on the SNS pin to protect from high voltages.

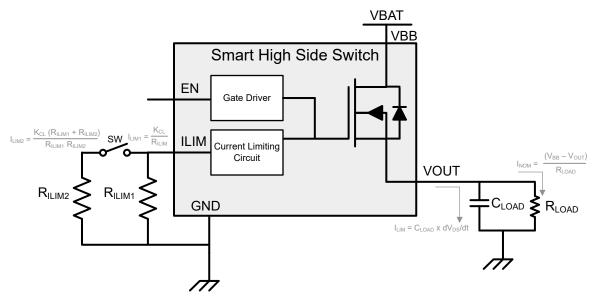

### 7.3.2 Programmable Current Limit

A high-accuracy current limit allows higher reliability, which protects the power supply during short circuit or power up. Also, a current limit can save system costs by reducing PCB traces, connector size, and the capacity of the preceding power stage.

Current limiting offers protection from over-stressing to the load and integrated power FET. The current limit regulates the output current to the set value, and pulls up the SNS pin to  $V_{SNSFH}$  and asserts the  $\overline{FLT}$  pin as diagnostic reports. The three current-limit thresholds are:

External programmable current limit – an external resistor, R<sub>ILIM</sub>, is used to set the channel current limit.

When the current through the device exceeds I<sub>CL</sub> (current limit threshold), a closed loop steps in immediately.

V<sub>GS</sub> voltage regulates accordingly, leading to the V<sub>DS</sub> voltage regulation. When the closed loop is set up, the

current is clamped at the set value. The external programmable current limit provides the capability to set the current-limit value by application.

Additionally, this value can be dynamically changed by changing the resistance on the ILIM pin. This information can be seen in the *Applications* section.

- Internal current limit: ILIM pin shorted to ground if the external current limit is out of range on the lower end or the I<sub>LIM</sub> pin is shorted to ground, the internal current limit is fixed and typically 7 A. To use the internal current limit for large-current applications, tie the ILIM pin directly to the device GND.

- Internal current limit: ILIM pin open if the external resistor is out of range on the higher end or the ILIM

pin is open, the current limit reverts to 3 A or half the current limit range. This level is still above the nominal

operation for the device to operate in DC steady state but is low enough that if a pin fault occurs and the R<sub>ILIM</sub>

opens up, the current does not default to the highest rating and put additional stress on the power supply.

Both the internal current limit ( $I_{lim,nom}$ ) and external programmable current limit are always active when  $V_{BB}$  is powered and EN is high. The lower value one (of  $I_{LIM}$  and the external programmable current limit) is applied as the actual current limit. The typical deglitch time for the current limit to assert is 2.5  $\mu$ s.

Note that if a GND network is used (which leads to the level shift between the device GND and board GND), the ILIM pin must be connected with device GND. Calculate  $R_{ILIM}$  with Equation 2.

$$R_{ILIM} = K_{CL} / I_{LIM}$$

(2)

For better protection from a *hot short* condition (when V<sub>BB</sub> is high, channel is on, and a short to GND happens suddenly), an over current protection, OVCR, circuit is triggered that makes sure to limit the maximum current the device allows to go through. With this OVCR, the device is protected during *hot short* events.

For more information about the current limiting feature, see the Short-Circuit and Overload Protection section.

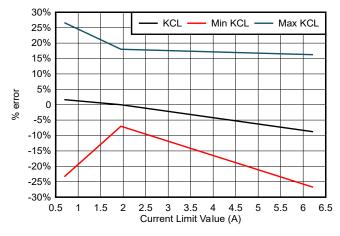

### **Current Limit Accuracy**

The TPS1HC100-Q1 has very tight accuracy of the current limit regulation level across the full range of currents and temperature. This accuracy is defined at several defined  $R_{ILIM}$  values, 7.15 k $\Omega$ , 25 k $\Omega$ , and 71.5 k $\Omega$  specified in the Electrical Characteristics. As the current limit is changed with the  $R_{ILIM}$ , the KCL ratio value also slightly changes. Additionally, the current limit architecture in the device allows for the tightest variation at current limit set by a 25-k $\Omega$   $R_{ILIM}$ , 1.9 A, of +18%, -7% and at the lower and upper ends of the range, 690 mA and 6.15 A respectively, to be about ±25%. Then, using the boundaries for  $R_{ILIM}$  of 7.15 k $\Omega$  and 71.5 k $\Omega$ , a graph can be built to linearly interpret the error for RILIM values that are inside of the range. This graph can be seen in the figure below.

Figure 7-4. Current Limit Ratio vs Current limit Value With Percent Error

Using this figure, the error can be estimated for any current limit value desired, and the associated KCL value can determine the RILIM resistor appropriate. This graph does not take into account RILIM resistor tolerances, only the error associated with the current limit regulation.

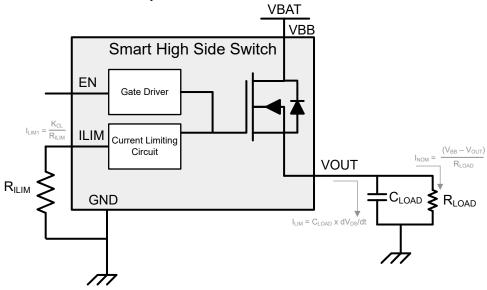

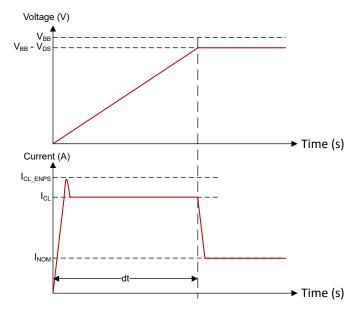

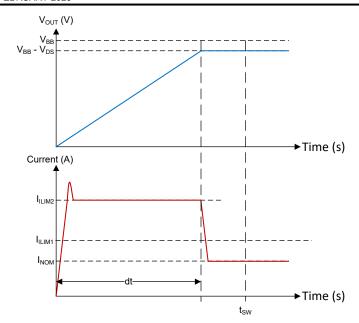

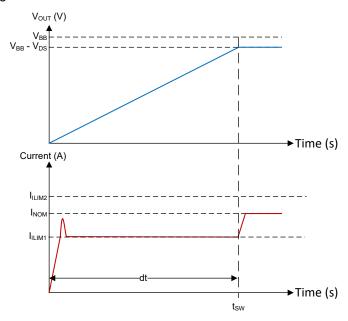

#### 7.3.2.1 Capacitive Charging

Figure 7-5 shows the typical set up for a capacitive load application and the internal blocks that function when the device is used. Note that all capacitive loads have an associated *load* in parallel with the capacitor that is described as a resistive load but in reality it can be inductive or resistive.

Figure 7-5. Capacitive Charging Circuit

The first thing to check is that the nominal DC current,  $I_{NOM}$ , is acceptable for the TPS1HC100-Q1 device. This check can easily be done by taking the  $R_{\theta JA}$  from the *Thermal* section and multiplying the  $R_{ON}$  of the TPS1HC100-Q1 and the  $I_{NOM}$  with it, add the ambient temperature and if that value is below the thermal shutdown value the device can operate with that load current. For an example of this calculation see the *Applications* section.

The second key care about for this application is to make sure that the capacitive load can be charged up completely without the device hitting thermal shutdown. The reason is because if the device hits thermal shutdown during the charging, the resistive nature of the load in parallel with the capacitor starts to discharge the capacitor over the duration the TPS1HC100-Q1 is off. Note that there are some application with high enough load impedance that the TPS1HC100-Q1 hitting thermal shutdown and trying again is acceptable; however, for the majority of applications, the system must be designed so that the TPS1HC100-Q1 does not hit thermal shutdown while charging the capacitor.

With the current clamping feature of the TPS1HC100-Q1, capacitors can be charged up at a lower inrush current than other high current limit switches. This lower inrush current means that the capacitor takes a little longer to charge all the way up. The time that it takes to charge up follows the equation below.

$$I_{LIM} = C \times d(V_{BB} - V_{DS}) / dt$$

(3)

However, because the  $V_{DS}$  for a typical 1 A applications is much less than the  $V_{BB}$  voltage ( $V_{DS} \approx 1A \times 0.1~\Omega = 100$  mV,  $V_{BB} \approx 13.5$  V), the equation can be rewritten and approximated as

$$dt = C \times dV_{BB} / I_{LIM}$$

(4)

Figure 7-6 pictures this charge timing.

Figure 7-6. Capacitive Charging Timing

For more information about capacitive charging with high side switches, see the *How to Drive Capacitive Loads* application note application note. This application note has information about the thermal modeling available along with quick ways to estimate if a high side switch is able to charge a capacitor to a given voltage.

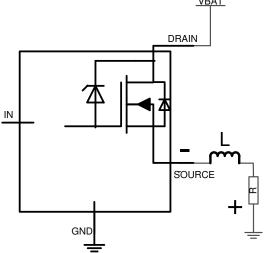

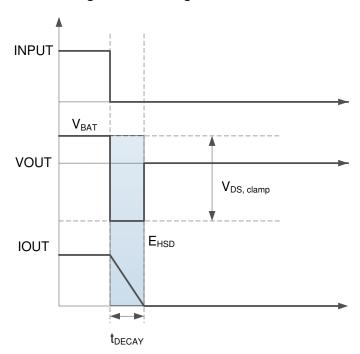

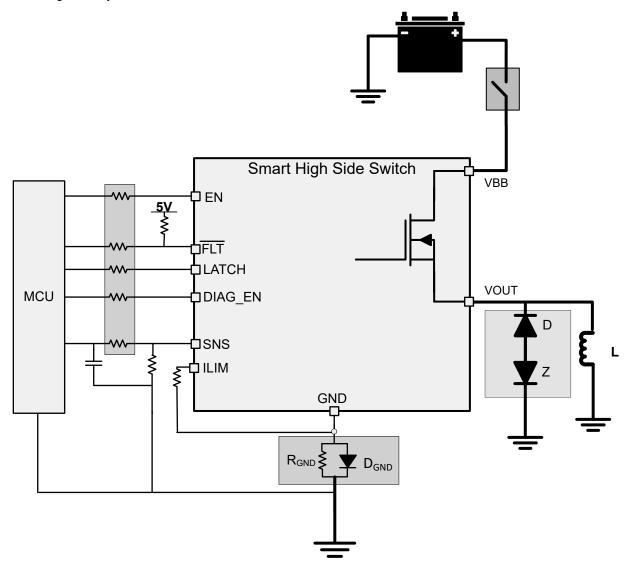

### 7.3.3 Inductive-Load Switching-Off Clamp

When an inductive load is switching off, the output voltage is pulled down to negative, due to the inductance characteristics. The power FET can break down if the voltage is not clamped during the current-decay period. To protect the power FET in this situation, internally clamp the drain-to-source voltage, namely  $V_{DS,clamp}$ , the clamp diode between the drain and gate.

$$V_{DS,clamp} = V_{BAT} - V_{OUT}$$

(5)

During the current-decay period ( $T_{DECAY}$ ), the power FET is turned on for inductance-energy dissipation. Both the energy of the power supply ( $E_{BAT}$ ) and the load ( $E_{LOAD}$ ) are dissipated on the high-side power switch itself, which is called  $E_{HSD}$ . If resistance is in series with inductance, some of the load energy is dissipated in the resistance.

$$E_{HSD} = E_{BAT} + E_{LOAD} = E_{BAT} + E_{L} - E_{R}$$

(6)

From the high-side power switch's view, E<sub>HSD</sub> equals the integration value during the current-decay period.

$$\mathsf{E}_{\mathsf{HSD}} = \int_{0}^{\mathsf{T}_{\mathsf{DECAY}}} \mathsf{V}_{\mathsf{DS},\mathsf{clamp}} \times \mathsf{I}_{\mathsf{OUT}}(\mathsf{t}) \, \mathsf{dt} \tag{7}$$

$$T_{DECAY} = \frac{L}{R} \times ln \left( \frac{R \times I_{OUT(MAX)} + |V_{OUT}|}{|V_{OUT}|} \right)$$

(8)

$$E_{HSD} = L \times \frac{V_{BAT} + |V_{OUT}|}{R^2} \times \left[ R \times I_{OUT(MAX)} - |V_{OUT}| In \left( \frac{R \times I_{OUT(MAX)} + |V_{OUT}|}{|V_{OUT}|} \right) \right]$$

(9)

When R approximately equals 0, E<sub>HSD</sub> can be given simply as:

Figure 7-7. Driving Inductive Load

Figure 7-8. Inductive-Load Switching-Off Diagram

When switching off, battery energy and load energy are dissipated on the high-side power switch, which leads to the large thermal variation. For each high-side power switch, the upper limit of the maximum safe power dissipation depends on the device intrinsic capacity, ambient temperature, and board dissipation condition.

See Figure 8-9 for one dedicated inductance, 5 mH. If the maximum switching-off current is lower than the current value shown on the curve, the internal clamp function can be used for the demagnetization energy dissipation. If not, external free-wheeling circuitry is necessary for device protection.

Figure 7-9. 5-mH Maximum Demagnetization Curve

# 7.3.4 Full Protections and Diagnostics

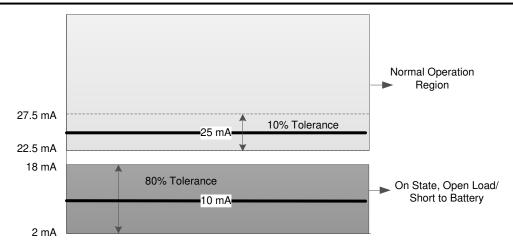

Table 7-1 is when DIAG\_EN is enabled. When DIAG\_EN is low, current sense and FLT are disabled. The output is in high-impedance mode. Refer to Table 7-1 for details.

**Table 7-1. Diagnostic Enable Logic Table**

| DIAG_EN | IN Condition | Protections and Diagnostics                                                                                        |  |  |  |

|---------|--------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|

| HIGH    | ON           | See Fault Table                                                                                                    |  |  |  |

| TilGit  | OFF          | See Fault Table                                                                                                    |  |  |  |

|         | ON           | Diagnostics disabled, protection normal                                                                            |  |  |  |

| LOW     | OFF          | FLT is high impedance,<br>SNS is not driven and is clamped to<br>1.5V if external voltage is applied to the<br>pin |  |  |  |

Table 7-2. Fault Table

| Conditions                                | EN | VOUT                                                        | Latch | FLT  | SNS                                  | Behavior                                                                                                                                                                                                                                               | Recovery                                                                                                |

|-------------------------------------------|----|-------------------------------------------------------------|-------|------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

|                                           | L  | L                                                           | х     | Hi-Z | 0                                    | Normal                                                                                                                                                                                                                                                 |                                                                                                         |

| Normal                                    | Н  | V <sub>BB</sub> –<br>I <sub>LOAD</sub> ×<br>R <sub>ON</sub> | Х     | Hi-Z | I <sub>Load</sub> / K <sub>sns</sub> | Normal                                                                                                                                                                                                                                                 |                                                                                                         |

| Overcurrent                               | н  | V <sub>BB</sub> – I <sub>LIM</sub><br>× R <sub>LOAD</sub>   | X     | L    | V <sub>SNSFH</sub>                   | Holds the current at the current limit until thermal shutdown or when the overcurrent event is removed. Typical deglitch time for device to recognize overcurrent fault and begin to act on it is 2.5 µs.                                              |                                                                                                         |

| STG, Relative<br>Thermal                  | н  | H/L                                                         | L     | L    | V <sub>SNSFH</sub>                   | Shuts down when devices hits relative or absolute thermal shutdown. Typical deglitch time for device to recognize overcurrent fault and begin to act on it is 2.5 µs. Typical deglitch time for device to recognize a T <sub>ABS</sub> fault is 20 µs. | Auto retries when T <sub>HYS</sub> is met and it has been longer than t <sub>RETRY</sub> amount of time |

| Shutdown,<br>Absolute Thermal<br>Shutdown | Н  | H/L                                                         | Н     | L    | Vsnsfh                               | Shuts down when devices hits relative or absolute thermal shutdown. Typical deglitch time for device to recognize overcurrent fault and begin to act on it is 2.5 µs. Typical deglitch time for device to recognize a T <sub>ABS</sub> fault is 20 µs. | Stays off until latch or enable is toggled                                                              |

| Conditions       | EN | VOUT | Latch | FLT  | SNS                                          | Behavior                                                                                                                                                  | Recovery                    |

|------------------|----|------|-------|------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

|                  | Н  | Н    | x     | Hi-Z | I <sub>Load</sub> /<br>K <sub>SNS</sub> = ~0 | Normal behavior, user can judge through SNS pin output if it is an open load or not.                                                                      |                             |

| Open load, STB   | L  | Н    | х     | L    | V <sub>SNSFH</sub>                           | Internal pullup resistor is active. If $V_{BB}$ – $V_{OUT}$ < $V_{OL}$ then fault active. Typical deglitch time before fault is indicated is 700 $\mu$ s. | Clears when fault goes away |

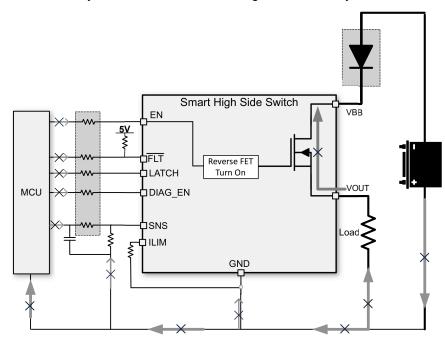

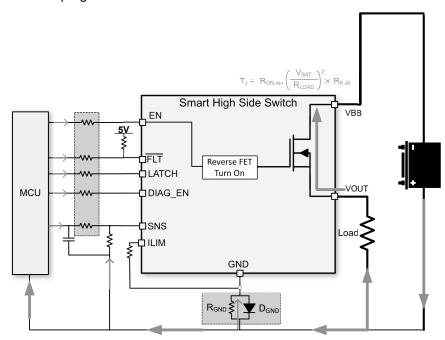

| Reverse Polarity | X  | x    | х     | х    | x                                            | Channel turns on to lower power dissipation. Current into ground pin is limited by external ground network.                                               |                             |

Table 7-3. Deglitch Time for Each Fault Condition

| Fault Condition | Deglitch Time |

|-----------------|---------------|

| ILIM            | 2.5 µs        |

| TREL            | 2.5 µs        |

| TABS            | 20 µs         |

| Open load       | 700 μs        |

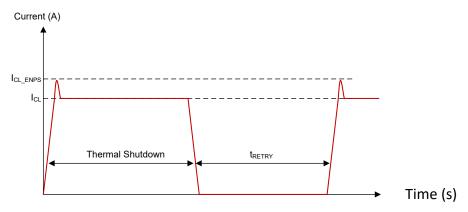

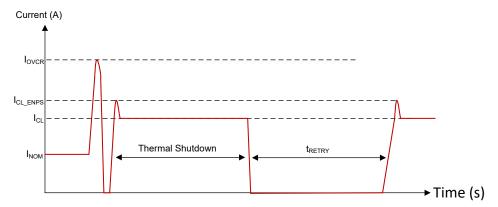

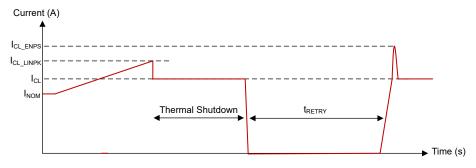

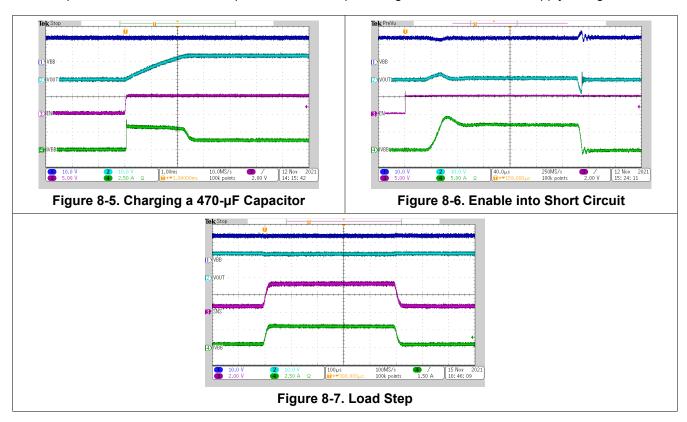

#### 7.3.4.1 Short-Circuit and Overload Protection